## XWD1003---具有 OOK 调制、适用于高频大电流二线制电力线通信的收发器

### 特性

■ NEW 专为 HBS 通讯应用设计：

- 隔离电感支持  $0.68\mu H \sim 22\mu H$  小体积大电流电感，极大减小方案成本。

- 通讯载波频率为 Mhz，可对应更高数据速率 115200 等

- 支持点对点单端通讯或无极性双端差分通讯

- 所需引脚更少，可支持独有 ESSOP10 和 SOP8 封装，节省方案体积

- 半双工通讯

- 3V 至 5.5V 宽范围电源 VCC 电压

- 采用双端通讯电路总线可支持市电交流供电

- 电路设计简单外围元件少

- 可靠性高，带有热关断保护

- 工作温度范围：-40°C 至 125°C

- $\pm 4KV$  HBM ESD

- SOP8、ESSOP10 封装

### 应用

- 直流&交流电力输送

- 电池充电通讯、光伏储能逆变、调光 LED 控制

### 描述

XWD1003 是具有内置开关键控 (OOK) 调制和解调功能的收发器，用于实现电力线上的通讯。通过将数据调制到现有电力线上，可实现在同一对导线中同时进行电力输送和数据通信，从而显著降低系统成本。利用高频震荡代替逻辑电平具有用于电力线通信的 OOK 调制功能，可使用两颗进行互联进行双端差分通讯，或者单端通讯。

引脚可编程接口可简化系统设计。可以通过更改 FADJ 引脚上的外部电阻器来调节载波频率。宽范围载波频率使系统设计人员能够灵活地选择外部电感器和电容器。此外，OOK 调制不受数据极性的影响，可简化系统安装。

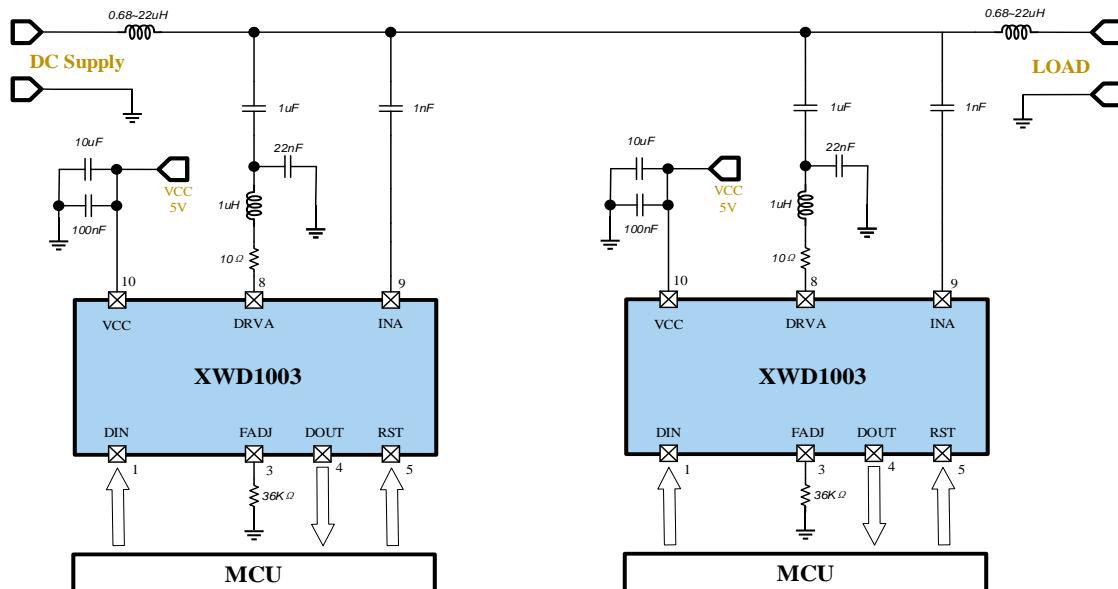

### 典型应用拓扑（单端通讯）

注：1.当 XWD1003 不发送数据时，其 DIN 需保持 5V 高电平来接受信号，即半双工通讯。

2.由于总线共用，当芯片发送数据时自身 Dout 也会解调输出相同数据，如介意可采用软件滤除、发送数据时通过 Mos 等断开 INA 与总线连接发完再恢复等方案避免自发自收情况。

## XWD1003---具有OOK调制、适用于高频大电流二线制电力线通信的收发器

绝对最大值<sup>(†)</sup>

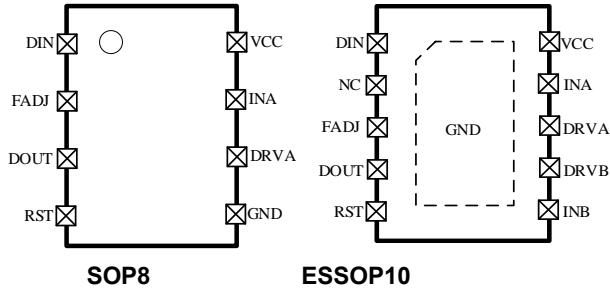

## 引脚排列

Table 2.1

图2. 引脚排列

| 参数                                    | 范围             |

|---------------------------------------|----------------|

| 引脚至 GND 电压<br>( VCC, RST, DOUT, DIN ) | -0.3V~7V       |

| 储存温度                                  | -65°C to 150°C |

| 工作温度                                  | -40°C to 125°C |

| ESD 额定值 ( HBM )                       | ±4KV           |

<sup>†</sup> 注：如果器件工作条件超过上述“绝对最大值”，可能引起器件永久性损坏。这仅是极限参数，不建议器件在极限值或超过上述极限值的条件下工作。器件长时间工作在极限条件下可能会影响其可靠性。

## ESD 警告

## ESD(静电放电)敏感器件。

带电器件和电路板可能会在没有察觉的情况下放电。尽管本产品具有专利或专有保护电路，但在遇到高能量ESD时，器件可能会损坏。因此，应当采取适当的ESD防范措施，以避免器件性能下降或功能丧失。

## 功能框图和引脚描述

表2.2 引脚功能描述

| 引脚编号    | 引脚名称 | 描述                           |

|---------|------|------------------------------|

| ESSOP10 |      |                              |

| 1       | DIN  | 接收模块数据输入端口。                  |

| 2       | NC   | NC 引脚浮空即可                    |

| 3       | FADJ | 载波频率选择。 使用连接至 GND 的电阻器来选择频率。 |

| 4       | DOUT | 接收模块数据输出端口。                  |

| 5       | RST  | 发送模块使能，低电平使能，高电平芯片停止发送信号。    |

| 6       | INB  | 接收模块输入 B                     |

| 7       | DRVB | 发送模块输出 B                     |

| 8       | DRVA | 发送模块输出 A                     |

| 9       | INA  | 接收模块输入 A                     |

| 10      | VCC  | 电源供电                         |

| EP      | GND  | 电源地。                         |

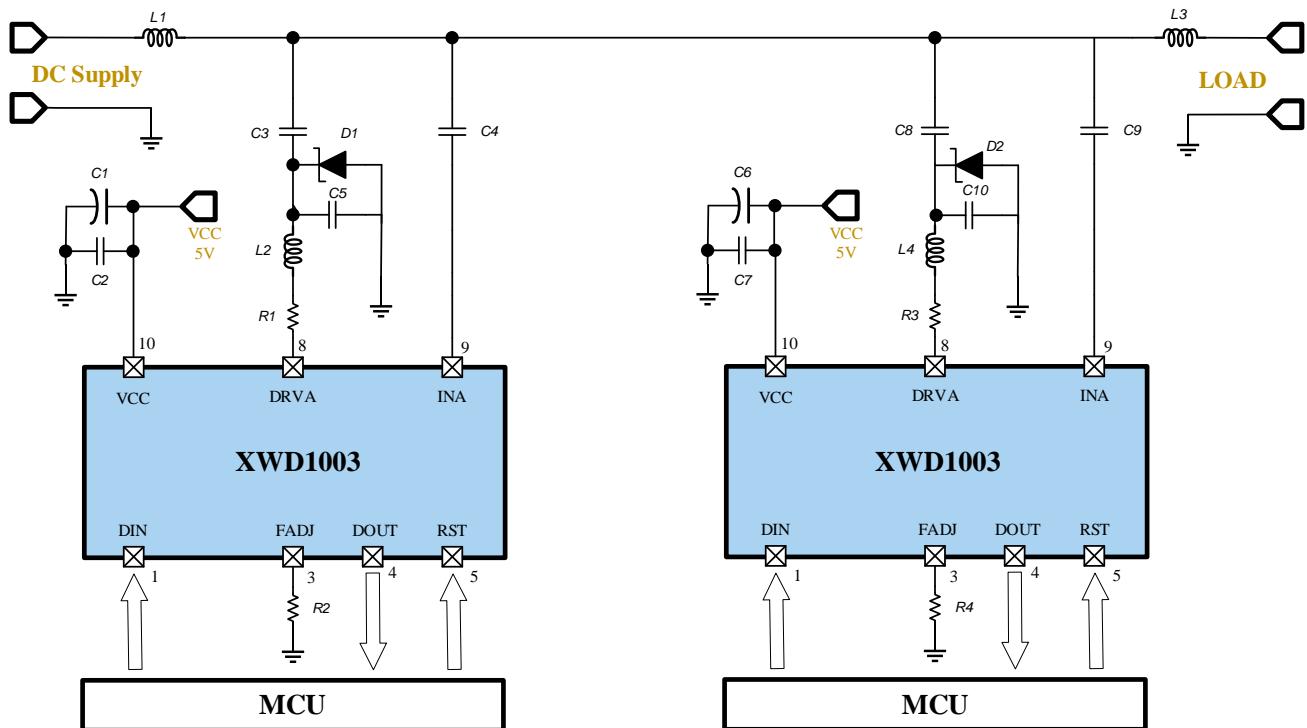

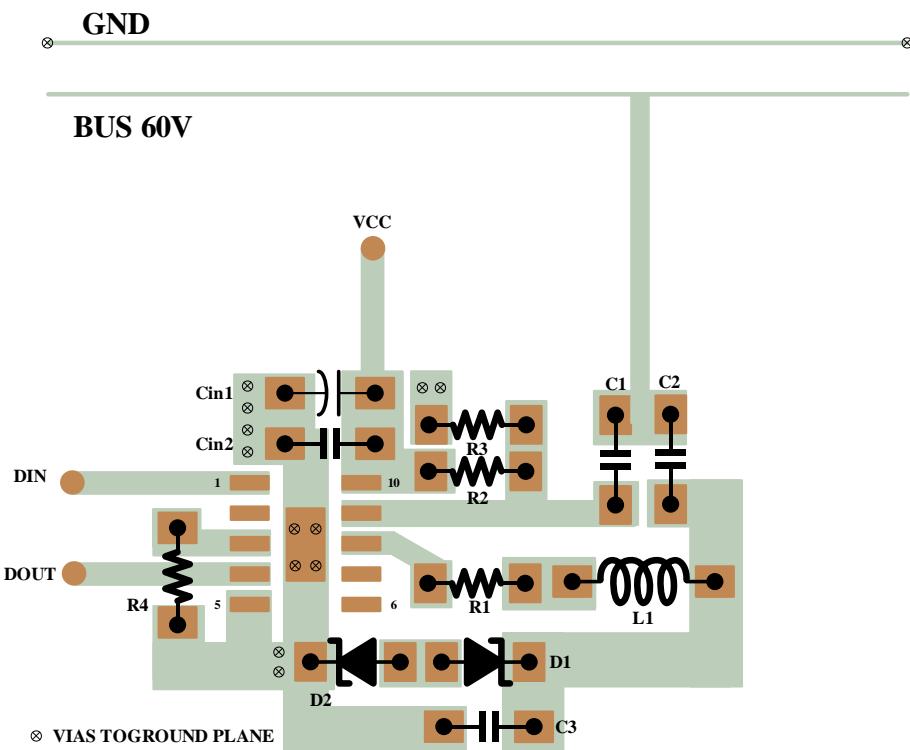

## 应用信息：单端通讯应用电路

图3 XWD1003采用单端通讯典型应用

## 单端通讯元器件选型推荐：

| 型号     | 含义       | 推荐值               | 备注                                    |

|--------|----------|-------------------|---------------------------------------|

| C1、C6  | 电解电容     | 47uF, 25V         | 该电容可吸收来自总线多余能量, 容值不易过小                |

| C2、C7  | 去耦电容     | 100nF, 25V        | 用于滤除高频噪声                              |

| C4、C9  | 耦合电容     | 1nF/470pF         | 耐压值根据总线电压减 2V 选择                      |

| C3、C8  | 耦合电容     | 1uF               | 耐压值根据总线电压选择                           |

| L1、L3  | 隔离电感     | 0.68~22uH         | 感值大小根据载波频率选择, 电感饱和电流根据总线最大电流的 1.4 倍选择 |

| L2、L4  | 电感       | 1uH               | 电感饱和电流大于 1A, 功率电感和贴片电感均可              |

| C5、C10 | 陶瓷电容     | 22nF              |                                       |

| R1、R3  | 贴片电阻     | 10Ω               | 减小电流应力                                |

| D1、D2  | 防浪涌二极管   | 6V>反向截止电压≥5V      | 防止芯片引脚过压损坏                            |

| R2、R4  | 载波频率设置电阻 | 36K ( 对应载波 2Mhz ) | 载波频率须大于 10 倍以上的数据频率                   |

## XWD1003---具有OOK调制、适用于高频大电流二线制电力线通信的收发器

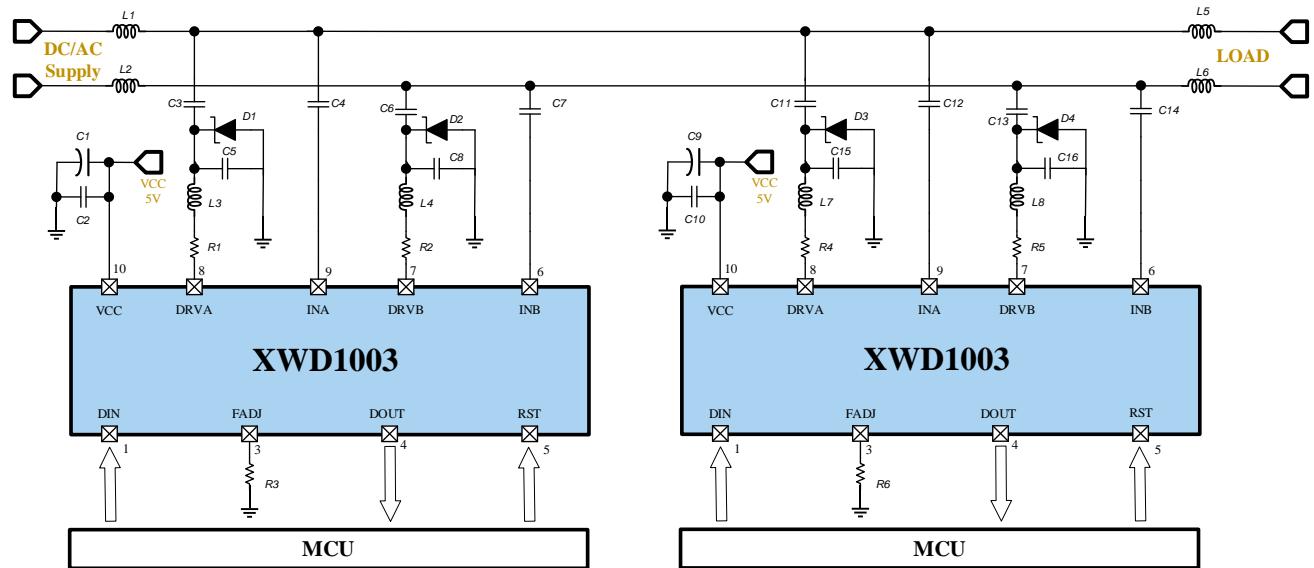

## 应用信息：双端无极性差分通讯应用电路

图4 XWD1003 采用双端差分通讯典型应用

注：XWD1003 采用双端差分通讯时，总线可支持 DC 直流电源或市电 50Hz 交流电源。

## 双端通讯元器件选型推荐：

| 型号            | 含义       | 推荐值               | 备注                                   |

|---------------|----------|-------------------|--------------------------------------|

| C1、C9         | 电解电容     | 47uF, 25V         | 该电容可吸收来自总线多余能量，容值不易过大                |

| C2、C10        | 去耦电容     | 100nF, 25V        | 用于滤除高频噪声                             |

| C4、C7、C12、C14 | 耦合电容     | 1nF/470pF         | 耐压值根据总线电压减 2V 选择                     |

| C3、C6、C11、C13 | 耦合电容     | 1uF               | 耐压值根据总线电压选择                          |

| L1、L2、L5、L6   | 隔离电感     | 0.68~22uH         | 感值大小根据载波频率选择，电感饱和电流根据总线最大电流的 1.4 倍选择 |

| L3、L4、L7、L8   | 电感       | 1uH               | 电感饱和电流大于 1A，功率电感和贴片电感均可              |

| C5、C8、C15、C16 | 陶瓷电容     | 22nF              |                                      |

| R1、R2、R4、R5   | 贴片电阻     | 10Ω               | 减小电流应力                               |

| D1、D2、D3、D4   | 防浪涌二极管   | 6V>反向截止电压≥5V      | 防止芯片引脚过压损坏                           |

| R3、R6         | 载波频率设置电阻 | 36K ( 对应载波 2Mhz ) | 载波频率须大于 10 倍以上的数据频率                  |

**XWD1003---具有OOK调制、适用于高频大电流二线制电力线通信的收发器****技术规格**

除非另有规定，所有电压均相对于 GND。

**表5.**

| 参数               | 测试条件                  | 最小值              | 典型值 | 最大值 | 单位  |

|------------------|-----------------------|------------------|-----|-----|-----|

| <b>电源输入</b>      |                       |                  |     |     |     |

| V <sub>VCC</sub> | VCC 输入电源工作电压          |                  | 2.7 | 5   | 5.5 |

| I <sub>VCC</sub> | 电源电流 ( 静态 )           | 传输模式 ( RST=0V )  |     | 61  |     |

|                  |                       | 接收模式 ( RST=VCC ) |     | 3   |     |

| I <sub>DIN</sub> | 输入电流 ( DIN、RST )      | DIN=5V,VCC=5V    |     | 13  |     |

| V <sub>OH</sub>  | 发送模块输出高电平(DRVA,DRVVB) | DIN=0V,VCC=5V    |     | 5   |     |

| V <sub>OL</sub>  | 发送模块输出低电平(DRVA,DRVVB) | DIN=0V,VCC=5V    |     | 0   |     |

| V <sub>TH</sub>  | 数据接收端口电压阈值 ( DIN )    | 上升沿              |     | 1.2 |     |

|                  |                       | 下降沿              |     | 0.7 |     |

## XWD1003---具有 OOK 调制、适用于高频大电流二线制电力线通信的收发器

### 特性说明

#### 1. 使用 FADJ 引脚进行 OOK 载波频率调制

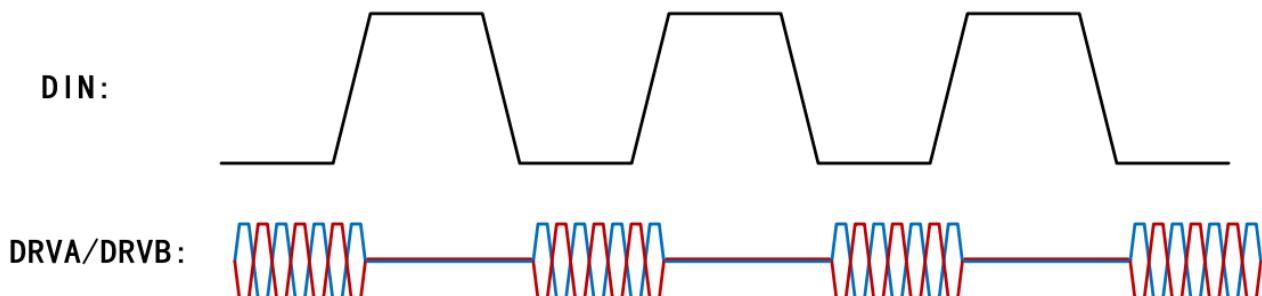

DIN 输入端的数据由载波频率 ( $f_0$ ) 通过 FADJ 引脚调制, 图 6.1 说明了调制方案。建议使用比数据速率高 10 倍的载波频率。更高的数据速率是可能的, 但代价是使用较低的比率会增加脉宽失真。

图 6.1 OOK 调制

载波频率可通过改变 FADJ 引脚外部接地的电阻值进行调整。表 6.1 显示了每个建议电阻值的载波频率。

表 6.1 OOK  $f_0$  与  $R_{SET}$

| $R_{SET}$ (KΩ) | OOK $f_0$ (MHz) |

|----------------|-----------------|

| 160            | 1               |

| 100            | 1.2             |

| 82             | 1.3             |

| 56             | 1.6             |

| 36             | 2               |

| 18             | 2.9             |

#### 2. OOK 解调

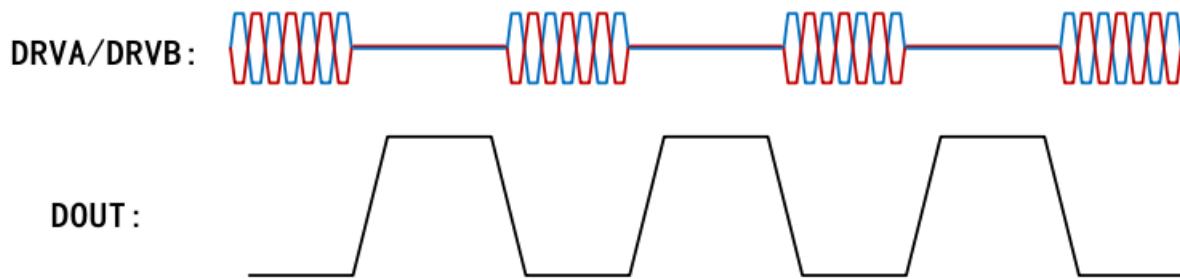

在 INA 和 INB 输入端接收到的 OOK 信号经过带通滤波器和峰值检测器, 以重新生成原始数据流。图 6.2 显示了 OOK 输入和 DOUT 输出波形。带通滤波器特性需根据载波频率 (通过 FADJ 对地电阻设置) 调整为最佳配置。

图 6.2 OOK 解调

#### 3. 无极性操作

在 OOK 模式下, XWD1003 在接收器输入端不受 INA 和 INB 极性的影响。接收器数据比较器仅检查接收输入信号幅度, 忽略极性, 以确定其逻辑电平。请注意, 反转极性确实会导致脉宽失真降低。

## XWD1003---具有OOK调制、适用于高频大电流二线制电力线通信的收发器

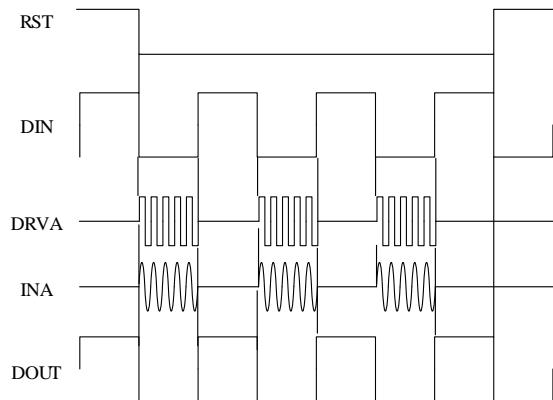

### 4. 通讯时序

当芯片进行发送 (RST=0V) 时, DIN 输入端的数据通过由 FADJ 对地电阻值设置的载波频率进行调制

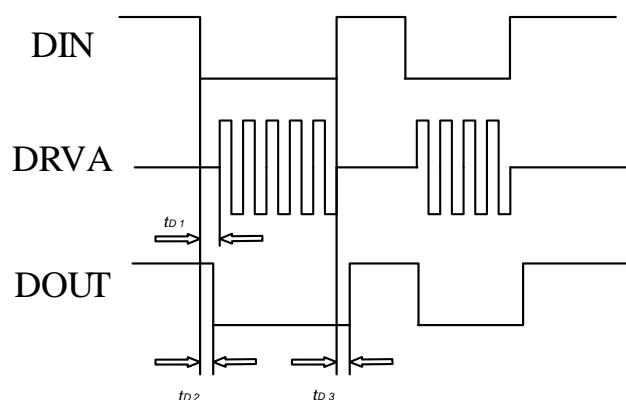

### 5. 通讯延时

延时时间

|          | ( $\mu$ s) |

|----------|------------|

| $t_{D1}$ | 0.25       |

| $t_{D2}$ | 2.5        |

| $t_{D3}$ | 3.2        |

## XWD1003---具有OOK调制、适用于高频大电流二线制电力线通信的收发器

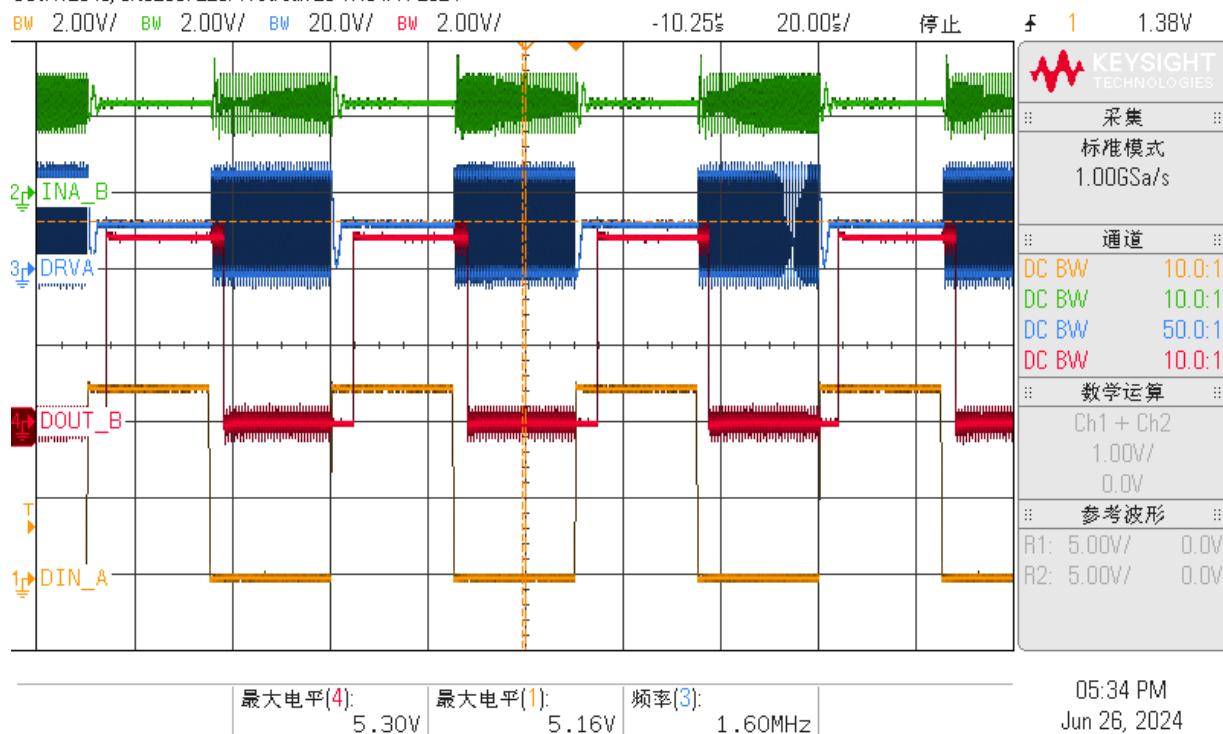

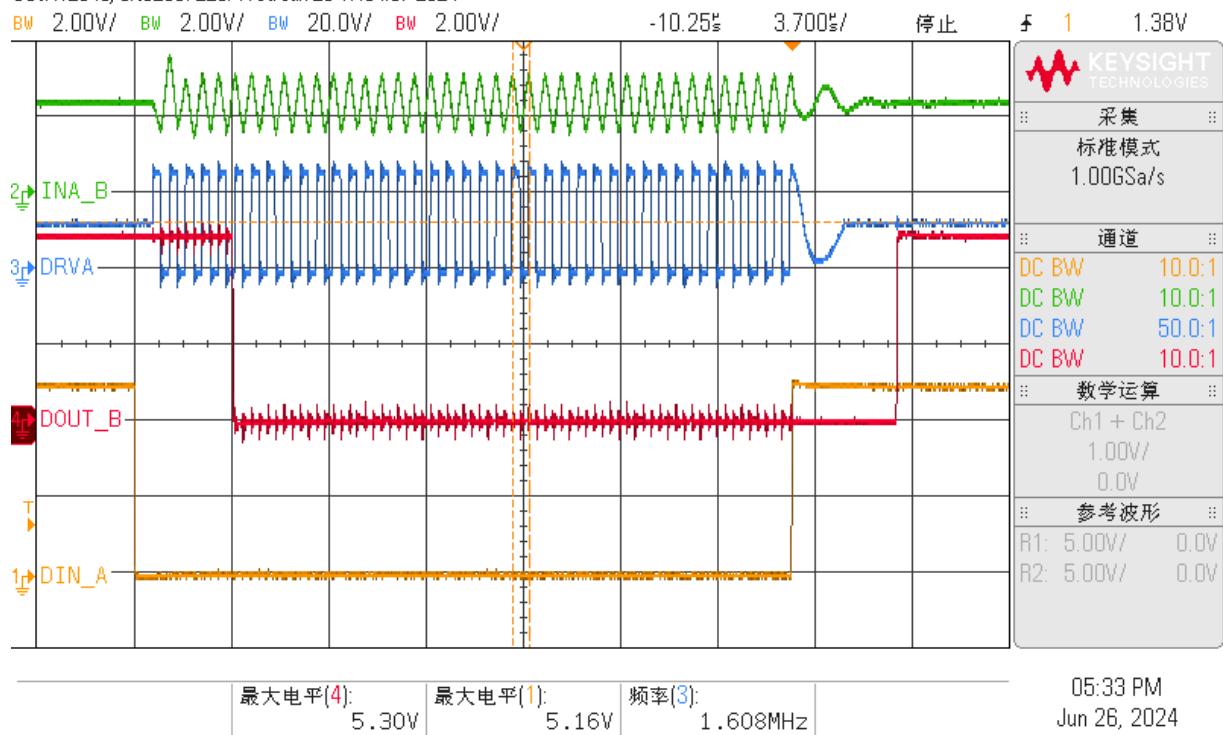

## 波形展示

DSOX1204G, CN62057226: Wed Jun 26 17:34:41 2024

DSOX1204G, CN62057226: Wed Jun 26 17:34:07 2024

## 应用信息：单端通讯参考布局举例

### 概述

XWD1003 的高集成度使 PCB 板布局非常简单和容易。较差的布局会影响 XWD1003 的性能，造成电磁干扰(EMI)、电磁兼容性(EMC)差、地跳以及电压损耗，进而影响稳压调节和稳定性。为了优化其电气和热性能，应运用下列规则来实现良好的 PCB 布局布线，确保最佳性能：

- 必须将高频陶瓷输入电容 CIN2 尽量近距离放在 VCC(PIN10)、GND 引脚旁边，以尽量降低高频噪声。

- 为使过孔传导损耗最小并降低模块热应力，应使用多个过孔来实现顶层和其他电源层或地层之间的互连。

- 避免从电感下方走线，信号线之间保留一定距离，可以采用铺地隔离。

- 应考虑电感所产生的 ACR 和 DCR 损耗，所造成的热量传导给芯片。可酌情将电感放置稍远或合理设计热岛。

- 对高电流路径应使用较大 PCB 覆铜区域，包括 GND 引脚。这有助于最大限度地减少 PCB 传导损耗和热应力。

## XWD1003---具有OOK调制、适用于高频大电流二线制电力线通信的收发器

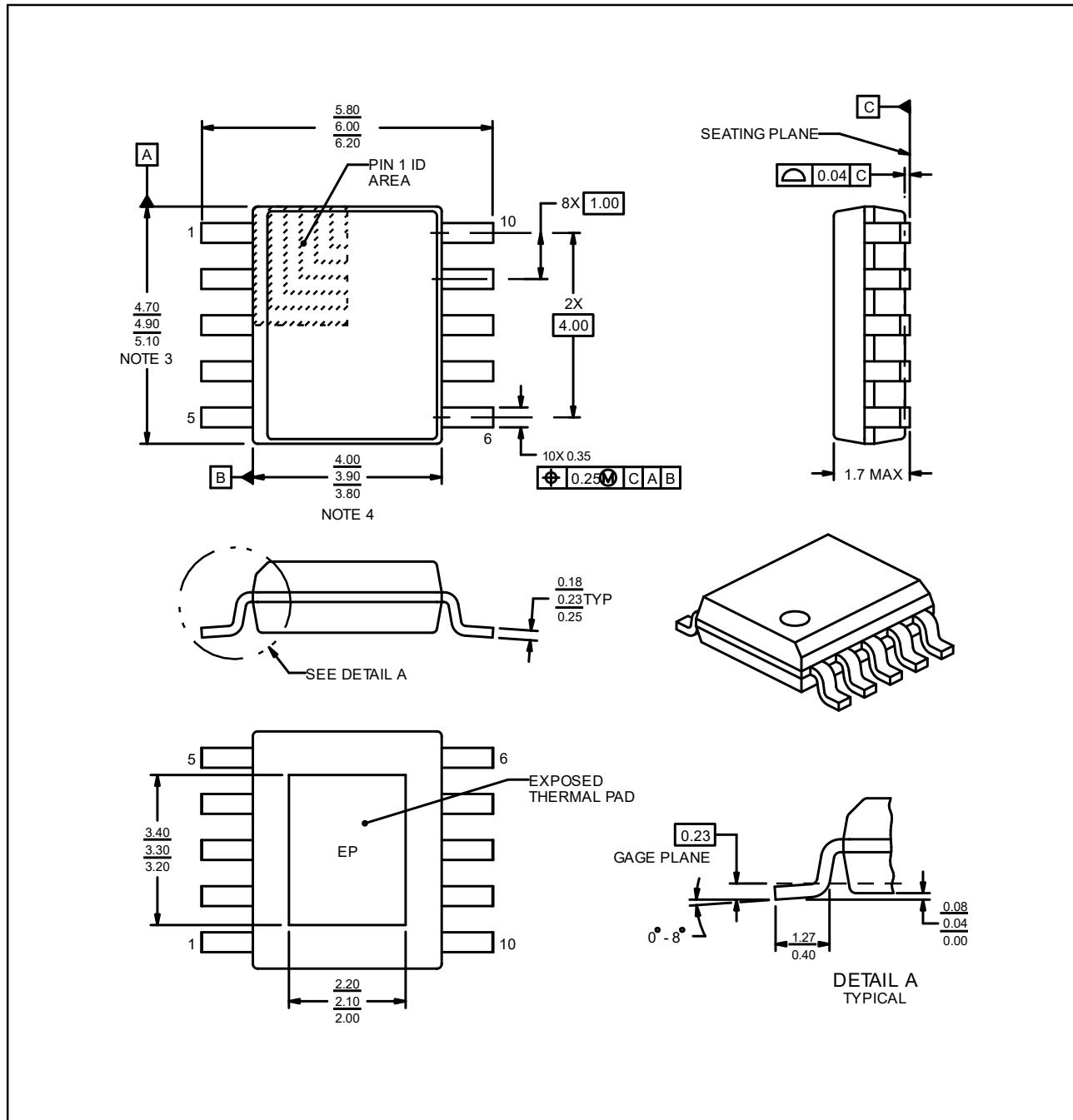

## 封装外形描述(ESSOP10)

## 具备底部ePad的10引脚塑封SOIC

注：

- (1) 所有的数据单位都是毫米，括号内的任何尺寸仅供参考。

- (2) 本图如有更改，恕不另行通知。

- (3) 此尺寸不包括塑模毛边，突起，或水口毛刺。

## 包装信息

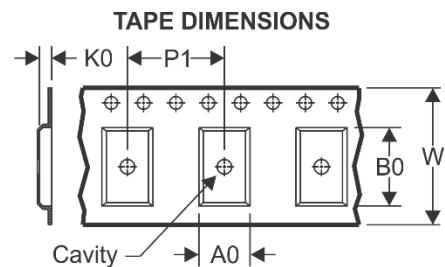

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

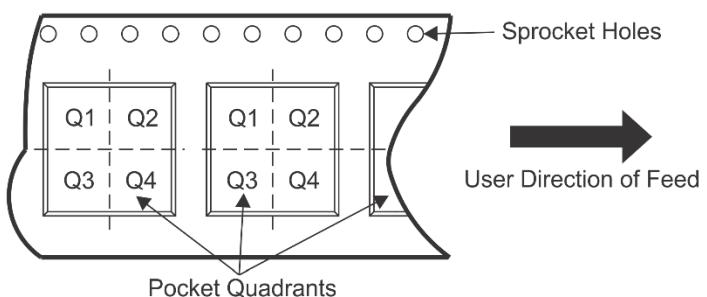

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

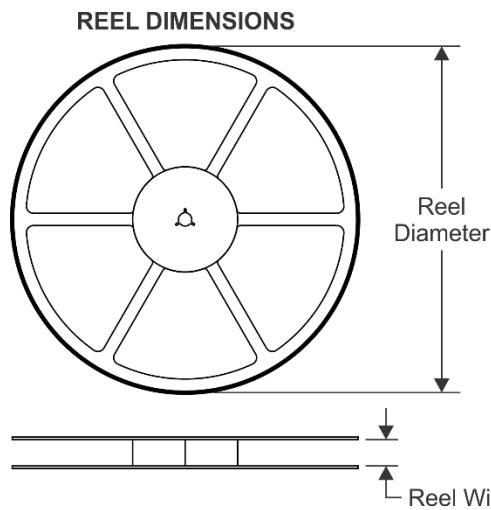

\*ALL dimensions are nominal

| Device  | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1(mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|---------|--------------|-----------------|------|------|--------------------|-------------------|---------|---------|---------|---------|--------|---------------|

| XWD1003 | ESSOP10      | ES              | 10   | 4000 | 330                | 12.4              | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |