乾芯科技

STARRYSTONETECH

QXS320F280049RevB数字信号控制器

合肥乾芯科技有限公司

表 1：版本历史

| 版本号  | 修订日期       | 修订内容                   |

|------|------------|------------------------|

| 1. 0 | 2025/04/22 | 初稿                     |

| 1. 1 | 2025/04/23 | 引脚说明、信号描述表格格式调整        |

| 1. 2 | 2025/04/25 | 修正电气参数                 |

| 1. 3 | 2025/05/09 | 名称变更为QXS320F280049RevB |

| 1. 4 | 2025/05/14 | 添加产品迭代版本               |

| 1. 5 | 2025/06/06 | 更新部分图片                 |

| 1. 6 | 2025/06/20 | 更新电气参数                 |

| 1. 7 | 2025/07/17 | 修正文字错误                 |

| 1. 8 | 2025/09/18 | 添加仿真/JTAG              |

| 1. 9 | 2025/09/19 | 更新产品编码                 |

| 2. 0 | 2025/10/11 | 删除FSI内容                |

## 目 录

|                                        |    |

|----------------------------------------|----|

| 1 特性 .....                             | 8  |

| 2 应用 .....                             | 9  |

| 3 说明 .....                             | 10 |

| 3.1 功能框图 .....                         | 11 |

| 3.2 器件特性 .....                         | 12 |

| 3.3 产品编码 .....                         | 13 |

| 3.3.1. 产品迭代版本 .....                    | 13 |

| 4 终端配置与功能 .....                        | 14 |

| 4.1 引脚图 .....                          | 14 |

| 4.2 引脚说明 .....                         | 17 |

| 4.3 信号描述 .....                         | 31 |

| 4.3.1 模拟信号 .....                       | 31 |

| 4.3.2 数字信号 .....                       | 36 |

| 4.3.3 电源与接地 .....                      | 41 |

| 4.3.4 测试, JTAG 与复位 .....               | 43 |

| 4.4 GPIO .....                         | 44 |

| 4.4.1 GPIO 复用引脚表 .....                 | 44 |

| 4.4.2 ADC 引脚上的数字复用 (AGPIO) .....       | 46 |

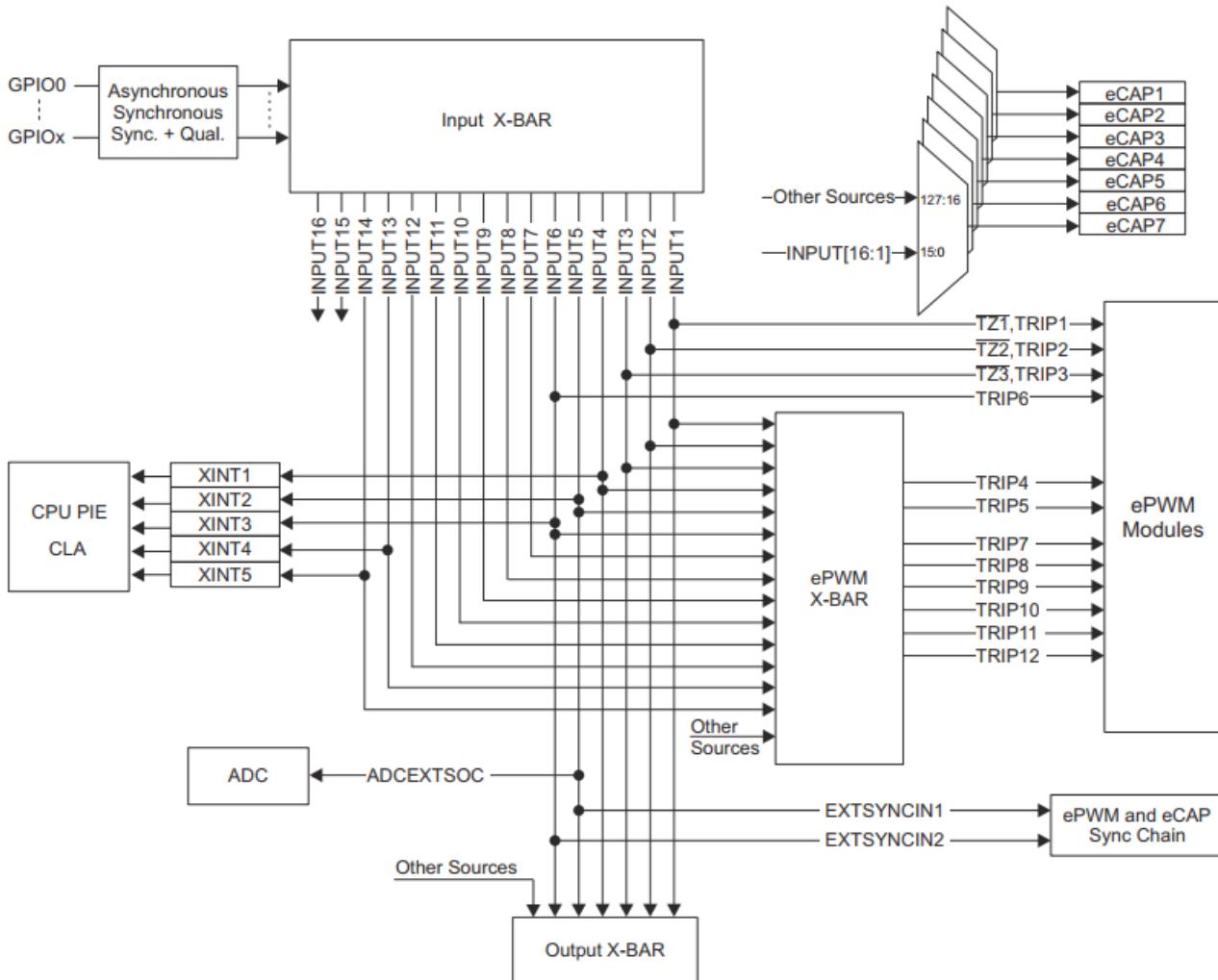

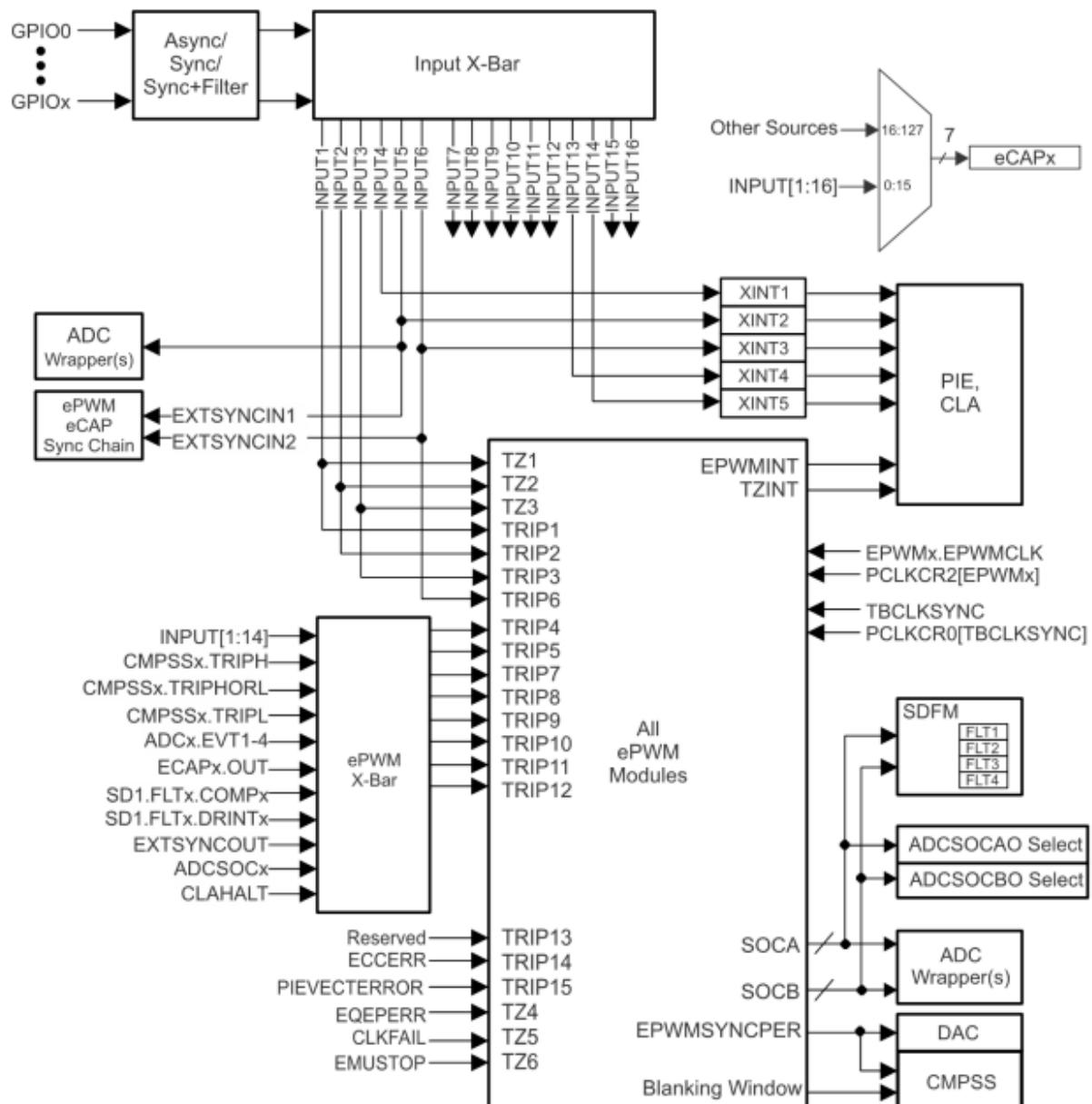

| 4.4.3 GPIO 输入 X-BAR .....              | 47 |

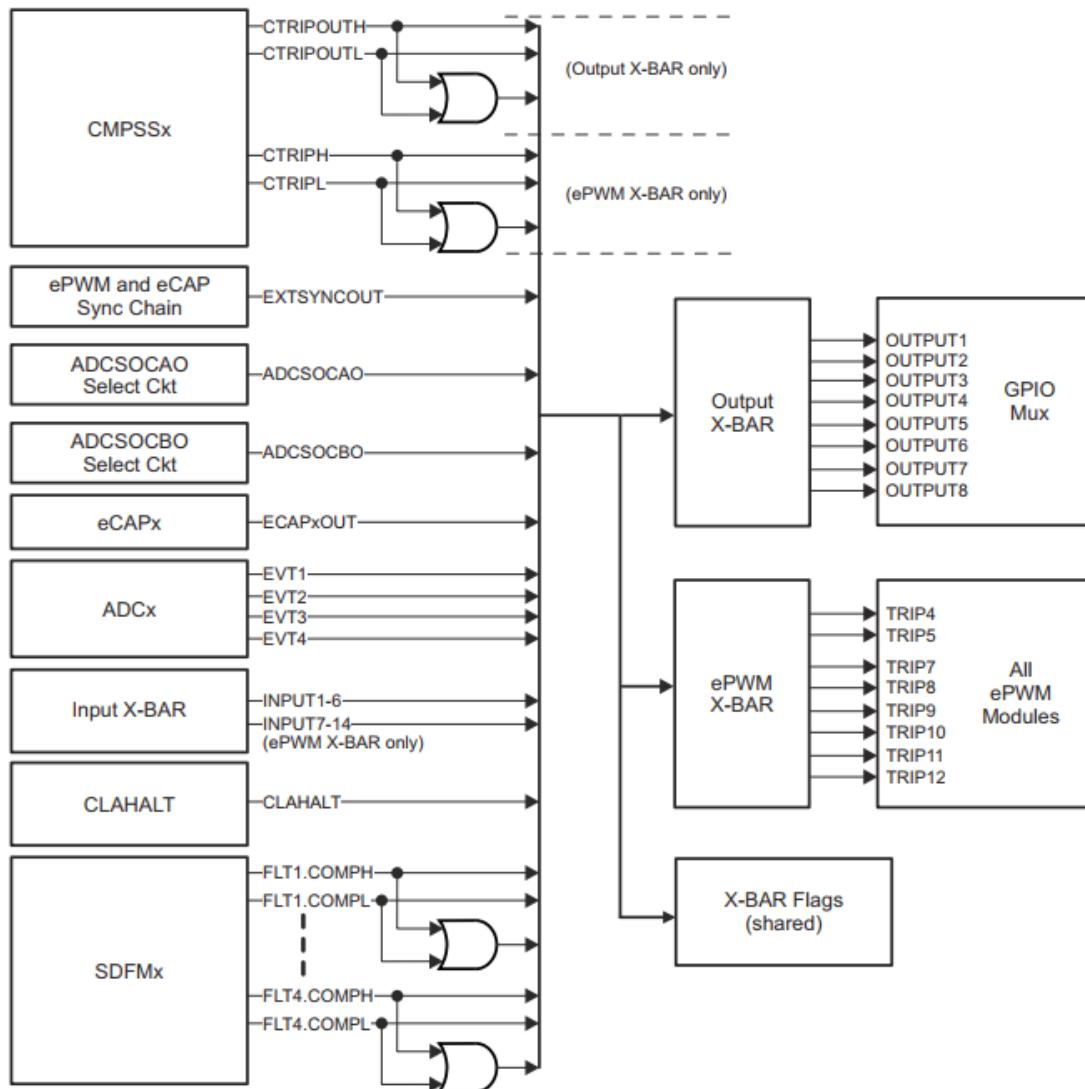

| 4.4.4 GPIO 输出 X-BAR 和 ePWM X-BAR ..... | 49 |

| 4.5 GPIO 引脚内部上拉/下拉 .....               | 50 |

| 4.6 未使用引脚的连接 .....                     | 51 |

| 5 规格 .....                             | 52 |

| 5.1 绝对最大值范围 <sup>(1)(2)</sup> .....    | 52 |

| 5.2 产品 ESD 范围 .....                    | 53 |

| 5.3 推荐工作条件 .....                       | 53 |

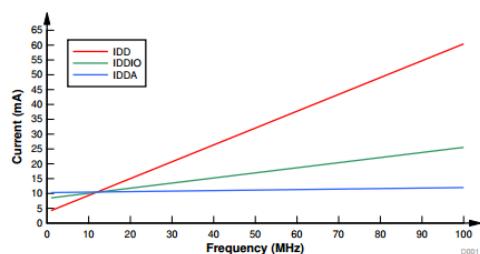

| 5.4 耗电概述 .....                         | 54 |

| 5.4.1 系统电流消耗 (外部电源) .....              | 54 |

|                                     |     |

|-------------------------------------|-----|

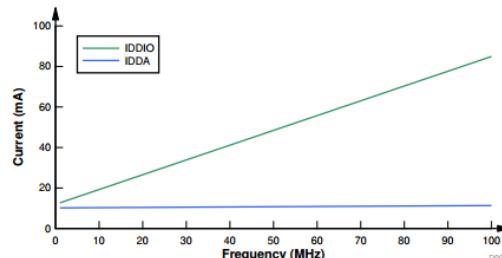

| 5.4.2 工作模式测试描述 .....                | 55  |

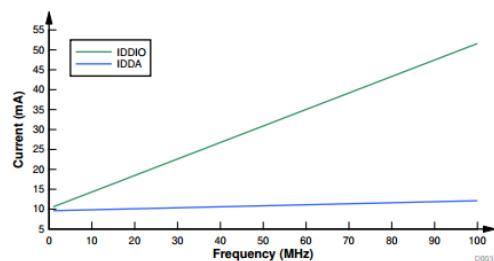

| 5.4.3 减少电流消耗.....                   | 56  |

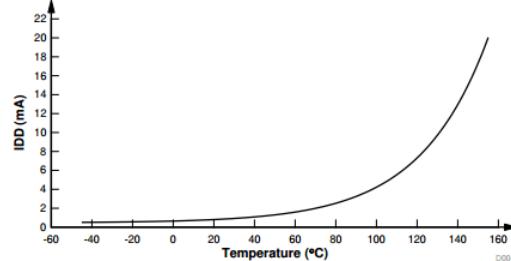

| 5.4.4 减少电流消耗.....                   | 57  |

| 5.5 电气特性.....                       | 59  |

| 5.6 热阻特征 .....                      | 61  |

| 5.6.1 PK封装的热阻特性 .....               | 61  |

| 5.6.2 PZ 封装的热阻特性 .....              | 62  |

| 5.6.3 PM 封装的热阻特性.....               | 63  |

| 5.6.4 RSH 封装的热阻特性 .....             | 64  |

| 5.7 散热设计注意事项.....                   | 66  |

| 5.8 模拟外设 .....                      | 67  |

| 5.8.1 模数转换器 (ADC) .....             | 77  |

| 5.8.1.1 结果寄存器映射.....                | 80  |

| 5.8.1.2 ADC 配置 .....                | 80  |

| 5.8.1.3 ADC 电气数据与时序 .....           | 80  |

| 5.8.2 可编程增益放大器(PGA).....            | 85  |

| 5.8.2.1 PGA电气数据和时序 .....            | 86  |

| 5.8.3 温度传感器 .....                   | 89  |

| 5.8.3.1 温度传感器电气数据和时序 .....          | 89  |

| 5.8.4 Buffered 数模转换器(DAC).....      | 90  |

| 5.8.4.1 Buffered DAC 电气数据和时序 .....  | 91  |

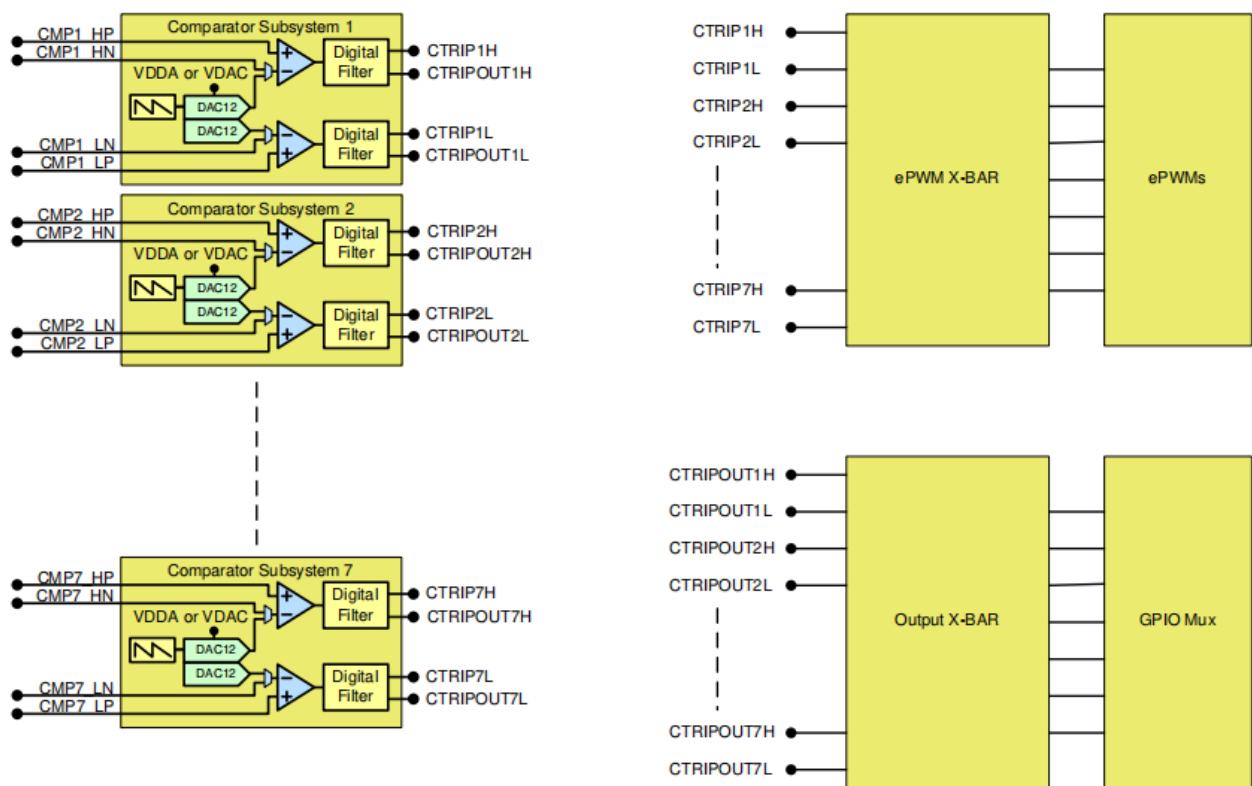

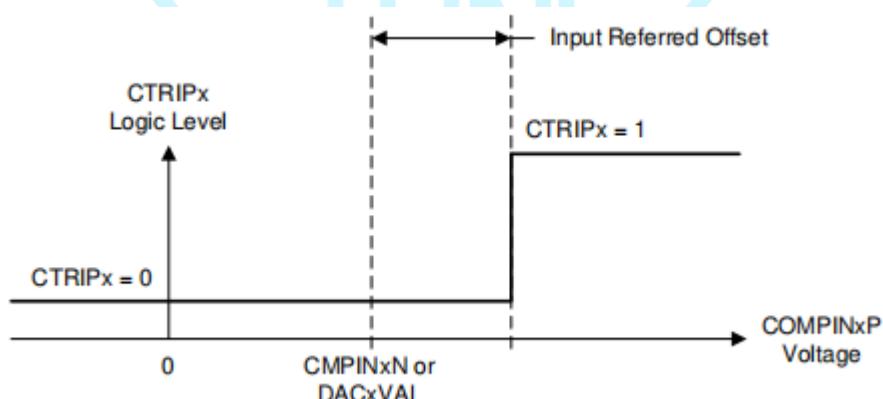

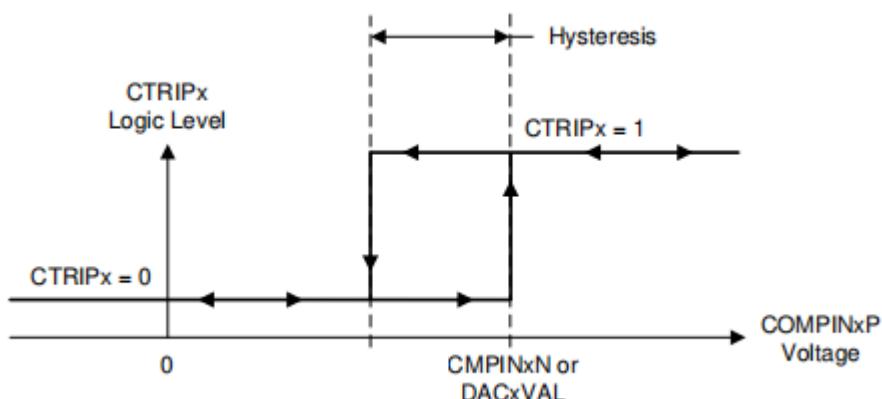

| 5.8.5 比较器子系统(CMPSS) .....           | 92  |

| 5.8.5.1 CMPSS 电气数据与时序 .....         | 93  |

| 5.9 控制外设 .....                      | 95  |

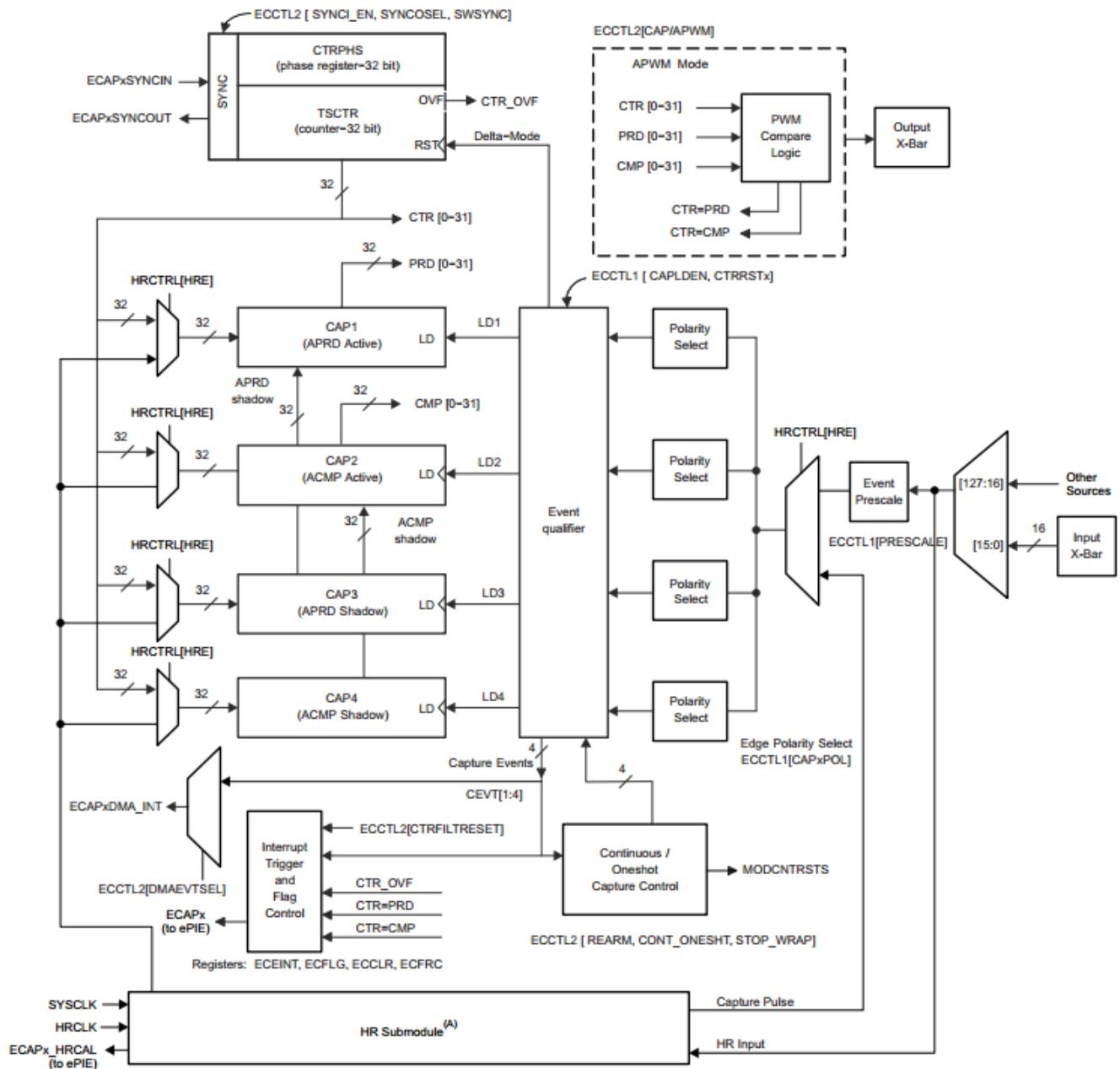

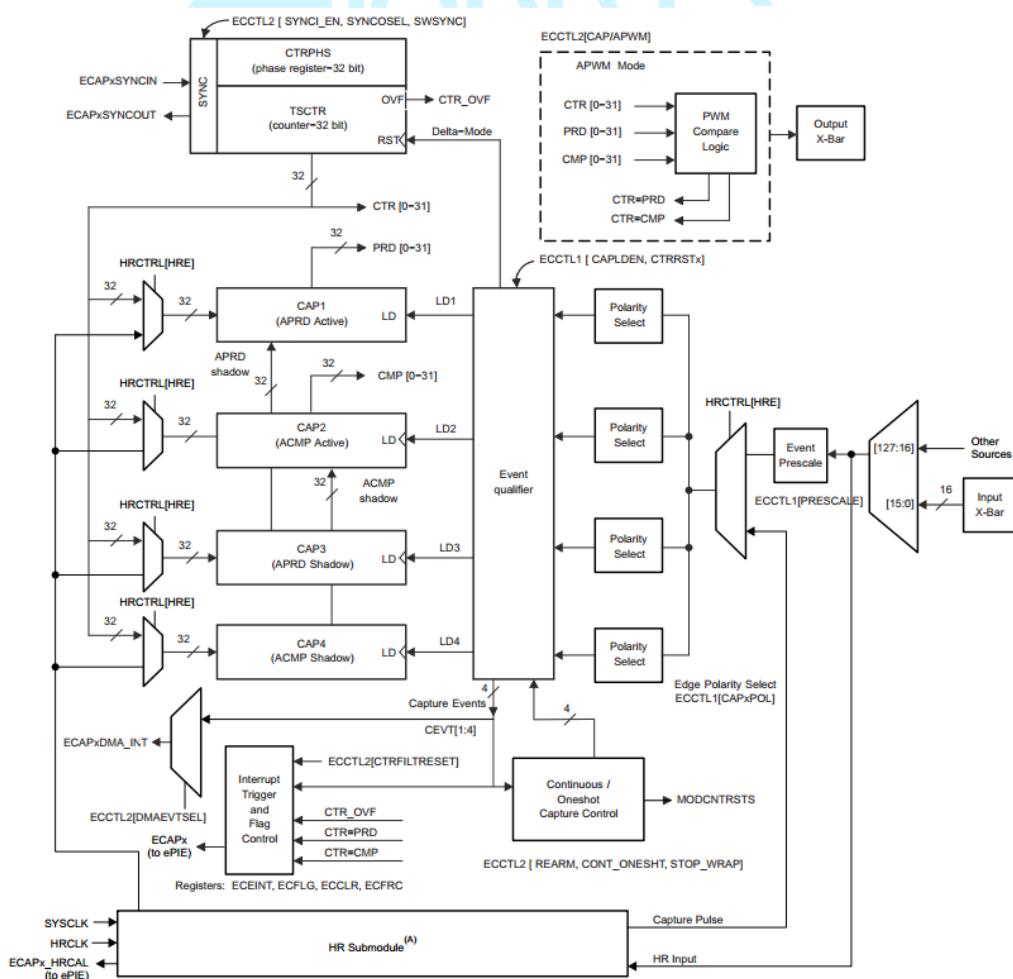

| 5.9.1 增强型捕获(eCAP) .....             | 95  |

| 5.9.1.1 eCAP电气数据和时序 .....           | 97  |

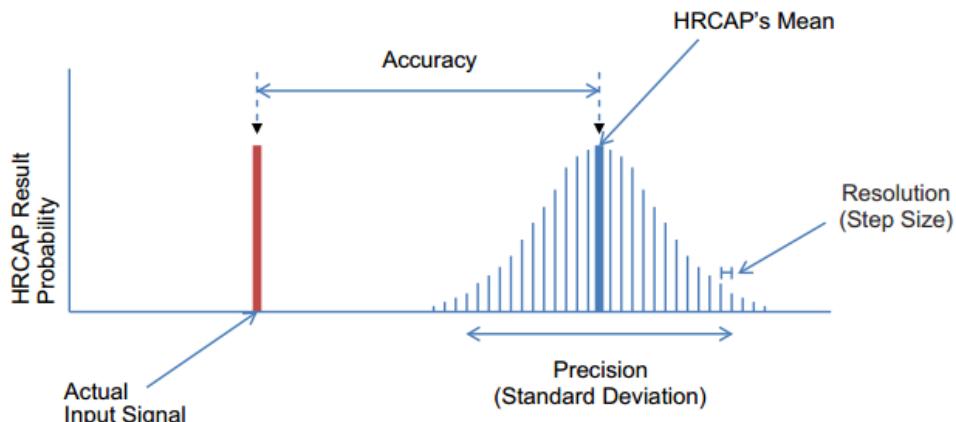

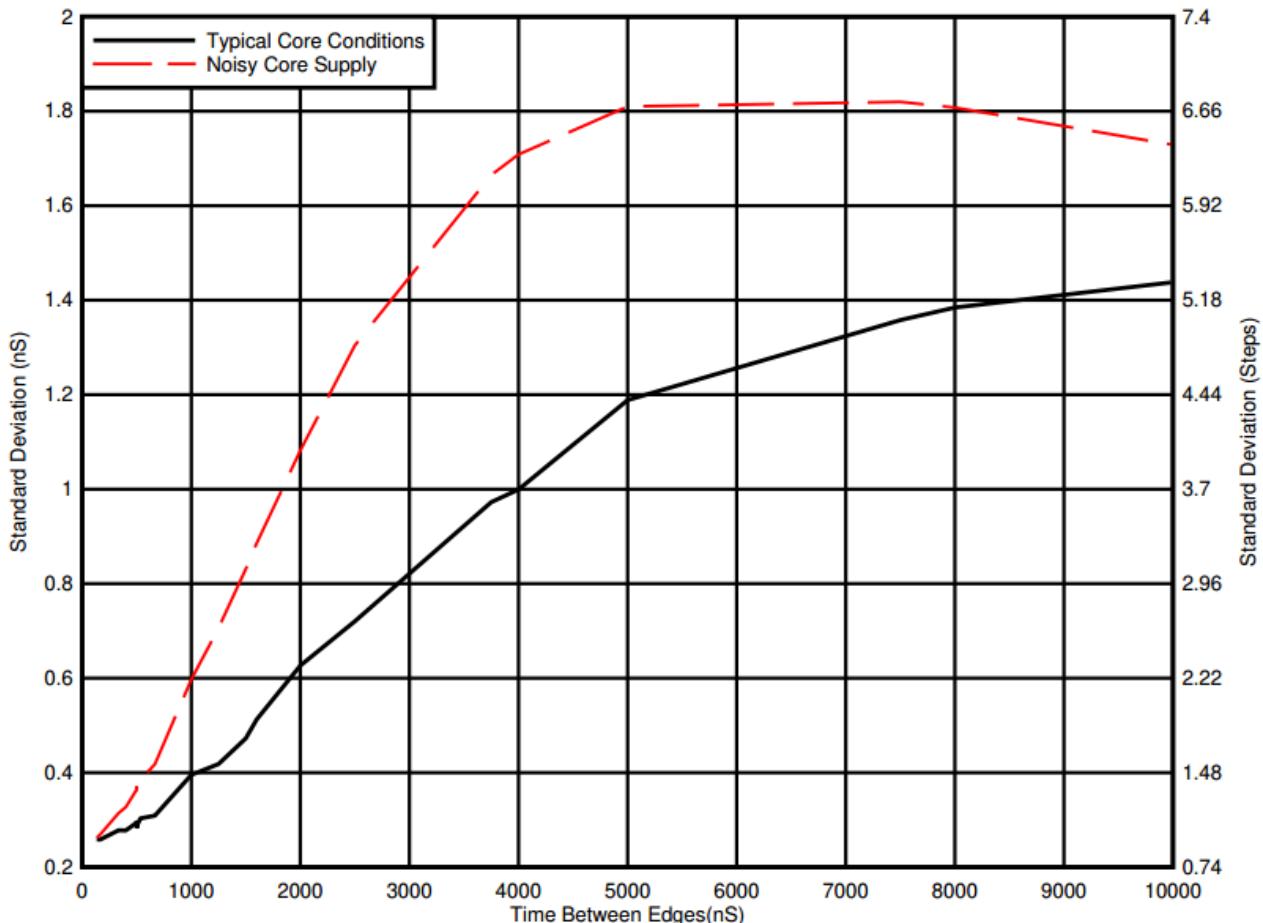

| 5.9.2 高分辨率捕捉子模块(HRCAP6–HRCAP7)..... | 98  |

| 5.9.2.1 HRCAP电气数据和时序 .....          | 101 |

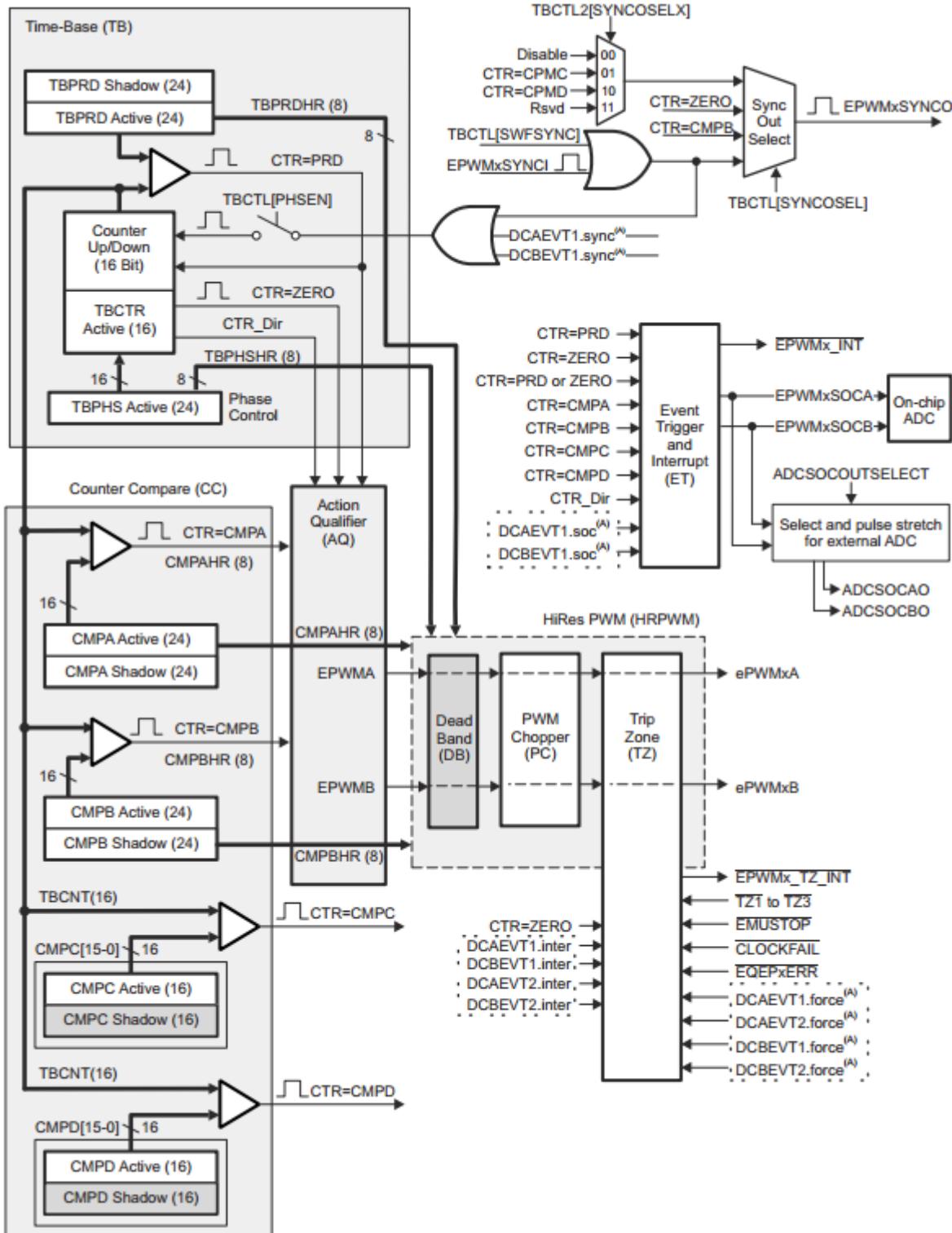

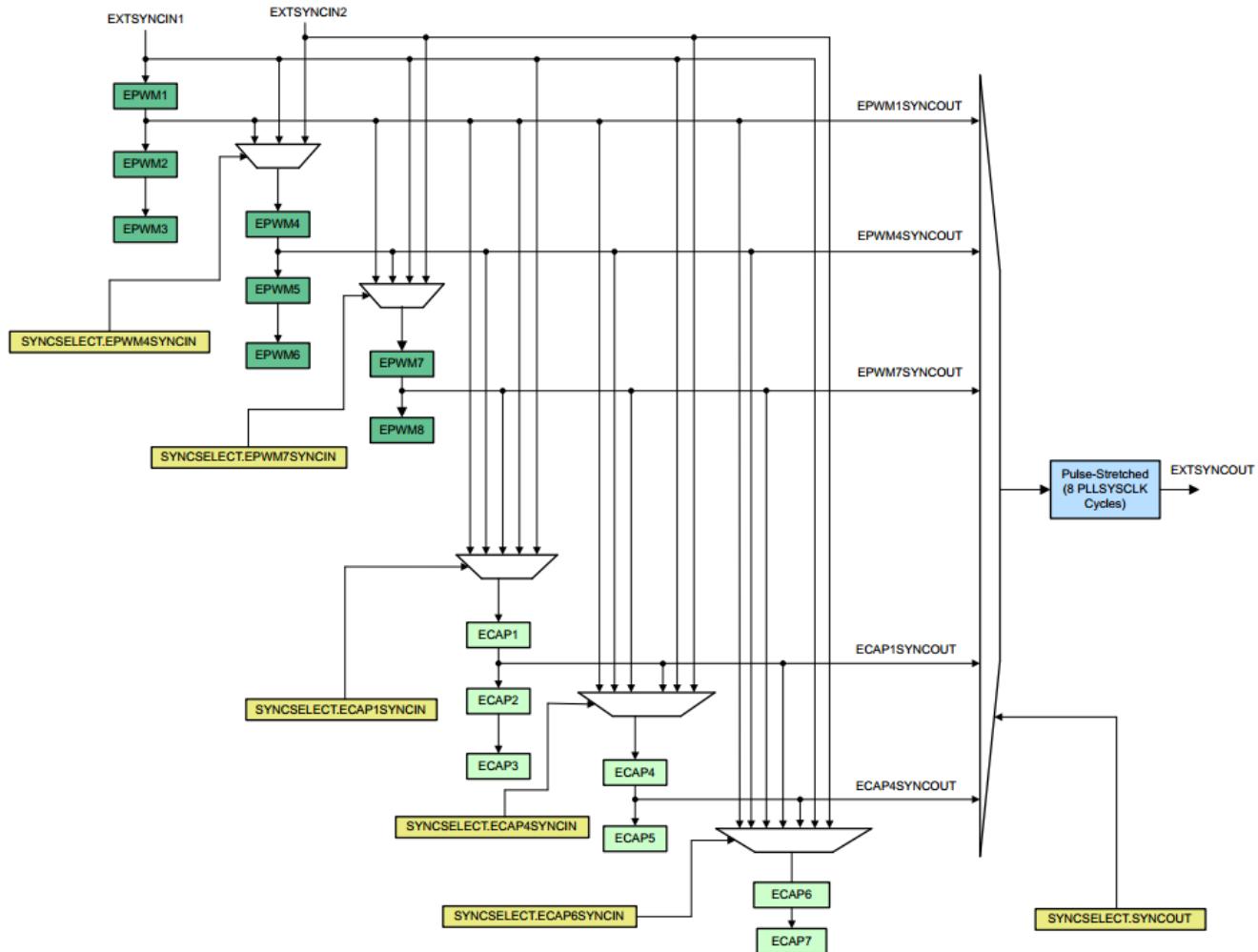

| 5.9.3 增强脉冲宽度调制(ePWM) .....          | 102 |

| 5.9.3.1 控制外设同步 .....                | 105 |

|                                            |     |

|--------------------------------------------|-----|

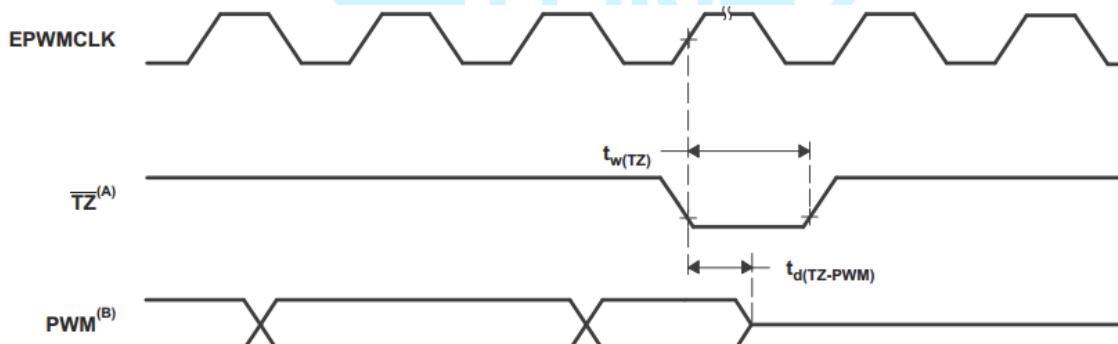

| 5.9.3.2 ePWM电气数据和时序 .....                  | 105 |

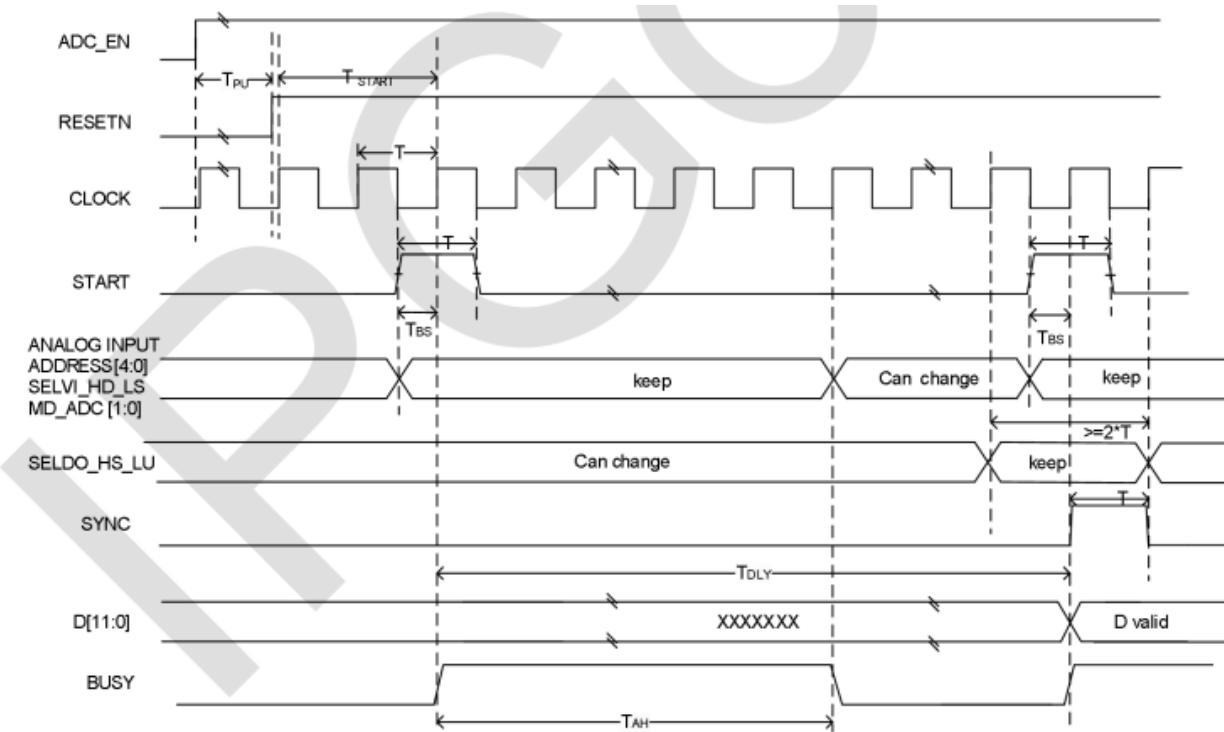

| 5.9.3.3 外部ADC转换脉冲开始的电气数据和时序 .....          | 107 |

| 5.9.4 高分辨率脉冲宽度调制器(HRPWM) .....             | 108 |

| 5.9.4.1 HRPWM 电气数据和时序 .....                | 108 |

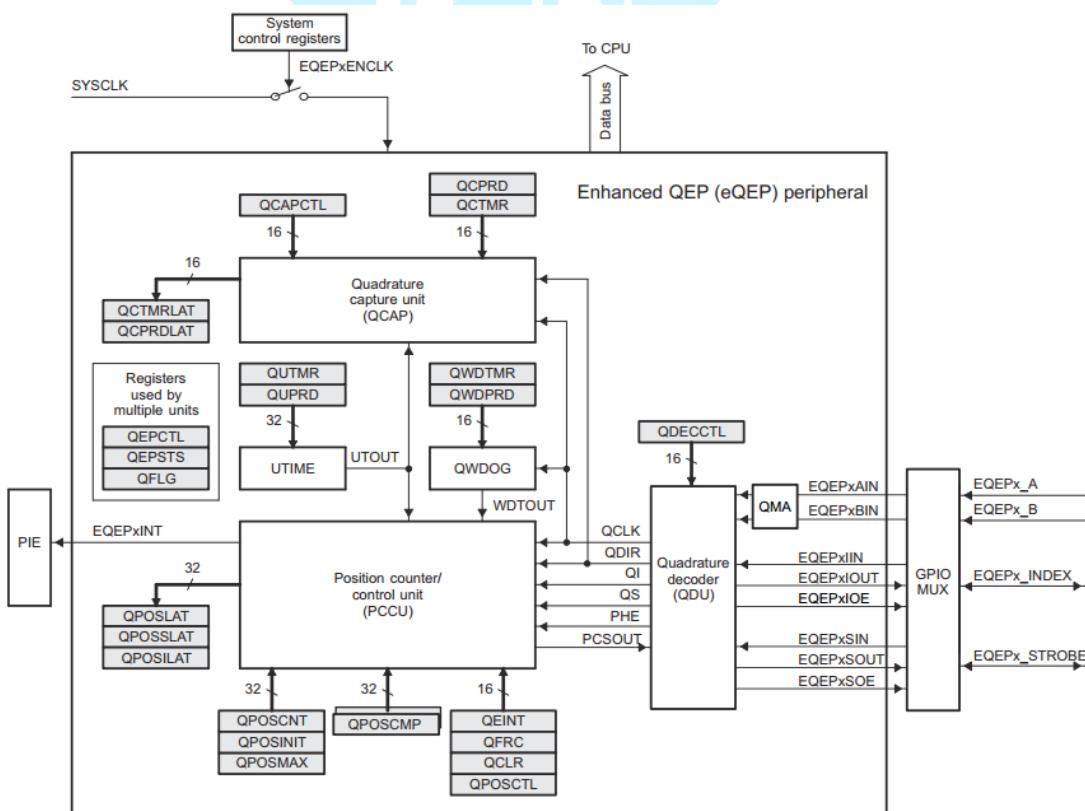

| 5.9.5 增强型正交编码器脉冲(eQEP) .....               | 109 |

| 5.9.5.1 eQEP电气数据和时序 .....                  | 109 |

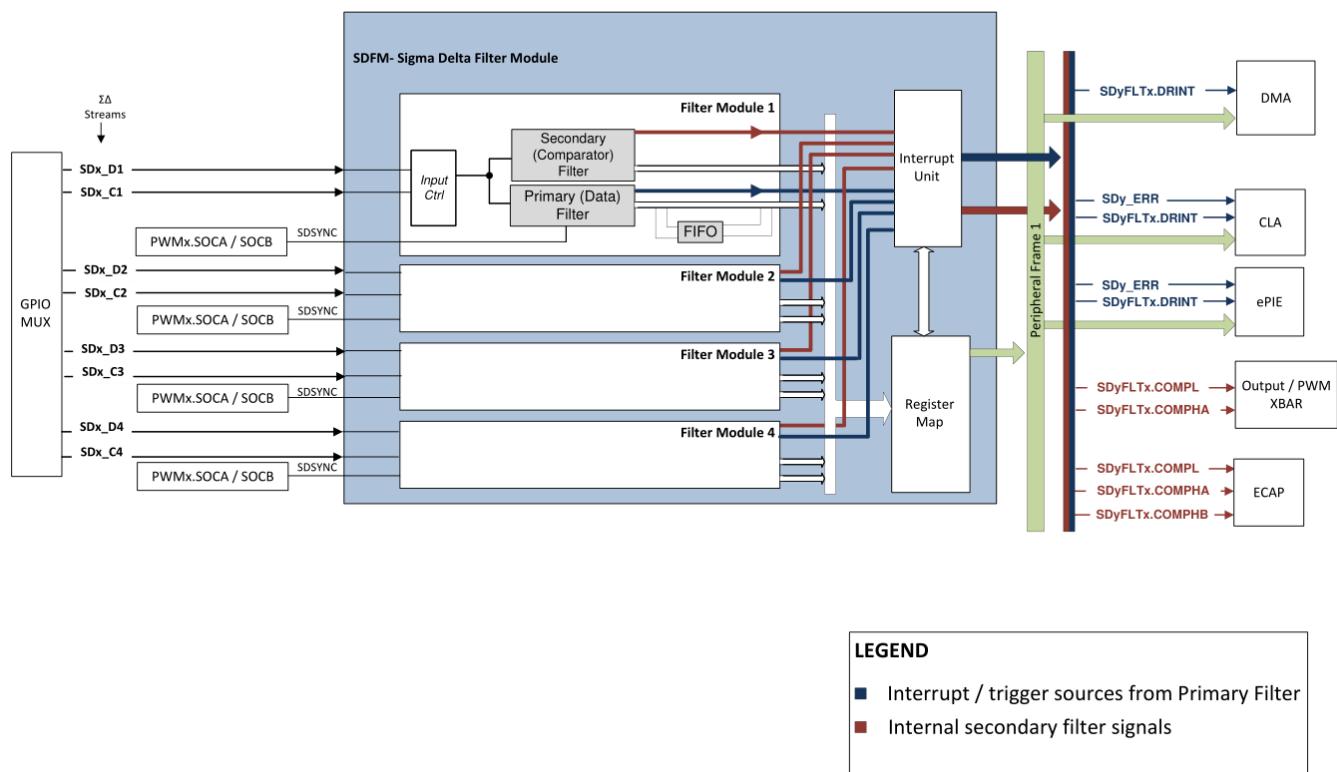

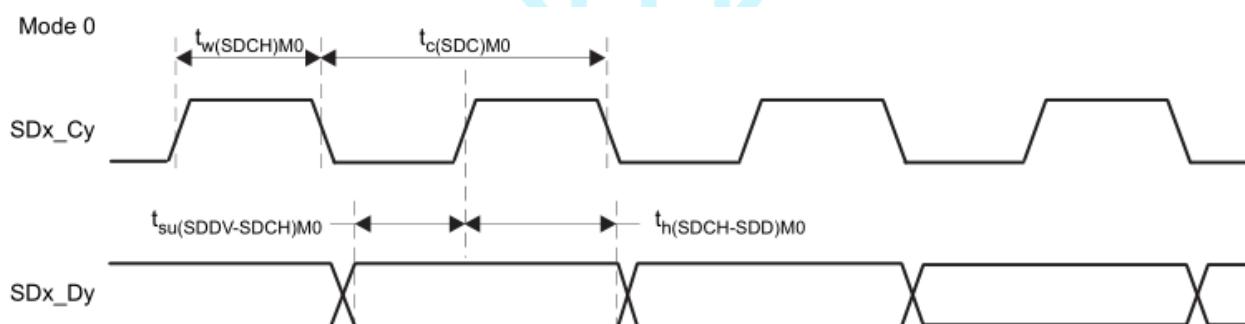

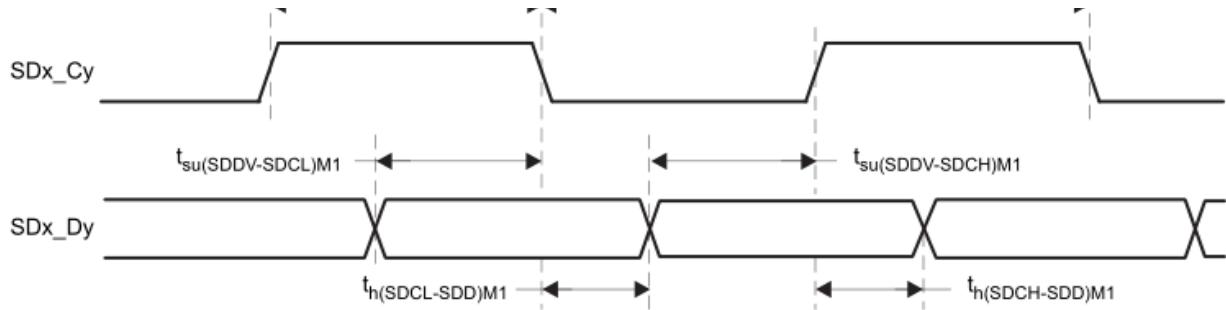

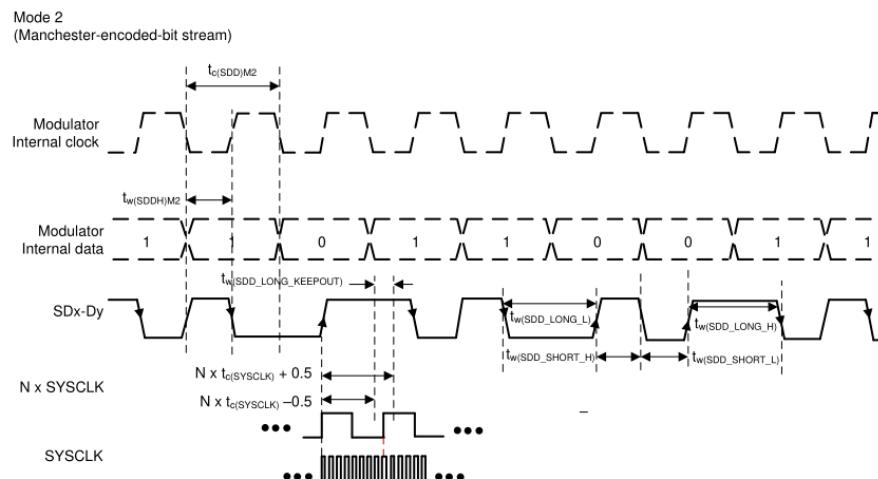

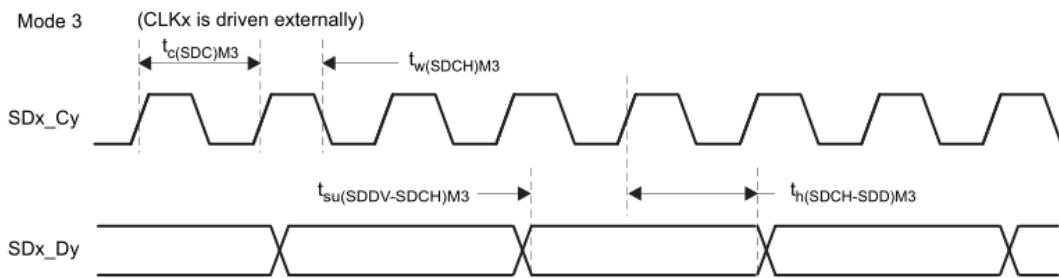

| 5.9.6 $\Sigma$ - $\Delta$ 滤波器模块(SDFM)..... | 111 |

| 5.9.6.1 SDFM电气数据和时序.....                   | 112 |

| 5.9.6.2 SDFM电气数据和时序 (同步GPIO) .....         | 115 |

| 5.9.6.2.1 使用同步GPIO(SYNC)选项时的SDFM时序要求.....  | 115 |

| 5.10 通信外设 .....                            | 118 |

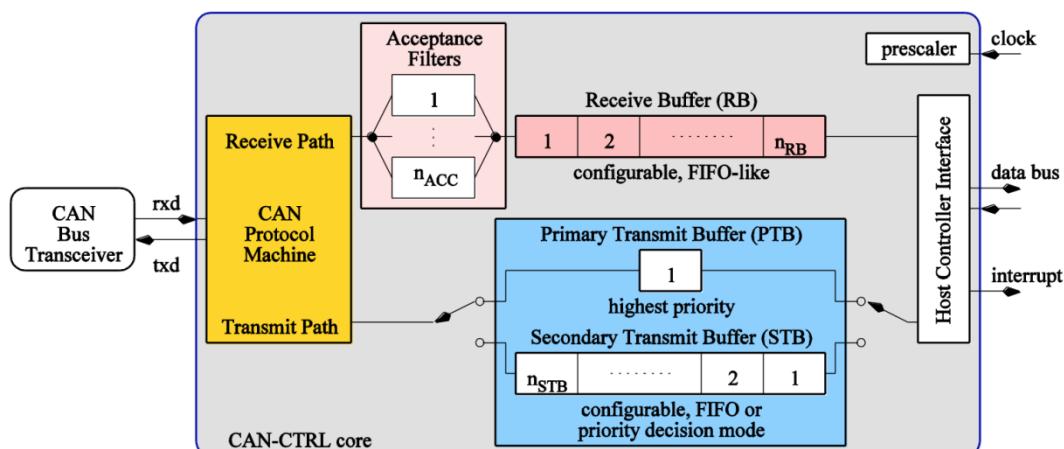

| 5.10.1 控制局域网络(CAN).....                    | 118 |

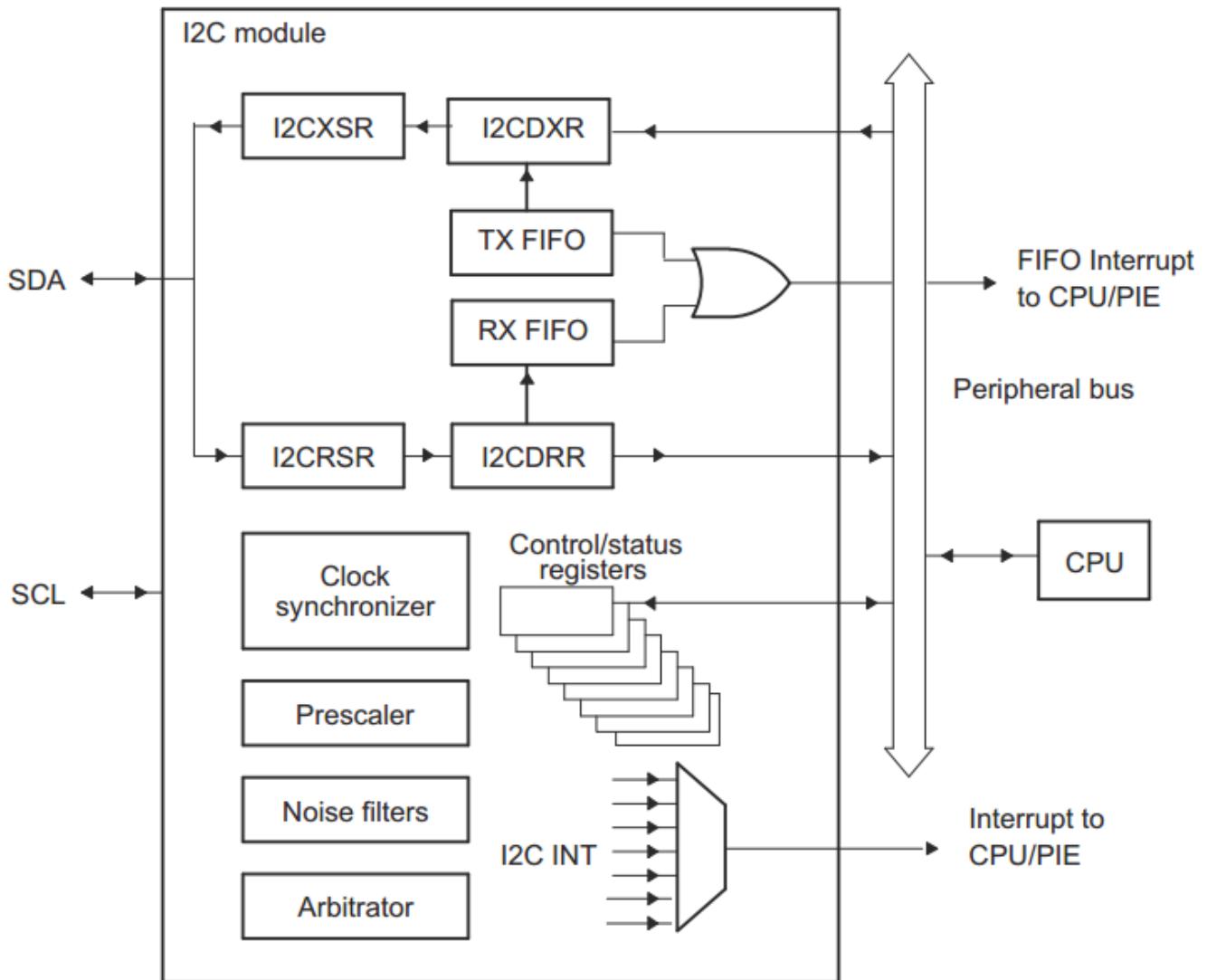

| 5.10.2 内置集成电路(I2C) .....                   | 120 |

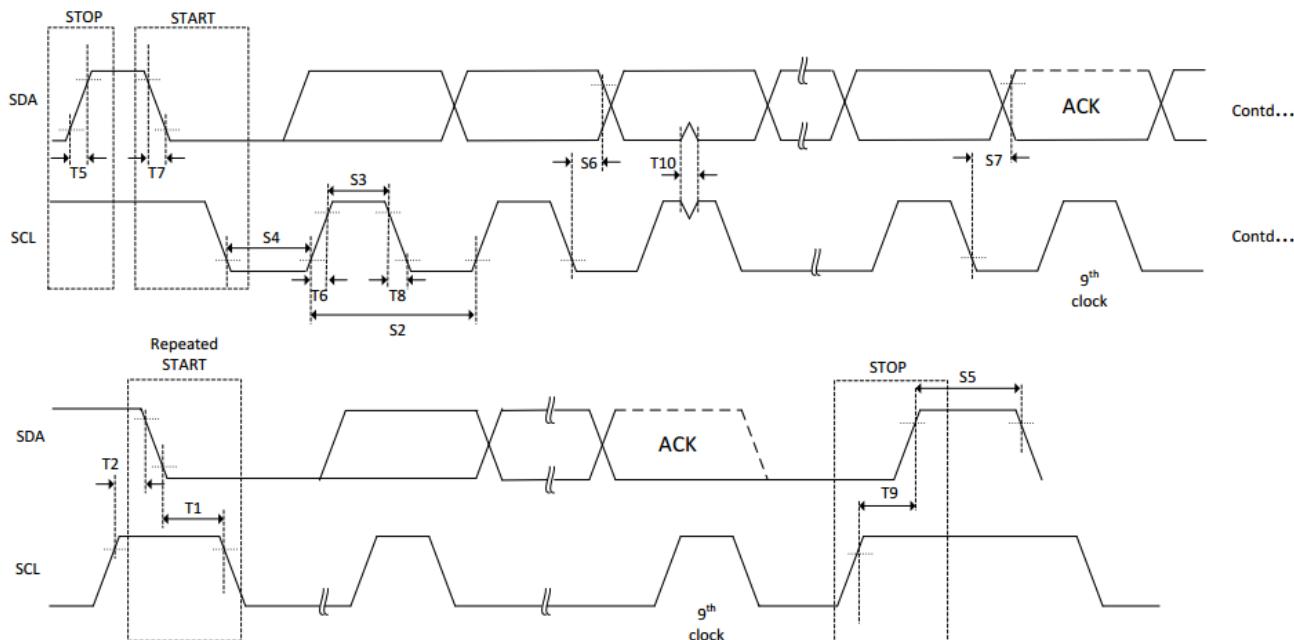

| 5.10.2.1 I2C电气数据和时序 .....                  | 122 |

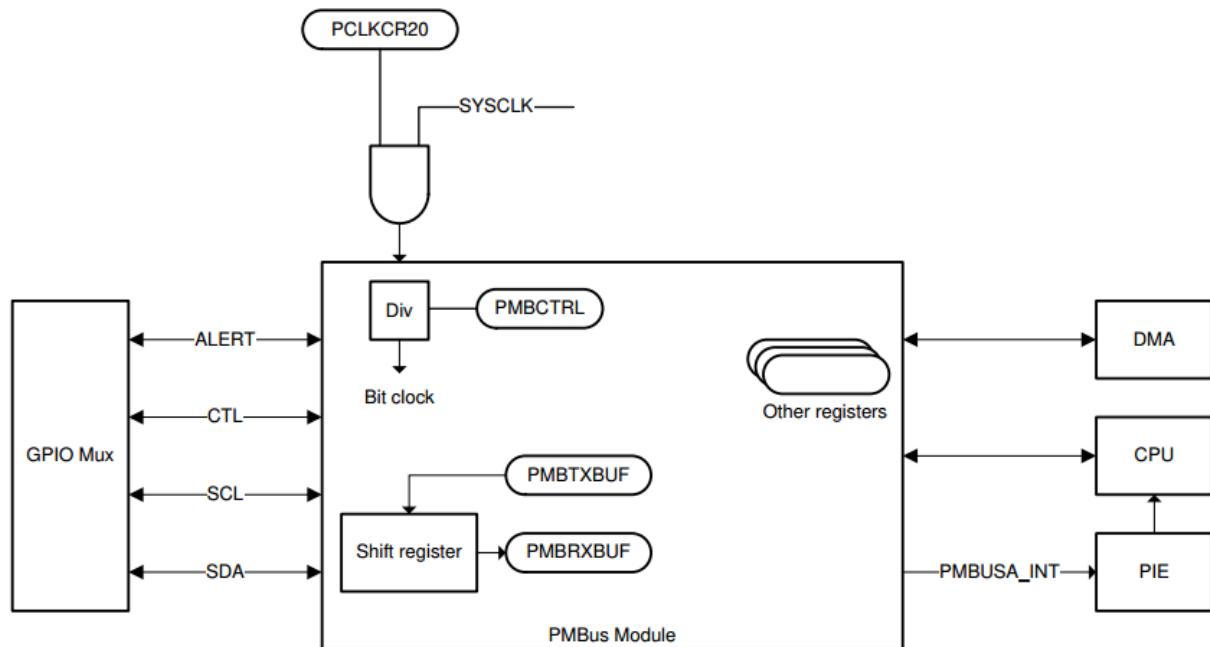

| 5.10.3 电源管理总线(PMBus)接口.....                | 125 |

| 5.10.3.1.1 PMBus 电气特性.....                 | 127 |

| 5.10.3.1.2 PMBus 快速模式的开关特性 .....           | 127 |

| 5.10.3.1.3 PMBus 标准模式的开关特性 .....           | 128 |

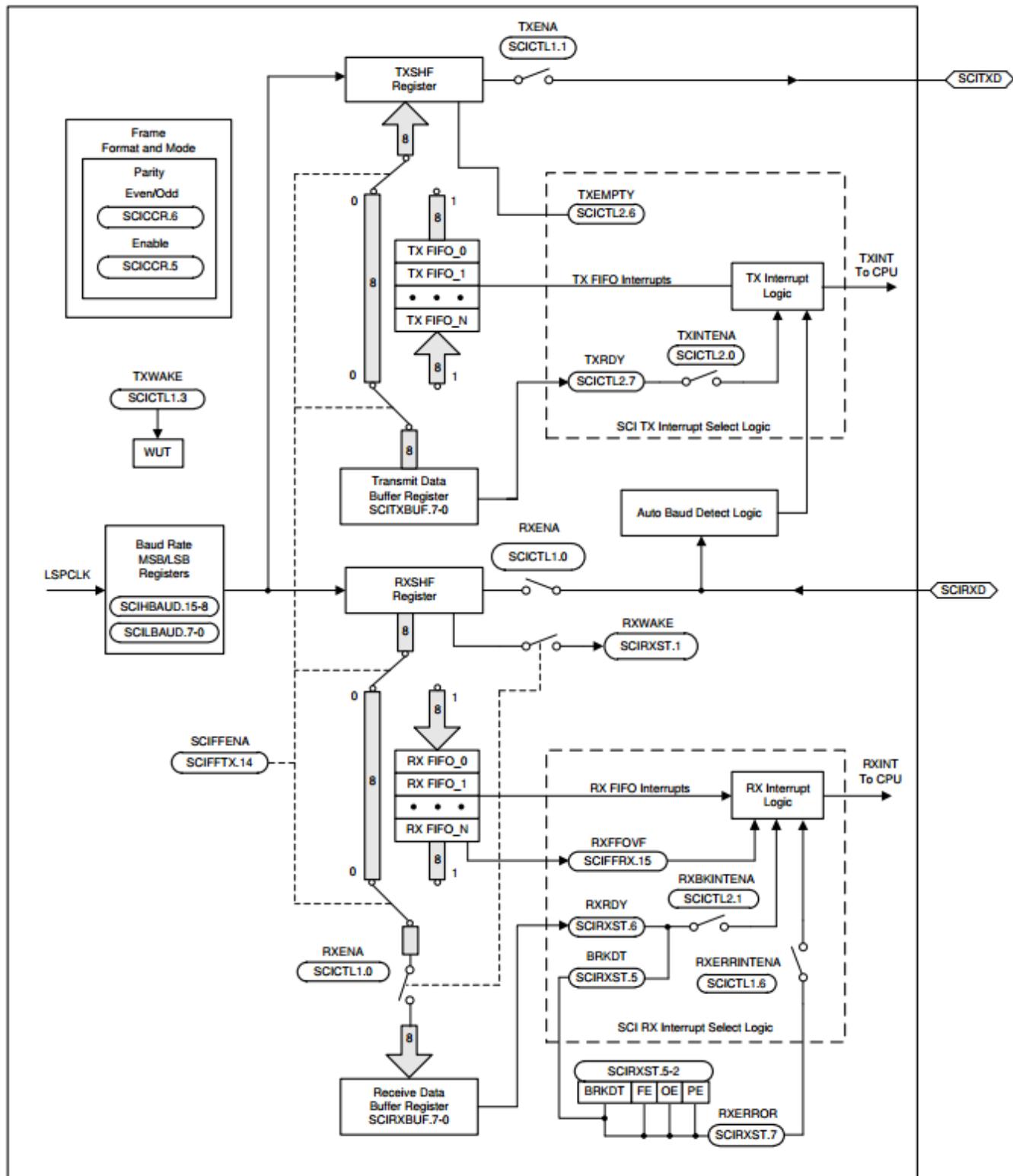

| 5.10.4 串行通信接口(SCI) .....                   | 129 |

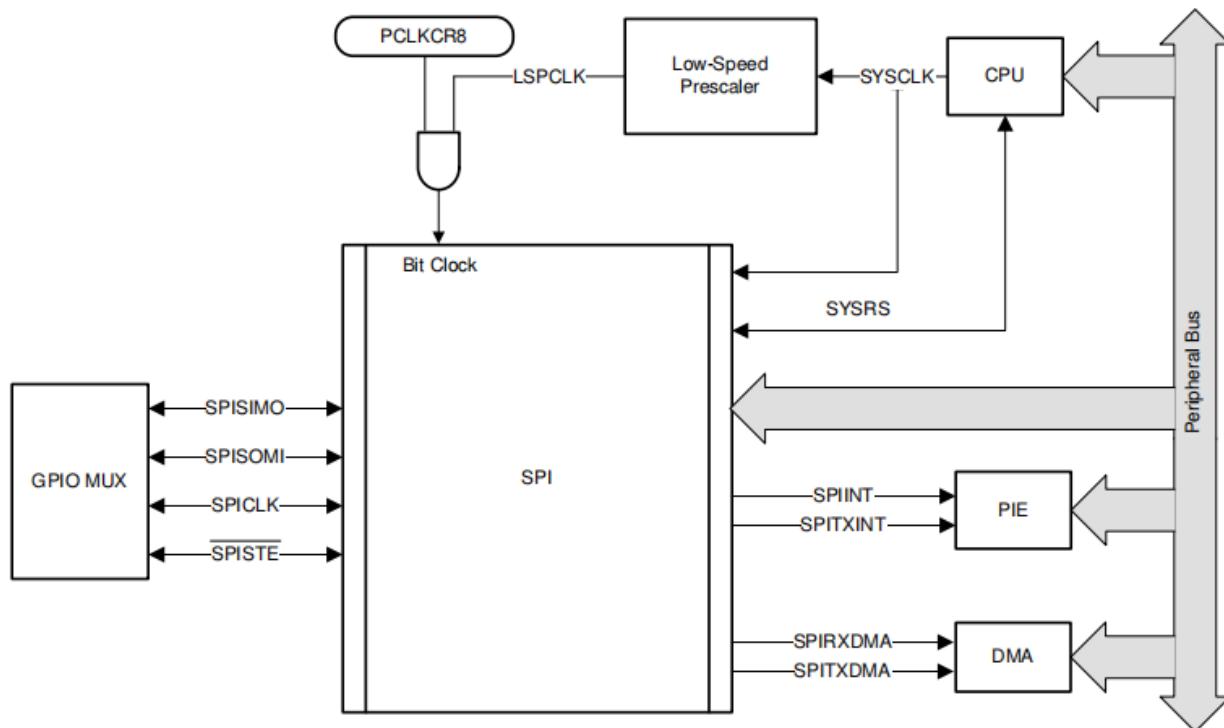

| 5.10.5 串行外设接口(SPI) .....                   | 132 |

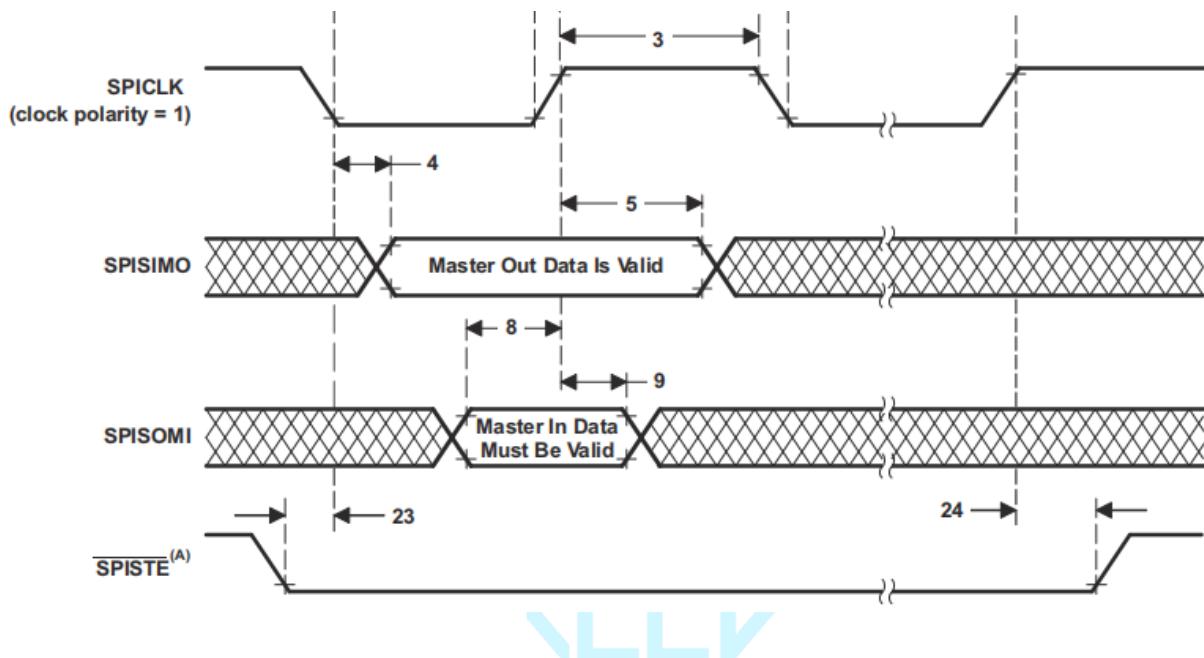

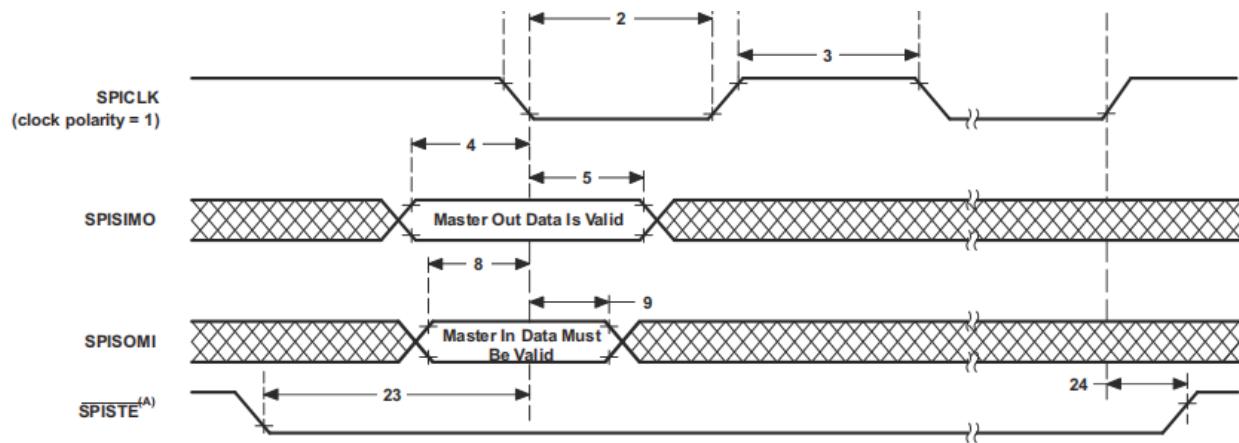

| 5.10.5.1 SPI 主模式时序 .....                   | 133 |

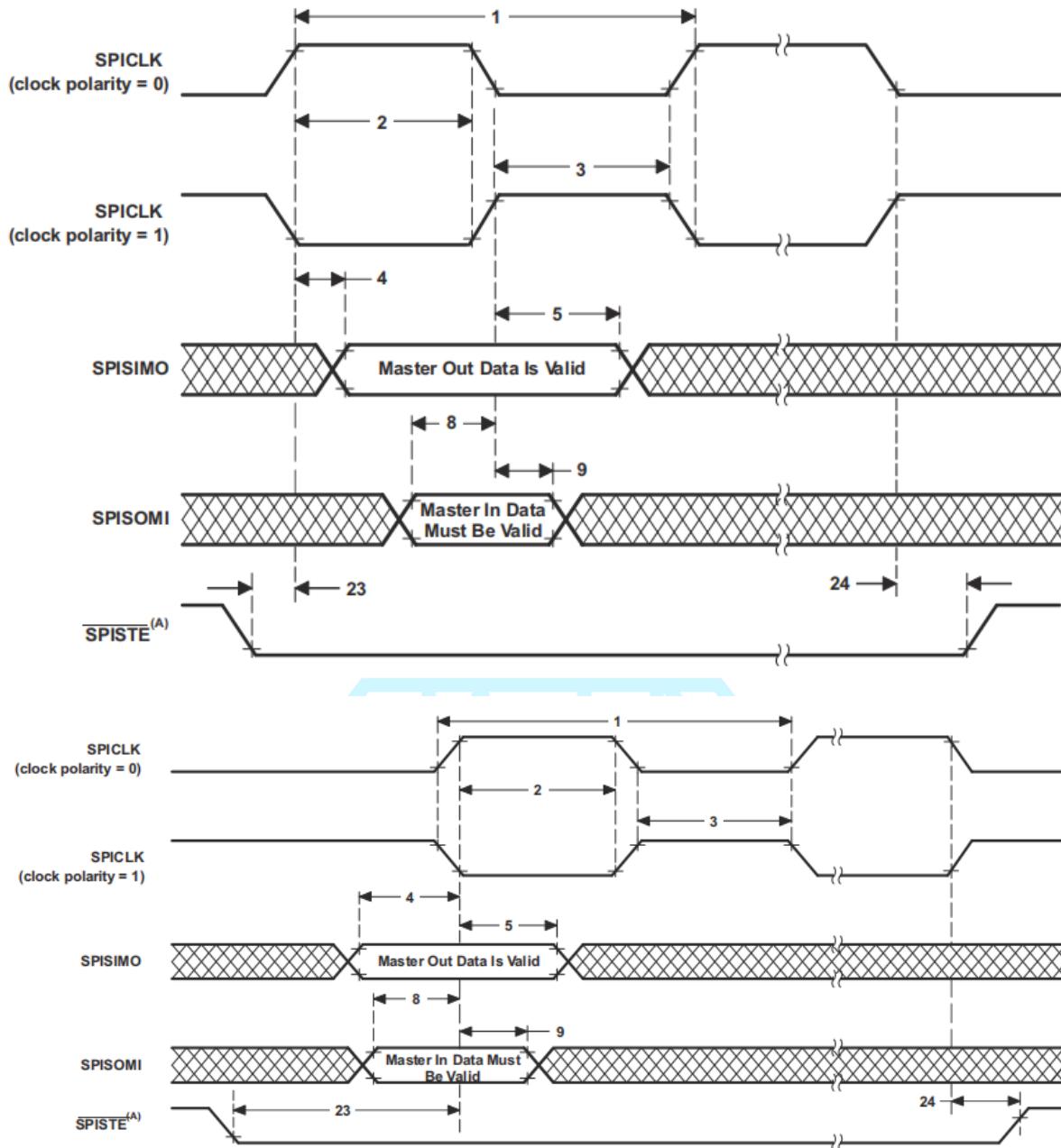

| 5.10.5.2 SPI从模式时序 .....                    | 137 |

| 5.10.5.2.1 SPI 从模式时序要求 .....               | 137 |

| 5.10.5.2.1 SPI 从模式开关特性 .....               | 138 |

| 5.10.5.2.2 SPI 从模式时序图 .....                | 138 |

| 5.10.6 本地互联网络(LIN).....                    | 139 |

| 5.11 系统 .....                              | 141 |

| 5.11.1 电源管理.....                           | 141 |

| 5.11.1.1 内部1.2 V LDO稳压器(VREG) .....        | 142 |

| 5.11.1.2 推荐的外部组件 .....                     | 142 |

|                                        |     |

|----------------------------------------|-----|

| 5.11.1.3 电源排序.....                     | 142 |

| 5.11.1.4 上电复位(POR) .....               | 143 |

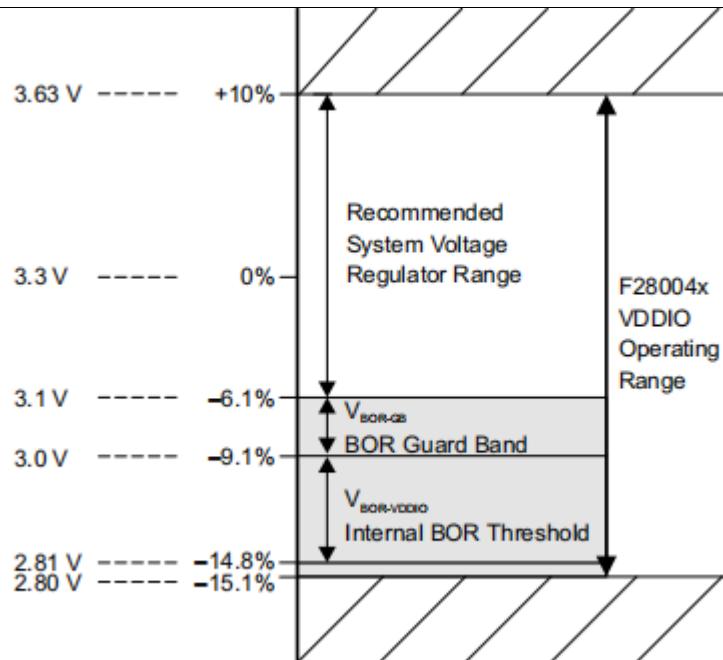

| 5.11.1.5 掉电复位(BOR) .....               | 143 |

| 5.11.2 时钟规范.....                       | 143 |

| 5.11.2.1 时钟资源.....                     | 143 |

| 5.11.2.2 时钟频率、要求和特性 .....              | 144 |

| 5.11.2.3 外部输入时钟 .....                  | 146 |

| 5.11.2.4 内部振荡器 .....                   | 147 |

| 5.11.3 仿真/JTAG.....                    | 148 |

| 6 详细描述 .....                           | 150 |

| 6.1 概述 .....                           | 150 |

| 6.2 功能框图 .....                         | 151 |

| 6.3 内存 .....                           | 152 |

| 6.3.1 内存映射 .....                       | 152 |

| 6.3.2 Flash 内存映射 .....                 | 158 |

| 6.3.2.1 Flash 扇区地址 .....               | 158 |

| 6.3.3.2 外设寄存器内存映射 .....                | 159 |

| 6.3.3 存储器类型 .....                      | 163 |

| 6.3.3.1 CPU共享数据 RAM (GSDx RAM) .....   | 163 |

| 6.3.3.2 IPC共享 RAM (IPC CPUx_RAM) ..... | 164 |

| 6.3.3.3 CPU共享指令RAM (GSIx RAM).....     | 164 |

| 6.3.3.4 CPU共享指令RAM (BOOT RAM) .....    | 164 |

| 6.4 总线架构-外设连接 .....                    | 164 |

| 6.6 C28x 处理器 .....                     | 166 |

| 6.6.1 介绍 .....                         | 166 |

| 6.6.2 特点 .....                         | 166 |

| 6.6.3 浮点单元(FPU) .....                  | 166 |

| 6.6.4 三角数学单元(TMU) .....                | 166 |

| 6.6.5 Viterbi、复数和循环冗余校验单元 (VCU) .....  | 167 |

| 6.6.5.1 Viterbi运算 .....                | 167 |

---

|                                          |     |

|------------------------------------------|-----|

| 6.6.5.2 循环冗余校验 (CRC) .....               | 167 |

| 6.6.5.3 复数运算.....                        | 168 |

| 6.6.6 增强型整数除法单元 (EINTDIV) .....          | 168 |

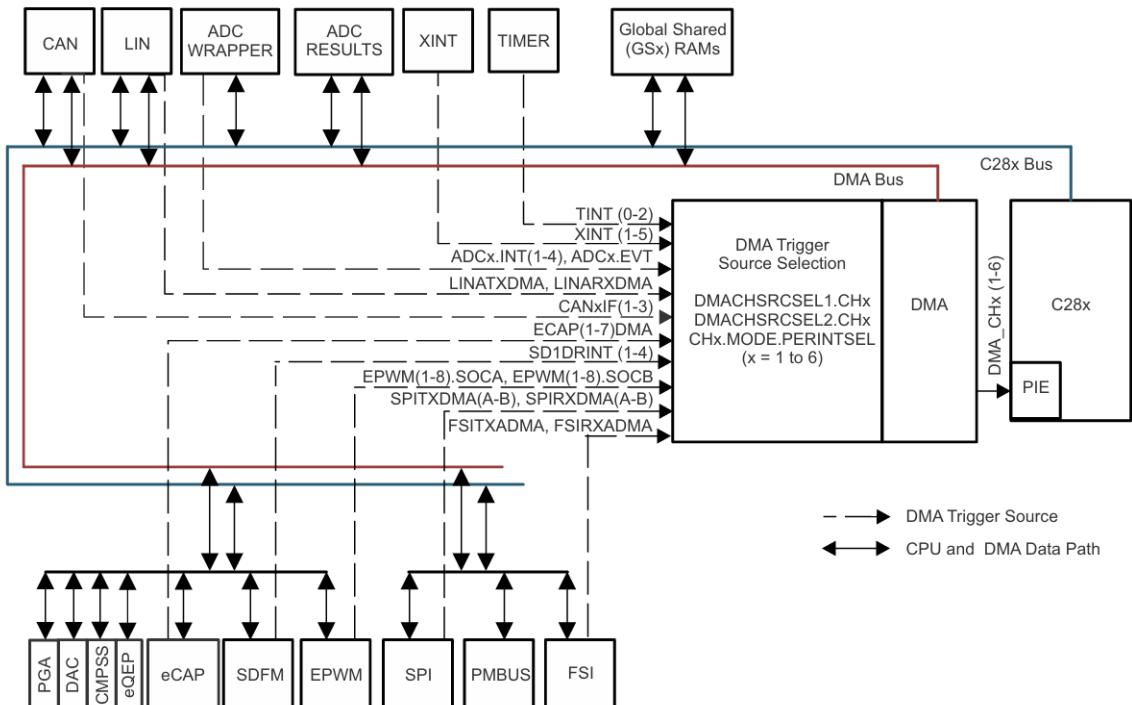

| 6.7 直接内存访问(DMA) .....                    | 169 |

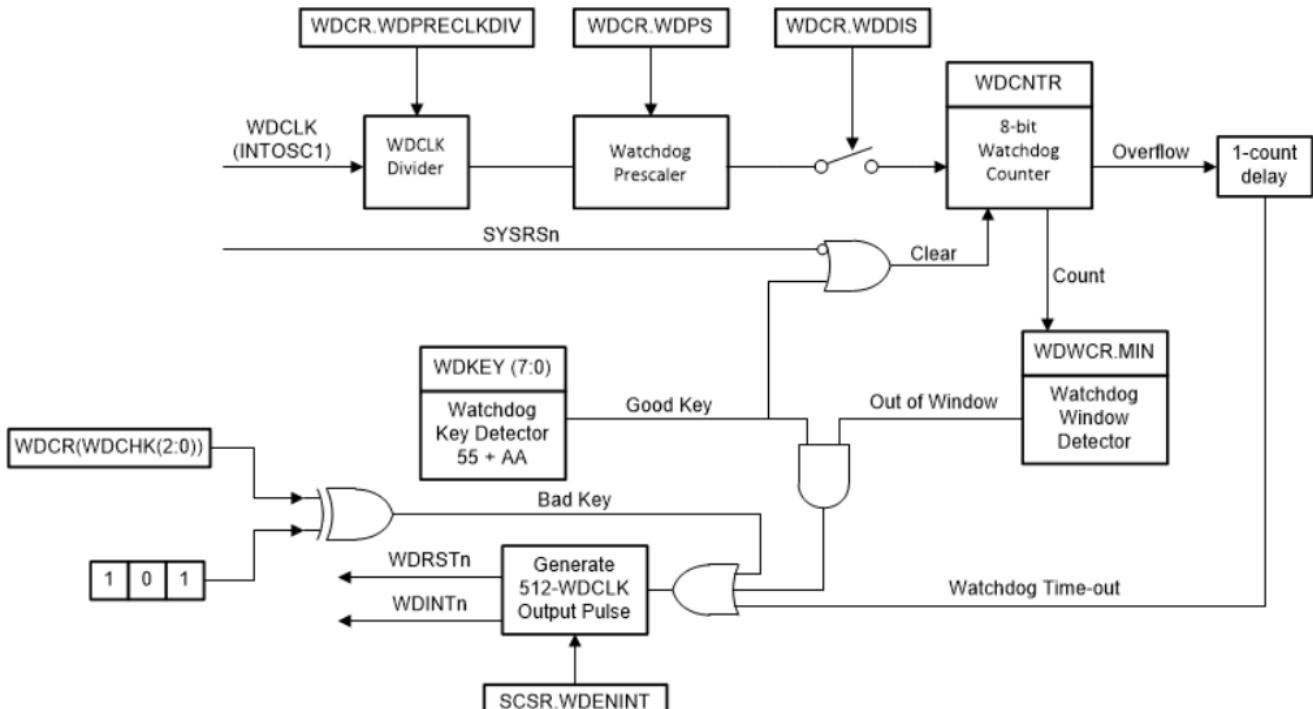

| 6.8 看门狗 .....                            | 171 |

| 6.9 C28x 计时器 .....                       | 171 |

| 6.10 双时钟比较器 (DCC).....                   | 172 |

| 6.10.1 特点.....                           | 172 |

| 6.10.2 DCCx(DCC0 and DCC1) 时钟源输入映射 ..... | 172 |

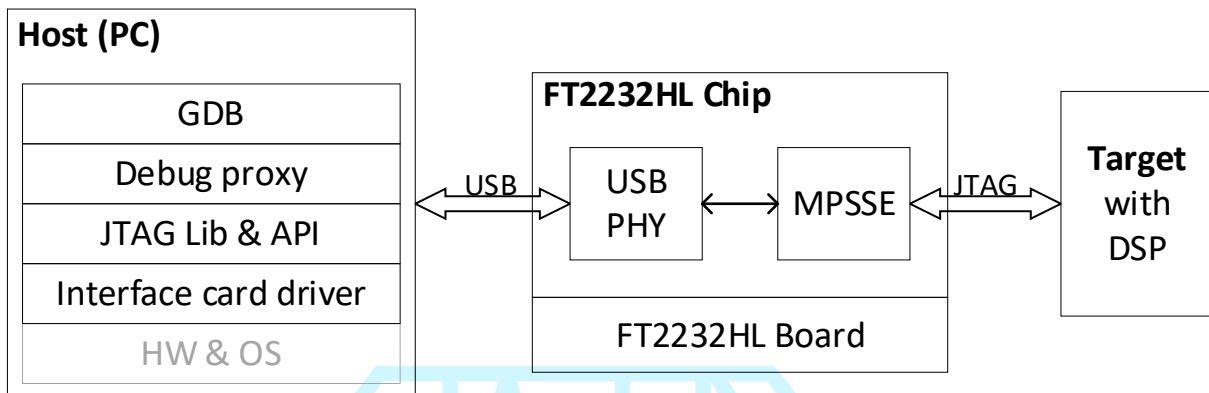

| 7 开发支持 .....                             | 173 |

| 7.1 集成开发环境QX-IDE .....                   | 173 |

| 7.2 仿真器 .....                            | 174 |

| 7.2.1 简介 .....                           | 174 |

| 7.2.2 结构 .....                           | 174 |

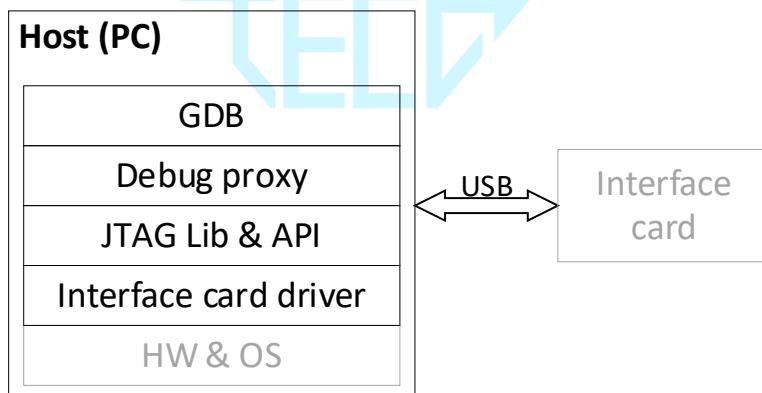

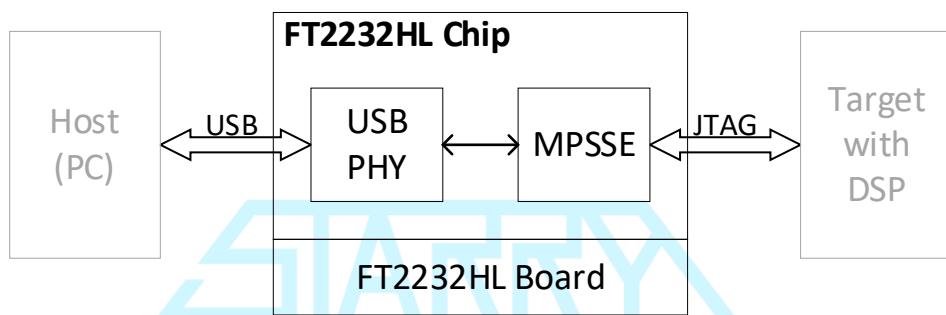

| 7.2.2.1 宿主机 .....                        | 174 |

| 7.2.2.2 目标机 .....                        | 175 |

| 7.2.2.3 接口卡 .....                        | 175 |

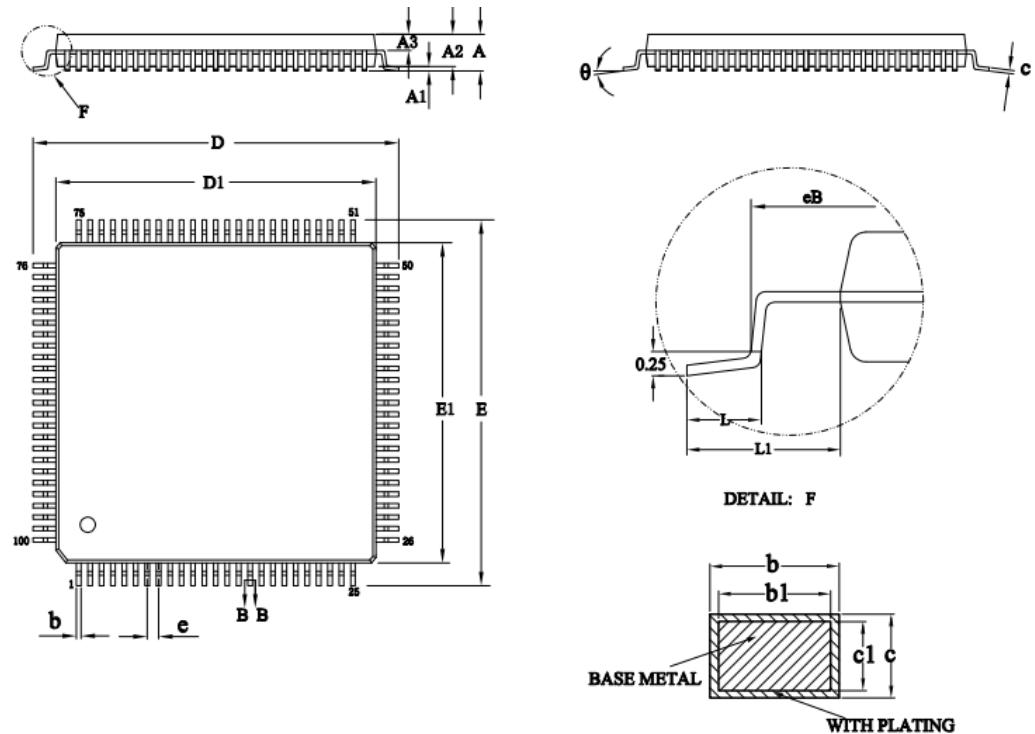

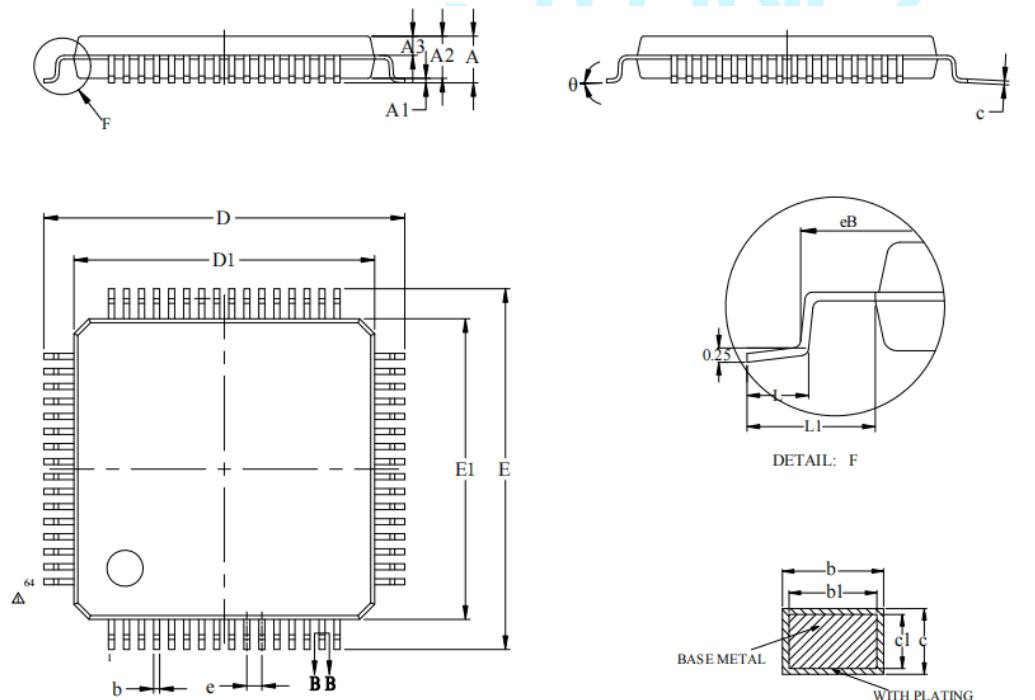

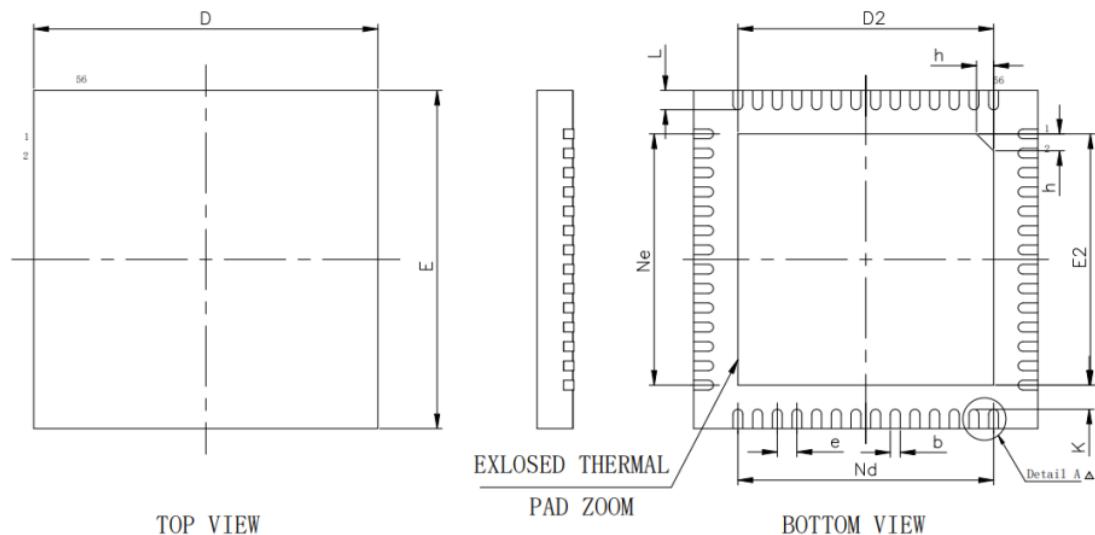

| 8 封装外形尺寸 .....                           | 176 |

| 8.1 LQFP100 PIN.....                     | 176 |

| 8.2 LQFP64 PIN.....                      | 176 |

| 8.3 VQFN56 PIN.....                      | 177 |

| 9 订货信息 .....                             | 178 |

| 9.1 封装信息.....                            | 178 |

| 9.2 封装概览 .....                           | 178 |

| 关于乾芯科技.....                              | 179 |

## 1 特性

- 32位双核CPU

- 160 MHz

- IEEE-754 单精度浮点单元 (FPU)

- 三角函数加速器 (TMU)

- Viterbi/复杂数学单元 (VCU-I)

- 片上存储器

- 1MB FLASH (ECC 保护)

- 1MB SRAM (ECC保护/奇偶校验保护)

- 1MB 指令RAM, 512KB 数据RAM

- 时钟和控制

- 两个内部零引脚 10MHz 振荡器

- 片上晶振振荡器和外部时钟输入

- 片上 10MHz 振荡器

- 外部晶振频率最高支持 20MHz

- 看门狗计时器模块

- 丢失时钟检测电路

- 电源电压: 1.2V 内核、3.3V I/O

- 可生成 1.2V 电压的内部 VREG

- 欠压复位 (BOR) 电路

- 系统外设

- 6通道直接存储器存取 (DMA) 控制器

- 40个独立可编程多路复用GPIO引脚

- 在模拟引脚上提供21路数字输入

- 增强型外设中断扩展 (ePIE) 模块

- 持多个具有外部唤醒功能的低功耗模式 (LPM)

- 嵌入式实时分析和诊断 (ERAD)

- 通信外设

- 1个电源管理总线 (PMBus) 接口

- 1个内部集成电路 (I2C) 接口

- 2个控制器局域网 (CAN) 总线端口

- 2个串行外设接口 (SPI) 端口支持QSPI

- 2个与UART兼容的串行通信接口 (SCI)

- 1个可兼容UART的本地互联网络 (LIN)

- 模拟系统

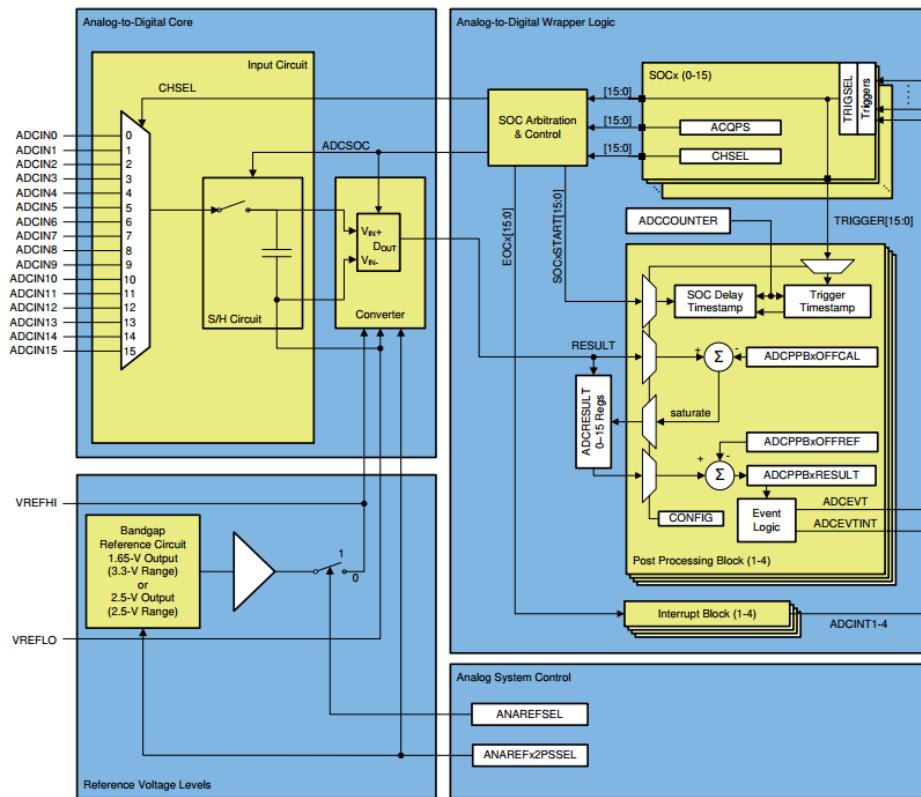

- 3个 3MSPS 12位模数转换器 (ADC)

- 多达21个外部通道

- 每个ADC集成4个后处理模块 (PPB)

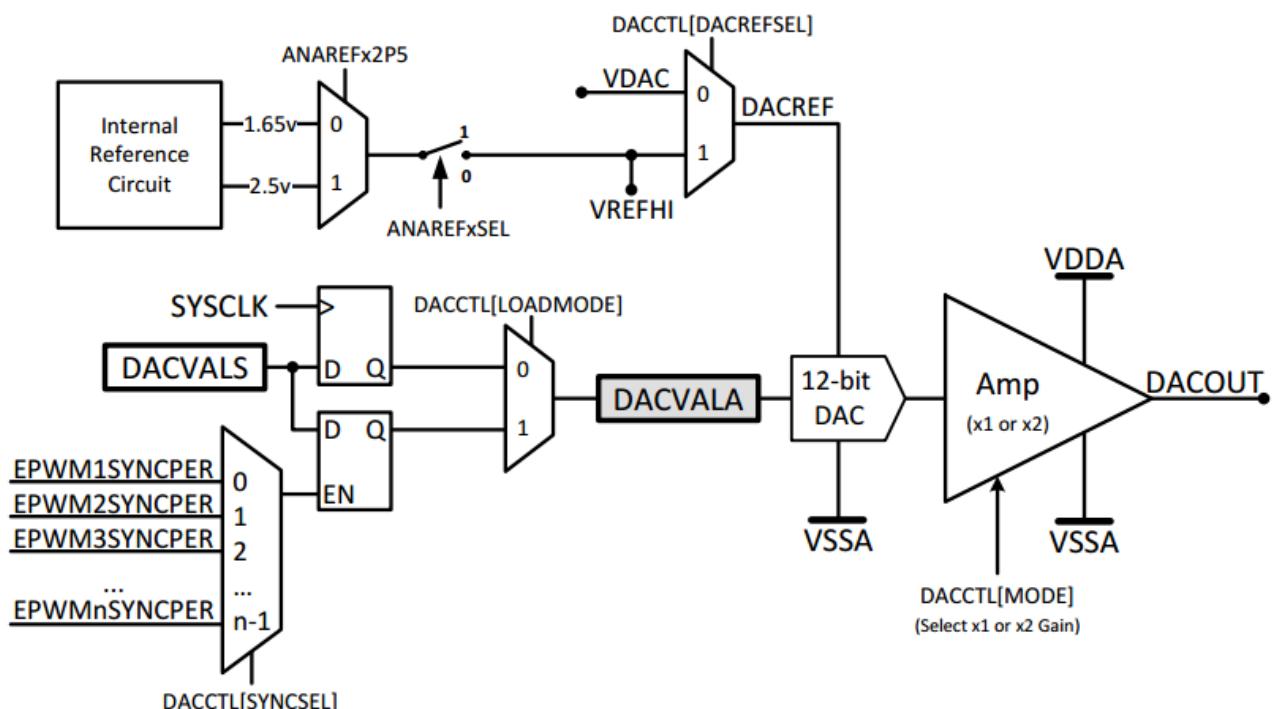

- 2个12位缓冲数模转换器 (DAC)

- 7个带12位参考数模转换器 (DAC) 的窗口比较器 (CMPSS)

- 数字干扰滤波器

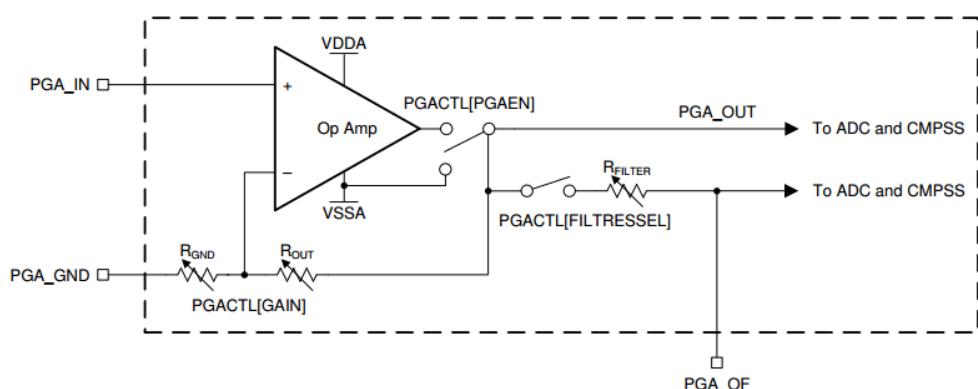

- 7个可编程增益放大器 (PGA)

- 可编程增益设置

- 可编程输出滤波

- 增强型控制外设

- 16个具有增强特性的ePWM通道

- 16个高分辨率 (110ps) HRPWM通道

- 具有高分辨率的集成死区支持

- 具有硬件跳闸区域 (TZ)

- 7个增强型捕捉 (eCAP) 模块

- 2个增强型捕捉模块 (HRCAP)

- 2个CW/CCW运行模式的增强型正交编码器脉冲 (eQEP) 模块

- 4条Σ-Δ滤波器模块 (SDFM) 输入通道

- QXFast-FOC

- 无传感器的磁场定向控制 (FOC)

- 封装

- 100 引脚LQFP

- 64 引脚LQFP

- 56 引脚VQFN

- 温度

- -40°C 至 125°C 结温

## 2 应用

- 交流充电桩

- 直流充电桩

- 电动汽车充电站电源模块

- 车辆无线充电模块

- 能量存储电源转换系统（PCS）

- 中央逆变器

- 太阳能电源优化器

- 串式逆变器

- 直流/交流转换器

- 逆变器和电机控制

- 伺服驱动器控制模块

- 交流BLDC电机驱动器

- 直流BLDC电机驱动器

- 工业交流/直流电源

- 三相UPS

- 商用网络和服务器PSU

- 商用通信电源整流器

### 3 说明

QXS320F280049RevB是一款对标TI公司的TMS320F28004x系列的32位处理器。主要针对实时控制应用（如工业电机驱动、光伏逆变器和数字电源、电动汽车的电机控制以及空调变频等）。

QXS320F280049RevB拥有对标TI C28x的自主研发的32位CPU内核，可提供160MHz的处理能力。QXS320F280049RevB内部同样集成了FPU，TMU和VCU扩展指令集，FPU可以提供32位浮点加速指令，TMU可快速执行包含变换和扭矩环路计算中常见三角运算的算法，VCU扩展指令集能够降低编码应用中常见复杂数学运算的延迟。

QXS320F280049RevB采用双核架构，CPU0和CPU1可独立并行运行，也可以相互通信。每个核都具有其独立的存储资源，都可以独立访问典型控制系统中所需的主要外设。双核之间可以通过中断，特殊寄存器和共享内存三种方式通信。

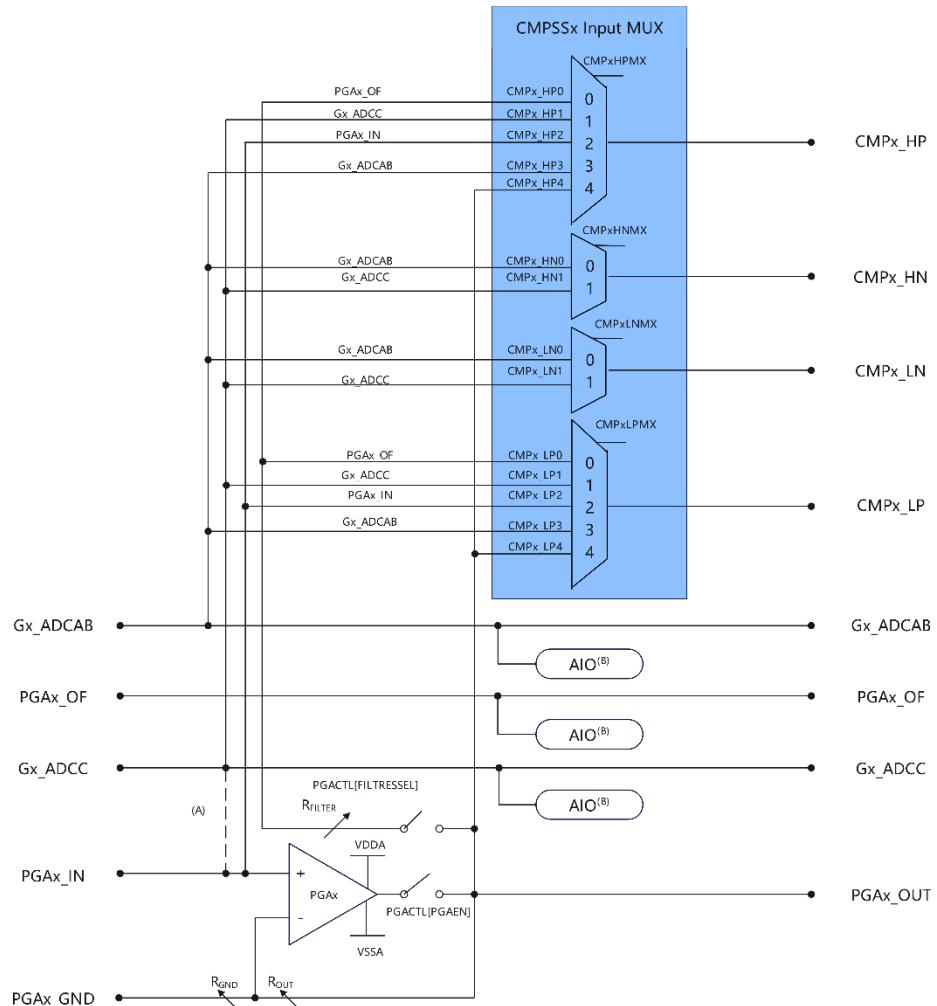

QXS320F280049RevB还集成了高性能模拟外设和增强型控制外设，三个独立的12位采样率为3MSPS的常规ADC可准确、高效地管理多个模拟信号，从而最终提高系统吞吐量。模拟前端上的七个PGA可以在转换之前实现片上电压调节。七个模拟比较器模块可以针对跳闸情况对输入电压电平进行持续监控。先进的控制外设（具有独立于频率的 ePWM/HRPWM 和 eCAP），可对系统进行出色的控制。内置的 4 通道 SDFM 允许在隔离层上无缝集成过采样  $\Sigma - \Delta$  调制器。

通过各种业界通用通信端口（如 SPI、SCI、I2C、LIN 和 CAN2.0，CAN FD）支持连接，并且提供了多个多路复用选项，可在各种应用中实现出色的信号布局。QXS320F280049RevB同时支持 PMBus。

嵌入式实时分析和诊断（ERAD）模块通过提供用于分析的附加硬件断点和计数器来增强器件的调试和系统分析功能。

QXS320F280049RevB支持高达512KB可配置的指令RAM或数据RAM以及额外的512KB指令RAM和1MB Flash存储，能够适应大部分嵌入场景。QXS320F280049RevB还支持8KB的bootloader指令RAM，灵活配置启动过程。

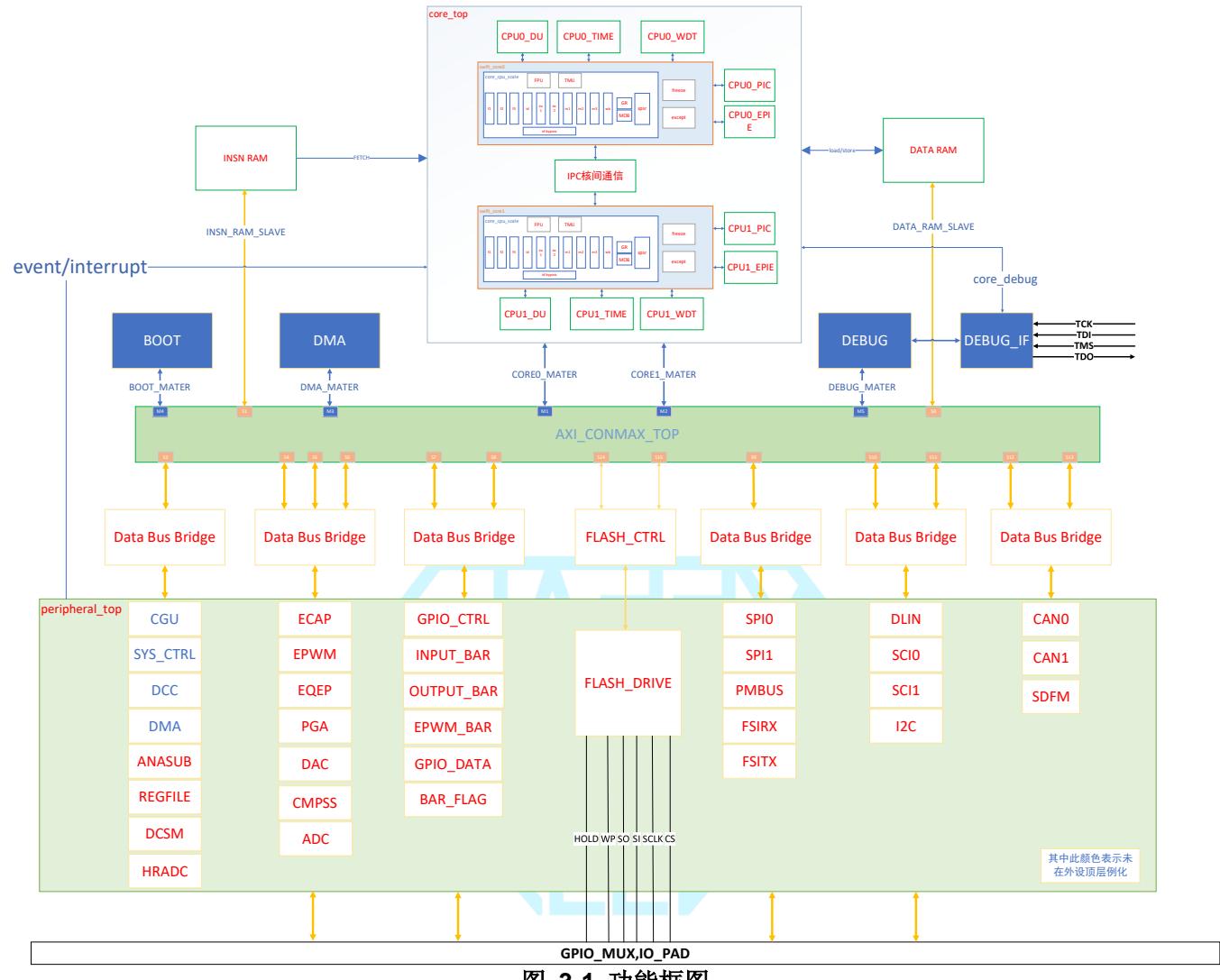

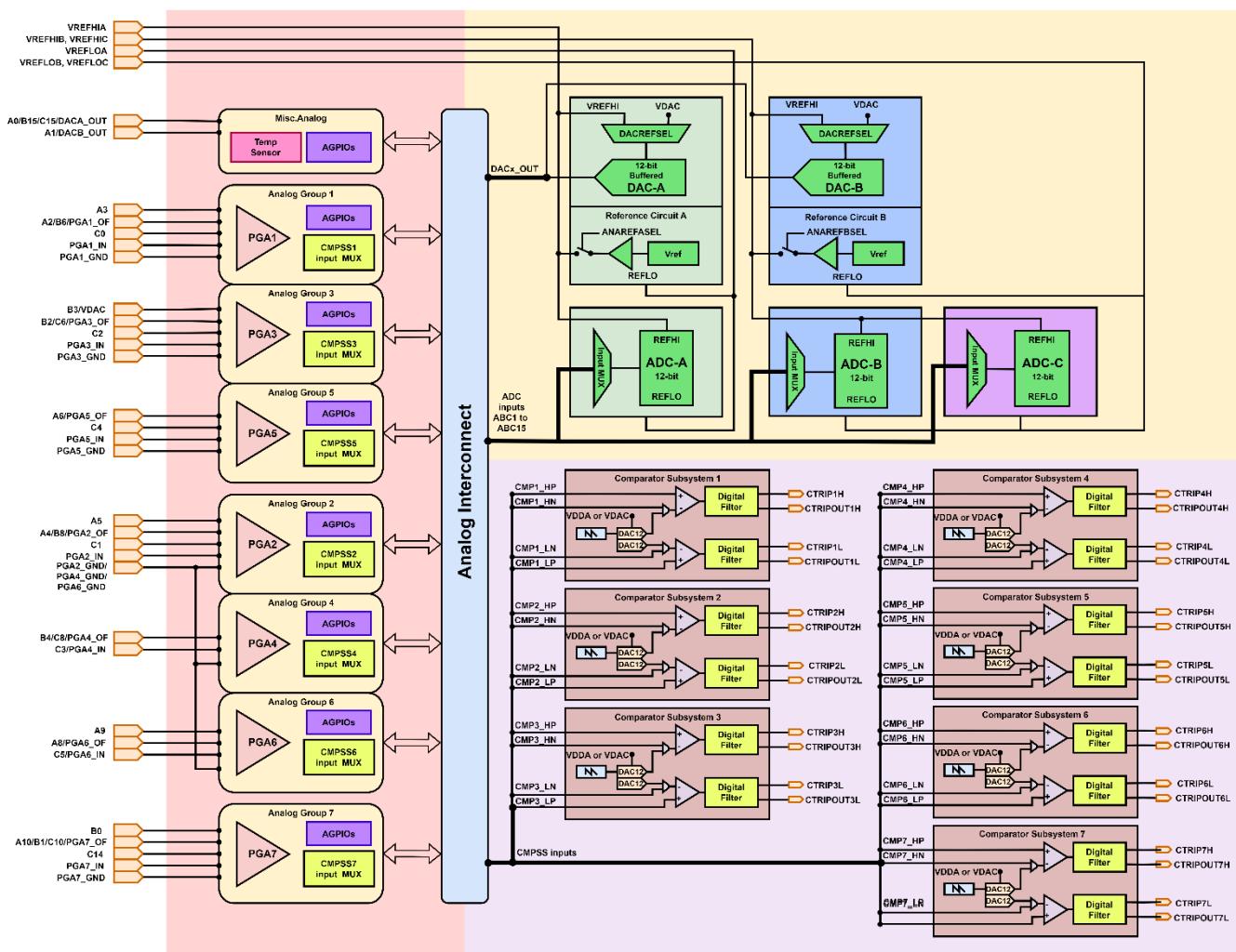

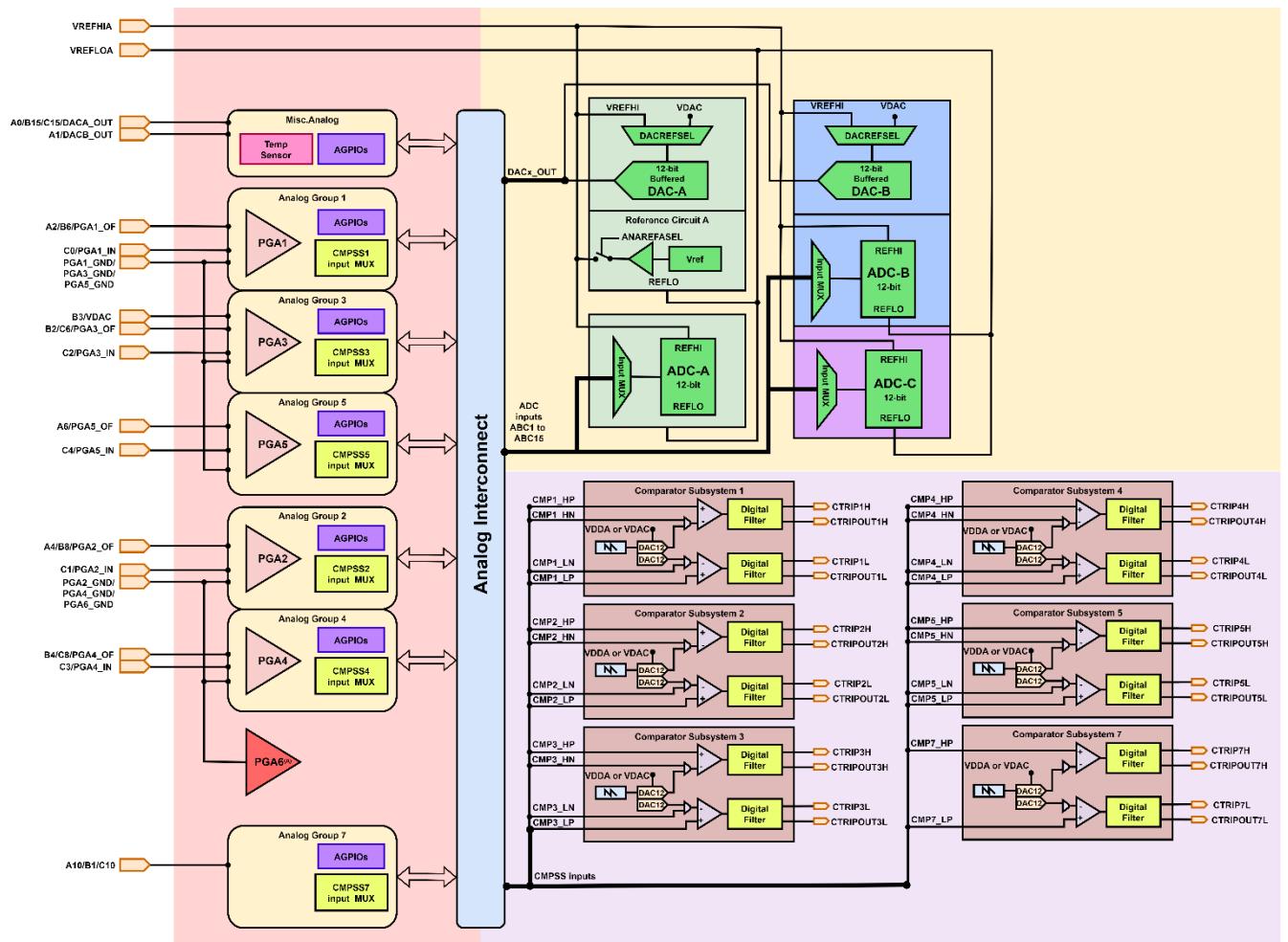

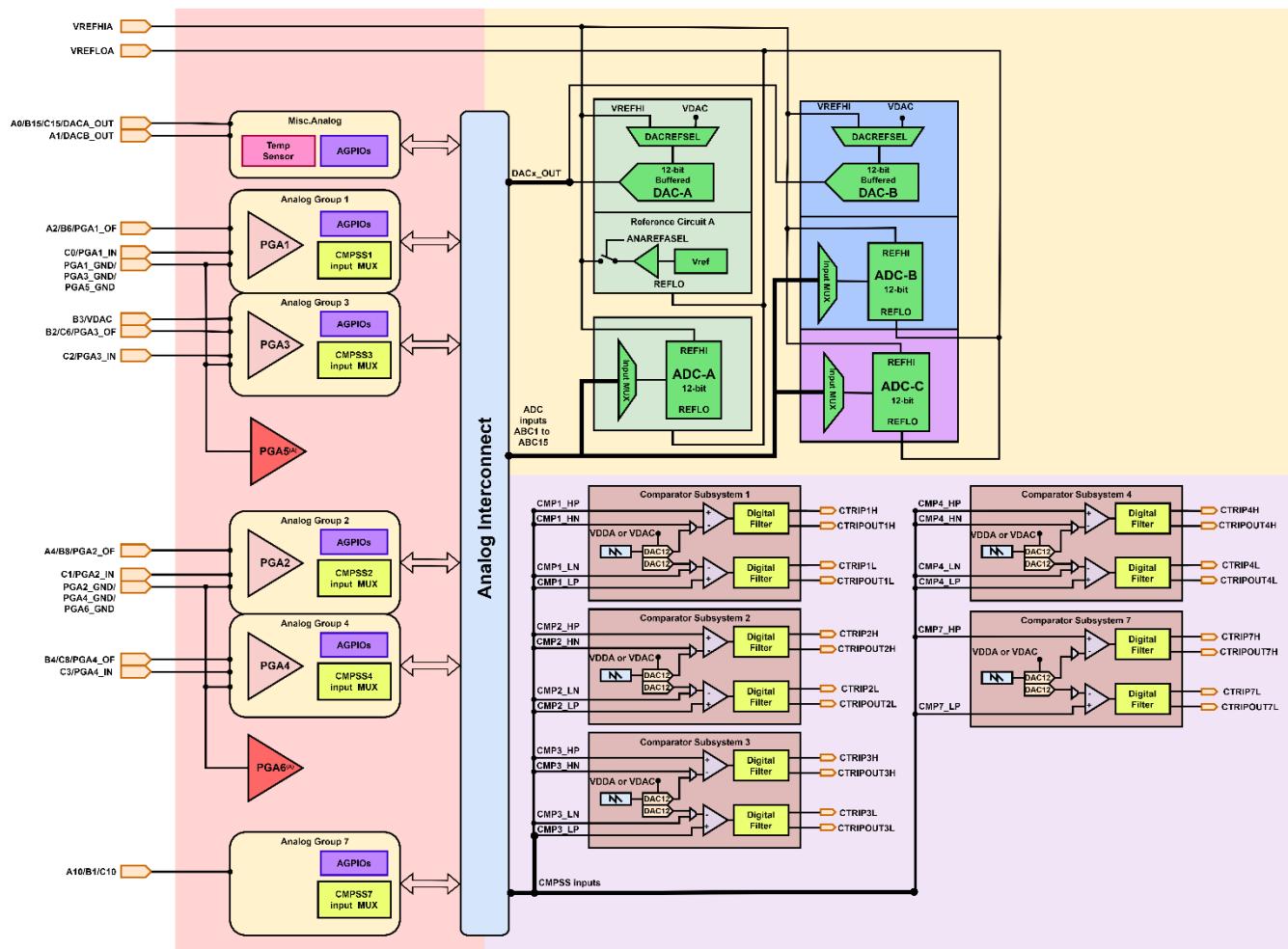

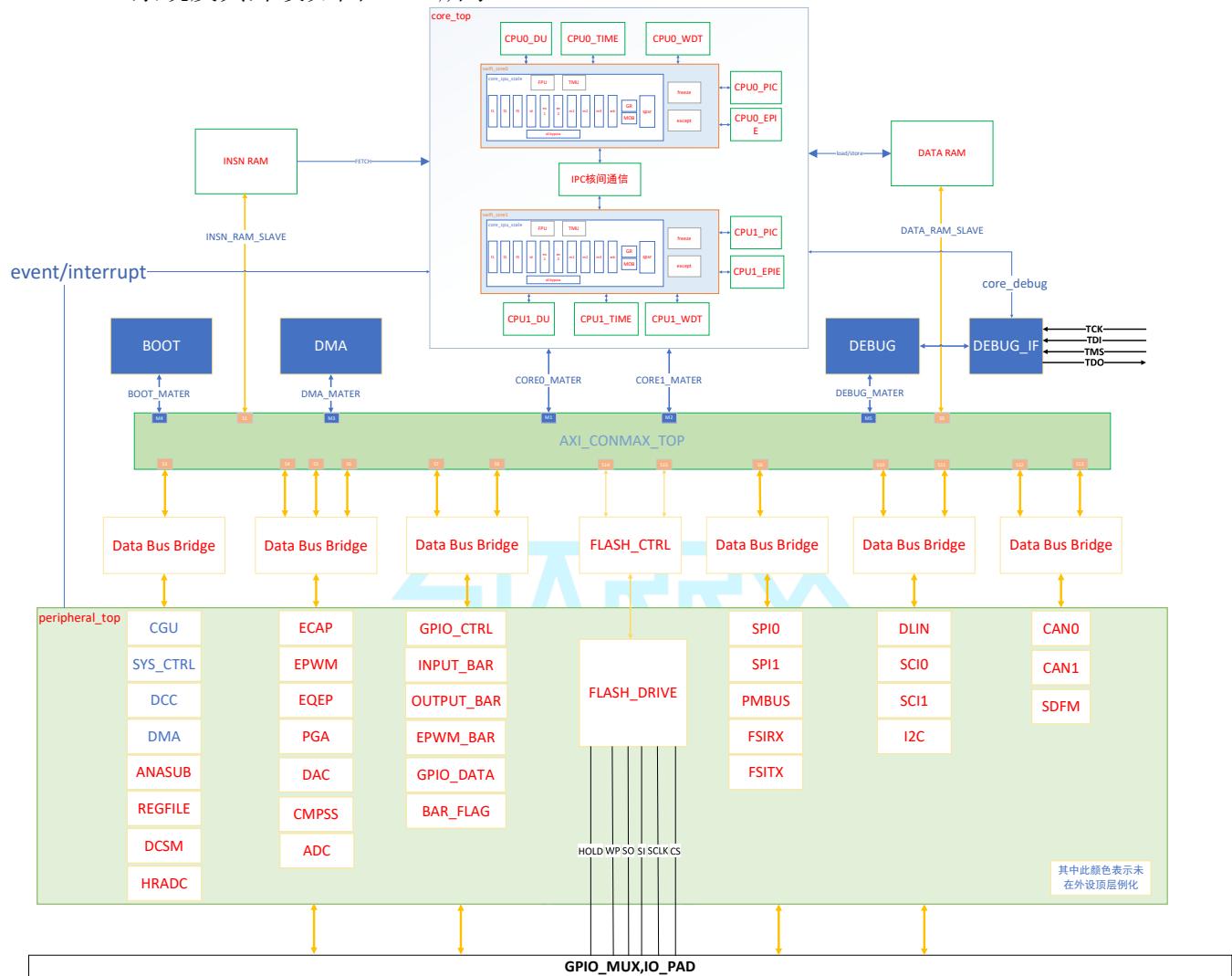

### 3.1 功能框图

功能框图展示了CPU 系统及关联的外设。

图 3-1 功能框图

### 3.2 器件特性

| 功能                   |               | QXS320F280049RevB |

|----------------------|---------------|-------------------|

| 时钟主频                 |               | 160 MHz           |

| 内核数                  |               | 双核                |

| IEEE754单精度浮点单元 (FPU) |               | 支持                |

| 三角函数加速器 (TMU)        |               | 支持                |

| 复杂数学单元 (VCU-I)       |               | 支持                |

| 指令存储IRAM             |               | 双核共享1MB           |

| 数据存储DRAM             |               | 双核共享512KB         |

| 片上FLASH              |               | 1MB               |

| 高速DMA模块通道            |               | 6                 |

| 32位CPU定时器            |               | 6 (每个核支持3个)       |

| 窗口看门狗定时器             |               | 2 (每个核支持1个)       |

| 非可屏蔽中断看门狗定时器         |               | 0                 |

| IO引脚                 | GPIO          | 40/26/25          |

|                      | AI0           | 21/14/12          |

| 嵌入式实时分析和诊断(ERAD)     |               | 有                 |

| 外部中断                 |               | 5                 |

| 12-bit ADC           | 数量            | 3                 |

|                      | 采样率           | 3M                |

|                      | 通道数           | 21                |

|                      | 输入模式          | 单端/差分             |

|                      | 后处理(PPB)      | 4                 |

| 比较子系统<br>(CMPSS)     | 数量            | 7/6/5             |

|                      | DAC           | 12bit             |

| 12-bit DAC           |               | 2                 |

| 可编程增益放大器<br>(PGA)    | 数量            | 7/5/4             |

|                      | 放大倍数          | 3 6 12 24 48      |

| PMBus                |               | 1                 |

| I2C                  |               | 1                 |

| CAN FD(兼容CAN2.0)     |               | 2                 |

| SPI                  |               | 2                 |

| SCI                  |               | 2                 |

| LIN                  |               | 1                 |

| 16bit/32bit EMIF     |               | -                 |

| EPWM                 | EPWM通道        | 16                |

|                      | HRPWM (110ps) | 16                |

|                      | HHRPWM(45ps)  | -                 |

| eCAP                 | eCAP          | 7                 |

|                      | HRCAP         | 2                 |

| eQEP                 |               | 2                 |

| Σ-Δ滤波器模块 (SDFM)      |               | 4/2/2             |

| 工作温度 (AT)            |               | -40°C~125°C       |

| 封装形式                 |               | 100 LQFP          |

|                      |               | 64 LQFP           |

|                      |               | 56 VQFN           |

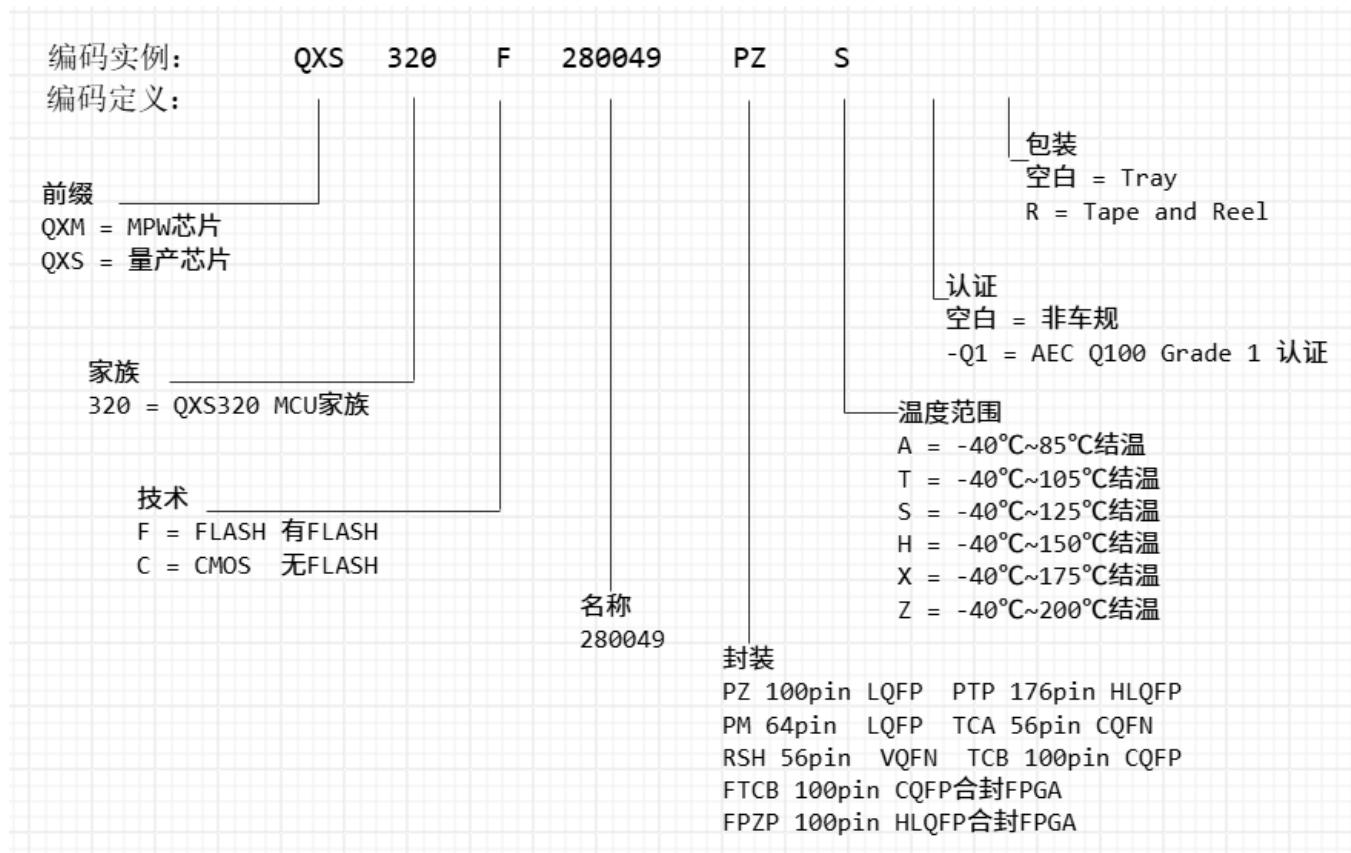

### 3.3 产品编码

图 3-2 器件命名规则图

#### 3.3.1. 产品迭代版本

文档所述产品迭代版本为RevB (QXS320F280049RevB)，该名称在文档、手册文件名，QX-IDE工程名中体现。

## 4 终端配置与功能

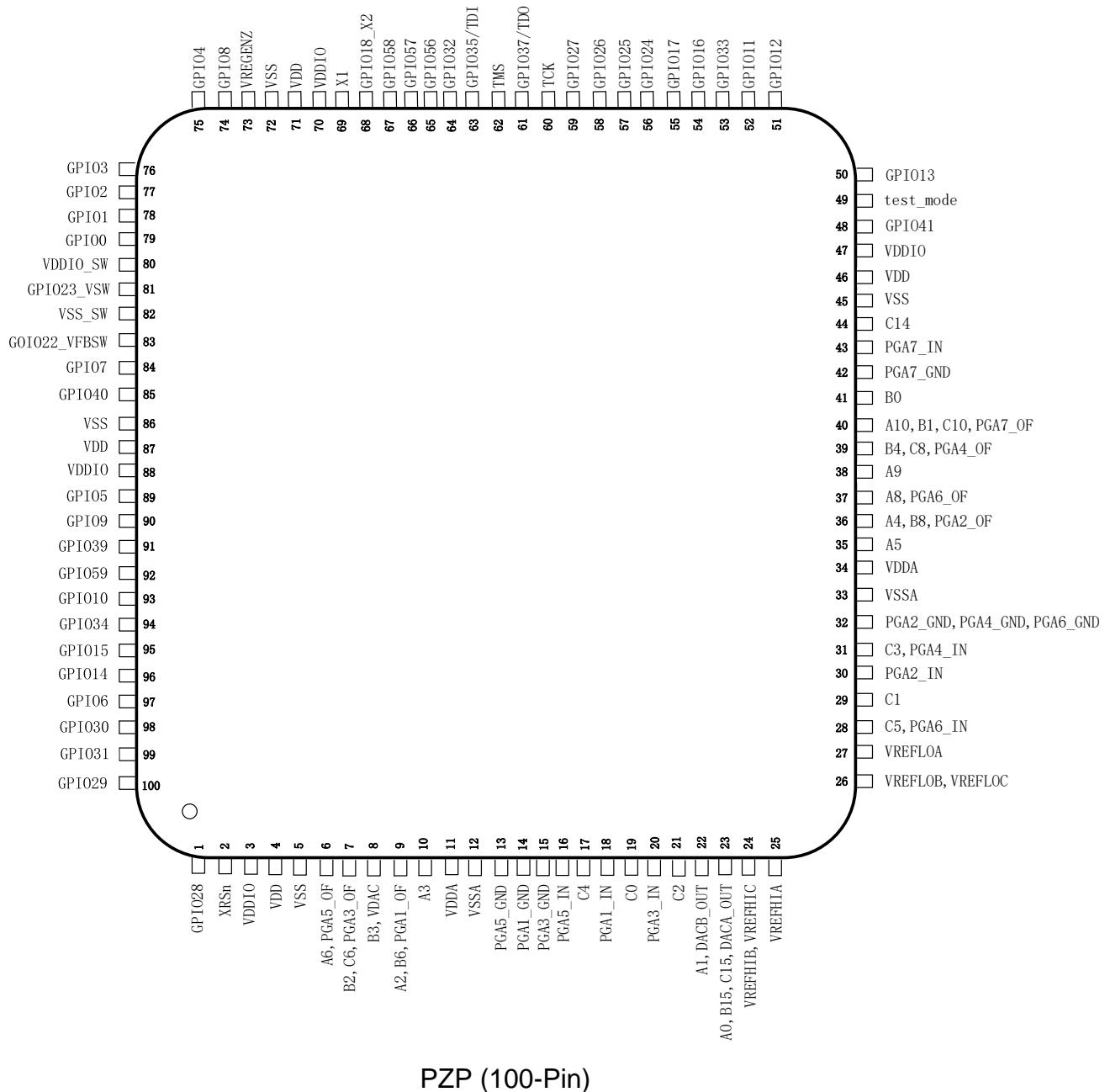

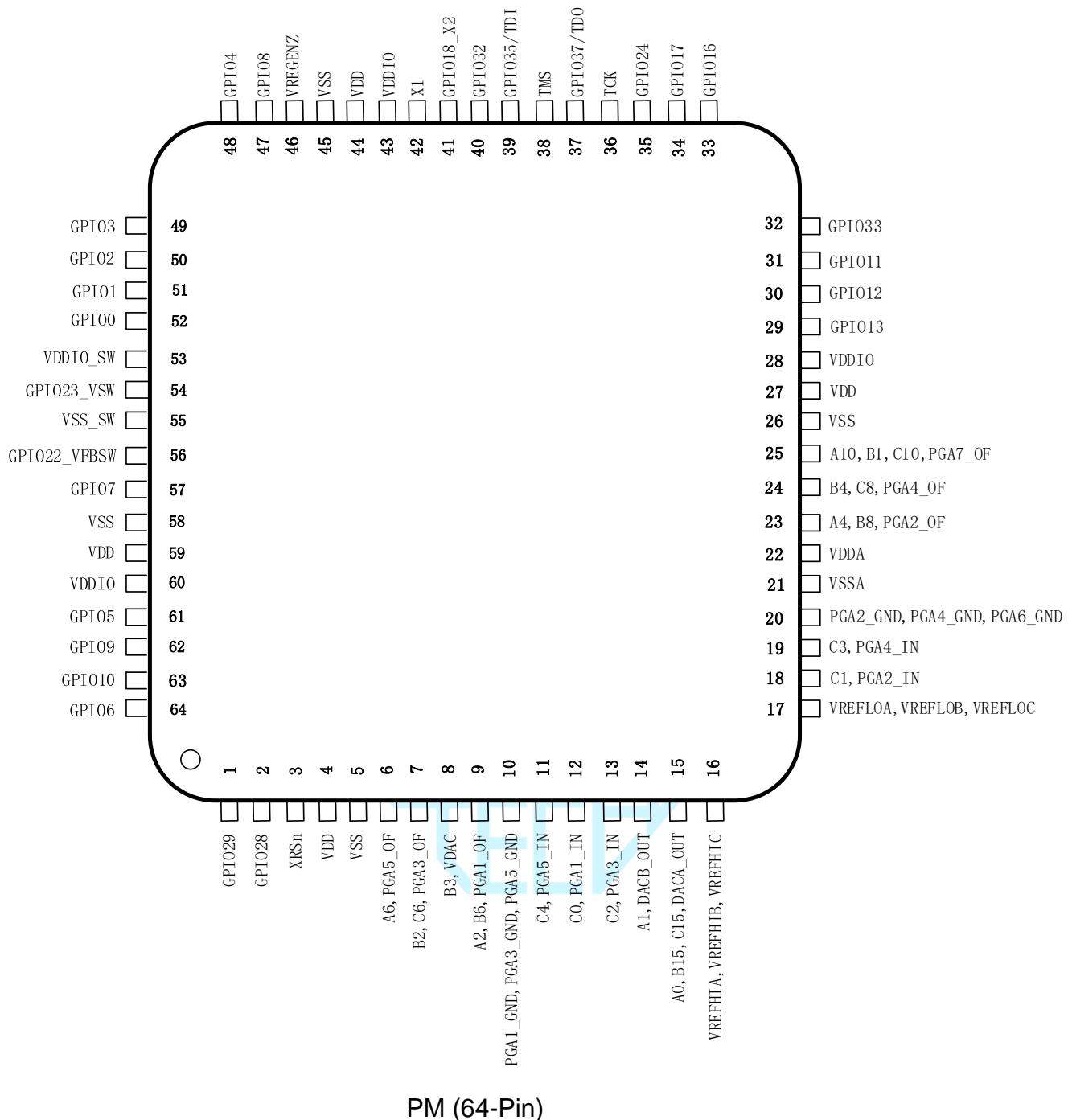

### 4.1 引脚图

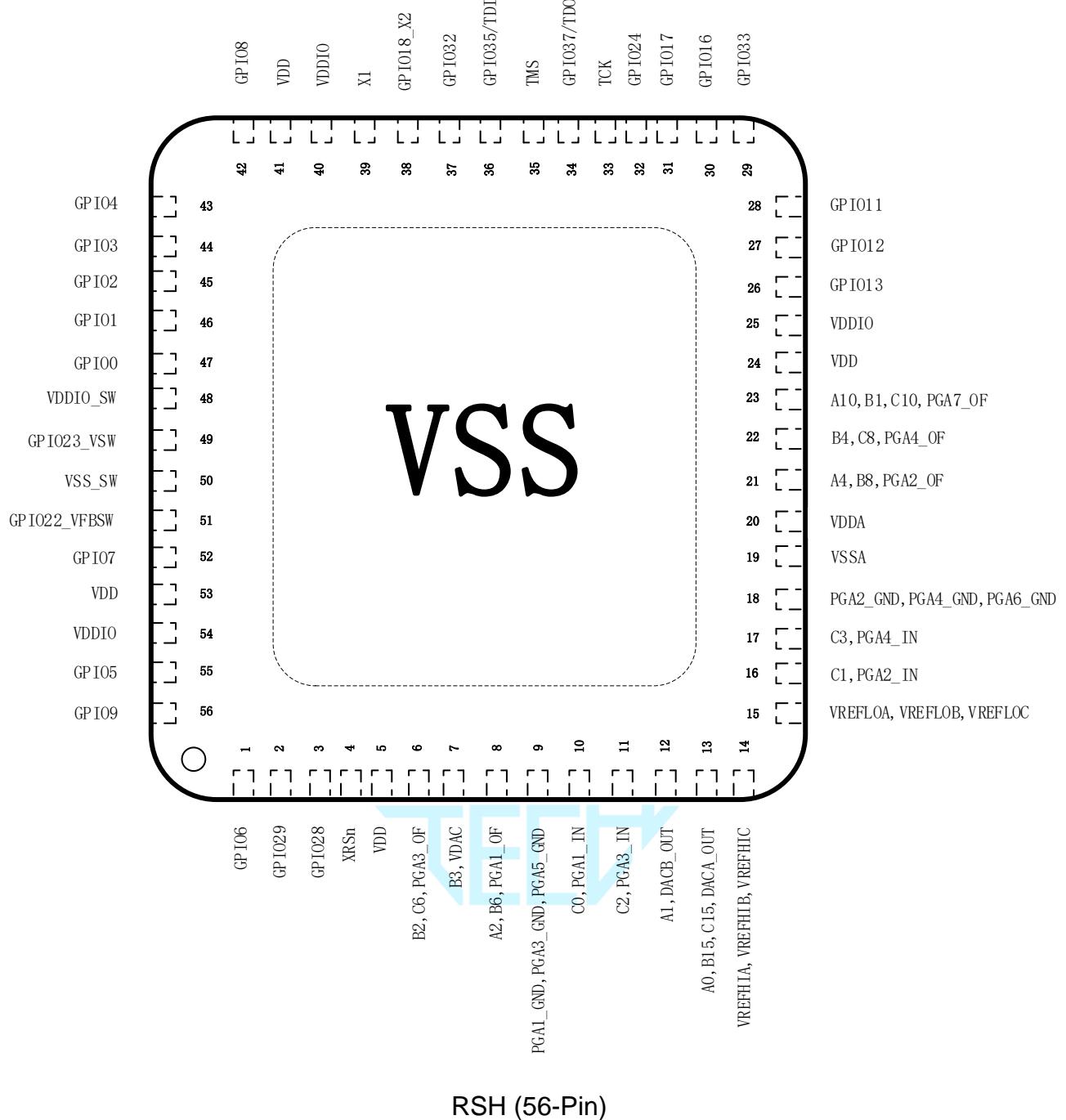

RSH (56-Pin)

## 4.2 引脚说明

表 6-1.引脚属性

| 信号名称                                                            | 多路复用器位置 | 100 PZ | 64 PM | 56RSH | 引脚类型                              | 说明                                                                                                                             |

|-----------------------------------------------------------------|---------|--------|-------|-------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| A0<br>B15<br>C15<br>DACA_OUT<br>AGPIO231                        |         | 23     | 15    | 13    | I<br>I<br>I<br>0<br>I/O           | ADC-A 输入 0<br>ADC-B 输入 15<br>ADC-C 输入 15<br>缓冲 DAC-A 输出<br>ADC 引脚上的数字复用 231                                                    |

| A1<br>DACP_OUT<br>AGPIO232                                      |         | 22     | 14    | 12    | I<br>0<br>I/O                     | ADC-A 输入 1<br>缓冲 DAC-B 输出<br>ADC 引脚上的数字复用 232                                                                                  |

| A10<br>B1<br>C10<br>PGA7_OF<br>CMP7_HPO<br>CMP7_LPOAG<br>PIO230 |         | 40     | 25    | 23    | I<br>I<br>I<br>0<br>I<br>I<br>I/O | ADC-A 输入 10<br>ADC-B 输入 1<br>ADC-C 输入 10<br>PGA-7 输出滤波器 (可选)<br>CMPSS-7 高电平比较器正输入 0<br>CMPSS-7 低电平比较器正输入 0<br>ADC 引脚上的数字复用 230 |

| A2<br>B6<br>PGA1_OF<br>CMP1_HPO<br>CMP1_LPO<br>AGPIO224         |         | 9      | 9     | 8     | I<br>I<br>0<br>I<br>I<br>I/O      | ADC-A 输入 2<br>ADC-B 输入 6<br>PGA-1 输出滤波器 (可选)<br>CMPSS-1 高电平比较器正输入 0<br>CMPSS-1 低电平比较器正输入 0<br>ADC 引脚上的数字复用 224                 |

| A3<br>CMP1_HP3<br>CMP1_HN0<br>CMP1_LP3<br>CMP1_LN0<br>AGPIO233  |         | 10     |       |       | I<br>I<br>I<br>I<br>I<br>I/O      | ADC-A 输入 3<br>CMPSS-1 高电平比较器正输入 3<br>CMPSS-1 高电平比较器负输入 0<br>CMPSS-1 低电平比较器正输入 3<br>CMPSS-1 低电平比较器负输入 0<br>ADC 引脚上的数字复用 233     |

| A4<br>B8<br>PGA2_OF<br>CMP2_HPO<br>CMP2_LPO<br>AGPIO225         |         | 36     | 23    | 21    | I<br>I<br>0<br>I<br>I<br>I/O      | ADC-A 输入 4<br>ADC-B 输入 8<br>PGA-2 输出滤波器 (可选)<br>CMPSS-2 高电平比较器正输入 0<br>CMPSS-2 低电平比较器正输入 0<br>ADC 引脚上的数字复用 225                 |

| A5<br>CMP2_HP3<br>CMP2_HN0<br>CMP2_LP3<br>CMP2_LN0<br>AGPIO234  |         | 35     |       |       | I<br>I<br>I<br>I<br>I<br>I/O      | ADC-A 输入 5<br>CMPSS-2 高电平比较器正输入 3<br>CMPSS-2 高电平比较器负输入 0<br>CMPSS-2 低电平比较器正输入 3<br>CMPSS-2 低电平比较器负输入 0<br>ADC 引脚上的数字复用 234     |

| 信号名称                                                                   | 多路复用器位置 | 100_PZ | 64_PM | 56RSH | 引脚类型                              | 说明                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------|---------|--------|-------|-------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A6<br>PGA5_OF<br>CMP5_HPO<br>CMP5_LPO<br>AGPIO228                      |         | 6      | 6     |       | I<br>0<br>I<br>I<br>I/O           | ADC-A 输入 6<br>PGA-5 输出滤波器 (可选)<br>CMPSS-5 高电平比较器正输入 0<br>CMPSS-5 低电平比较器正输入 0<br>ADC 引脚上的数字复用 228                                                                                                                                               |

| A8<br>PGA6_OF<br>CMP6_HPO<br>CMP6_LPO<br>AGPIO229                      |         | 37     |       |       | I<br>0<br>I<br>I<br>I/O           | ADC-A 输入 8<br>PGA-6 输出滤波器 (可选)<br>CMPSS-6 高电平比较器正输入 0<br>CMPSS-6 低电平比较器正输入 0<br>ADC 引脚上的数字复用 229                                                                                                                                               |

| A9<br>CMP6_HP3<br>CMP6_HN0<br>CMP6_LP3<br>CMP6_LN0<br>AGPIO236         |         | 38     |       |       | I<br>I<br>I<br>I<br>I<br>I/O      | ADC-A 输入 9<br>CMPSS-6 高电平比较器正输入 3<br>CMPSS-6 高电平比较器负输入 0<br>CMPSS-6 低电平比较器正输入 3<br>CMPSS-6 低电平比较器负输入 0<br>ADC 引脚上的数字复用 236                                                                                                                     |

| B0<br>CMP7_HP3<br>CMP7_HN0<br>CMP7_LP3<br>CMP7_LN0<br>AGPIO241         |         | 41     |       |       | I<br>I<br>I<br>I<br>I<br>I/O      | ADC-B 输入 0<br>CMPSS-7 高电平比较器正输入 3<br>CMPSS-7 高电平比较器负输入 0<br>CMPSS-7 低电平比较器正输入 3<br>CMPSS-7 低电平比较器负输入 0<br>ADC 引脚上的数字复用 241                                                                                                                     |

| B2<br>C6<br>PGA3_OF<br>CMP3_HPO<br>CMP3_LPO<br>AGPIO226                |         | 7      | 7     | 6     | I<br>I<br>0<br>I<br>I<br>I/O      | ADC-B 输入 2<br>ADC-C 输入 6<br>PGA-3 输出滤波器 (可选)<br>CMPSS-3 高电平比较器正输入 0<br>CMPSS-3 低电平比较器正输入 0<br>ADC 引脚上的数字复用 226                                                                                                                                 |

| B3<br>VDAC<br>CMP3_HP3<br>CMP3_HN0<br>CMP3_LP3<br>CMP3_LN0<br>AGPIO242 |         | 8      | 8     | 7     | I<br>I<br>I<br>I<br>I<br>I<br>I/O | ADC-B 输入 3<br>片上 DAC 的可选外部基准电压。无论是用于 ADC 输入还是 DAC 基准，此引脚上有一个连接至 VSSA 且无法禁用的 100pF 电容器。如果将此引脚用作片上 DAC 的基准，请在此引脚上放置至少一个 1μF 电容器。<br>CMPSS-3 高电平比较器正输入 3<br>CMPSS-3 高电平比较器负输入 0<br>CMPSS-3 低电平比较器正输入 3<br>CMPSS-3 低电平比较器负输入 0<br>ADC 引脚上的数字复用 242 |

| B4<br>C8<br>PGA4_OF<br>CMP4_HPO<br>CMP4_LPO<br>AGPIO227                |         | 39     | 24    | 22    | I<br>I<br>0<br>I<br>I<br>I/O      | ADC-B 输入 4<br>ADC-C 输入 8<br>PGA-4 输出滤波器 (可选)<br>CMPSS-4 高电平比较器正输入 0<br>CMPSS-4 低电平比较器正输入 0<br>ADC 引脚上的数字复用 227                                                                                                                                 |

| 信号名称                                                            | 多路复用器位置 | 100 PZ | 64 PM | 56RSH | 引脚类型                         | 说明                                                                                                                          |

|-----------------------------------------------------------------|---------|--------|-------|-------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| C0<br>CMP1_HP1<br>CMP1_HN1<br>CMP1_LP1<br>CMP1_LN1<br>AGPIO237  |         | 19     | 12    | 10    | I<br>I<br>I<br>I<br>I<br>I/O | ADC-C 输入 0<br>CMPSS-1 高电平比较器正输入 1<br>CMPSS-1 高电平比较器负输入 1<br>CMPSS-1 低电平比较器正输入 1<br>CMPSS-1 低电平比较器负输入 1<br>ADC 引脚上的数字复用 237  |

| C1<br>CMP2_HP1<br>CMP2_HN1<br>CMP2_LP1<br>CMP2_LN1<br>AGPIO238  |         | 29     | 18    | 16    | I<br>I<br>I<br>I<br>I<br>I/O | ADC-C 输入 1<br>CMPSS-2 高电平比较器正输入 1<br>CMPSS-2 高电平比较器负输入 1<br>CMPSS-2 低电平比较器正输入 1<br>CMPSS-2 低电平比较器负输入 1<br>ADC 引脚上的数字复用 238  |

| C14<br>CMP7_HP1<br>CMP7_HN1<br>CMP7_LP1<br>CMP7_LN1<br>AGPIO246 |         | 44     |       |       | I<br>I<br>I<br>I<br>I<br>I/O | ADC-C 输入 14<br>CMPSS-7 高电平比较器正输入 1<br>CMPSS-7 高电平比较器负输入 1<br>CMPSS-7 低电平比较器正输入 1<br>CMPSS-7 低电平比较器负输入 1<br>ADC 引脚上的数字复用 246 |

| C2<br>CMP3_HP1<br>CMP3_HN1<br>CMP3_LP1<br>CMP3_LN1<br>AGPIO244  |         | 21     | 13    | 11    | I<br>I<br>I<br>I<br>I<br>I/O | ADC-C 输入 2<br>CMPSS-3 高电平比较器正输入 1<br>CMPSS-3 高电平比较器负输入 1<br>CMPSS-3 低电平比较器正输入 1<br>CMPSS-3 低电平比较器负输入 1<br>ADC 引脚上的数字复用 244  |

| C3<br>CMP4_HP1<br>CMP4_HN1<br>CMP4_LP1<br>CMP4_LN1<br>AGPIO245  |         | 31     | 19    | 17    | I<br>I<br>I<br>I<br>I<br>I/O | ADC-C 输入 3<br>CMPSS-4 高电平比较器正输入 1<br>CMPSS-4 高电平比较器负输入 1<br>CMPSS-4 低电平比较器正输入 1<br>CMPSS-4 低电平比较器负输入 1<br>ADC 引脚上的数字复用 245  |

| C4<br>CMP5_HP1<br>CMP5_HN1<br>CMP5_LP1<br>CMP5_LN1<br>AGPIO239  |         | 17     | 11    |       | I<br>I<br>I<br>I<br>I<br>I/O | ADC-C 输入 4<br>CMPSS-5 高电平比较器正输入 1<br>CMPSS-5 高电平比较器负输入 1<br>CMPSS-5 低电平比较器正输入 1<br>CMPSS-5 低电平比较器负输入 1<br>ADC 引脚上的数字复用 239  |

| C5<br>CMP6_HP1<br>CMP6_HN1<br>CMP6_LP1<br>CMP6_LN1<br>AGPIO240  |         | 28     |       |       | I<br>I<br>I<br>I<br>I<br>I/O | ADC-C 输入 5<br>CMPSS-6 高电平比较器正输入 1<br>CMPSS-6 高电平比较器负输入 1<br>CMPSS-6 低电平比较器正输入 1<br>CMPSS-6 低电平比较器负输入 1<br>ADC 引脚上的数字复用 240  |

| PGA1_GND                                                        |         | 14     | 10    | 9     | I                            | PGA-1 接地                                                                                                                    |

| 信号名称     | 多路复用器位置 | 100 PZ | 64 PM | 56RSH | 引脚类型 | 说明                                                                                                                                                                 |

|----------|---------|--------|-------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PGA1_IN  |         | 18     | 12    | 10    | I    | PGA-1 输入                                                                                                                                                           |

| CMP1_HP2 |         |        |       |       | I    | CMPSS-1 高电平比较器正输入 2                                                                                                                                                |

| CMP1_LP2 |         |        |       |       | I    | CMPSS-1 低电平比较器正输入 2                                                                                                                                                |

| PGA2_GND |         | 32     | 20    | 18    | I    | PGA-2 接地                                                                                                                                                           |

| PGA2_IN  |         | 30     | 18    | 16    | I    | PGA-2 输入                                                                                                                                                           |

| CMP2_HP2 |         |        |       |       | I    | CMPSS-2 高电平比较器正输入 2                                                                                                                                                |

| CMP2_LP2 |         |        |       |       | I    | CMPSS-2 低电平比较器正输入 2                                                                                                                                                |

| PGA3_GND |         | 15     | 10    | 9     | I    | PGA-3 接地                                                                                                                                                           |

| PGA3_IN  |         | 20     | 13    | 11    | I    | PGA-3 输入                                                                                                                                                           |

| CMP3_HP2 |         |        |       |       | I    | CMPSS-3 高电平比较器正输入 2                                                                                                                                                |

| CMP3_LP2 |         |        |       |       | I    | CMPSS-3 低电平比较器正输入 2                                                                                                                                                |

| PGA4_GND |         | 32     | 20    | 18    | I    | PGA-4 接地                                                                                                                                                           |

| PGA4_IN  |         | 31     | 19    | 17    | I    | PGA-4 输入                                                                                                                                                           |

| CMP4_HP2 |         |        |       |       | I    | CMPSS-4 高电平比较器正输入 2                                                                                                                                                |

| CMP4_LP2 |         |        |       |       | I    | CMPSS-4 低电平比较器正输入 2                                                                                                                                                |

| PGA5_GND |         | 13     | 10    | 9     | I    | PGA-5 接地                                                                                                                                                           |

| PGA5_IN  |         | 16     | 11    |       | I    | PGA-5 输入                                                                                                                                                           |

| CMP5_HP2 |         |        |       |       | I    | CMPSS-5 高电平比较器正输入 2                                                                                                                                                |

| CMP5_LP2 |         |        |       |       | I    | CMPSS-5 低电平比较器正输入 2                                                                                                                                                |

| PGA6_GND |         | 32     | 20    | 18    | I    | PGA-6 接地                                                                                                                                                           |

| PGA6_IN  |         | 28     |       |       | I    | PGA-6 输入                                                                                                                                                           |

| CMP6_HP2 |         |        |       |       | I    | CMPSS-6 高电平比较器正输入 2                                                                                                                                                |

| CMP6_LP2 |         |        |       |       | I    | CMPSS-6 低电平比较器正输入 2                                                                                                                                                |

| PGA7_GND |         | 42     |       |       | I    | PGA-7 接地                                                                                                                                                           |

| PGA7_IN  |         | 43     |       |       | I    | PGA-7 输入                                                                                                                                                           |

| CMP7_HP2 |         |        |       |       | I    | CMPSS-7 高电平比较器正输入 2                                                                                                                                                |

| CMP7_LP2 |         |        |       |       | I    | CMPSS-7 低电平比较器正输入 2                                                                                                                                                |

| VREFHIA  |         | 25     | 16    | 14    | I/O  | ADC-A 高基准电压。在外部基准模式下，从外部驱动这个引脚上的高基准电压。在内部基准模式下，电压由器件驱动到该引脚。在任一模式下，在此引脚上放置至少一个 2.2 $\mu$ F 电容器。此电容器应放置在 VREFHIA 和 VREFLOA 引脚之间<br>尽可能靠近器件的位置。不要在内部或外部基准模式下从外部加载此引脚。 |

| VREFHIB  |         | 24     | 16    | 14    | I/O  | ADC-B 高基准电压。在外部基准模式下，从外部驱动这个引脚上的高基准电压。在内部基准模式下，电压由器件驱动到该引脚。在任一模式下，在此引脚上放置至少一个 2.2 $\mu$ F 电容器。此电容器应放置在 VREFHIB 和 VREFLOB 引脚之间<br>尽可能靠近器件的位置。不要在内部或外部基准模式下从外部加载此引脚。 |

| 信号名称    | 多路复用器位置 | 100 PZ | 64 PM | 56RSH | 引脚类型 | 说明                                                                                                                                                                |

|---------|---------|--------|-------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VREFHIC |         | 24     | 16    | 14    | I/O  | ADC-C 高基准电压。在外部基准模式下，从外部驱动这个引脚上的高基准电压。在内部基准模式下，电压由器件驱动到该引脚。在任一模式下，在此引脚上放置至少一个 $2.2\mu F$ 电容器。此电容器应放置在 VREFHIC 和 VREFLOC 引脚之间<br>尽可能靠近器件的位置。不要在内部或外部基准模式下从外部加载此引脚。 |

| VREFLOA |         | 27     | 17    | 15    | I    | ADC-A 低基准电压                                                                                                                                                       |

| VREFLOB |         | 26     | 17    | 15    | I    | ADC-B 低基准电压                                                                                                                                                       |

| VREFLOC |         | 26     | 17    | 15    | I    | ADC-C 低基准电压                                                                                                                                                       |

| 信号名称                 | 多路复用器位置     | 100<br>PZ | 64 PM | 56RSH | 引脚类型 | 说明                                          |

|----------------------|-------------|-----------|-------|-------|------|---------------------------------------------|

| GPIO0                | 0, 4, 8, 12 |           |       |       | I/O  | 通用输入/输出 0                                   |

| EPWM1_A              | 1           |           |       |       | 0    | ePWM-1 输出 A                                 |

| SPIA_D2              | 2           | 79        | 52    | 47    | I/O  | SPI-A QSPI模式的第三位数据                          |

| I2CA_SDA             | 6           |           |       |       | I/OD | I2C-A 开漏双向数据                                |

| GPIO1                | 0, 4, 8, 12 |           |       |       | I/O  | 通用输入/输出 1                                   |

| EPWM1_B              | 1           |           |       |       | 0    | ePWM-1 输出 B                                 |

| SPIA_D2              | 2           | 78        | 51    | 46    | I/O  | SPI-A QSPI模式的第三位数据                          |

| I2CA_SCL             | 6           |           |       |       | I/OD | I2C-A 开漏双向时钟                                |

| GPIO2                | 0, 4, 8, 12 |           |       |       | I/O  | 通用输入/输出 2                                   |

| EPWM2_A              | 1           |           |       |       | 0    | ePWM-2 输出 A                                 |

| OUTPUTXBAR1          | 5           | 77        | 50    | 45    | 0    | 输出 X-BAR 输出 1                               |

| PMBUSA_SDA           | 6           |           |       |       | I/OD | PMBus-A 开漏双向数据                              |

| SCIA_TX              | 9           |           |       |       | 0    | SCI-A 送数据                                   |

| GPIO3                | 0, 4, 8, 12 |           |       |       | I/O  | 通用输入/输出 3                                   |

| EPWM2_B              | 1           |           |       |       | 0    | ePWM-2 输出 B                                 |

| OUTPUTXBAR2          | 2、5         |           |       |       | 0    | 输出 X-BAR 输出 2                               |

| PMBUSA_SCL           | 6           | 76        | 49    | 44    | I/OD | PMBus-A 开漏双向时钟                              |

| SPIA_CLK             | 7           |           |       |       | I/O  | SPI-A 时钟                                    |

| SCIA_RX              | 9           |           |       |       | I    | SCI-A 接收数据                                  |

| GPIO4                | 0, 4, 8, 12 |           |       |       | I/O  | 通用输入/输出 4                                   |

| EPWM3_A              | 1           |           |       |       | 0    | ePWM-3 输出 A                                 |

| SPIA_D3              | 2           | 75        | 48    | 43    | I/O  | SPI-A QSPI模式的第四位数据                          |

| OUTPUTXBAR3          | 5           |           |       |       | 0    | 输出 X-BAR 输出 3                               |

| CANA_TX              | 6           |           |       |       | 0    | CAN-A 发送                                    |

| GPIO5                | 0, 4, 8, 12 |           |       |       | I/O  | 通用输入/输出 5                                   |

| EPWM3_B              | 1           |           |       |       | 0    | ePWM-3 输出 B                                 |

| OUTPUTXBAR3          | 3           | 89        | 61    | 55    | 0    | 输出 X-BAR 输出 3                               |

| CANA_RX              | 6           |           |       |       | I    | CAN-A 接收                                    |

| SPIA_STE             | 7           |           |       |       | I/O  | SPI-A 器件使能 (STE)                            |

| GPIO6                | 0, 4, 8, 12 |           |       |       | I/O  | 通用输入/输出 6                                   |

| EPWM4_A              | 1           |           |       |       | 0    | ePWM-4 输出 A                                 |

| OUTPUTXBAR4          | 2           |           |       |       | 0    | 输出 X-BAR 输出 4                               |

| SYNCOUT              | 3           | 97        | 64    | 1     | 0    | 外部 ePWM 同步脉冲                                |

| EQEP1_A              | 5           |           |       |       | I    | eQEP-1 输入 A                                 |

| CANB_TX              | 6           |           |       |       | 0    | CAN-B 发送                                    |

| SPIB_SOMI (QSPIB_D1) | 7           |           |       |       | I/O  | SPI-B 从器件输出, 主器件输入 (SOMI)<br>或QSPI模式下的第二位数据 |

| 信号名称                                                                                                     | 多路复用器位置                                        | 100<br>PZ | 64 PM | 56RSH | 引脚类型                                          | 说明                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------|-------|-------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO7<br>EPWM4_B<br>OUTPUTXBAR5<br>EQEP1_B<br>CANB_RX<br>SPIB_SIMO (QSPI_B_D0)                           | 0, 4, 8, 12<br>1<br>3<br>5<br>6<br>7           | 84        | 57    | 52    | I/O<br>0<br>0<br>I<br>I<br>I/O                | 通用输入/输出 7<br>ePWM-4 输出 B<br>输出 X-BAR 输出 5<br>eQEP-1 输入 B<br>CAN-B 接收<br>SPI-B 从器件输入, 主器件输出 (SIMO) 或QSPI模式下的第一位数据                                                      |

| GPIO8<br>EPWM5_A<br>CANB_TX<br>ADCSOCDAO<br>EQEP1_STROBE<br>SCIA_TX<br>SPIA_SIMO (QSPI_A_D0)<br>I2CA_SCL | 0, 4, 8, 12<br>1<br>2<br>3<br>5<br>6<br>7<br>9 | 74        | 47    | 42    | I/O<br>0<br>0<br>0<br>I/O<br>0<br>I/O<br>I/OD | 通用输入/输出 8<br>ePWM-5 输出 A<br>CAN-B 发送<br>外部 ADC (来自 ePWM 模块) 的 ADC 转换启动 A 输出<br>eQEP-1 选通<br>SCI-A 发送数据<br>SPI-A 从器件输入, 主器件输出 (SIMO) 或QSPI模式下的第一位数据<br>I2C-A 开漏双向时钟    |

| GPIO9<br>EPWM5_B<br>SCIB_TX<br>OUTPUTXBAR6<br>EQEP1_INDEX<br>SCIA_RX<br>SPIA_CLK                         | 0, 4, 8, 12<br>1<br>2<br>3<br>5<br>6<br>7      | 90        | 62    | 56    | I/O<br>0<br>0<br>0<br>I/O<br>I<br>I/O         | 通用输入/输出 9<br>ePWM-5 输出 B<br>SCI-B 发送数据<br>输出 X-BAR 输出 6<br>eQEP-1 索引<br>SCI-A 接收数据<br>SPI-A 时钟                                                                        |

| GPIO10<br>EPWM6_A<br>CANB_RX<br>ADCSOCBO<br>EQEP1_A<br>SCIB_TX<br>SPIA_SOMI (QSPI_A_D1)<br>I2CA_SDA      | 0, 4, 8, 12<br>1<br>2<br>3<br>5<br>6<br>7<br>9 | 93        | 63    |       | I/O<br>0<br>I<br>0<br>I<br>0<br>I/O<br>I/OD   | 通用输入/输出 10<br>ePWM-6 输出 A<br>CAN-B 接收<br>外部 ADC (来自 ePWM 模块) 的 ADC 转换启动 B 输出<br>eQEP-1 输入 A<br>SCI-B 发送数据<br>SPI-A 从器件输出, 主器件输入 (SOMI) 或QSPI模式下的第二位数据<br>I2C-A 开漏双向数据 |

| GPIO11<br>EPWM6_B<br>SCIB_RX<br>OUTPUTXBAR7<br>EQEP1_B<br>SPIA_STE                                       | 0, 4, 8, 12<br>1<br>2, 6<br>3<br>5<br>7        | 52        | 31    | 28    | I/O<br>0<br>I<br>0<br>I<br>I/O                | 通用输入/输出 11<br>ePWM-6 输出 B<br>SCI-B 接收数据<br>输出 X-BAR 输出 7<br>eQEP-1 输入 B<br>SPI-A 器件使能 (STE)                                                                           |

| GPIO12<br>EPWM7_A<br>CANB_TX<br>SPIB_D2<br>EQEP1_STROBE<br>SCIB_TX<br>PMBUSA_CTL                         | 0, 4, 8, 12<br>1<br>2<br>3<br>5<br>6<br>7      | 51        | 30    | 27    | I/O<br>0<br>0<br>I/O<br>I/O<br>0<br>I         | 通用输入/输出 12<br>ePWM-7 输出 A<br>CAN-B 发送<br>SPI-B 从器件数据输入, 主器件输出或QSPI模式下的第三位数据<br>eQEP-1 选通<br>SCI-B 发送数据<br>PMBus-A 控制信号                                                |

| 信号名称                                                                                                                                 | 多路复用器位置                                                    | 100<br>PZ | 64 PM | 56RSH | 引脚类型                                                    | 说明                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------|-------|-------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO13<br>EPWM7_B<br>CANB_RX<br>SPIB_D2<br>EQEP1_INDEX<br>SCIB_RX<br>PMBUSA_ALERT                                                    | 0, 4, 8, 12<br>1<br>2<br>3<br>5<br>6<br>7                  | 50        | 29    | 26    | I/O<br>0<br>I<br>I/O<br>I/O<br>I<br>I/OD                | 通用输入/输出 13<br>ePWM-7 输出 B<br>CAN-B 接收<br>SPI-B QSPI模式下的第三位数据<br>eQEP-1 索引<br>SCI-B 接收数据<br>PMBus-A 开漏双向警报信号                                                                                                 |

| GPIO14<br>EPWM8_A<br>SCIB_TX<br>OUTPUTXBAR3<br>PMBUSA_SDA<br>SPIB_CLK<br>EQEP2_A                                                     | 0, 4, 8, 12<br>1<br>2<br>6<br>7<br>9<br>10                 | 96        |       |       | I/O<br>0<br>0<br>0<br>I/OD<br>I/O<br>I                  | 通用输入/输出 14<br>ePWM-8 输出 A<br>SCI-B 发送数据<br>输出 X-BAR 输出 3<br>PMBus-A 开漏双向数据<br>SPI-B 时钟<br>eQEP-2 输入 A                                                                                                       |

| GPIO15<br>EPWM8_B<br>SCIB_RX<br>SPIB_D3<br>OUTPUTXBAR4<br>PMBUSA_SCL<br>SPIB_STE<br>EQEP2_B                                          | 0, 4, 8, 12<br>1<br>2<br>3<br>6<br>7<br>9<br>10            | 95        |       |       | I/O<br>0<br>I<br>I/O<br>0<br>I/OD<br>I/O<br>I           | 通用输入/输出 15<br>ePWM-8 输出 B<br>SCI-B 接收数据<br>SPI-B QSPI模式下的第四位数据<br>输出 X-BAR 输出 4<br>PMBus-A 开漏双向时钟<br>SPI-B 器件使能 (STE)<br>eQEP-2 输入 B                                                                        |

| GPIO16<br>SPIA_SIMO(QSPI<br>A_DO)<br>CANB_TX<br>OUTPUTXBAR7<br>EPWM5_A<br>SCIA_TX<br>SD1_D1<br>EQEP1_STROBE<br>PMBUSA_SCL<br>XCLKOUT | 0, 4, 8, 12<br>1<br>2<br>3<br>5<br>6<br>7<br>9<br>10<br>11 | 54        | 33    | 30    | I/O<br>I/O<br>0<br>0<br>0<br>0<br>I<br>I/O<br>I/OD<br>0 | 通用输入/输出 16<br>SPI-A 从器件输入, 主器件输出 (SIMO) 或QSPI模式<br>下的第一位数据<br>CAN-B 发送<br>输出 X-BAR 输出 7<br>ePWM-5 输出 A<br>SCI-A 发送数据<br>SDFM-1 通道 1 数据输入<br>eQEP-1 选通<br>PMBus-A 开漏双向时钟<br>外部时钟输出。此引脚从器件中输出所选时钟信号<br>的分频版本。 |

| GPIO17<br>SPIA_SOMI(QSP<br>IA_D1)<br>CANB_RX<br>OUTPUTXBAR8<br>EPWM5_B<br>SCIA_RX<br>SD1_C1<br>EQEP1_INDEX<br>PMBUSA_SDA             | 0, 4, 8, 12<br>1<br>2<br>3<br>5<br>6<br>7<br>9<br>10       | 55        | 34    | 31    | I/O<br>I/O<br>I<br>0<br>0<br>I<br>I<br>I/O<br>I/OD      | 通用输入/输出 17<br>SPI-A 从器件输出, 主器件输入 (SOMI) 或QSPI模式<br>下的第二位数据<br>CAN-B 接收<br>输出 X-BAR 输出 8<br>ePWM-5 输出 B<br>SCI-A 接收数据<br>SDFM-1 通道 1 时钟输入<br>eQEP-1 索引<br>PMBus-A 开漏双向数据                                     |

| GPIO18<br>X2                                                                                                                         | 0, 4, 8, 12<br>ALT                                         | 68        | 41    | 38    | I/O<br>I/O                                              | 通用输入/输出 18<br>晶振振荡器输出                                                                                                                                                                                       |

| GPIO20                                                                                                                               | 0                                                          |           |       |       | I/O                                                     | 通用输入/输出 20                                                                                                                                                                                                  |

| GPIO21                                                                                                                               | 0                                                          |           |       |       | I/O                                                     | 通用输入/输出 21                                                                                                                                                                                                  |

| GPIO22<br>VFBSW(1)                                                                                                                   | 0, 4, 8, 12<br>ALT                                         | 83        | 56    | 51    | I/O<br>-                                                | 通用输入/输出 22<br>内部线性稳压器输出信号, 直流/直流稳压器反馈信<br>号。如果使用内部直流/直流稳压器, 请将此引脚连<br>接到L (VSW) 与VDD之间的节点上 (尽可能靠近芯<br>片)。                                                                                                   |

| 信号名称                                                                                                               | 多路复用器位置                                                | 100 PZ | 64 PM | 56RSH | 引脚类型                                             | 说明                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------|-------|-------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO23<br>VSW(1)                                                                                                   | 0, 4, 8, 12<br>ALT                                     | 81     | 54    | 49    | I/O<br>-                                         | 通用输入/输出 23<br>内部直流/直流稳压器的切换输出。                                                                                                                                                                                                                                    |

| GPIO24<br>OUTPUTXBAR1<br>EQEP2_A<br>EPWM8_A<br>SPIB_SIMO(QSPI_B_D0)<br>SD1_D1<br>PMBUSA_SCL<br>SCIA_TX<br>ERRORSTS | 0, 4, 8, 12<br>1<br>2<br>5<br>6<br>7<br>10<br>11<br>13 | 56     | 35    | 32    | I/O<br>0<br>I<br>0<br>I/O<br>I<br>I/OD<br>0<br>0 | 通用输入/输出 24<br>输出 X-BAR 输出 1<br>eQEP-2 输入 A<br>ePWM-8 输出 A<br>SPI-B 从器件输入, 主器件输出 (SIMO) 或QSPI模式下的第一位数据<br>SDFM-1 通道 1 数据输入<br>PMBus-A 开漏双向时钟<br>SCI-A 发送数据<br>低电平有效错误状态输出。如果您希望在上电期间或在 ERRORSTS 信号本身发生故障期间将错误状态置为有效, 则可以使用外部下拉电阻。如果您不希望在上述条件下将错误状态置为有效, 则可以使用上拉电阻。 |

| GPIO25<br>OUTPUTXBAR2<br>EQEP2_B<br>SPIB_SOMI(QSPI_B_D1)<br>SD1_C1<br>PMBUSA_SDA<br>SCIA_RX                        | 0, 4, 8, 12<br>1<br>2<br>6<br>7<br>10<br>11            | 57     |       |       | I/O<br>0<br>I<br>I/O<br>I<br>I/OD<br>I           | 通用输入/输出 25<br>输出 X-BAR 输出 2<br>eQEP-2 输入 B<br>SPI-B 从器件输出, 主器件输入 (SOMI) 或QSPI模式下的第二位数据<br>SDFM-1 通道 1 时钟输入<br>PMBus-A 开漏双向数据<br>SCI-A 接收数据                                                                                                                        |

| GPIO26<br>OUTPUTXBAR3<br>EQEP2_INDEX<br>CAN0_STBY<br>SPIB_CLK<br>SD1_D2<br>PMBUSA_CTL<br>I2CA_SDA                  | 0, 4, 8, 12<br>1, 5<br>2<br>3<br>6<br>7<br>10<br>11    | 58     |       |       | I/O<br>0<br>I/O<br>0<br>I/O<br>I<br>I<br>I/OD    | 通用输入/输出 26<br>输出 X-BAR 输出 3<br>eQEP-2 索引<br>CAN0 STBY 输出<br>SPI-B 时钟<br>SDFM-1 通道 2 数据输入<br>PMBus-A 控制信号<br>I2C-A 开漏双向数据                                                                                                                                          |

| GPIO27<br>OUTPUTXBAR4<br>EQEP2_STROBE<br>CAN1_STBY<br>SPIB_STE<br>SD1_C2<br>PMBUSA_ALERT<br>I2CA_SCL               | 0, 4, 8, 12<br>1, 5<br>2<br>3<br>6<br>7<br>10<br>11    | 59     |       |       | I/O<br>0<br>I/O<br>0<br>I/O<br>I<br>I/OD<br>I/OD | 通用输入/输出 27<br>输出 X-BAR 输出 4<br>eQEP-2 选通<br>CAN1 STBY 输出<br>SPI-B 器件使能 (STE)<br>SDFM-1 通道 2 时钟输入<br>PMBus-A 开漏双向警报信号<br>I2C-A 开漏双向时钟                                                                                                                              |

| 信号名称                                                                                                                             | 多路复用器位置                                                          | 100 PZ | 64 PM | 56RSH | 引脚类型                                                      | 说明                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------|-------|-------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO28<br>SCIA_RX<br>CAN1_STBY<br>EPWM7_A<br>OUTPUTXBAR5<br>EQEP1_A<br>SD1_D3<br>EQEP2_STROBE<br>LINA_TX<br>SPIB_CLK<br>ERRORSTS | 0, 4, 8, 12<br>1<br>2<br>3<br>5<br>6<br>7<br>9<br>10<br>11<br>13 |        |       |       | I/O<br>I<br>0<br>0<br>0<br>I<br>I<br>I/O<br>0<br>I/O<br>0 | 通用输入/输出 28<br>SCI-A 接收数据<br>CANB STBY 输出<br>ePWM-7 输出 A<br>输出 X-BAR 输出 5<br>eQEP-1 输入 A<br>SDFM-1 通道 3 数据输入<br>eQEP-2 选通<br>LIN-A 发送<br>SPI-B 时钟<br>低电平有效错误状态输出。如果您希望在上电期间或在 ERRORSTS 信号本身发生故障期间将错误状态置为有效，则可以使用外部下拉电阻。如果您不希望在上述条件下将错误状态置为有效，则可以使用上拉电阻。         |

| GPIO29<br>SCIA_TX<br>CAN1_STBY<br>EPWM7_B<br>OUTPUTXBAR6<br>EQEP1_B<br>SD1_C3<br>EQEP2_INDEX<br>LINA_RX<br>SPIB_STE<br>ERRORSTS  | 0, 4, 8, 12<br>1<br>2<br>3<br>5<br>6<br>7<br>9<br>10<br>11<br>13 | 100    | 1     | 2     | I/O<br>0<br>0<br>0<br>0<br>I<br>I<br>I/O<br>I<br>I/O<br>0 | 通用输入/输出 29<br>SCI-A 发送数据<br>CANB STBY 输出<br>ePWM-7 输出 B<br>输出 X-BAR 输出 6<br>eQEP-1 输入 B<br>SDFM-1 通道 3 时钟输入<br>eQEP-2 索引<br>LIN-A 接收<br>SPI-B 器件使能 (STE)<br>低电平有效错误状态输出。如果您希望在上电期间或在 ERRORSTS 信号本身发生故障期间将错误状态置为有效，则可以使用外部下拉电阻。如果您不希望在上述条件下将错误状态置为有效，则可以使用上拉电阻。 |

| GPIO30<br>CANA_RX<br>SPIB_SIMO (QSPIB_D0)<br>OUTPUTXBAR7<br>EQEP1_STROBE<br>SD1_D4                                               | 0, 4, 8, 12<br>1<br>3<br>5<br>6<br>7                             |        | 98    |       | I/O<br>I<br>I/O<br>0<br>I/O<br>I                          | 通用输入/输出 30<br>CAN-A 接收<br>SPI-B 从器件输入，主器件输出 (SIMO) 或QSPI模式下的第一位数据<br>输出 X-BAR 输出 7<br>eQEP-1 选通<br>SDFM-1 通道 4 数据输入                                                                                                                                            |

| GPIO31<br>CANA_TX<br>SPIB_SOMI (QSPIB_D1)<br>OUTPUTXBAR8<br>EQEP1_INDEX<br>SD1_C4                                                | 0, 4, 8, 12<br>1<br>3<br>5<br>6<br>7                             |        | 99    |       | I/O<br>0<br>I/O<br>0<br>I/O<br>I                          | 通用输入/输出 31<br>CAN-A 发送<br>SPI-B 从器件输出，主器件输入 (SOMI) 或QSPI模式下的第二位数据<br>输出 X-BAR 输出 8<br>eQEP-1 索引<br>SDFM-1 通道 4 时钟输入                                                                                                                                            |

| 信号名称                                                                                                            | 多路复用器位置                                                    | 100 PZ | 64 PM | 56RSH | 引脚类型                                                     | 说明                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------|-------|-------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO32<br>I2CA_SDA<br>SPIB_CLK<br>EPWM8_B<br>LINA_TX<br>SD1_D3<br>CANA_TX                                       | 0, 4, 8, 12<br>1<br>3<br>5<br>6<br>7<br>10                 | 64     | 40    | 37    | I/O<br>I/OD<br>I/O<br>0<br>0<br>I<br>0                   | 通用输入/输出 32<br>I2C-A 开漏双向数据<br>SPI-B 时钟<br>ePWM-8 输出 B<br>LIN-A 发送<br>SDFM-1 通道 3 数据输入<br>CAN-A 发送                                                        |

| GPIO33<br>I2CA_SCL<br>SPIB_STE<br>OUTPUTXBAR4LI<br>NA_RX<br>SD1_C3<br>CANA_RX                                   | 0, 4, 8, 12<br>1<br>3<br>5<br>6<br>7<br>10                 | 53     | 32    | 29    | I/O<br>I/OD<br>I/O<br>0<br>I<br>I<br>I                   | 通用输入/输出 33<br>I2C-A 开漏双向时钟<br>SPI-B 器件使能 (STE)<br>输出 X-BAR 输出 4<br>LIN-A 接收<br>SDFM-1 通道 3 时钟输入<br>CAN-A 接收                                              |

| GPIO34<br>OUTPUTXBAR1<br>SPIB_D3<br>CANO_STBY<br>PMBUSA_SDA                                                     | 0, 4, 8, 12<br>1<br>2<br>3<br>6                            | 94     |       |       | I/O<br>0<br>I/O<br>0<br>I/OD                             | 通用输入/输出 34<br>输出 X-BAR 输出 1<br>SPI-B QSPI模式下的第四位数据<br>CANA STBY 输出<br>PMBus-A 开漏双向数据                                                                     |

| GPIO35<br>SCIA_RX<br>I2CA_SDA<br>CANA_RX<br>PMBUSA_SCL<br>LINA_RX<br>EQEP1_A<br>PMBUSA_CTL<br>TDI               | 0, 4, 8, 12<br>1<br>3<br>5<br>6<br>7<br>9<br>10<br>15      | 63     | 39    | 36    | I/O<br>I<br>I/OD<br>I<br>I/OD<br>I<br>I<br>I<br>I        | 通用输入/输出 35<br>SCI-A 接收数据<br>I2C-A 开漏双向数据<br>CAN-A 接收<br>PMBus-A 开漏双向时钟<br>LIN-A 接收<br>eQEP-1 输入 A<br>PMBus-A 控制信号<br>JTAG数据输入。                           |

| GPIO37<br>OUTPUTXBAR2<br>SPIA_D3<br>I2CA_SCL<br>SCIA_TX<br>CANA_TX<br>LINA_TX<br>EQEP1_B<br>PMBUSA_ALERT<br>TDO | 0, 4, 8, 12<br>1<br>2<br>3<br>5<br>6<br>7<br>9<br>10<br>15 | 61     | 37    | 34    | I/O<br>0<br>I/O<br>I/OD<br>0<br>0<br>0<br>I<br>I/OD<br>0 | 通用输入/输出 37<br>输出 X-BAR 输出 2<br>SPI-A QSPI模式下的第四位数据<br>I2C-A 开漏双向时钟<br>SCI-A 发送数据<br>CAN-A 发送<br>LIN-A 发送<br>eQEP-1 输入 B<br>PMBus-A 开漏双向警报信号<br>JTAG数据输出。 |

| GPIO39<br>CANB_RX                                                                                               | 0, 4, 8, 12<br>6                                           | 91     |       |       | I/O<br>I                                                 | 通用输入/输出 39<br>CAN-B 接收                                                                                                                                   |

| GPIO40<br>CANO_STBY<br>PMBUSA_SDA<br>SCIB_TX<br>EQEP1_A                                                         | 0, 4, 8, 12<br>1<br>6<br>9<br>10                           | 85     |       |       | I/O<br>0<br>I/OD<br>0<br>I                               | 通用输入/输出 40<br>CANA STBY 输出<br>PMBus-A 开漏双向数据<br>SCI-B 发送数据<br>eQEP-1 输入 A                                                                                |

| 信号名称           | 多路复用器位置     | 100 PZ | 64 PM | 56RSH | 引脚类型 | 说明                           |

|----------------|-------------|--------|-------|-------|------|------------------------------|

| GPIO41         | 0, 4, 8, 12 |        |       |       | I/O  | 通用输入/输出 41                   |

| SPIA_CLK       | 1           |        |       |       | I/O  | SPI-A 时钟                     |

| SCIB_TX        | 2           |        |       |       | 0    | SCI-B 发送数据                   |

| CANA_RX        | 3           |        |       |       | I    | CAN-A 接收                     |

| EPWM6_A        | 5           |        |       |       | 0    | ePWM-6 输出 A                  |

| I2CA_SCL       | 6           | 48     |       |       | I/OD | I2C-A 开漏双向时钟                 |

| SD1_D2_EQEP2_A | 7           |        |       |       | I    | SDFM-1 通道 2 数据入              |

| PMBUSA_CTL     | 9           |        |       |       | I    | eQEP-2 输入 A                  |

| XCLKOUT        | 10          |        |       |       | I    | PMBus-A 控制信号                 |

|                | 11          |        |       |       | 0    | 外部时钟输出。此引脚从器件中输出所选时钟信号的分频版本。 |

| GPIO42         | 0           |        |       |       | I/O  | 通用输入/输出 42                   |

| GPIO43         | 0           |        |       |       | I/O  | 通用输入/输出 43                   |

| GPIO44         | 0           |        |       |       | I/O  | 通用输入/输出 44                   |

| GPIO45         | 0           |        |       |       | I/O  | 通用输入/输出 45                   |

| GPIO46         | 0           |        |       |       | I/O  | 通用输入/输出 46                   |

| GPIO47         | 0           |        |       |       | I/O  | 通用输入/输出 47                   |

| GPIO48         | 0           |        |       |       | I/O  | 通用输入/输出 48                   |

| GPIO49         | 0           |        |       |       | I/O  | 通用输入/输出 49                   |

| GPIO50         | 0           |        |       |       | I/O  | 通用输入/输出 50                   |

| GPIO51         | 0           |        |       |       | I/O  | 通用输入/输出 51                   |

| GPIO52         | 0           |        |       |       | I/O  | 通用输入/输出 52                   |

| GPIO53         | 0           |        |       |       | I/O  | 通用输入/输出 53                   |

| GPIO54         | 0           |        |       |       | I/O  | 通用输入/输出 54                   |

| GPIO55         | 0           |        |       |       | I/O  | 通用输入/输出 55                   |

| 信号名称                  | 多路复用器位置     | 100 PZ | 64 PM | 56RSH | 引脚类型 | 说明                                                                     |

|-----------------------|-------------|--------|-------|-------|------|------------------------------------------------------------------------|

| GPIO56                | 0, 4, 8, 12 |        |       |       | I/O  | 通用输入/输出 56                                                             |

| SPIA_CLK              | 1           |        |       |       | I/O  | SPI-A 时钟                                                               |

| EQEP2_STROBE          | 5           |        |       |       | I/O  | eQEP-2 选通                                                              |

| SCIB_TX               | 6           | 65     |       |       | 0    | SCI-B 发送数据                                                             |

| SD1_D3                | 7           |        |       |       | I    | SDFM-1 通道 3 数据输入                                                       |

| SPIB_SIMO (QSPI_B_D0) | 9           |        |       |       | I/O  | SPI-B 从器件输入, 主器件输出 (SIMO) 或QSPI模式下的第一位数据                               |

| EQEP1_A               | 11          |        |       |       | I    | eQEP-1 输入 A                                                            |

| GPIO57                | 0, 4, 8, 12 |        |       |       | I/O  | 通用输入/输出 57                                                             |

| SPIA_STE              | 1           |        |       |       | I/O  | SPI-A 器件使能 (STE)                                                       |

| EQEP2_INDEX           | 5           |        |       |       | I/O  | eQEP-2 索引                                                              |

| SCIB_RX               | 6           | 66     |       |       | I    | SCI-B 接收数据                                                             |

| SD1_C3                | 7           |        |       |       | I    | SDFM-1 通道 3 时钟输入                                                       |

| SPIB_SOMI (QSPI_B_D1) | 9           |        |       |       | I/O  | SPI-B 从器件输出, 主器件输入 (SOMI) 或QSPI模式下的第二位数据                               |

| EQEP1_B               | 11          |        |       |       | I    | eQEP-1 输入 B                                                            |

| GPIO58                | 0, 4, 8, 12 |        |       |       | I/O  | 通用输入/输出 58                                                             |

| OUTPUTXBAR1           | 5           |        |       |       | 0    | 输出 X-BAR 输出 1                                                          |

| SPIB_CLK              | 6           |        |       |       | I/O  | SPI-B 时钟                                                               |

| SD1_D4                | 7           | 67     |       |       | I    | SDFM-1 通道 4 数据输入                                                       |

| LINA_TX               | 9           |        |       |       | 0    | LIN-A 发送                                                               |

| CANB_TX               | 10          |        |       |       | 0    | CAN-B 发送                                                               |

| EQEP1_STROBE          | 11          |        |       |       | I/O  | eQEP-1 选通                                                              |

| GPIO59                | 0, 4, 8, 12 |        |       |       | I/O  | 通用输入/输出 59                                                             |

| OUTPUTXBAR2           | 5           |        |       |       | 0    | 输出 X-BAR 输出 2                                                          |

| SPIB_STE              | 6           |        |       |       | I/O  | SPI-B 器件使能 (STE)                                                       |

| SD1_C4                | 7           | 92     |       |       | I    | SDFM-1 通道 4 时钟输入                                                       |

| LINA_RX               | 9           |        |       |       | I    | LIN-A 接收                                                               |

| CANB_RX               | 10          |        |       |       | I    | CAN-B 接收                                                               |

| EQEP1_INDEX           | 11          |        |       |       | I/O  | eQEP-1 索引                                                              |

| test_mode             |             | 49     |       |       | I/O  | 测试引脚。必须保持未连接状态。                                                        |

| TCK                   |             | 60     | 36    | 33    | I    | JTAG 时钟。                                                               |

| TMS                   |             | 62     | 38    | 35    | I/O  | JTAG 模式选择。                                                             |

| VREGENZ               |             | 73     | 46    |       | I    | 具有内部下拉电阻的内部稳压器使能。直接连接到 VSS (低电平) 以启用内部 VREG。直接连接到 VDDIO (高电平) 以使用外部电源。 |

| 信号名称     | 多路复用器位置 | 100 PZ                 | 64 PM                  | 56RSH                  | 引脚类型 | 说明                                                                                                                                                                                                                                                                                                                                                                             |

|----------|---------|------------------------|------------------------|------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X1       |         | 69                     | 42                     | 39                     | I/O  | 晶体振荡器或单端时钟输入。器件初始化软件必须在启用晶体振荡器之前配置该引脚。为了使用此振荡器，必须将一个石英晶体电路连接至 X1 和 X2。此引脚也可用于馈入单端3.3V 电平时钟。不支持 GPIO19。                                                                                                                                                                                                                                                                         |

| XRSn     |         | 2                      | 3                      | 4                      | I/OD | 器件复位（输入）和看门狗复位（输出）。在上电条件下，此引脚由器件驱动为低电平。外部电路也可能会驱动此引脚以使器件复位生效。发生看门狗复位时，此引脚也由 MCU 驱动为低电平。在看门狗复位期间，XRSn 引脚在 512 个 OSCCLK 周期的看门狗复位持续时间内被驱动为低电平。应在 XRSn 和 VDDIO 之间放置一个阻值为 2.2kΩ 至 10kΩ 的电阻。如果在 XRSn 和 VSS 之间放置一个电容器进行噪声滤除，则该电容器的容值应为 100nF 或更小。当看门狗复位生效时，这些值允许看门狗在 512 个 OSCCLK 周期内正确地将 XRSn 引脚驱动至 VOL。这个引脚的输出缓冲器是一个有内部上拉电阻的开漏。如果此引脚由外部器件驱动，则应使用开漏器件进行驱动。如果此引脚由外部器件驱动，则应使用开漏器件进行驱动。 |

| VDD      |         | 4,<br>46,<br>71,<br>87 | 4,<br>27,<br>44,<br>59 | 5,<br>24,<br>41,<br>53 |      | 1.2V 数字逻辑电源引脚。建议在 VDD 引脚与 VSS 之间一个最小总电容值约为 20μF 的去耦电容器。当不使用内部稳压器时，去耦电容的确切值应由您的系统电压调节解决方案来确定。                                                                                                                                                                                                                                                                                   |

| VDDA     |         | 11,<br>34              | 22                     | 20                     |      | 3.3V 模拟电源引脚。在引脚上放置一个最小值为 2.2μF 且连接至 VSSA 的去耦电容器。且该引脚接 600Ω@100MHz 磁珠到 3.3V。                                                                                                                                                                                                                                                                                                    |

| VDDIO    |         | 3,<br>47,<br>70,<br>88 | 28,<br>43,<br>60       | 25,<br>40,<br>54       |      | 3.3V 数字 I/O 电源引脚。在每个引脚上放置一个最小值为 0.1μF 的去耦电容器。                                                                                                                                                                                                                                                                                                                                  |

| VDDIO_SW |         | 80                     | 53                     | 48                     |      | 内部直流/直流稳压器的 3.3V 电源引脚。如果使用内部直流/直流稳压器，则应在该引脚上放置一个 20 μF 的大容量输入电容。务必将该引脚连接至 VDDIO 引脚。如果需要，可以使用铁氧体磁珠进行隔离，但 VDDIO_SW 和 VDDIO 必须由同一电源供电。                                                                                                                                                                                                                                            |

| VSS      |         | 5,<br>45,<br>72,<br>86 | 5,<br>26,<br>45,<br>58 | PAD                    |      | 数字接地                                                                                                                                                                                                                                                                                                                                                                           |

| VSSA     |         | 12, 33                 | 21                     | 19                     |      | 模拟接地                                                                                                                                                                                                                                                                                                                                                                           |

| VSS_SW   |         | 82                     | 55                     | 50                     |      | 内部直流/直流稳压器接地。务必将该引脚连接至 VSS 引脚。                                                                                                                                                                                                                                                                                                                                                 |

(1) 当 DDCDCEN = 1 时，AMSEL 寄存器中的相应位为无关位。

## 4.3 信号描述

### 4.3.1 模拟信号

表 4-2. 模拟信号

| 信号名称     | 说明               | 引脚类型 | GPIO | 100 PZ | 64PM | 56 RSH |

|----------|------------------|------|------|--------|------|--------|

| A0       | ADC-A 输入 0       | I    |      | 23     | 15   | 13     |

| A1       | ADC-A 输入 1       | I    |      | 22     | 14   | 12     |

| A2       | ADC-A 输入 2       | I    |      | 9      | 9    | 8      |

| A3       | ADC-A 输入 3       | I    |      | 10     |      |        |

| A4       | ADC-A 输入 4       | I    |      | 36     | 23   | 21     |

| A5       | ADC-A 输入 5       | I    |      | 35     |      |        |

| A6       | ADC-A 输入 6       | I    |      | 6      | 6    |        |

| A8       | ADC-A 输入 8       | I    |      | 37     |      |        |

| A9       | ADC-A 输入 9       | I    |      | 38     |      |        |

| A10      | ADC-A 输入 10      | I    |      | 40     | 25   | 23     |

| AGPI0224 | ADC 引脚上的数字复用 224 | I/O  |      | 9      | 9    | 8      |

| AGPI0225 | ADC 引脚上的数字复用 225 | I/O  |      | 36     | 23   | 21     |

| AGPI0226 | ADC 引脚上的数字复用 226 | I/O  |      | 7      | 7    | 6      |

| AGPI0227 | ADC 引脚上的数字复用 227 | I/O  |      | 39     | 24   | 22     |

| AGPI0228 | ADC 引脚上的数字复用 228 | I/O  |      | 6      | 6    |        |

| AGPI0229 | ADC 引脚上的数字复用 229 | I/O  |      | 37     |      |        |

| AGPI0230 | ADC 引脚上的数字复用 230 | I/O  |      | 40     | 25   | 23     |

| AGPI0231 | ADC 引脚上的数字复用 231 | I/O  |      | 23     | 15   | 13     |

| AGPI0232 | ADC 引脚上的数字复用 232 | I/O  |      | 22     | 14   | 12     |

| AGPI0233 | ADC 引脚上的数字复用 233 | I/O  |      | 10     |      |        |

| AGPI0234 | ADC 引脚上的数字复用 234 | I/O  |      | 35     |      |        |

| AGPI0236 | ADC 引脚上的数字复用 236 | I/O  |      | 38     |      |        |

| AGPI0237 | ADC 引脚上的数字复用 237 | I/O  |      | 19     | 12   | 10     |

| AGPI0238 | ADC 引脚上的数字复用 238 | I/O  |      | 29     | 18   | 16     |

| AGPI0239 | ADC 引脚上的数字复用 239 | I/O  |      | 17     | 11   |        |

| AGPI0240 | ADC 引脚上的数字复用 240 | I/O  |      | 28     |      |        |

| AGPI0241 | ADC 引脚上的数字复用 241 | I/O  |      | 41     |      |        |

| AGPI0242 | ADC 引脚上的数字复用 242 | I/O  |      | 8      | 8    | 7      |

| AGPI0244 | ADC 引脚上的数字复用 244 | I/O  |      | 21     | 13   | 11     |

| AGPI0245 | ADC 引脚上的数字复用 245 | I/O  |      | 31     | 19   | 17     |

| AGPI0246 | ADC 引脚上的数字复用 246 | I/O  |      | 44     |      |        |

| B0       | ADC-B 输入 0       | I    |      | 41     |      |        |

| B1       | ADC-B 输入 1       | I    |      | 40     | 25   | 23     |

| B2       | ADC-B 输入 2       | I    |      | 7      | 7    | 6      |

| B3       | ADC-B 输入 3       | I    |      | 8      | 8    | 7      |

| B4       | ADC-B 输入 4       | I    |      | 39     | 24   | 22     |

| B6       | ADC-B 输入 6       | I    |      | 9      | 9    | 8      |

| B8       | ADC-B 输入 8       | I    |      | 36     | 23   | 21     |

| B15      | ADC-B 输入 15      | I    |      | 23     | 15   | 13     |

| 信号名称     | 说明                  | 引脚类型 | GPIO | 100 PZ | 64PM | 56 RSH |

|----------|---------------------|------|------|--------|------|--------|

| C0       | ADC-C 输入 0          | I    |      | 19     | 12   | 10     |

| C1       | ADC-C 输入 1          | I    |      | 29     | 18   | 16     |

| C2       | ADC-C 输入 2          | I    |      | 21     | 13   | 11     |

| C3       | ADC-C 输入 3          | I    |      | 31     | 19   | 17     |

| C4       | ADC-C 输入 4          | I    |      | 17     | 11   |        |

| C5       | ADC-C 输入 5          | I    |      | 28     |      |        |

| C6       | ADC-C 输入 6          | I    |      | 7      | 7    | 6      |

| C8       | ADC-C 输入 8          | I    |      | 39     | 24   | 22     |

| C10      | ADC-C 输入 10         | I    |      | 40     | 25   | 23     |

| C14      | ADC-C 输入 14         | I    |      | 44     |      |        |

| C15      | ADC-C 输入 15         | I    |      | 23     | 15   | 13     |

| CMP1_HN0 | CMPSS-1 高电平比较器负输入 0 | I    |      | 10     |      |        |

| CMP1_HN1 | CMPSS-1 高电平比较器负输入 1 | I    |      | 19     | 12   | 10     |

| CMP1_HP0 | CMPSS-1 高电平比较器正输入 0 | I    |      | 9      | 9    | 8      |

| CMP1_HP1 | CMPSS-1 高电平比较器正输入 1 | I    |      | 19     | 12   | 10     |

| CMP1_HP2 | CMPSS-1 高电平比较器正输入 2 | I    |      | 18     | 12   | 10     |

| CMP1_HP3 | CMPSS-1 高电平比较器正输入 3 | I    |      | 10     |      |        |

| CMP1_LN0 | CMPSS-1 低电平比较器负输入 0 | I    |      | 10     |      |        |

| CMP1_LN1 | CMPSS-1 低电平比较器负输入 1 | I    |      | 19     | 12   | 10     |

| CMP1_LP0 | CMPSS-1 低电平比较器正输入 0 | I    |      | 9      | 9    | 8      |

| CMP1_LP1 | CMPSS-1 低电平比较器正输入 1 | I    |      | 19     | 12   | 10     |

| CMP1_LP2 | CMPSS-1 低电平比较器正输入 2 | I    |      | 18     | 12   | 10     |

| CMP1_LP3 | CMPSS-1 低电平比较器正输入 3 | I    |      | 10     |      |        |

| CMP2_HN0 | CMPSS-2 高电平比较器负输入 0 | I    |      | 35     |      |        |

| CMP2_HN1 | CMPSS-2 高电平比较器负输入 1 | I    |      | 29     | 18   | 16     |

| CMP2_HP0 | CMPSS-2 高电平比较器正输入 0 | I    |      | 36     | 23   | 21     |

| CMP2_HP1 | CMPSS-2 高电平比较器正输入 1 | I    |      | 29     | 18   | 16     |

| CMP2_HP2 | CMPSS-2 高电平比较器正输入 2 | I    |      | 30     | 18   | 16     |

| CMP2_HP3 | CMPSS-2 高电平比较器正输入 3 | I    |      | 35     |      |        |

| CMP2_LN0 | CMPSS-2 低电平比较器负输入 0 | I    |      | 35     |      |        |

| CMP2_LN1 | CMPSS-2 低电平比较器负输入 1 | I    |      | 29     | 8    | 7      |

| CMP2_LP0 | CMPSS-2 低电平比较器正输入 0 | I    |      | 36     | 13   | 11     |

| CMP2_LP1 | CMPSS-2 低电平比较器正输入 1 | I    |      | 29     | 7    | 6      |

| CMP2_LP2 | CMPSS-2 低电平比较器正输入 2 | I    |      | 30     | 13   | 11     |

| CMP2_LP3 | CMPSS-2 低电平比较器正输入 3 | I    |      | 35     | 13   | 11     |

| CMP3_HN0 | CMPSS-3 高电平比较器负输入 0 | I    |      | 8      | 8    | 7      |

| CMP3_HN1 | CMPSS-3 高电平比较器负输入 1 | I    |      | 21     | 8    | 7      |

| CMP3_HP0 | CMPSS-3 高电平比较器正输入 0 | I    |      | 7      | 13   | 11     |

| CMP3_HP1 | CMPSS-3 高电平比较器正输入 1 | I    |      | 21     | 7    | 6      |

| CMP3_HP2 | CMPSS-3 高电平比较器正输入 2 | I    |      | 20     | 13   | 11     |

| CMP3_HP3 | CMPSS-3 高电平比较器正输入 3 | I    |      | 8      | 8    | 7      |

| CMP3_LN0 | CMPSS-3 低电平比较器负输入 0 | I    |      | 8      | 8    | 7      |

| 信号名称     | 说明                  | 引脚类型 | GPIO | 100 PZ | 64PM | 56 RSH |

|----------|---------------------|------|------|--------|------|--------|

| CMP3_LN1 | CMPSS-3 低电平比较器负输入 1 | I    |      | 21     | 13   | 11     |

| CMP3_LP0 | CMPSS-3 低电平比较器正输入 0 | I    |      | 7      | 7    | 6      |

| CMP3_LP1 | CMPSS-3 低电平比较器正输入 1 | I    |      | 21     | 13   | 11     |

| CMP3_LP2 | CMPSS-3 低电平比较器正输入 2 | I    |      | 20     | 13   | 11     |

| CMP3_LP3 | CMPSS-3 低电平比较器正输入 3 | I    |      | 8      | 8    | 7      |

| CMP4_HN1 | CMPSS-4 高电平比较器负输入 1 | I    |      | 31     | 19   | 17     |

| CMP4_HP0 | CMPSS-4 高电平比较器正输入 0 | I    |      | 39     | 24   | 22     |

| CMP4_HP1 | CMPSS-4 高电平比较器正输入 1 | I    |      | 31     | 19   | 17     |

| CMP4_HP2 | CMPSS-4 高电平比较器正输入 2 | I    |      | 31     | 19   | 17     |

| CMP4_LN1 | CMPSS-4 低电平比较器负输入 1 | I    |      | 31     | 19   | 17     |

| CMP4_LP0 | CMPSS-4 低电平比较器正输入 0 | I    |      | 39     | 24   | 22     |

| CMP4_LP1 | CMPSS-4 低电平比较器正输入 1 | I    |      | 31     | 19   | 17     |

| CMP4_LP2 | CMPSS-4 低电平比较器正输入 2 | I    |      | 31     | 19   | 17     |

| CMP5_HN1 | CMPSS-5 高电平比较器负输入 1 | I    |      | 17     | 11   |        |

| CMP5_HP0 | CMPSS-5 高电平比较器正输入 0 | I    |      | 6      | 6    |        |

| CMP5_HP1 | CMPSS-5 高电平比较器正输入 1 | I    |      | 17     | 11   |        |

| CMP5_HP2 | CMPSS-5 高电平比较器正输入 2 | I    |      | 16     | 11   |        |

| CMP5_LN1 | CMPSS-5 低电平比较器负输入 1 | I    |      | 17     | 11   |        |

| CMP5_LP0 | CMPSS-5 低电平比较器正输入 0 | I    |      | 6      | 6    |        |

| CMP5_LP1 | CMPSS-5 低电平比较器正输入 1 | I    |      | 17     | 11   |        |

| CMP5_LP2 | CMPSS-5 低电平比较器正输入 2 | I    |      | 16     | 11   |        |

| CMP6_HN0 | CMPSS-6 高电平比较器负输入 0 | I    |      | 38     |      |        |

| CMP6_HN1 | CMPSS-6 高电平比较器负输入 1 | I    |      | 28     |      |        |

| CMP6_HP0 | CMPSS-6 高电平比较器正输入 0 | I    |      | 37     |      |        |

| CMP6_HP1 | CMPSS-6 高电平比较器正输入 1 | I    |      | 28     |      |        |

| CMP6_HP2 | CMPSS-6 高电平比较器正输入 2 | I    |      | 28     |      |        |

| CMP6_HP3 | CMPSS-6 高电平比较器正输入 3 | I    |      | 38     |      |        |

| CMP6_LN0 | CMPSS-6 低电平比较器负输入 0 | I    |      | 38     |      |        |

| CMP6_LN1 | CMPSS-6 低电平比较器负输入 1 | I    |      | 28     |      |        |

| CMP6_LP0 | CMPSS-6 低电平比较器正输入 0 | I    |      | 37     |      |        |

| CMP6_LP1 | CMPSS-6 低电平比较器正输入 1 | I    |      | 28     |      |        |

| CMP6_LP2 | CMPSS-6 低电平比较器正输入 2 | I    |      | 28     |      |        |

| CMP6_LP3 | CMPSS-6 低电平比较器正输入 3 | I    |      | 38     |      |        |

| CMP7_HN0 | CMPSS-7 高电平比较器负输入 0 | I    |      | 41     |      |        |

| CMP7_HN1 | CMPSS-7 高电平比较器负输入 1 | I    |      | 44     |      |        |

| CMP7_HP0 | CMPSS-7 高电平比较器正输入 0 | I    |      | 40     | 25   | 23     |

| CMP7_HP1 | CMPSS-7 高电平比较器正输入 1 | I    |      | 44     |      |        |

| CMP7_HP2 | CMPSS-7 高电平比较器正输入 2 | I    |      | 43     |      |        |

| CMP7_HP3 | CMPSS-7 高电平比较器正输入 3 | I    |      | 41     |      |        |

| CMP7_LN0 | CMPSS-7 低电平比较器负输入 0 | I    |      | 41     |      |        |

| CMP7_LN1 | CMPSS-7 低电平比较器负输入 1 | I    |      | 44     |      |        |

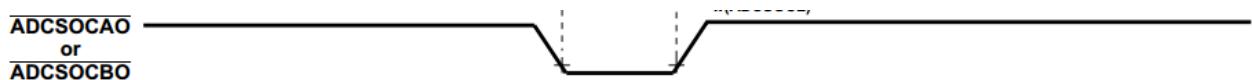

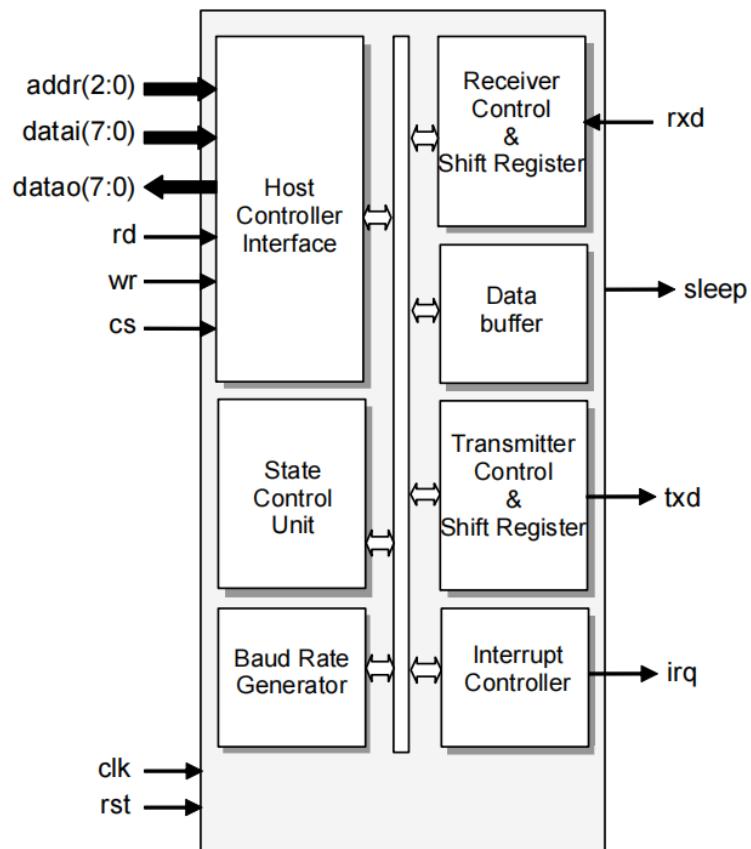

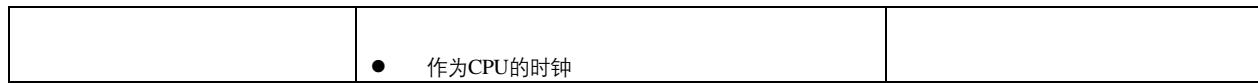

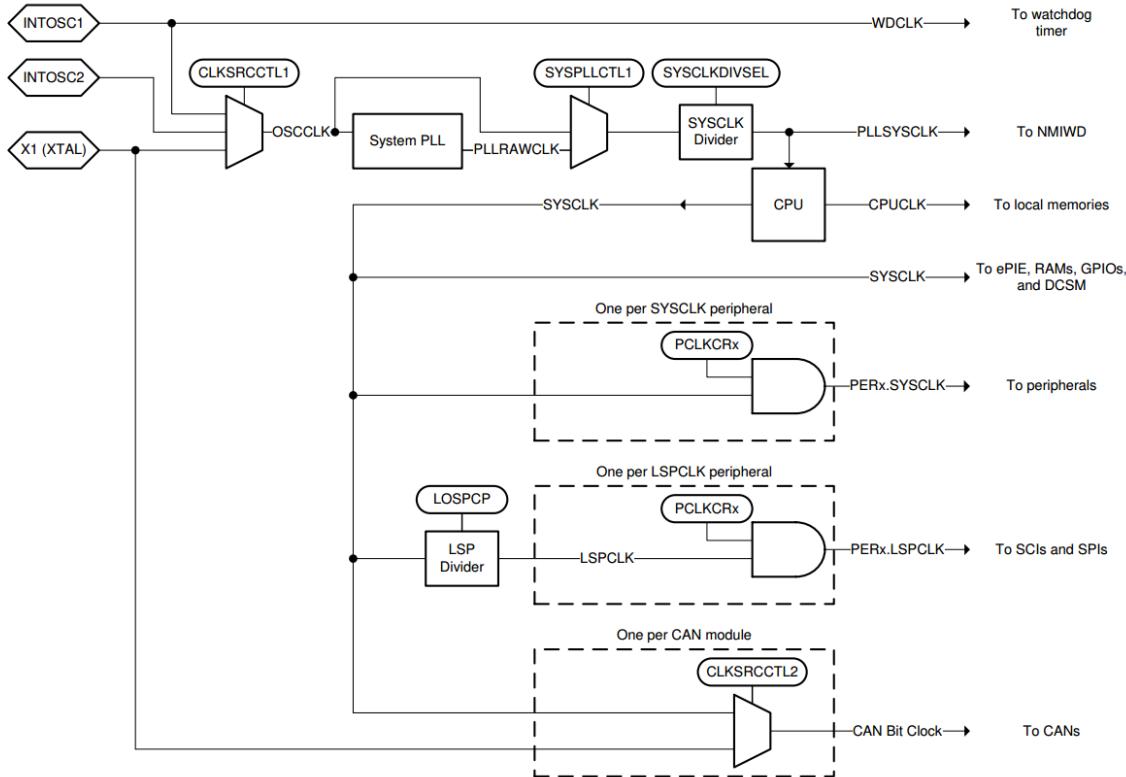

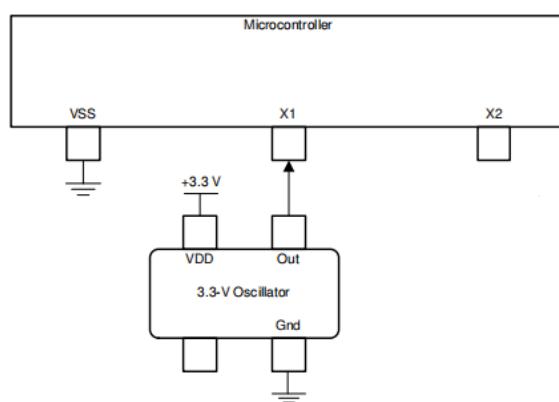

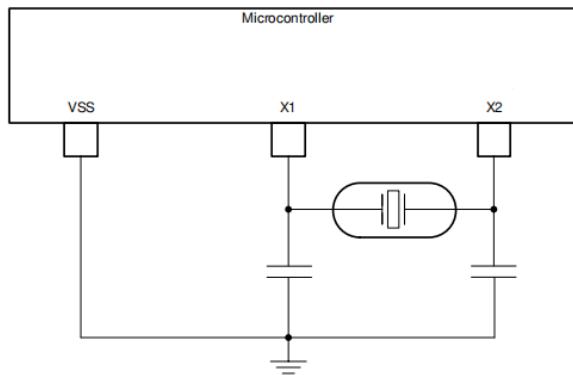

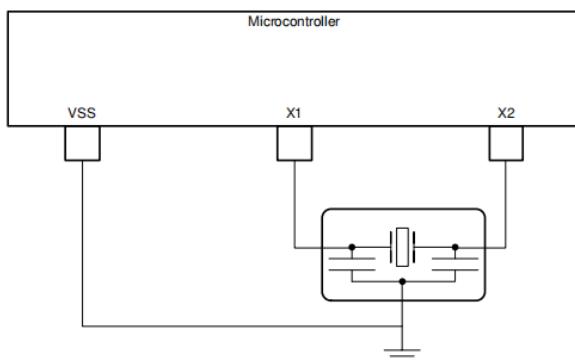

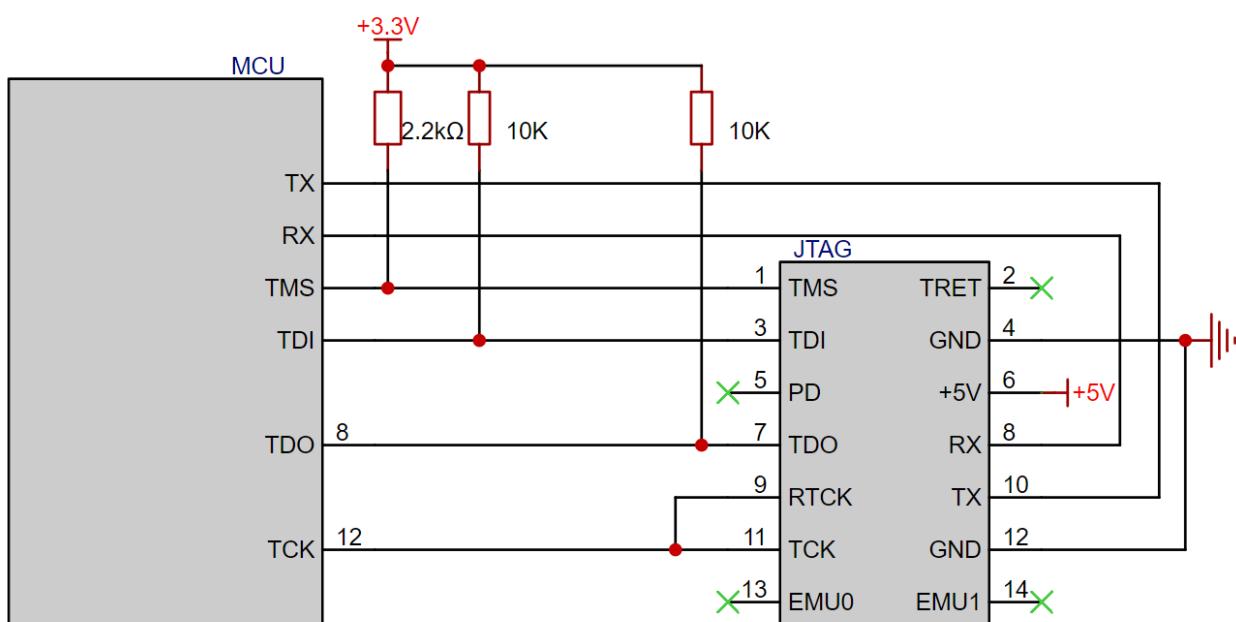

| CMP7_LP0 | CMPSS-7 低电平比较器正输入 0 | I    |      | 40     | 25   | 23     |