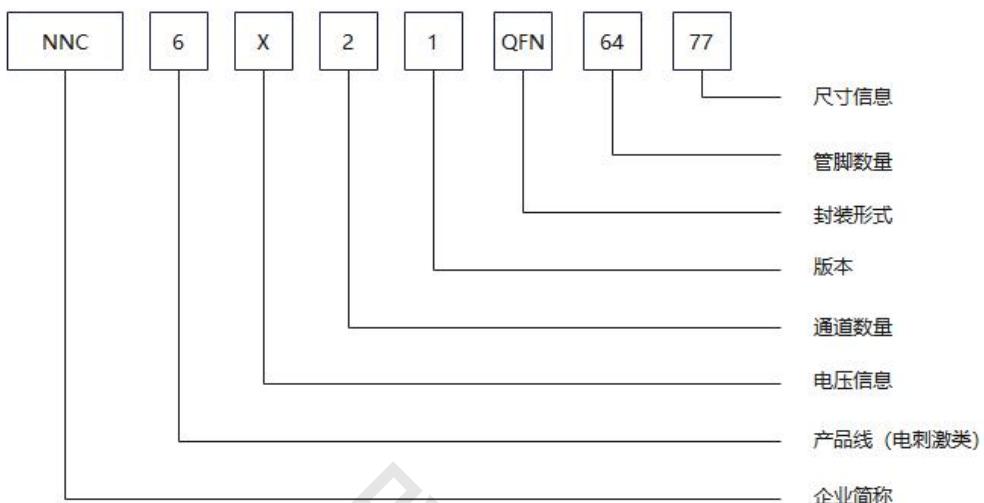

## 可编程通用刺激双通道芯片

## 1 概述

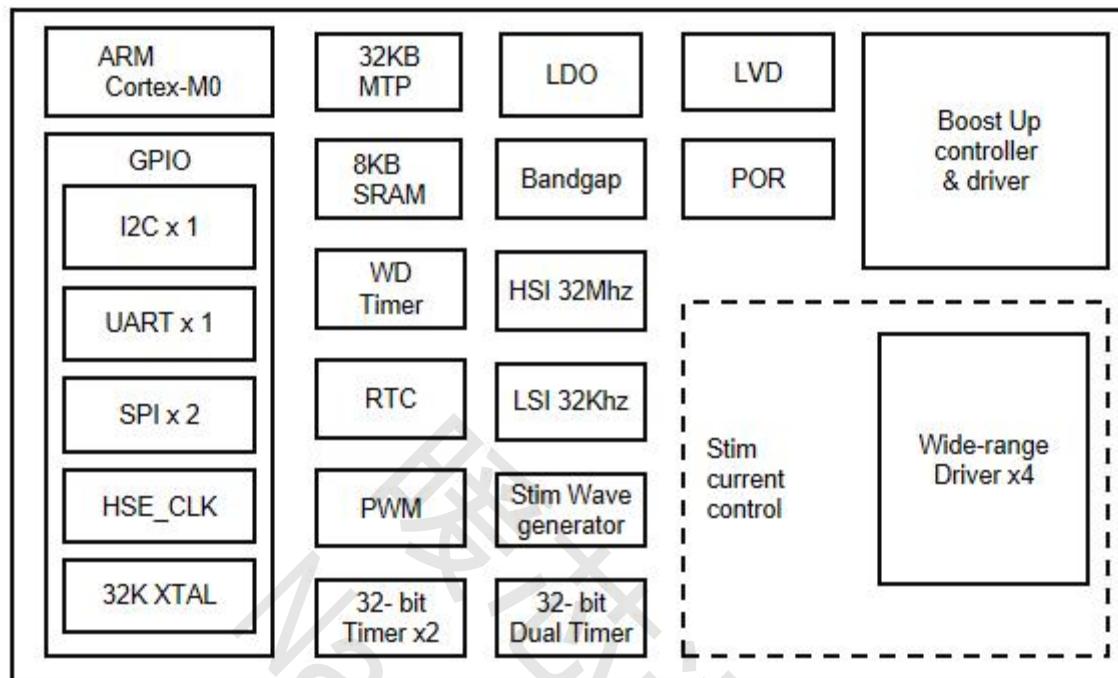

NNC6121 是一款单芯片刺激装置。它集成了一个强大的 ARM 单片机，集成了电源开关，高压升压转换器和高灵活性刺激块。NNC6121 可以用于具有最小的芯片外组件的目标应用程序。刺激器块设计用于单驱动高达 67mA 的双向刺激电流脉冲，如应用需要更大电流请与我们联系。芯片有 2 个高压刺激通道。 NNC6121 生成多种刺激模式来支持各种应用程序。该系统可配置为支持中低频物理治疗、常规 TENS、肌肉康复，可穿戴电刺激等。

## 2 应用

- 肌肉强化与弱肌康复

- 中低频物理治疗

- 可穿戴电刺激设备

## 3 特性

- 工作温度范围：-40°C 至 85°C

- 工作电压范围：3V 至 5V

- ESD：人体放电模式 (HBM) +/-2000V；充电器件模式 (CDM) +/-500V

- 集成式 5~55V 高压升压转换器

- 内核

- 32-位 ARM Cortex-M0 CPU

- 频率可达 32MHz

- 内存

- 32K 字节 MTP 内存

- 8K 字节 SRAM

- 时钟

- HSI RC 4-32MHz

- 高达 32MHz 的外部时钟

- LSI RC 约 32KHz

- 32.768kHz 外部晶振 LSE OSC

- 低功率运行模式

- 睡眠模式

- 低功率运行模式

- 低功率睡眠模式

- 待机模式

- 2 个高范围驱动器（4 个电极）（最大 55V）

- 输出电流：33μA~67mA, 255 步进

- 输出单位电流：33μA~264μA, 8 级（输出单位电流可调，配置方法见 8.2.3.8 章节）

如应用需要更小的单位电流请与我们联系

(可以到 64 级，配置方法见 8.17.1.3 章节)

- 2us~无限宽脉冲

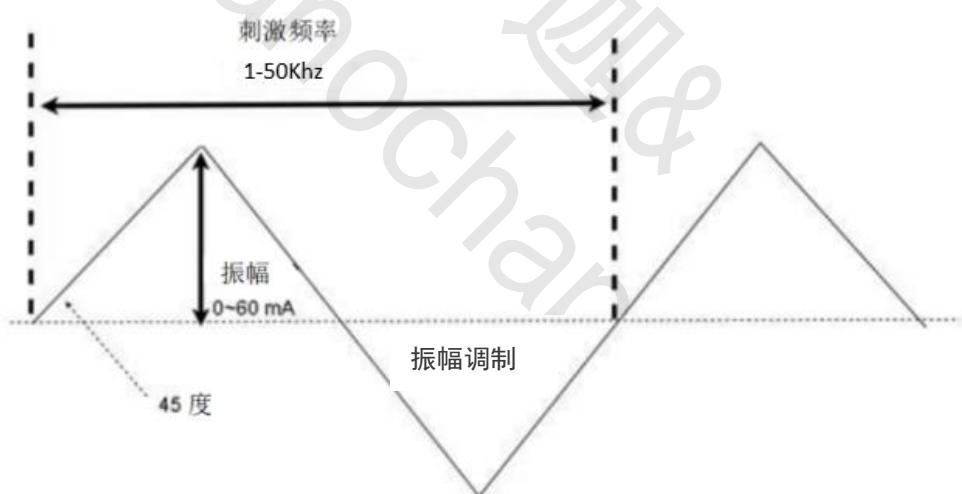

- 高达 50kHz 正弦/三角形/方形或任意波形

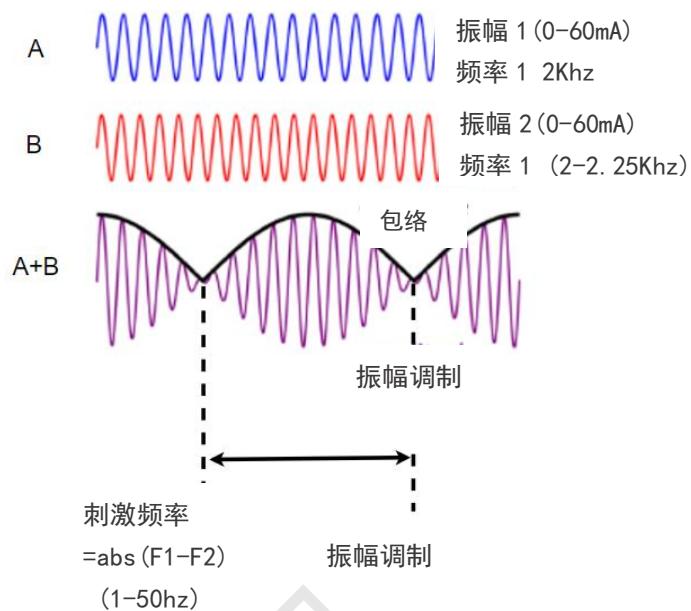

- 可用于 TENS(Transcutaneous Electrical nerve Stimulation, 经皮电刺激)，IFT(Interferential Therapy, 干扰波电疗)，EMS(Electrical Muscle Stimulation, 肌肉电刺激)

- 外设模拟电路

- 通电/断电复位 (POR/PDR)

- 低压检测器 (LVD)

- 脱落检测 (Lead off detector)

- 19GPIOs

- 96-位唯一性标识

- 通信接口

- UARTx1, 硬件流控

- SPIx2, 主/从模式

- I<sup>2</sup>Cx1, 主/从模式

- 各种各样的计时器

- 实时时钟 (RTC)

- 看门狗定时器 (WDT)

- 脉宽调制 (PWM)

- 32-位定时器 x2

- 32-位或 16-位双定时器

- SysTick 定时器

## 4 框图

图 1 原理框图

## 目录

|                                         |    |                             |    |

|-----------------------------------------|----|-----------------------------|----|

| 1 概述 .....                              | 1  | 8.3.3 时钟控制 .....            | 23 |

| 2 应用 .....                              | 1  | 8.3.3.1 时钟树结构 .....         | 23 |

| 3 特性 .....                              | 1  | 8.3.3.2 不同电源模式下的时钟说明 .....  | 24 |

| 4 框图 .....                              | 2  | 8.3.3.3 时钟开关顺序 .....        | 24 |

| 5 器件信息 .....                            | 9  | 8.4 CPU .....               | 33 |

| 6 引脚配置和功能以及升压电路 .....                   | 9  | 8.4.1 概述 .....              | 33 |

| 6.1 引脚与封装定义 .....                       | 9  | 8.4.2 处理器配置 .....           | 33 |

| 6.2 BOOST 升压电路选择 .....                  | 12 | 8.4.3 核寄存器 .....            | 33 |

| 7 规格 .....                              | 13 | 8.4.4 异常和中断 .....           | 34 |

| 7.1 绝对最大额定值 .....                       | 13 | 8.4.5 调试 .....              | 36 |

| 7.2 ESD 额定值 .....                       | 13 | 8.5 Cortex-M0 外设 .....      | 37 |

| 7.3 建议的工作条件 .....                       | 13 | 8.5.1 概述 .....              | 37 |

| 8 详细功能描述 .....                          | 14 | 8.5.2 嵌套矢量中断控制器 .....       | 37 |

| 8.1 内存 .....                            | 14 | 8.5.2.1 寄存器 .....           | 37 |

| 8.1.1 内存映射 .....                        | 14 | 8.5.3 系统控制块 .....           | 39 |

| 8.1.2 嵌入式 SRAM .....                    | 15 | 8.5.4 SysTick 定时器 .....     | 43 |

| 8.1.3 启动配置 .....                        | 15 | 8.5.4.1 寄存器 .....           | 43 |

| 8.2 多次编程存储器 (MTP) .....                 | 15 | 8.6 通用输入/输出 (GPIO) .....    | 45 |

| 8.2.1 概述 .....                          | 15 | 8.6.1 概述 .....              | 45 |

| 8.2.1.1 功能列表 .....                      | 16 | 8.6.1.1 功能列表 .....          | 45 |

| 8.2.2 框图 .....                          | 16 | 8.6.2 功能描述 .....            | 45 |

| 8.2.3 功能描述 .....                        | 17 | 8.6.2.1 三态数字 I/O 单元 .....   | 45 |

| 8.2.3.1 支持的用户操作方式 .....                 | 17 | 8.6.2.2 替代功能多路复用器 .....     | 46 |

| 8.2.3.2 在 MTP 块中的扇区写入操作的定义 .....        | 17 | 8.6.2.3 输入配置 .....          | 47 |

| 8.2.3.3 MTP 块中引导加载扇区的定义 .....           | 18 | 8.6.2.4 输出配置 .....          | 47 |

| 8.2.3.4 信息块中的 trim 和 ID 配置信息区域的定义 ..... | 18 | 8.6.2.5 模拟功能 .....          | 47 |

| 8.2.3.5 信息块中的用户配置信息区域的定义 .....          | 18 | 8.6.2.6 I/O 数据按位处理 .....    | 47 |

| 8.2.3.6 MTP 用户访问权限 .....                | 18 | 8.6.3 寄存器 .....             | 48 |

| 8.2.3.7 时序参数 .....                      | 19 | 8.7 扩展中断和事件控制器 (EXTI) ..... | 55 |

| 8.2.3.8 MTP 单元电流配置 .....                | 20 | 8.7.1 概述 .....              | 55 |

| 8.3 系统控制器 (SCU) .....                   | 21 | 8.7.1.1 功能列表 .....          | 55 |

| 8.3.1 PMU .....                         | 21 | 8.7.2 功能描述 .....            | 55 |

| 8.3.2 复位控制 .....                        | 22 |                             |    |

|                              |    |                             |     |

|------------------------------|----|-----------------------------|-----|

| 8.7.2.1 EXTI 连接 .....        | 55 | 8.10.2.2 I2C 从模式 .....      | 99  |

| 8.7.2.2 EXTI 可配置事件输入唤醒 ..... | 56 | 8.10.2.3 I2C 主模式 .....      | 100 |

| 8.7.2.3 EXTI 直接事件输入唤醒 .....  | 56 | 8.10.2.4 错误条件 .....         | 101 |

| 8.7.3 寄存器 .....              | 57 | 8.10.2.5 I2C 中断 .....       | 102 |

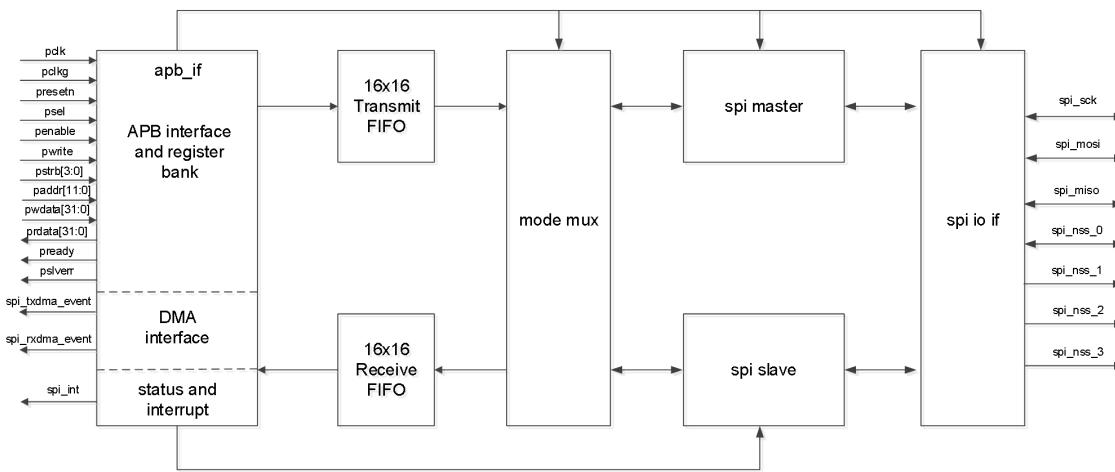

| 8.8 串行外设接口 (SPI) .....       | 59 | 8.10.3 寄存器 .....            | 103 |

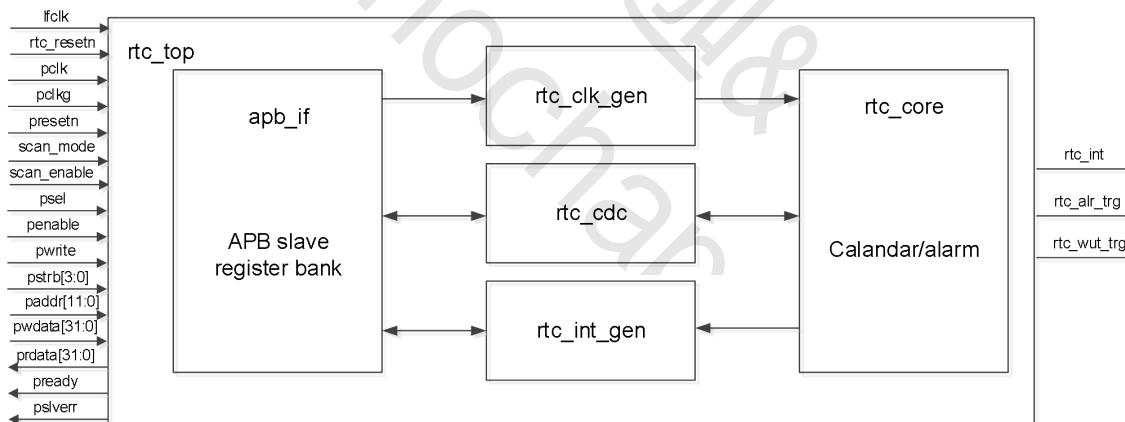

| 8.8.1 概述 .....               | 59 | 8.11 实时时钟 (RTC) .....       | 108 |

| 8.8.1.1 功能列表 .....           | 59 | 8.11.1 概述 .....             | 108 |

| 8.8.2 框图 .....               | 60 | 8.11.1.1 功能列表 .....         | 108 |

| 8.8.3 功能描述 .....             | 61 | 8.11.2 框图 .....             | 108 |

| 8.8.3.1 SPI 引脚 .....         | 61 | 8.11.3 功能描述 .....           | 109 |

| 8.8.3.2 通信 .....             | 61 | 8.11.3.1 时钟和预分频器 .....      | 109 |

| 8.8.3.3 SPI 配置 .....         | 67 | 8.11.3.2 实时时钟和日历 .....      | 109 |

| 8.8.3.4 序列处理 .....           | 68 | 8.11.3.3 时间/日历/闹钟数据模式 ..... | 109 |

| 8.8.4 寄存器 .....              | 70 | 8.11.3.4 可编程闹钟 .....        | 110 |

| 8.9 通用异步接收发送器 (UART) .....   | 76 | 8.11.3.5 周期性唤醒 .....        | 110 |

| 8.9.1 概述 .....               | 76 | 8.11.3.6 初始化与配置 .....       | 110 |

| 8.9.1.1 功能列表 .....           | 76 | 8.11.4 寄存器 .....            | 112 |

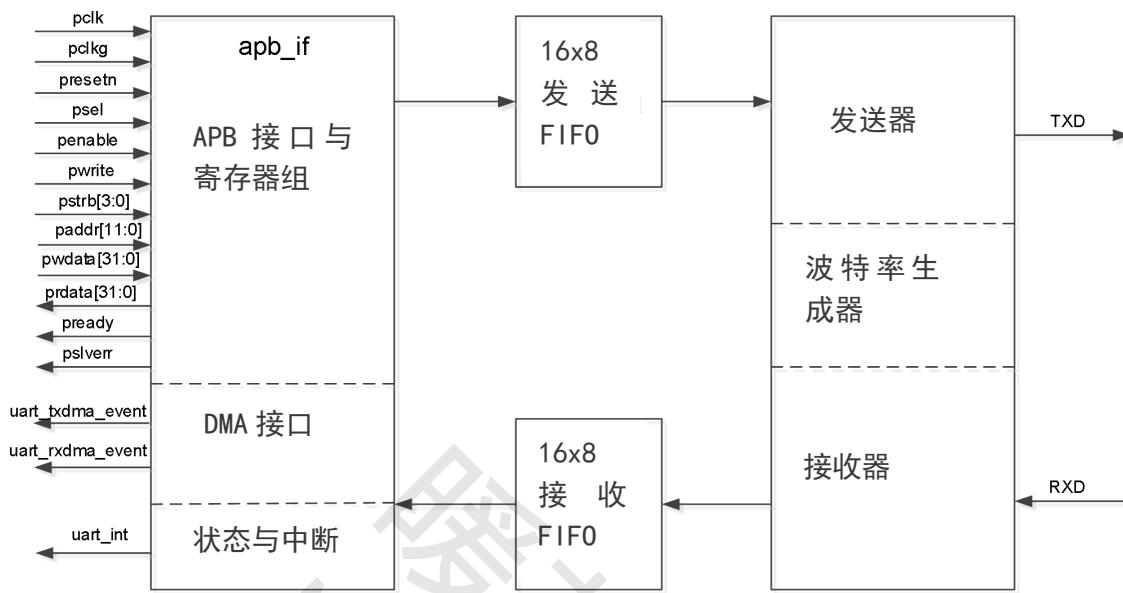

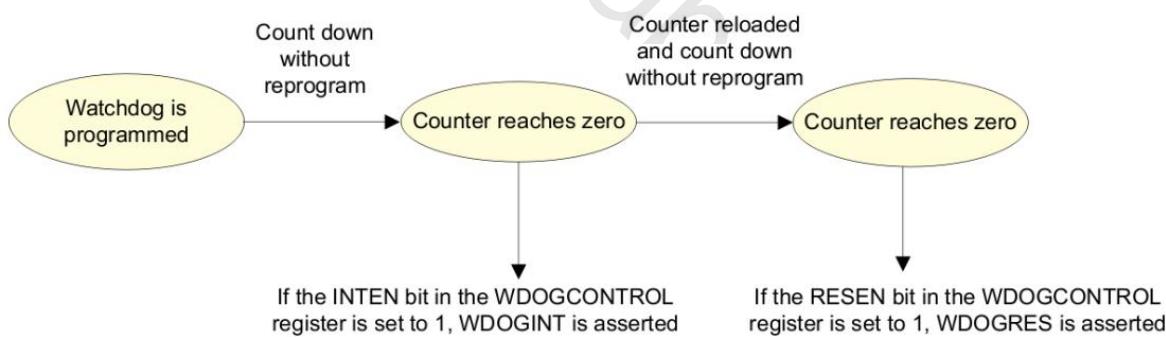

| 8.9.2 框图 .....               | 77 | 8.12 看门狗定时器 (WDT) .....     | 116 |

| 8.9.3 功能描述 .....             | 77 | 8.12.1 概述 .....             | 116 |

| 8.9.3.1 波特率控制 .....          | 77 | 8.12.1.1 功能列表 .....         | 116 |

| 8.9.3.2 协议描述 .....           | 77 | 8.12.2 流程图 .....            | 116 |

| 8.9.3.3 FIFO 模式 .....        | 79 | 8.12.3 功能描述 .....           | 116 |

| 8.9.3.4 自动硬件流控 .....         | 80 | 8.12.3.1 时钟配置 .....         | 116 |

| 8.9.3.5 回环控制 .....           | 81 | 8.12.3.2 操作 .....           | 117 |

| 8.9.3.6 复位 .....             | 81 | 8.12.4 寄存器 .....            | 118 |

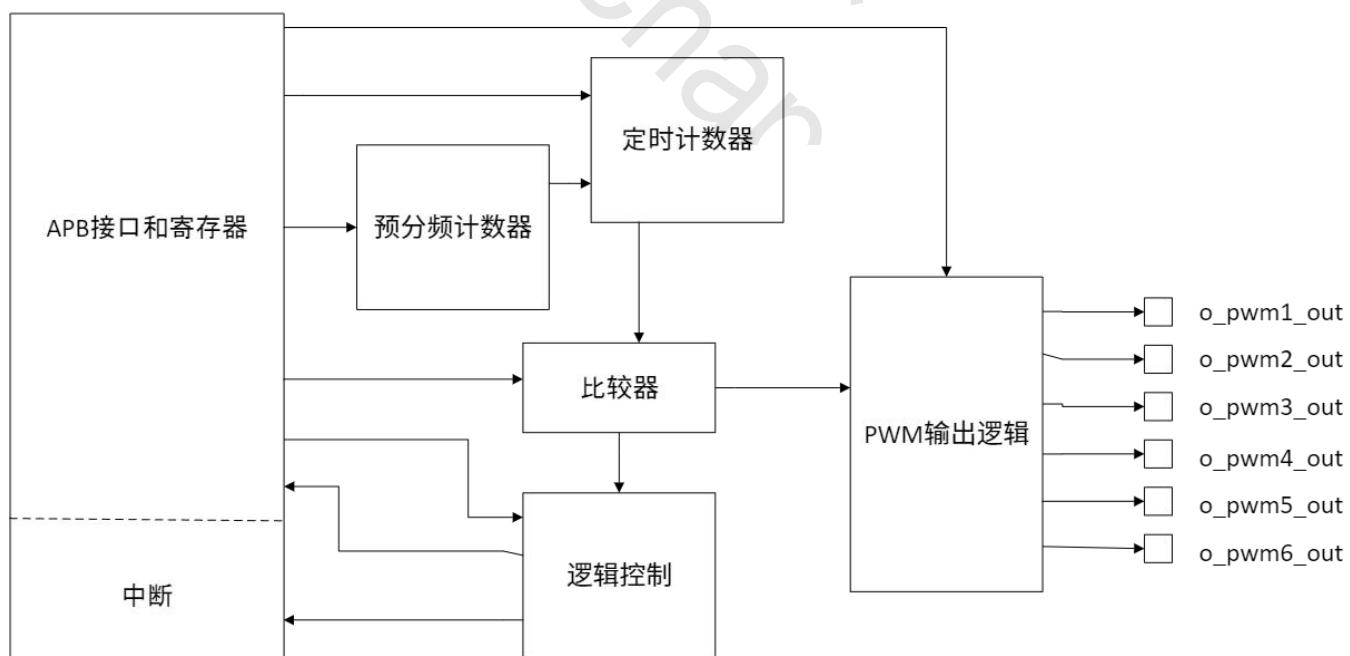

| 8.9.3.7 初始化 .....            | 81 | 8.13 脉冲宽度调制 (PWM) .....     | 121 |

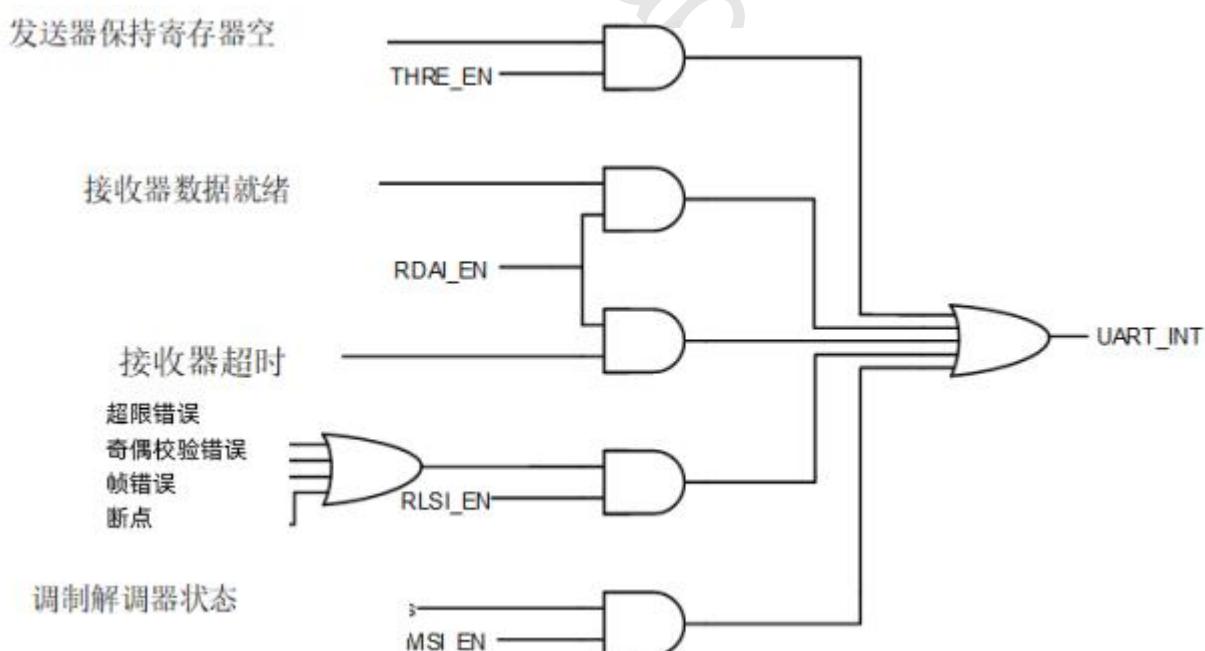

| 8.9.3.8 中断支持 .....           | 81 | 8.13.1 概述 .....             | 121 |

| 8.9.4 寄存器 .....              | 83 | 8.13.1.1 功能列表 .....         | 121 |

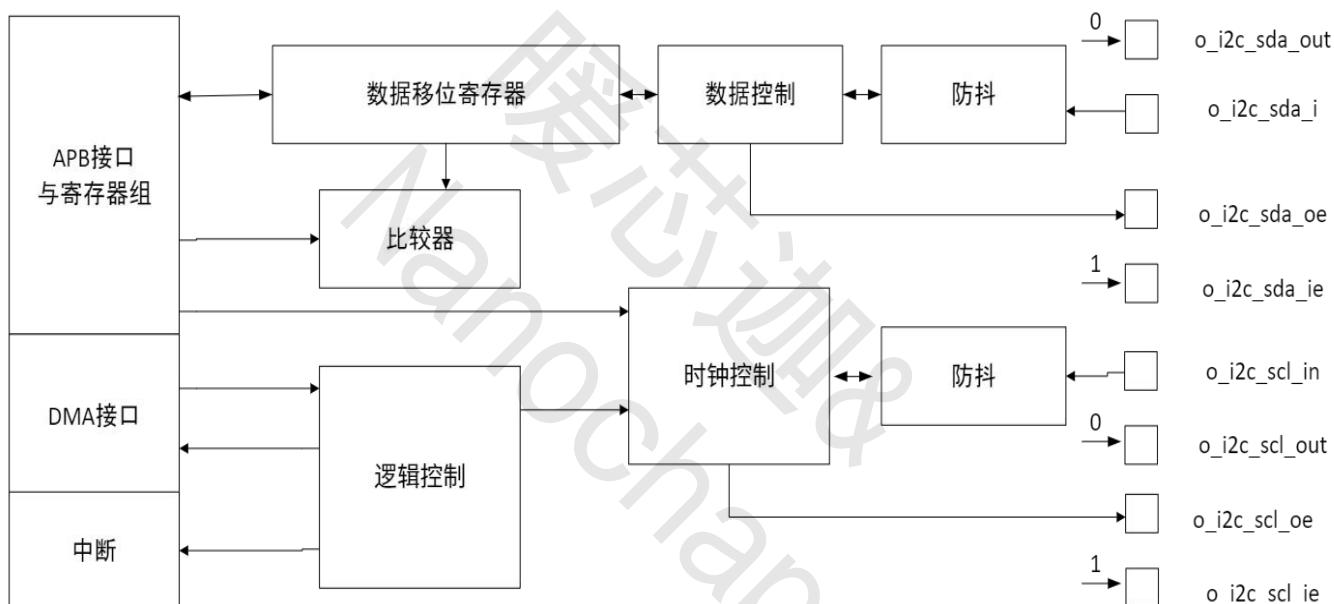

| 8.10 集成电路间接口 (I2C) .....     | 98 | 8.13.2 框图 .....             | 121 |

| 8.10.1 概述 .....              | 98 | 8.13.3 功能描述 .....           | 122 |

| 8.10.1.1 功能列表 .....          | 98 | 8.13.3.1 单边缘控制 PWM 输出 ..... | 122 |

| 8.10.2 功能描述 .....            | 99 | 8.13.3.2 双边缘控制 PWM 输出 ..... | 122 |

| 8.10.2.1 支持模式 .....          | 99 | 8.13.4 寄存器 .....            | 123 |

|                        |     |                           |     |

|------------------------|-----|---------------------------|-----|

| 8.14 定时器 .....         | 129 | 8.16.1 脱落检测 .....         | 139 |

| 8.14.1 概述 .....        | 129 | 8.16.2 寄存器 .....          | 140 |

| 8.14.1.1 功能列表 .....    | 129 | 8.17 电刺激模块 .....          | 146 |

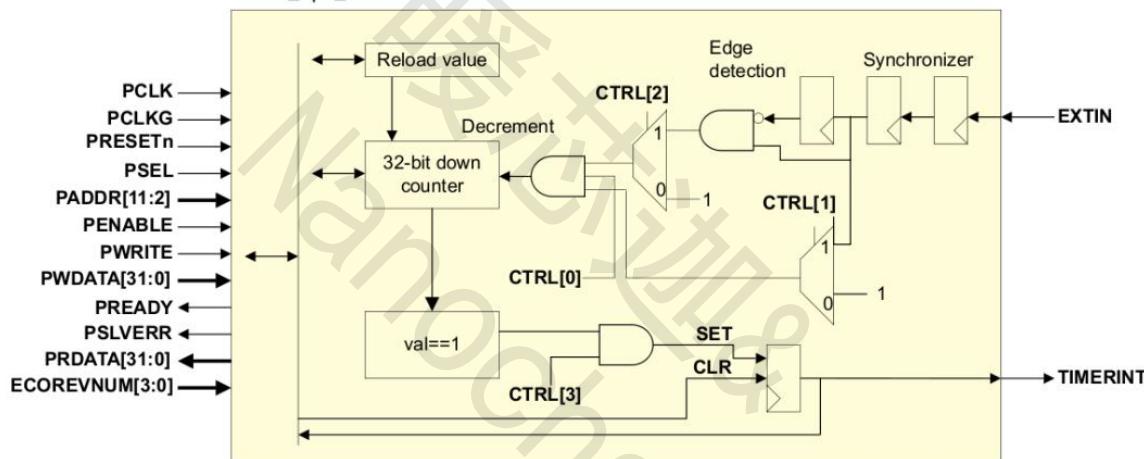

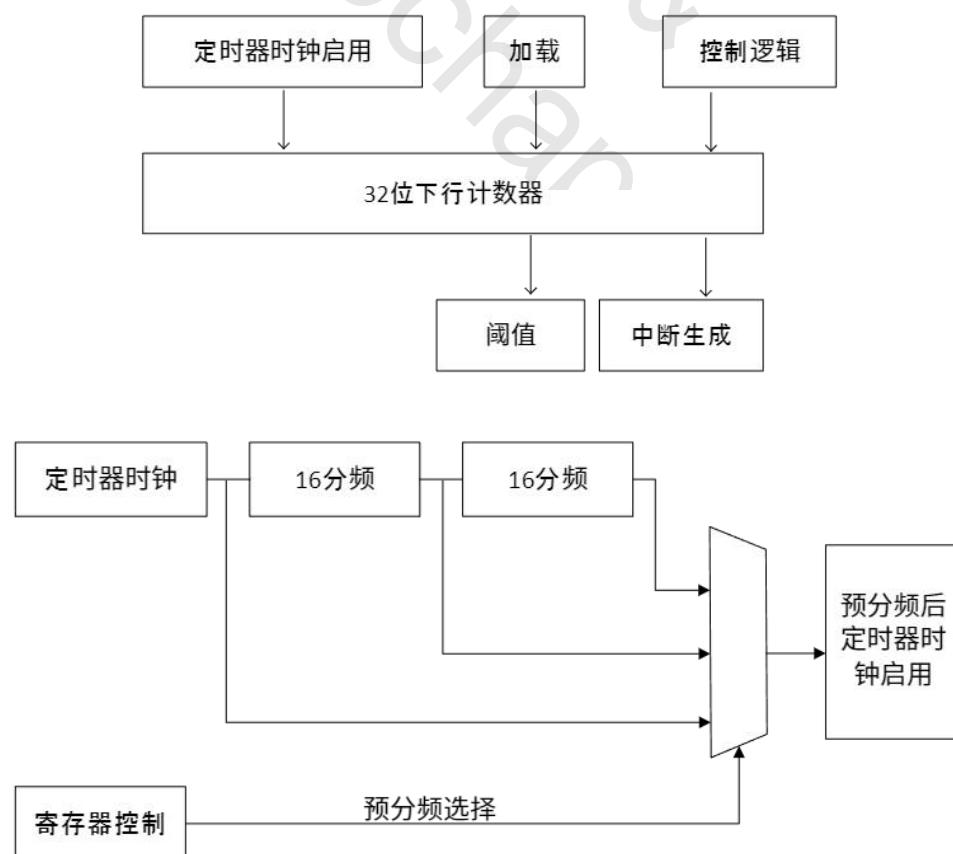

| 8.14.2 框图 .....        | 129 | 8.17.1 任意波发生器 (AWG) ..... | 146 |

| 8.14.3 功能描述 .....      | 129 | 8.17.1.1 概述 .....         | 146 |

| 8.14.4 寄存器 .....       | 130 | 8.17.1.2 模块架构 .....       | 146 |

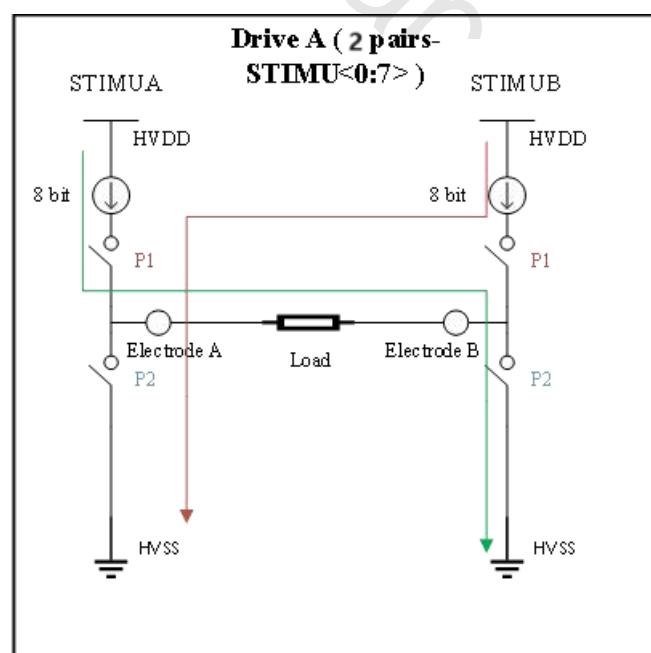

| 8.15 双定时器 .....        | 131 | 8.17.1.2.1 驱动器 A .....    | 146 |

| 8.15.1 概述 .....        | 131 | 8.17.1.3 波形寄存器 .....      | 147 |

| 8.15.1.1 功能列表 .....    | 131 | 8.17.1.4 设计规格 .....       | 149 |

| 8.15.2 框图 .....        | 131 | 8.17.1.5 模块设计 .....       | 149 |

| 8.15.3 功能描述 .....      | 132 | 8.17.2 刺激参数 .....         | 150 |

| 8.15.3.1 自由运行模式 .....  | 132 | 8.17.2.1 高范围驱动器 .....     | 150 |

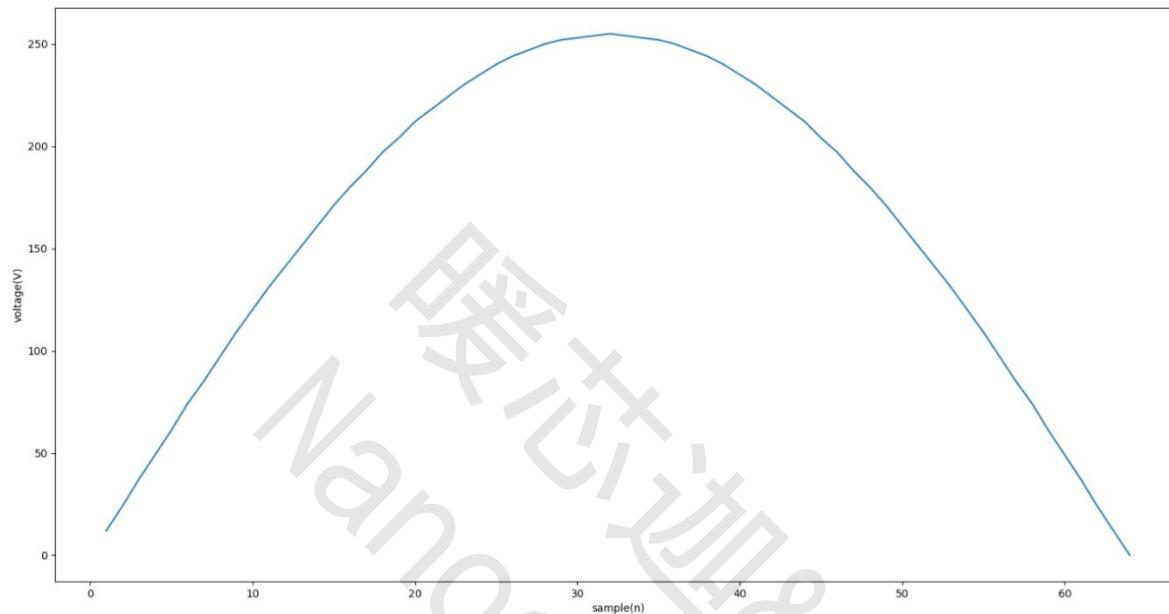

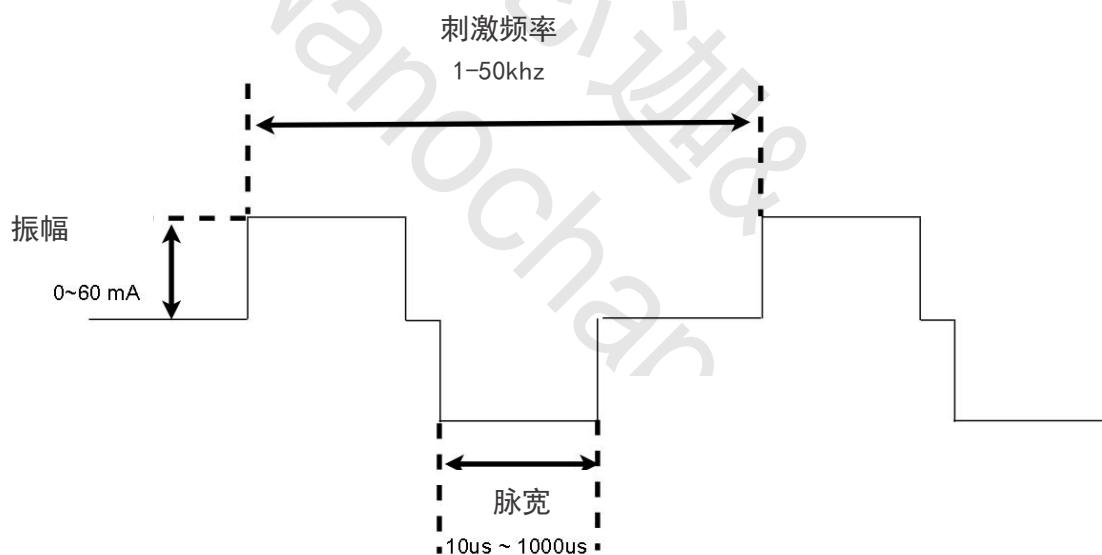

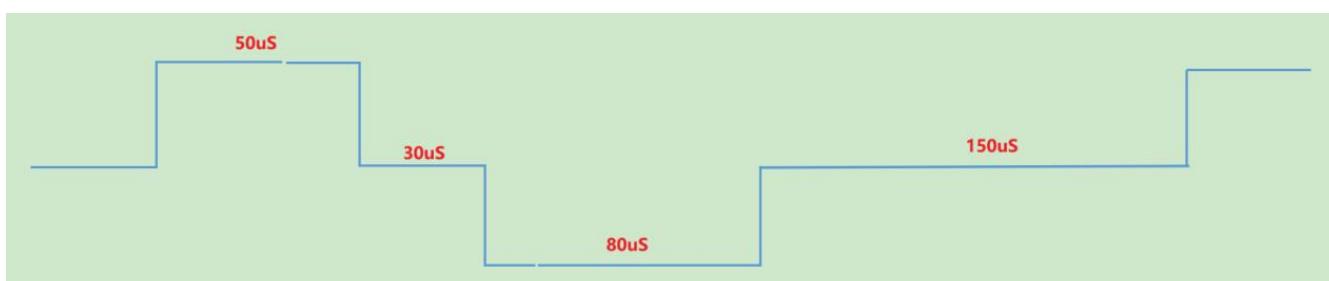

| 8.15.3.2 周期定时器模式 ..... | 132 | 8.17.2.2 波形示例 .....       | 150 |

| 8.15.3.3 单次定时器模式 ..... | 132 | 9 典型应用电路 .....            | 152 |

| 8.15.3.4 操作 .....      | 132 | 10 注意事项 .....             | 155 |

| 8.15.4 寄存器 .....       | 134 | 11 详细封装信息 .....           | 156 |

| 8.16 模拟控制 (ANAC) ..... | 139 | 12 订购信息 .....             | 158 |

## 表格一览表

|                             |    |                         |     |

|-----------------------------|----|-------------------------|-----|

| 表 1 器件信息 .....              | 9  | 表 20 GPIO 寄存器 .....     | 48  |

| 表 2 芯片管脚功能 (64QFN7X7) ..... | 10 | 表 21 EXTI 线连接 .....     | 56  |

| 表 3 启动模式 .....              | 15 | 表 22 EXTI 寄存器 .....     | 57  |

| 表 4 用户操作模式 .....            | 17 | 表 23 SPI 寄存器 .....      | 70  |

| 表 5 MTP 块存储器阵列配置 .....      | 17 | 表 24 UART 字符时间 .....    | 80  |

| 表 6 用户配置信息定义 .....          | 18 | 表 25 UART 中断源 .....     | 82  |

| 表 7 MTP 访问权限 .....          | 18 | 表 26 UART 寄存器 .....     | 83  |

| 表 8 低功耗模式汇总 .....           | 21 | 表 27 中断表 .....          | 102 |

| 表 9 取决于工作模式的功能 .....        | 22 | 表 28 I2C 寄存器 .....      | 103 |

| 表 10 不同电源模式下的时钟描述 .....     | 24 | 表 29 RTC 数据模式 .....     | 109 |

| 表 11 SYSCtrl 寄存器 .....      | 25 | 表 30 RTC 寄存器 .....      | 112 |

| 表 12 处理器配置 .....            | 33 | 表 31 WDT 寄存器 .....      | 118 |

| 表 13 核寄存器 .....             | 33 | 表 32 PWM 寄存器 .....      | 123 |

| 表 14 中断向量表 .....            | 35 | 表 33 定时器寄存器 .....       | 130 |

| 表 15 核外设寄存器区 .....          | 37 | 表 34 双定时器寄存器 .....      | 134 |

| 表 16 NVIC 寄存器 .....         | 37 | 表 35 COMPO 引脚和寄存器 ..... | 139 |

| 表 17 SCB 寄存器 .....          | 39 | 表 36 COMP1 引脚和寄存器 ..... | 139 |

| 表 18 SysTick 定时器寄存器 .....   | 43 | 表 37 模拟控制寄存器 .....      | 140 |

| 表 19 逻辑操作表 .....            | 46 |                         |     |

## 插图目录

|                              |    |                      |     |

|------------------------------|----|----------------------|-----|

| 图 1 原理框图 .....               | 2  | 图 18 UART 中断输出 ..... | 82  |

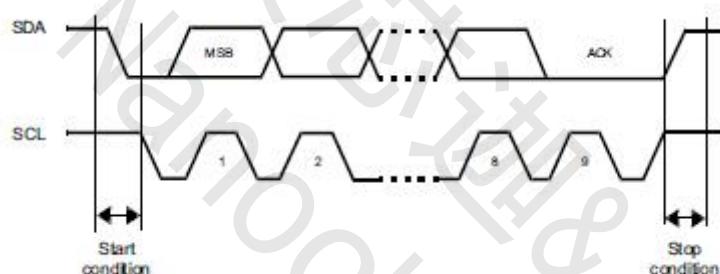

| 图 2 芯片原理图 .....              | 9  | 图 19 I2C 总线协议 .....  | 98  |

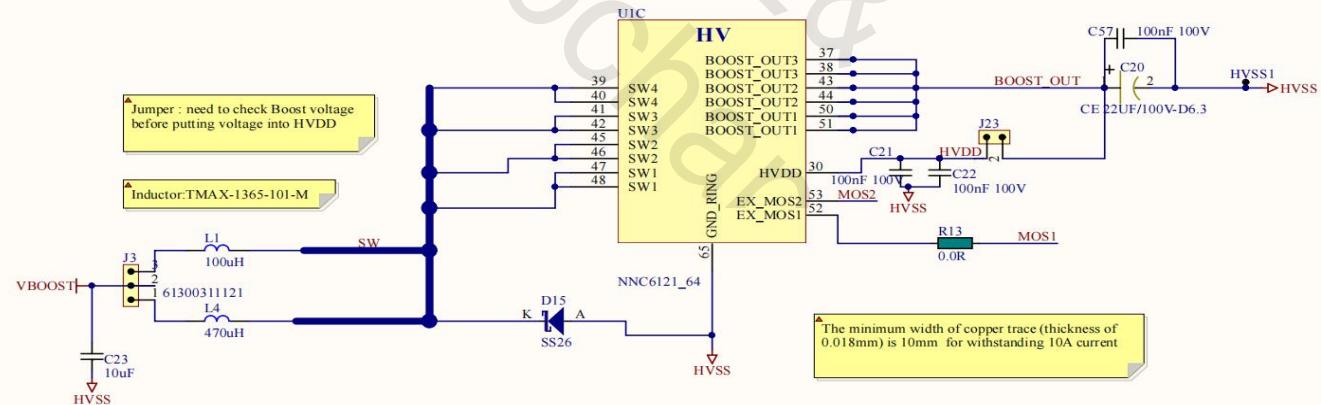

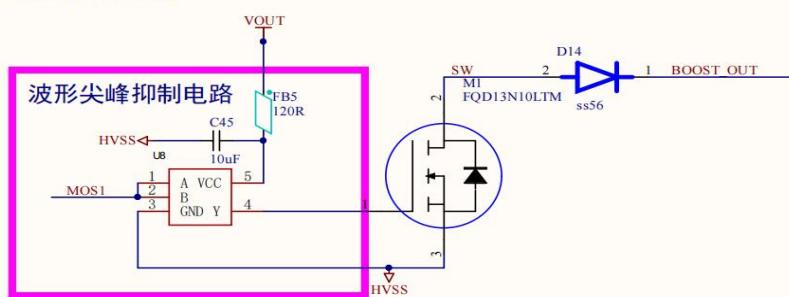

| 图 3 内置 MOS 升压电路图 .....       | 12 | 图 20 I2C 框图 .....    | 99  |

| 图 4 外置 MOS 升压模块电路图 .....     | 12 | 图 21 RTC 框图 .....    | 108 |

| 图 5 内存映射图 .....              | 14 | 图 22 WDT 流程图 .....   | 116 |

| 图 6 MTP 框图 .....             | 16 | 图 23 PWM 框图 .....    | 121 |

| 图 7 时钟树 .....                | 23 | 图 24 定时器框图 .....     | 129 |

| 图 8 I/O 单元功能示意图 .....        | 46 | 图 25 双定时器框图 .....    | 131 |

| 图 9 SPI 框图 .....             | 60 | 图 26 方波形 .....       | 150 |

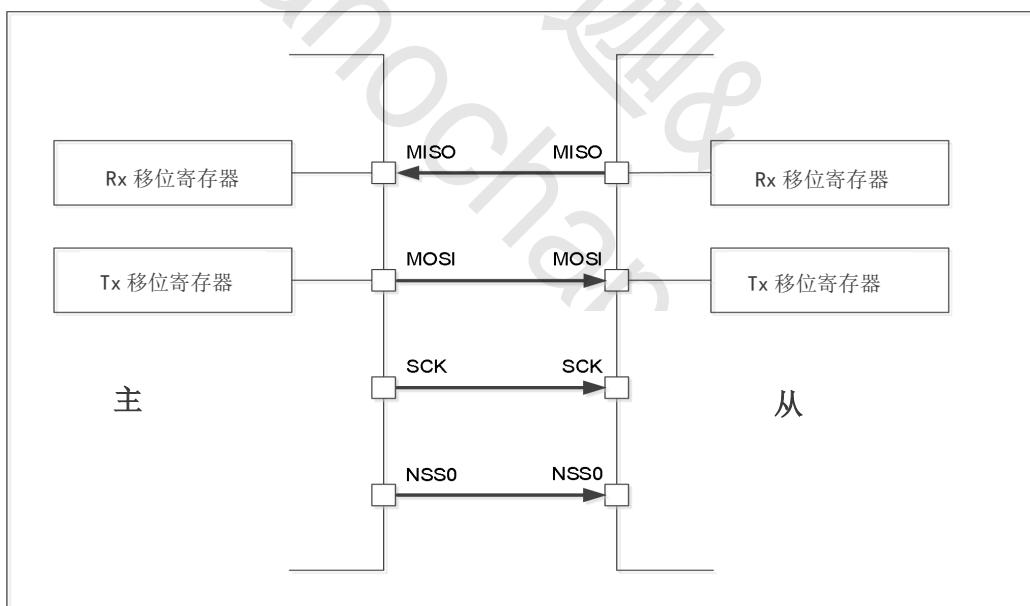

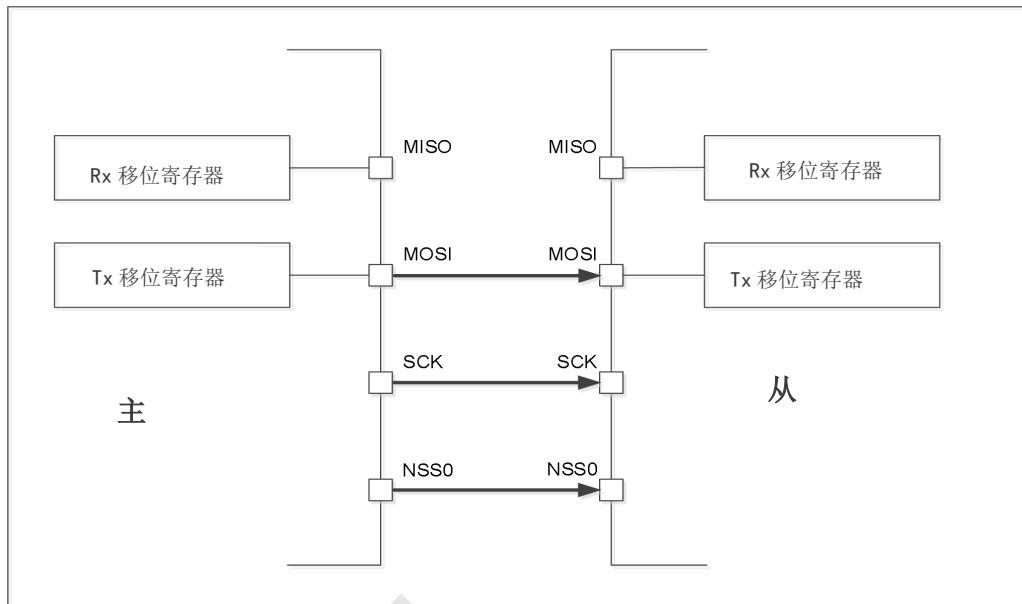

| 图 10 全双工的应用程序 .....          | 61 | 图 27 正弦波形 .....      | 151 |

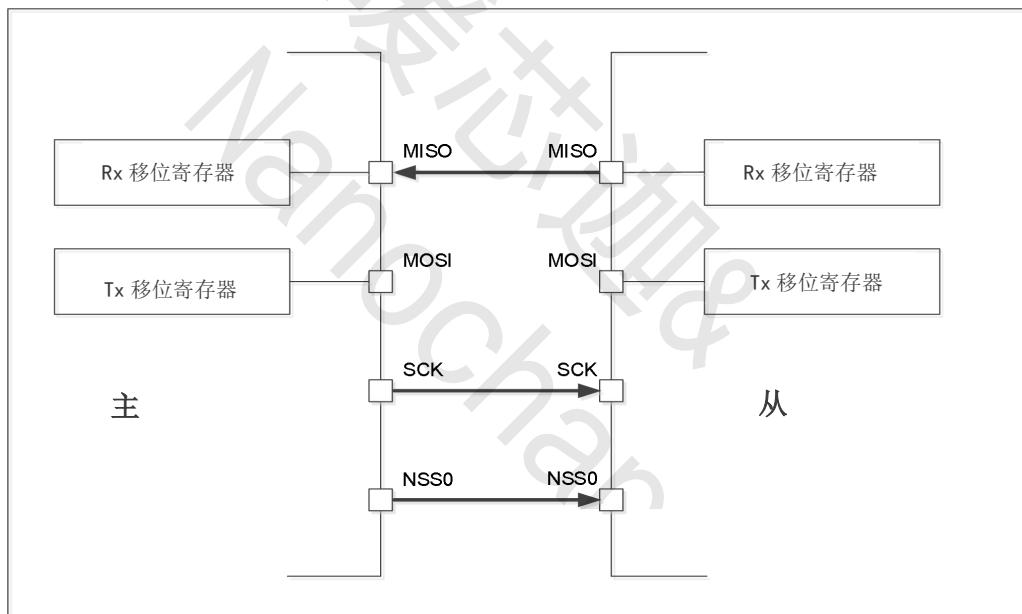

| 图 11 半双工传输应用 .....           | 62 | 图 28 三角波形 .....      | 151 |

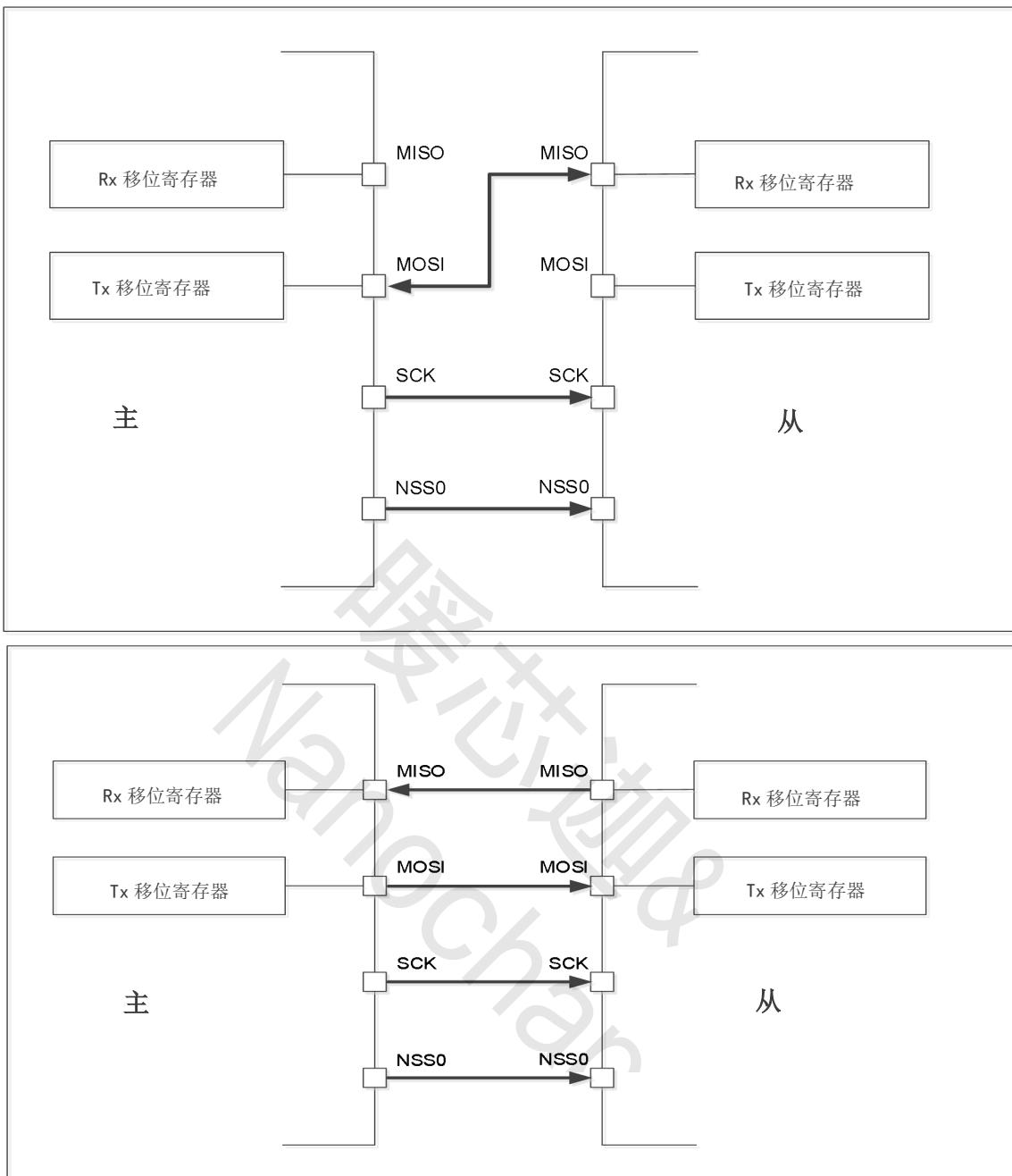

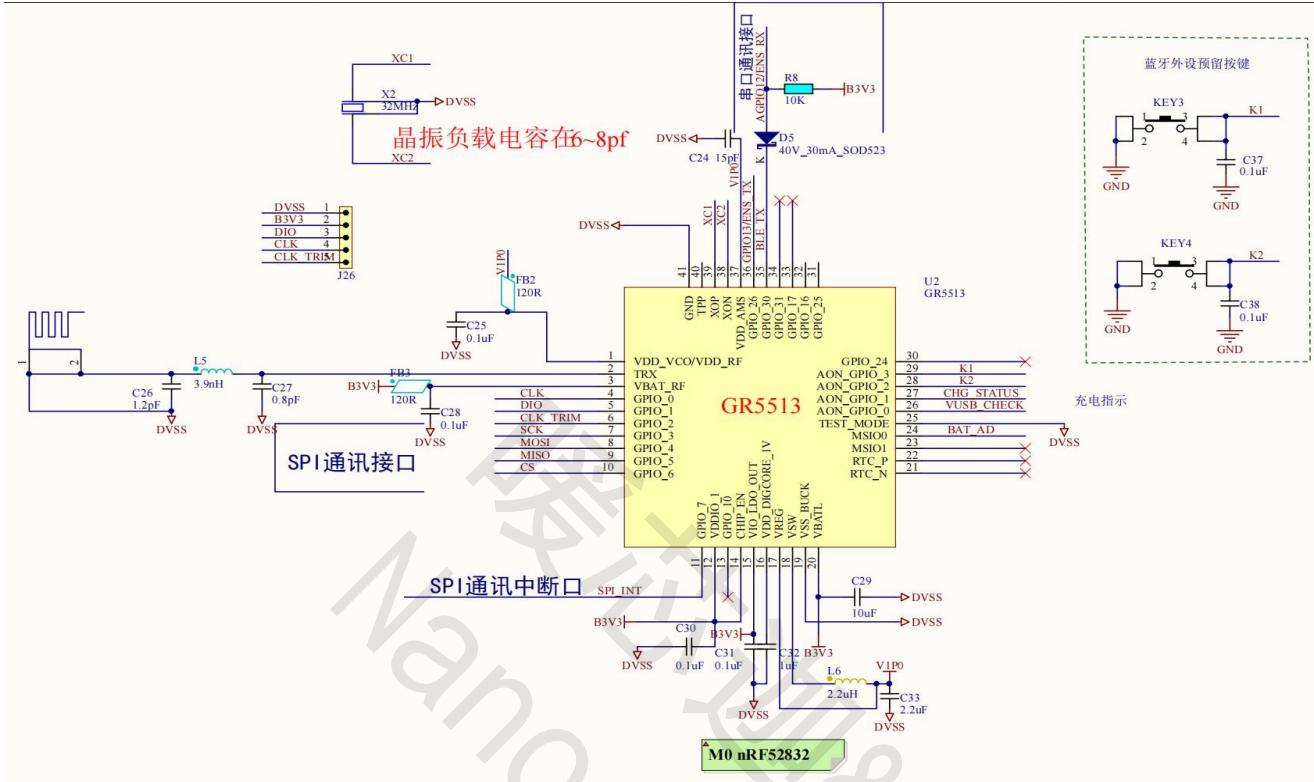

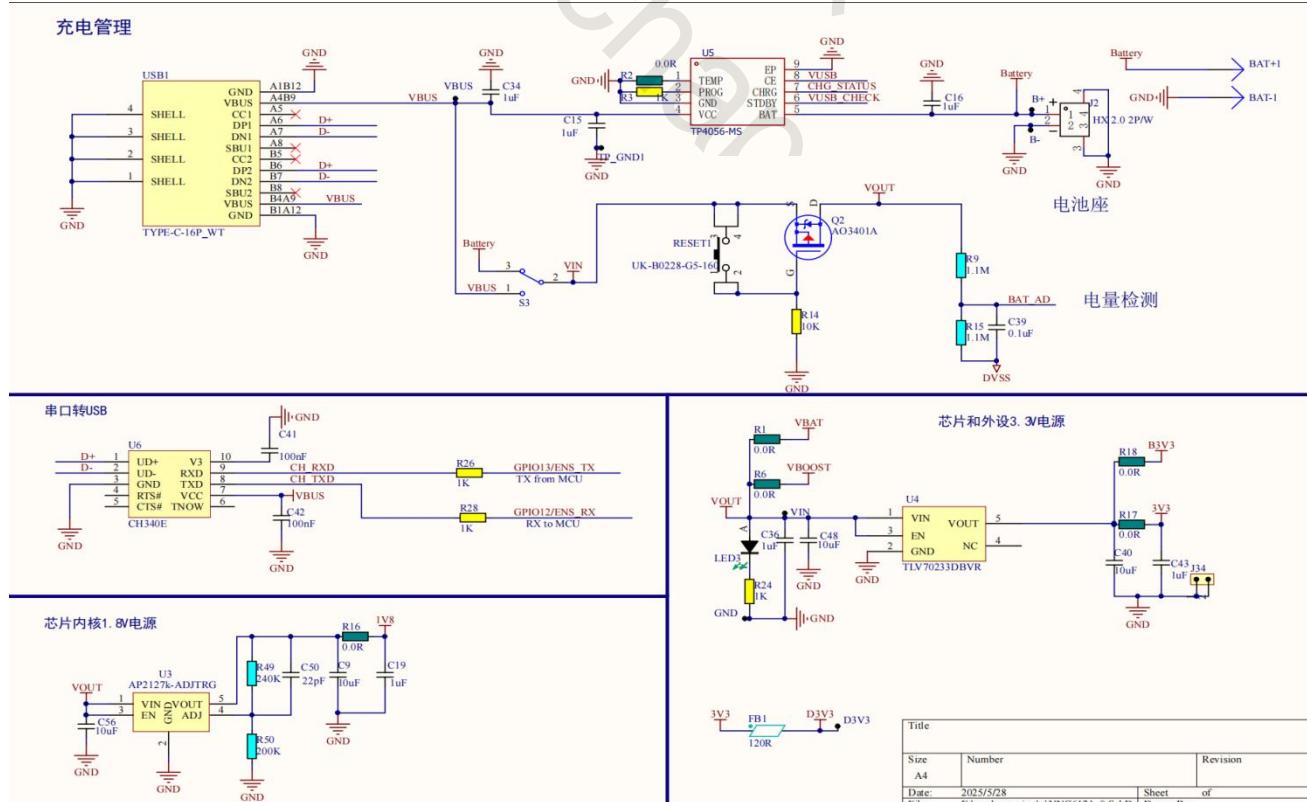

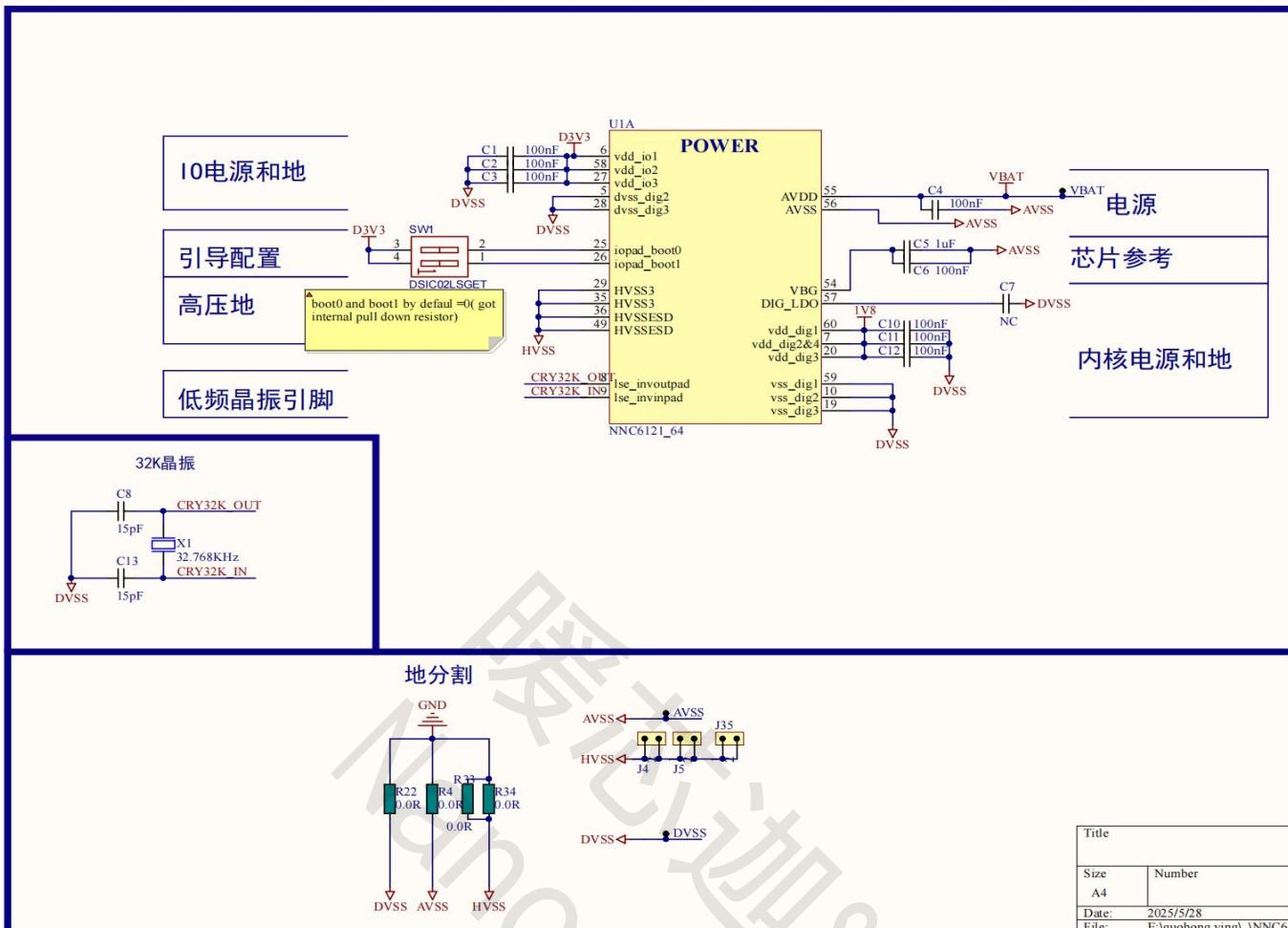

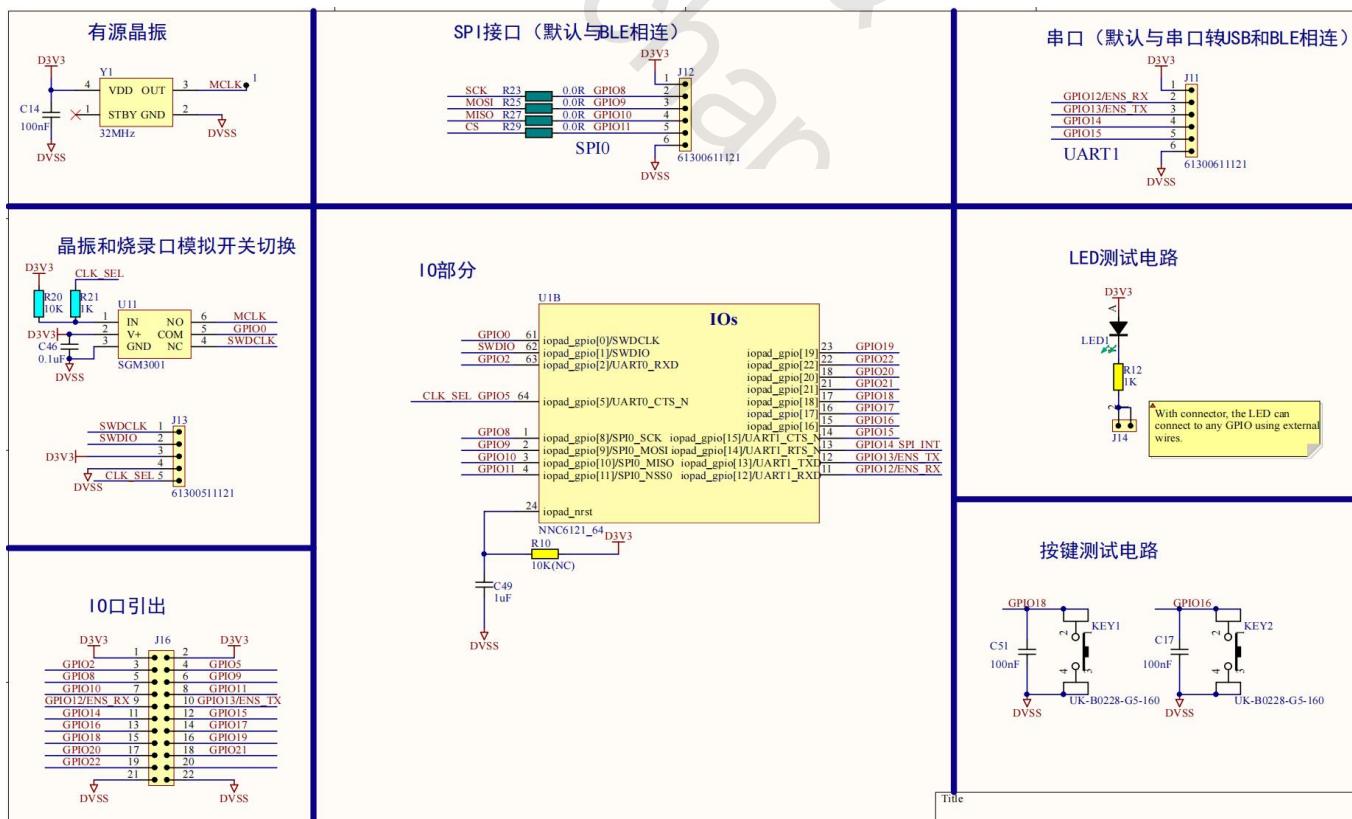

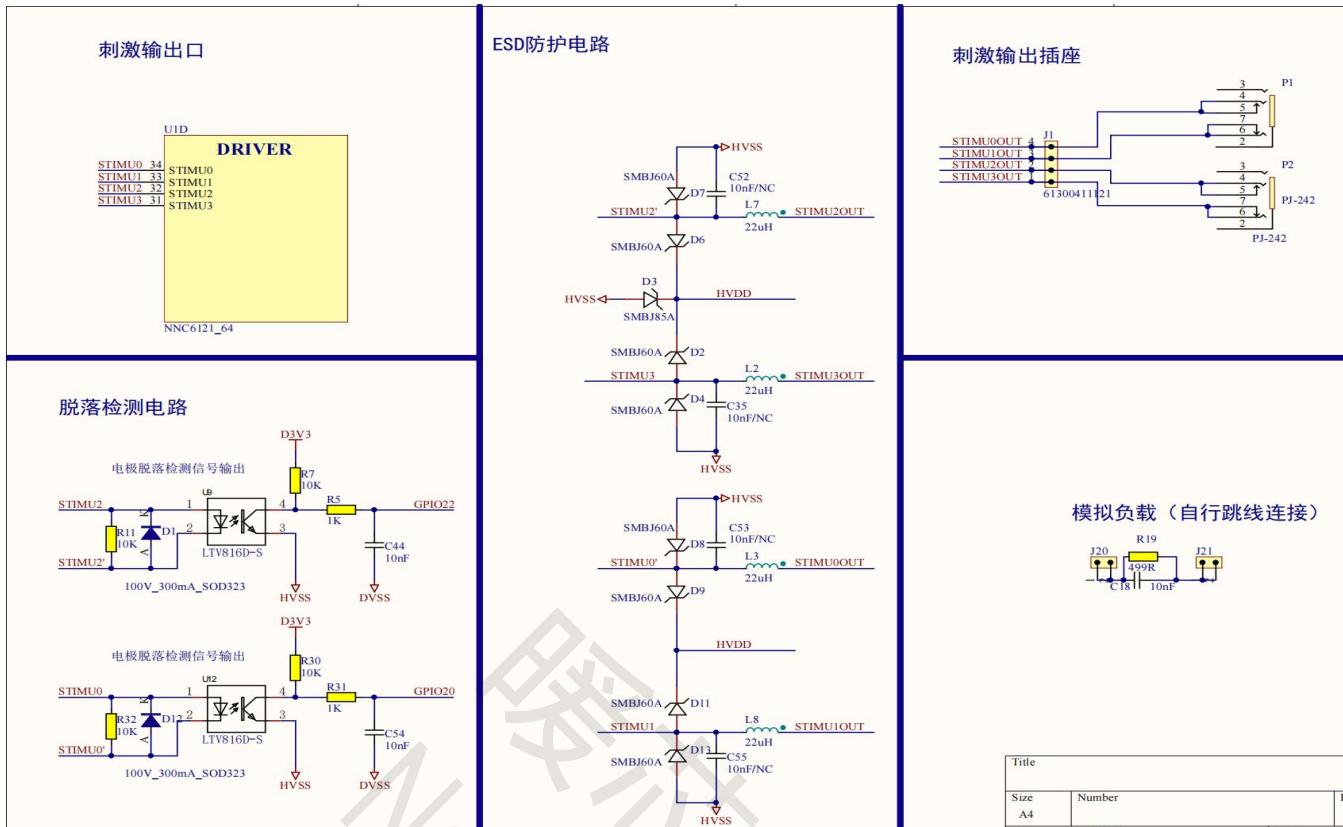

| 图 12 主模式为发送模式，从模式为接收模式 ..... | 63 | 图 29 原理图 1/6 .....   | 152 |

| 图 13 主模式为接收模式，从模式为发送模式 ..... | 63 | 图 30 原理图 2/6 .....   | 152 |

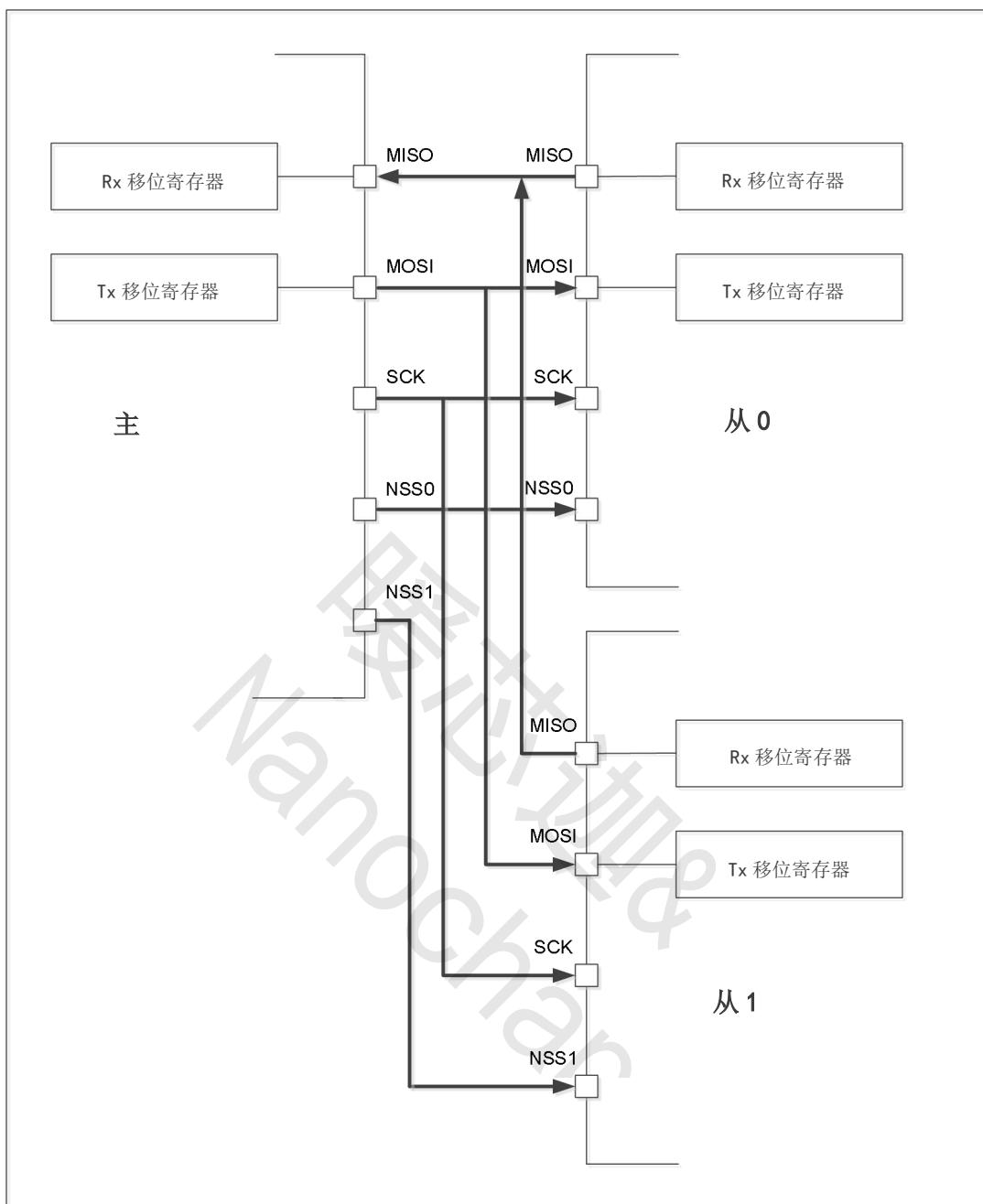

| 图 14 主多从应用程序 .....           | 64 | 图 31 原理图 3/6 .....   | 153 |

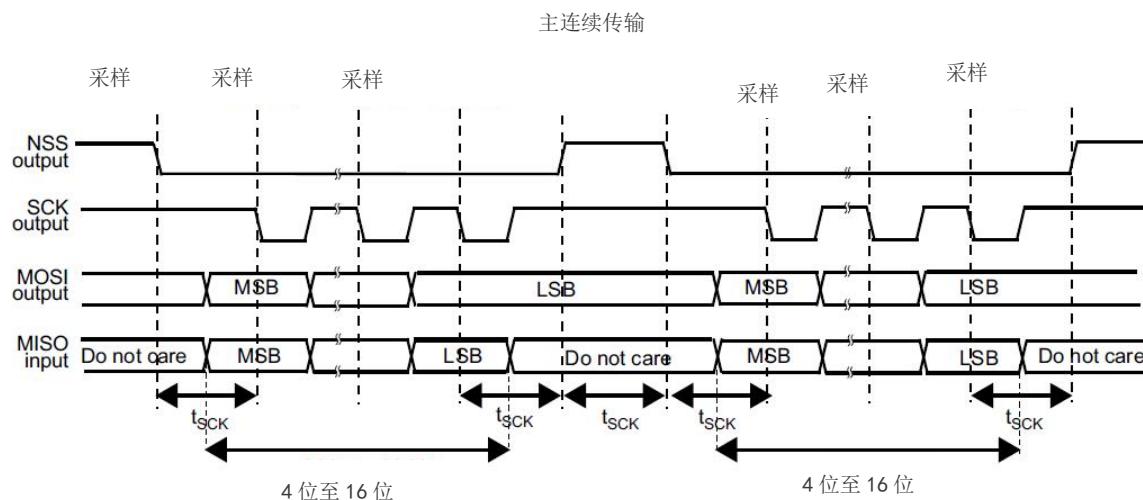

| 图 15 NSS 脉冲模式 .....          | 65 | 图 32 原理图 4/6 .....   | 153 |

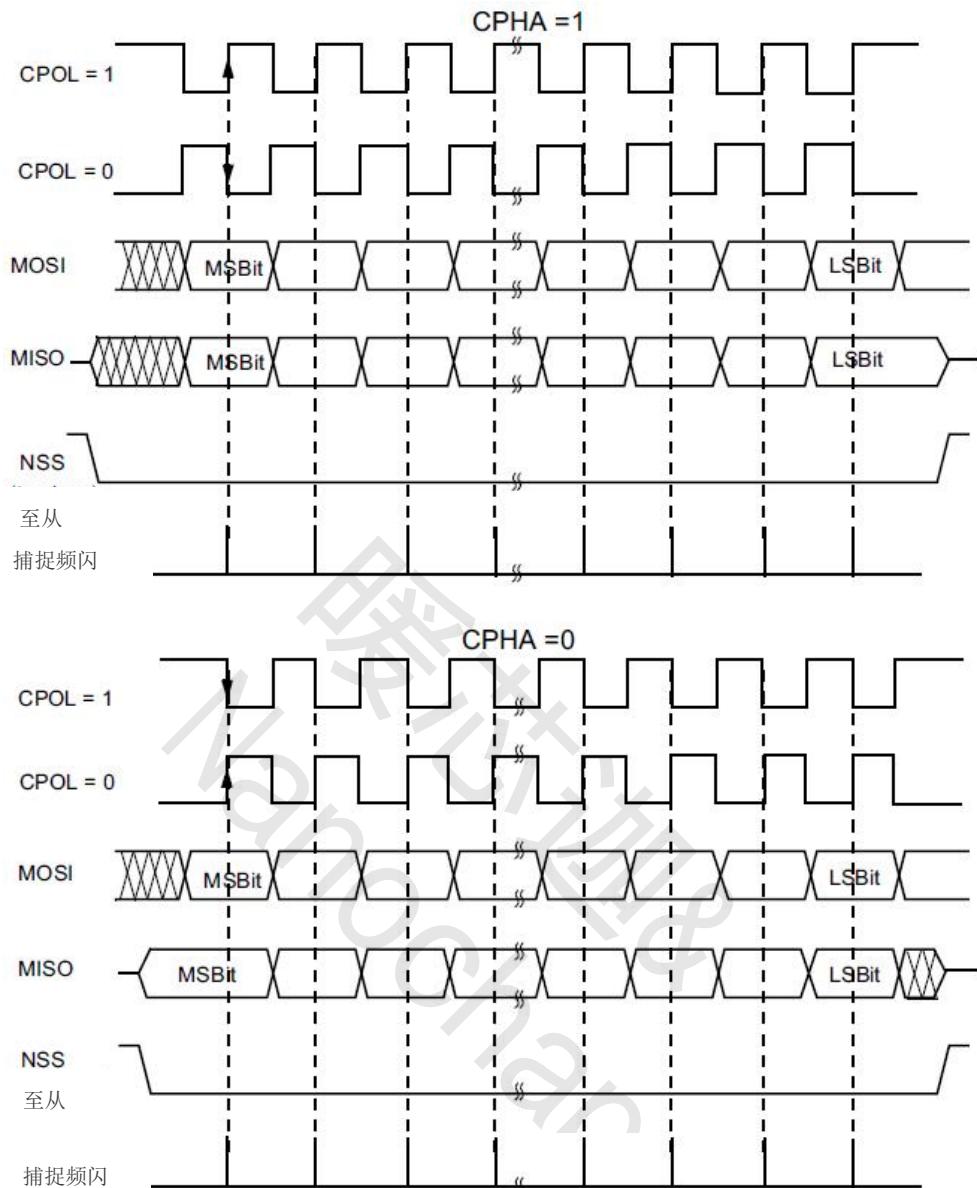

| 图 16 数据时钟时序图 .....           | 66 | 图 33 原理图 5/6 .....   | 154 |

| 图 17 UART 框图 .....           | 77 | 图 34 原理图 6/6 .....   | 154 |

## 文档修订记录

| 序号 | 版本号 | 修订日期       | 修订概述                                                                                                    | 修订人 | 审核人 | 批准人 | 备注 |

|----|-----|------------|---------------------------------------------------------------------------------------------------------|-----|-----|-----|----|

| 1  | A/1 | 2024-10-13 | 1) 修改文档格式<br>2) 加了比较器/刺激器部分细节描述<br>3) 加了封装信息                                                            |     |     |     |    |

| 2  | A/2 | 2024-11-22 | 1) 去掉单独的比较器章节，合并到脱联检测部分<br>2) BG 调整寄存器偏移地址改成 0F-0C<br>3) BIST_SEL 的具体含义<br>4) 函数描述改为功能描述<br>5) 双定时器举个例子 |     |     |     |    |

| 3  | A/3 | 2024-12-2  | 1) 8.2.2 框图<br>2) 8.2.3.1 表四<br>3) 8.6.3 GPIO 替代功能描述<br>4) CPUID 描述<br>5) 8.13.2 框图<br>6) MTP 框图        |     |     |     |    |

| 4  | A/4 | 2024-12-19 | 根据反馈意见进行的修改，包括<br>1) 增加中文描述<br>2) 双计时器框图<br>3) Uart 奇偶判断描述等                                             |     |     |     |    |

| 5  | A/5 | 2025-05-29 | 1) 最大刺激频率改为 50K<br>2) nRST 管脚说明<br>3) 章节 9 典型应用电路增加说明、图纸增加外部晶振切换、MOS 管控制供电<br>4) 增加章节 10 注意事项。          |     |     |     |    |

## 5 器件信息

表 1 器件信息

| 产品      | 封装选项       | 工作温度范围         | 驱动器    |

|---------|------------|----------------|--------|

| NNC6121 | QFN-64 7x7 | -40° C 至 85° C | 2 个高范围 |

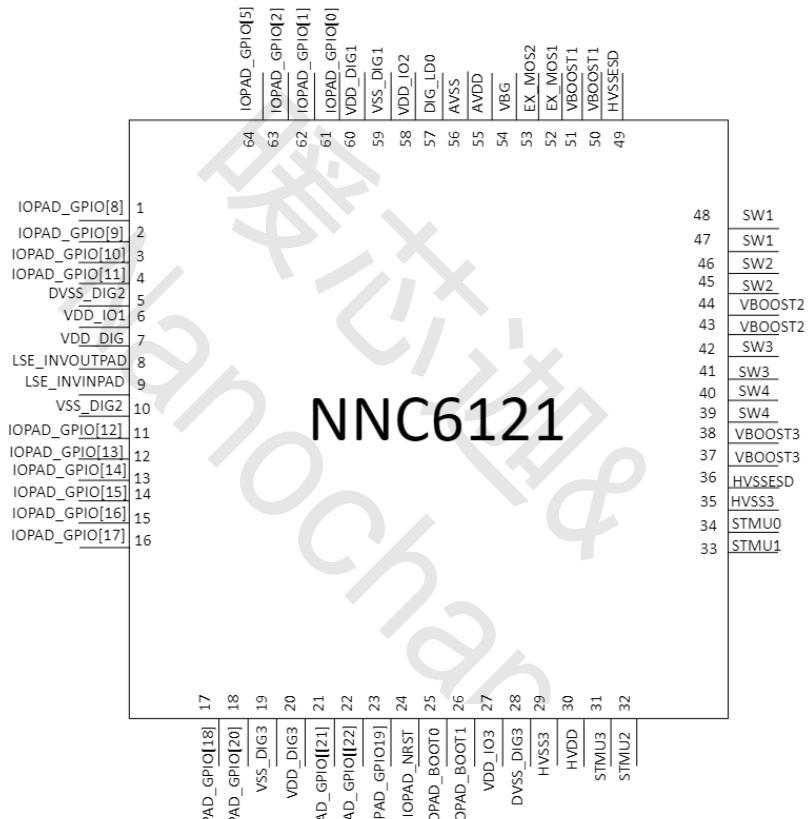

## 6 引脚配置和功能以及升压电路

### 6.1 引脚与封装定义

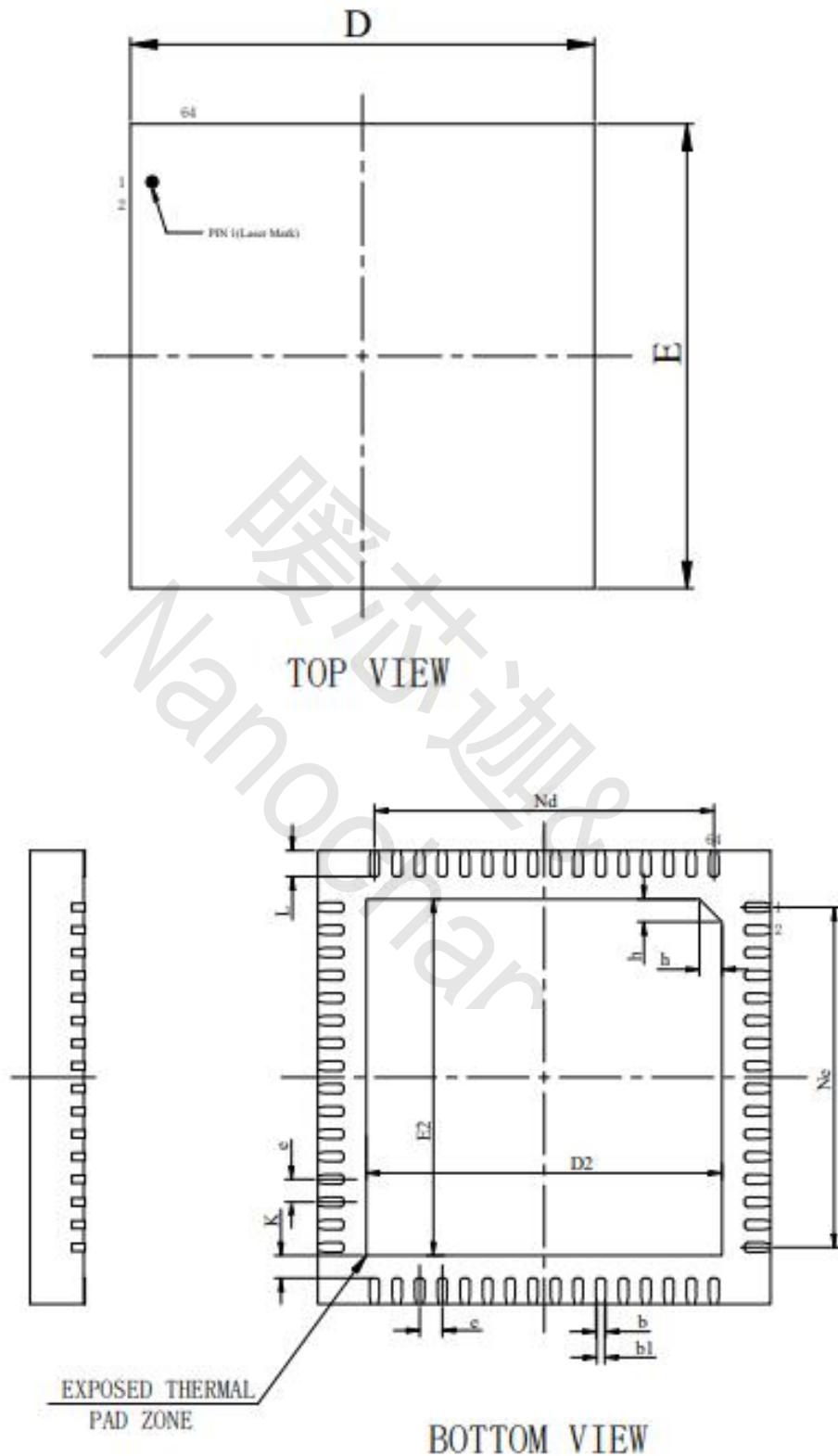

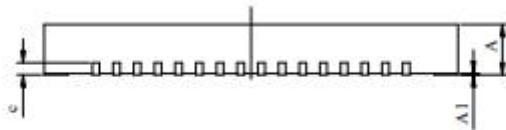

图 2 芯片原理图

表 2 芯片管脚功能 (64QFN7X7)

| 封装管脚编号 | 封装管脚名         | 缺省功能                                                     | 复用功能 1       | 复用功能 2    | 复用功能 3   |

|--------|---------------|----------------------------------------------------------|--------------|-----------|----------|

| 1      | GPIO8         | GPIO8                                                    | SPI0_SCK     | I2C1_SCL  | COMPO_IN |

| 2      | GPIO9         | GPIO9                                                    | SPI0_MOSI    | I2C1_SDA  | COMP1_IN |

| 3      | GPIO10        | GPIO10                                                   | SPI0_MISO    | -         | -        |

| 4      | GPIO11        | GPIO11                                                   | SPI0_NSS0    | RTC_1HZ   | -        |

| 5      | DVSS_DIG      | 数字 IO 地                                                  | -            | -         | -        |

| 6      | VDD_IO        | 3.3V IO 电源                                               | -            | -         | -        |

| 7      | VDD_DIG       | 1.8V 数字内部电源                                              | -            | -         | -        |

| 8      | LSE_INVOUTPAD | 外部 32K 晶体输出 pad                                          | -            | -         | -        |

| 9      | LSE_INVINPAD  | 外部 32K 晶体输入 pad                                          | -            | -         | -        |

| 10     | VSS_DIG       | 数字内部地                                                    | -            | -         | -        |

| 11     | GPIO12        | GPIO12                                                   | UART1_RXD    | MCO       | -        |

| 12     | GPIO13        | GPIO13                                                   | UART1_TXD    | SPI0_NSS1 | -        |

| 13     | GPIO14        | GPIO14                                                   | UART1_RTS_N  | SPI0_NSS2 | -        |

| 14     | GPIO15        | GPIO15                                                   | UART1_CTS_N  | SPI0_NSS3 | -        |

| 15     | GPIO16        | GPIO16                                                   | PWM1_OUT     | SPI1_SCK  | -        |

| 16     | GPIO17        | GPIO17                                                   | PWM2_OUT     | SPI1_MOSI | -        |

| 17     | GPIO18        | GPIO18                                                   | PWM3_OUT     | SPI1_MISO | -        |

| 18     | GPIO20        | GPIO20                                                   | PWM5_OUT     | COMPO_OUT | -        |

| 19     | VSS_DIG       | 数字内部地                                                    | -            | -         | -        |

| 20     | VDD_DIG       | 1.8V 数字内部电源                                              | -            | -         | -        |

| 21     | GPIO21        | GPIO21                                                   | PWM6_OUT     | COMP1_OUT | -        |

| 22     | GPIO22        | GPIO22                                                   | TIMER0_EXTIN | -         | -        |

| 23     | GPIO19        | GPIO19                                                   | PWM4_OUT     | SPI1_NSS0 | -        |

| 24     | NRST          | 复位, 低有效, 默认值 1 (仅在内部晶振时有效)                               | -            | -         | -        |

| 25     | BOOT0         | Boot 选择 0, 默认值 0                                         | -            | -         | -        |

| 26     | BOOT1         | Boot 选择 1, 默认值 0                                         | -            | -         | -        |

| 27     | VDD_IO        | 3.3V IO 电源                                               | -            | -         | -        |

| 28     | DVSS_DIG      | 数字 IO 地                                                  | -            | -         | -        |

| 29     | HVSS          | 高电压地                                                     | -            | -         | -        |

| 30     | HVDD          | 刺激驱动的高电压电源                                               | -            | -         | -        |

| 31     | STIMU3        | 驱动器 A and 驱动器 B 输出<br>/DA_CH1_Anode/DB_ELE3              | -            | -         | -        |

| 32     | STIMU2        | Driver A and Driver B Outputs<br>/DA_CH1_Cathode/DB_ELE2 | -            | -         | -        |

| 33     | STIMU1        | 驱动器 A and 驱动器 B 输出<br>/DA_CHO_Anode/DB_ELE1              | -            | -         | -        |

|    |         |                                               |       |           |          |

|----|---------|-----------------------------------------------|-------|-----------|----------|

| 34 | STIMU0  | 驱动器 A and 驱动器 B 输出<br>/DA_CHO_Cathode/DB_ELE0 | -     | -         | -        |

| 35 | HVSS    | 高电压地                                          | -     | -         | -        |

| 36 | HVSSESD | 高电压地 ESD                                      | -     | -         | -        |

| 37 | VB00ST3 | DC-DC BOOSTER 输出 3                            | -     | -         | -        |

| 38 | VB00ST3 | DC-DC BOOSTER 输出 3                            | -     | -         | -        |

| 39 | SW4     | DC-DC BOOSTER INDUCTOR-DIODE 4                | -     | -         | -        |

| 40 | SW4     | DC-DC BOOSTER INDUCTOR-DIODE 4                | -     | -         | -        |

| 41 | SW3     | DC-DC BOOSTER INDUCTOR-DIODE 3                | -     | -         | -        |

| 42 | SW3     | DC-DC BOOSTER INDUCTOR-DIODE 3                | -     | -         | -        |

| 43 | VB00ST2 | DC-DC BOOSTER 输出 2                            | -     | -         | -        |

| 44 | VB00ST2 | DC-DC BOOSTER 输出 2                            | -     | -         | -        |

| 45 | SW2     | DC-DC BOOSTER INDUCTOR-DIODE 2                | -     | -         | -        |

| 46 | SW2     | DC-DC BOOSTER INDUCTOR-DIODE 2                | -     | -         | -        |

| 47 | SW1     | DC-DC BOOSTER INDUCTOR-DIODE 1                | -     | -         | -        |

| 48 | SW1     | DC-DC BOOSTER INDUCTOR-DIODE 1                | -     | -         | -        |

| 49 | HVSSESD | 高电压地 ESD                                      | -     | -         | -        |

| 50 | VB00ST1 | DC-DC BOOSTER 输出 1                            | -     | -         | -        |

| 51 | VB00ST1 | DC-DC BOOSTER 输出 1                            | -     | -         | -        |

| 52 | EX_MOS1 | DC-DC Booste 外部主开关 NMOS 的门控信号                 | -     | -         | -        |

| 53 | EX_MOS2 | DC-DC Booste 外部过压放电 NMOS 的门控信号                | -     | -         | -        |

| 54 | VBG     | Bandgap 电压                                    | -     | -         | -        |

| 55 | AVDD    | 跟随 VBAT 或 AVDD5P0 电压                          | -     | -         | -        |

| 56 | AVSS    | 模拟地                                           | -     | -         | -        |

| 57 | DIG_LDO | 1.8V LDO 输出                                   | -     | -         | -        |

| 58 | VDD_IO  | 3.3V IO 电源                                    | -     | -         | -        |

| 59 | VSS_DIG | 数字地                                           | -     | -         | -        |

| 60 | VDD_DIG | 1.8V 数字内部电源                                   | -     | -         | -        |

| 61 | GPI00   | SWCLK                                         | GPI00 | HSE_CLK   | -        |

| 62 | GPI01   | SWDIO                                         | GPI01 | -         | -        |

| 63 | GPI02   | GPI02                                         | -     | SPI1_NSS1 | -        |

| 64 | GPI05   | GPI05                                         | -     | -         | ANA_BIST |

注：设计请参考原理图。如果您需要使用升压电路过压、过温功能，请联系制造商。

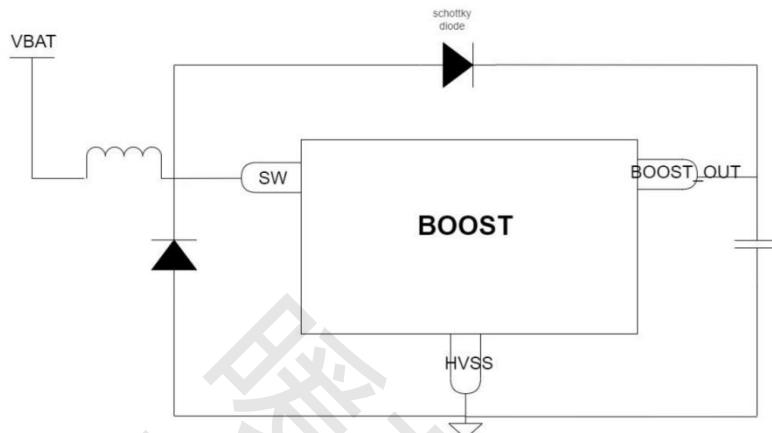

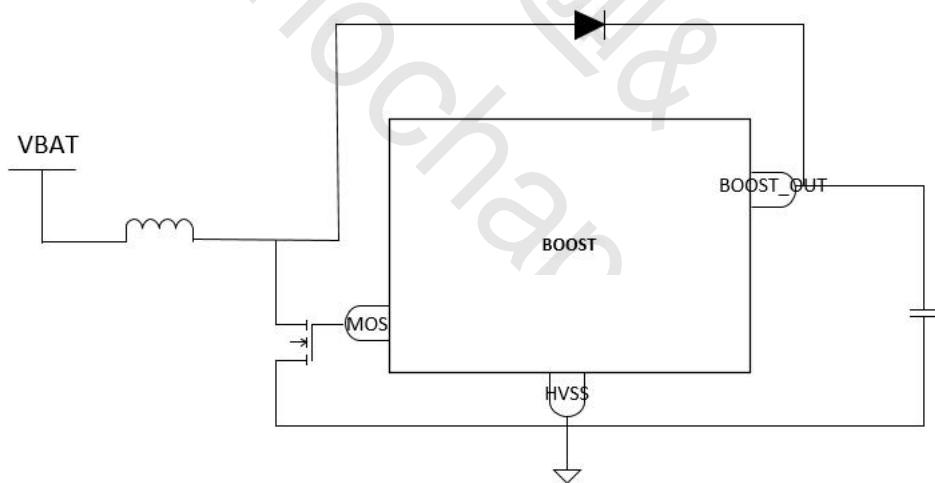

## 6.2 BOOST 升压电路选择

NNC6121 芯片自身提供两种升压电路供应用端选择：内置 MOS 升压电路和外置 MOS 升压电路，以上两种 NNC6121 升压电路均为芯片的可选配置。

使用 NNC6121 芯片内部 MOS 升压电路，芯片外部需接入升压电感、肖特基二极管、滤波电容，使用寄存器配置程序的方式配置内部 SW 信号的频率及占空比，调整 BOOST 电路输出的电压。

图 3 内置 MOS 升压电路图

使用 NNC6121 芯片外部 MOS 升压电路，芯片外部需接入升压电感、外置 MOS 管、肖特基二极管、滤波电容，使用寄存器配置程序的方式配置内部 MOS 控制信号的频率及占空比，调整 BOOST 电路输出的电压。

图 4 外置 MOS 升压模块电路图

用户端如需要更高输出功率（比如 2 瓦以上）的应用，可使用外加 BOOST 电路方案搭配 NNC6121 波形发生刺激功能。

## 7 规格

### 7.1 绝对最大额定值

在自然通风温度范围内测得（除非另有说明）

|                | 最小值   | 最大值   | 单位  |

|----------------|-------|-------|-----|

| VBAT 至 AVSS    | -0. 3 | 5. 5  | V   |

| AVDD5P0 至 AVSS | -0. 3 | 5. 5  | V   |

| VDD_IO 至 VSS   | -0. 3 | 3. 63 | V   |

| VDD_DIG 至 VSS  | -0. 3 | 1. 98 | V   |

| HVDD 值 AVSS    | 0     | 55    | V   |

| 驱动器输出电流        | 0     | 100   | mA  |

| AVSS 至 VSS     | -0. 3 | 0. 2  | V   |

| 最大工作温度         | -40   | 85    | ° C |

| 最大锡焊温度         |       | 260   | ° C |

| 储藏温度           | -40   | 150   | ° C |

### 7.2 ESD 额定值

|                | 最大                | 最小                 |

|----------------|-------------------|--------------------|

| V (ESD) 静电释放   | 人体放电模式 (HBM)，所有引脚 | ±2000              |

|                | 充电器件模型 (CDM)，所有引脚 | ±500               |

| 系统级 IEC 静电防护能力 | 电化学工作电极，参考电极，对电极  | ±15KV AIR/±8KV CON |

### 7.3 建议的工作条件

在工作环境温度范围内（除非另外注明）

|                | 最小值   | 标准值  | 最大值   | 单位 |

|----------------|-------|------|-------|----|

| <b>电源</b>      |       |      |       |    |

| VBAT 至 AVSS    | 3. 0  | 4. 2 | 5. 5  | V  |

| AVDD5P0 至 AVSS | 4. 5  | 5. 0 | 5. 5  | V  |

| VDD_IO 至 VSS   | 2. 97 | 3. 3 | 3. 63 | V  |

| VDD_DIG 至 VSS  | 1. 62 | 1. 8 | 1. 98 | V  |

| HVDD 值 AVSS    | 0     |      | 55    | V  |

| <b>电流</b>      |       |      |       |    |

| 驱动器输出电流        | 0     |      | 67    | mA |

## 8 详细功能描述

### 8.1 内存

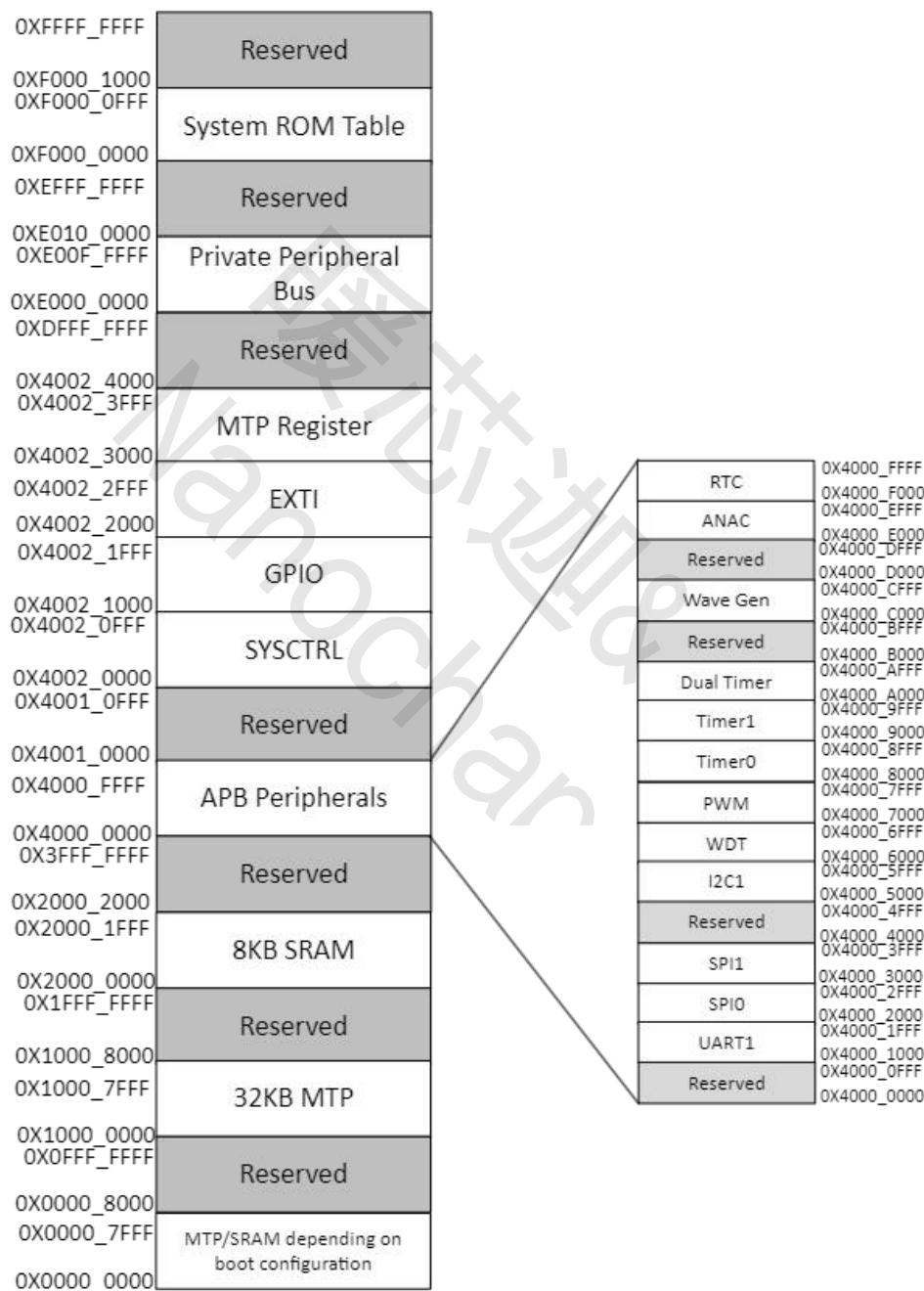

#### 8.1.1 内存映射

程序存储器、数据存储器、寄存器和输入输出端口被组织在相同的线性 4G 字节地址空间中。字节在内存中以小端格式编码。所有没有分配到芯片内存和外设的内存映射区域都被认为是“预留的”。

图 5 内存映射图

### 8.1.2 嵌入式 SRAM

嵌入式 SRAM 容量为 8K 字节。可以通过字节、半字（16 位）或全字（32 位）来访问 SRAM。可以在没有等待状态的情况下以最大系统时钟频率寻址这个内存。

SRAM 起始地址为 0x2000\_0000。

当通过 BOOT pin 引脚或 REMAP 寄存器选择物理重映射时，CPU 可以从地址 0x0000\_0000 访问 SRAM。

### 8.1.3 启动配置

通过 BOOT0 和 BOOT1 引脚可以选择三种启动方式，如下表所示。

表 3 启动模式

#### 启动模式选择

| 引导 1 引脚 | 引导 0 引脚 | 启动模式        | 别名使用                             |

|---------|---------|-------------|----------------------------------|

| X       | 0       | MTP 基地址     | 选择来自基本区域的 MTP 主区域作为应用程序代码使用的引导区域 |

| 0       | 1       | MTP 高 4K 字节 | MTP 高 4K 字节区域被选为引导加载程序使用的引导区域    |

| 1       | 1       | 嵌入式 SRAM    | 嵌入式 SRAM 被选择为用于调试的引导区域           |

启动延迟结束后，CPU 从地址 0x0000\_0000 获取堆栈顶部值，然后从引导内存 0x0000\_0004 开始执行代码。

从基地地址的 MTP 主区域引导：MTP 内存在引导内存空间（0x0000\_0000）中被别名，但仍然可以从其原始内存空间（0x1000\_0000）访问。换句话说，可以从地址 0x0000\_0000 或 0x1000\_0000 开始访问 MTP 内存内容。

从 MTP 高 4K 字节区引导：MTP 高 4K 字节区域用于引导加载程序，它在引导内存空间（0x0000\_0000）中被别名化，但仍然可以从其原始内存空间（0x1000\_7000）中访问。剩余的 28K 字节空间用于应用程序代码。

从嵌入式 SRAM 引导：SRAM 在引导内存空间（0x0000\_0000）中有别名，但仍然可以从其原始内存空间（0x2000\_0000）中访问它。

一旦选择了 BOOT0 和 BOOT1 引脚，应用软件就可以在代码区修改内存。这种修改是通过在 SYSCTRL 寄存器中编程 REMAP 重新映射位来执行的。

BOOT0 和 BOOT1 默认是弱下拉，当从引导加载程序空间引导，即引导 0pin 需要拉高，软件可以清除 GPIO\_P[24] 寄存器以节省电力。

## 8.2 多次编程存储器 (MTP)

### 8.2.1 概述

YEG8K32F18B5AA1 是从 Globalfoundries 0.18um BCD1lite1.8V - ULL 6V\_40V-65V 进程中编出来的一个嵌入式 MTP IP 宏。它的每个存储器阵列均被分成三个内存块，一个 MTP 块（8K × 32 位），一个信息块（32 × 32 位），和一个 EEPROM 块（512×8 位）。

YEG8K32F18B5AA1 支持两种运行模式：用户模式和测试模式。

- 用户模式支持五种内存操作：复位（RESET）/待机（STANDBY）/静态（STATIC）/读取（READ）/内部高电压写入（INTHV WRITE）。

- 测试模式支持四种内存操作；测量存储单元电流（CLEN）/数据保持测试读取（MRGN READ）/数据保持测试内部高电压写入（MRGN INTHV WRITE）/外部高电压对所有 MTP 密度写入（EXTHV WRITE ALL）。

### 8.2.1.1 功能列表

- 存储器组成：MTP 块（ $8K \times 32$  位），信息块（ $32 \times 32$  位），EEPROM 块（ $512 \times 8$  位）。

- MTP 块支持 32 位读取和扇区写入操作。

- 信息块支持 32 位读取和 32 位写入操作。

- EEPROM 块支持字节读取和字节写入操作。

- 数据重新写入，不进行擦除操作。

- 写入时间为非固定值。

- BUSY 信号提供了一种硬件方法，可检测写入操作是否已完成。

- 写入 MTP 密钥：0x5A5A5A5A。

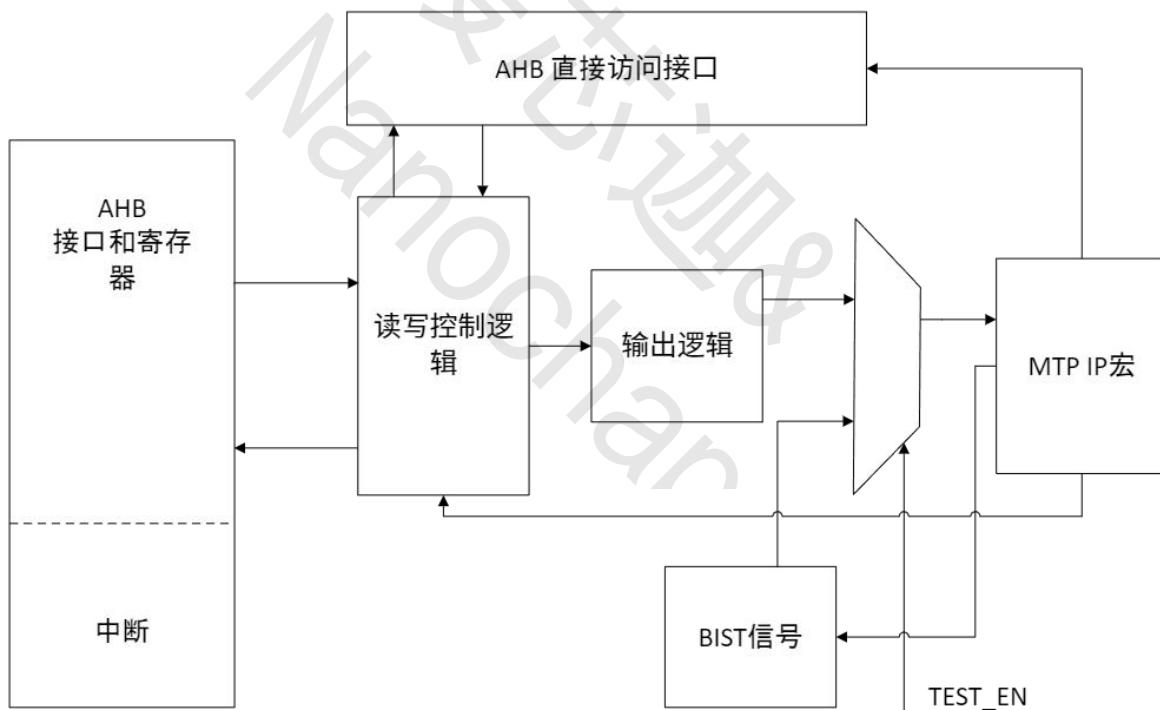

### 8.2.2 框图

MTP 控制器的功能框图如下图所示。

图 6 MTP 框图

### 8.2.3 功能描述

#### 8.2.3.1 支持的用户操作方式

用户模式可以在以下五种模式中选择一种：

- 复位 (RESET)

- 待机 (STANDBY)

- 静态 (STATIC)

- 读取 (READ)

- 内部高电压写入 (INTHV WRITE)

工作模式选择如下图所示：

表 4 用户操作模式

| 引脚名称   | 复位    | 待机    | 静态    | 读取    | 内部高电压写入 |       |

|--------|-------|-------|-------|-------|---------|-------|

| RESETB | L     | H     | H     | H     |         | H     |

| CS     | L     | L     | H     | H     |         | H     |

| READ   | L 或 H | L 或 H | L     | H     |         | L     |

| WR     | L 或 H | L 或 H | L     | L     |         | H     |

| CLEN   | L 或 H | L 或 H | L     | L     |         | L     |

| IFREN  | L 或 H | L 或 H | L 或 H | L 或 H | L       | L 或 H |

| EEPROM | L 或 H | L 或 H | L 或 H | L     | H       | L     |

| SRL    | L 或 H | L 或 H | L     | L     |         | L     |

| MRGN   | L 或 H | L 或 H | L     | L     |         | L     |

| HVEN   | L 或 H | L 或 H | L     | L     |         | L     |

| WRALL  | L 或 H | L 或 H | L     | L     |         | L     |

| VPP    | VDD2  |       |       |       |         |       |

#### 8.2.3.2 在 MTP 块中的扇区写入操作的定义

MTP 块中的存储器阵列由多个扇区集成而成，每个扇区的地址定义和描述如下表。

MTP 块只允许“扇区写入”操作。

不允许将数据随机写入存储器阵列，从目标扇区的第一个地址到最后一个地址连续发起写入操作。

表 5 MTP 块存储器阵列配置

| 扇区编号 | 使用地址         | 扇区编号 | 使用地址         |

|------|--------------|------|--------------|

| 扇区 0 | 0000H-03FFH  | 扇区 4 | 1000H-03FFH  |

| 扇区 1 | 0400H-07FFH  | 扇区 5 | 1400H-17FFH  |

| 扇区 2 | 0800H-0BFFFH | 扇区 6 | 1800H-1BFFFH |

| 扇区 3 | 0C00H-0FFFFH | 扇区 7 | 1C00H-1FFFFH |

### 8.2.3.3 MTP 块中引导加载扇区的定义

引导加载扇区地址为 MTP 块中的扇区 7。当 DBGPA\_EN 和 BOOTLD\_WEN 关闭时，引导加载扇区可以由 SWD 写入，该软件应用程序只能读取引导加载扇区。

### 8.2.3.4 信息块中的 trim 和 ID 配置信息区域的定义

Trim 配置信息区域地址为 0x0018 ~ 0x001B。设备 ID 配置信息区域地址为 0x001C ~ 0x001E。它们用于存储模拟 trim 值和设备 ID 值，这些值将在上电和复位后自动加载到相关配置寄存器中。

### 8.2.3.5 信息块中的用户配置信息区域的定义

用户配置信息区域地址为 0x001F。它用于存储用户配置信息，这些信息将在上电和复位后自动加载到配置寄存器中。

表 6 用户配置信息定义

| 位      | 字段名             | 字段描述                          | 默认   |

|--------|-----------------|-------------------------------|------|

| 31: 24 | -               | -                             | -    |

| 23: 16 | BOOTLD_SWDPA_EN | 引导加载程序 SWD 访问保护启用：0x55：开 其他：关 | 0x55 |

| 15: 8  | DBGPA_EN        | 调试端口访问保护启用：0xAA：开 其他：关        | 0xAA |

| 7: 0   | SEC_ACL_EN      | 应用程序代码锁启用：0X33：启用时钟 其他：禁止时钟   | 0x33 |

### 8.2.3.6 MTP 用户访问权限

表 7 MTP 访问权限

| MTP 区 | MTP_DBGPA_EN | SEC_ACL | BOOTLD_SWDPA_EN | SWD   | 应用    |

|-------|--------------|---------|-----------------|-------|-------|

| MTP 块 | 扇区 0-扇区 6    | 0       | x               | -     | 读取/写入 |

|       |              |         | x               | -     | -     |

|       |              | 1       | x               | 读取/写入 | 读取/写入 |

|       |              | 0       | x               | 读取/写入 | -     |

|       | 引导加载区扇区 7    | 1       | 1               | -     | 读取    |

|       |              |         | x               | -     | 读取    |

|       |              | 0       | 0               | -     | 读取    |

|       |              | 0       | 1               | -     | 读取    |

|       |              |         | x               | 读取/写入 | 读取    |

| 信息块   | 其他区          | 1       | x               | -     | 读取/写入 |

|       |              | 0       | x               | 读取/写入 | 读取/写入 |

|       | Trim 和 ID 区  | 1       | x               | -     | 读取    |

|       |              | 0       | x               | 读取/写入 | 读取    |

|       | 用户区          | 1       | x               | -     | 读取    |

|       |              | 0       | x               | 读取/写入 | 读取    |

|       | EEPROM 块     | 1       | x               | -     | 读取/写入 |

|       |              | 0       | x               | 读取/写入 | 读取/写入 |

## 8.2.3.7 时序参数

| 参数                | 符号       | 最小值   | 典型值  | 最大值 | 单位 |

|-------------------|----------|-------|------|-----|----|

| VDD1 设置时间         | Tpws     | 100   |      |     | ns |

| VDD1 保持时间         | Tpwh     | 100   |      |     | ns |

| VDD2 设置时间         | Trsts    | 100   |      |     | ns |

| VDD2 保持时间         | Trsth    | 100   |      |     | ns |

| RESETB 到 CS 的设置时间 | Trscs    | 40    |      |     | us |

| RESETB 到 CS 的保持时间 | Trsch    | 100   |      |     | ns |

| CS 至读取/写入设置时间     | Tcsctrls | 100   |      |     | ns |

| 地址/数据设置时间         | Tads     | 20    |      |     | ns |

| 地址持续时间            | Tadhr    | 50    |      |     | ns |

| 读取脉宽              | MTP 和信息块 | Trpw  | 60   |     | ns |

|                   | EEPROM 块 |       | 250  |     | ns |

| 读取访问时间            | MTP 和信息块 | Trac  |      | 60  |    |

|                   | EEPROM 块 |       |      | 250 |    |

| 读取周期时间            | MTP 和信息块 | Trc   | 80   |     | ns |

|                   | EEPROM 块 |       | 270  |     | ns |

| DOUT 持续时间         | Tdoh     | 3     |      |     | ns |

| WR 脉宽             | Twpw     | 100   |      |     | ns |

| 写入的地址/数据持续时间      | Tadhw    | 50    |      |     | ns |

| 写入时间 (变更代码)       | MTP 和信息块 | Twr   | 0.5  |     | ms |

|                   | EEPROM 块 |       | 0.15 |     | ms |

| 写入时间 (非变更代码)      |          |       | 1    |     | Us |

| 对 WR 的 BUSY 访问时间  |          | Tbas  |      | 100 | ns |

| 写入恢复时间            |          | Twrc  | 100  |     | ns |

| 测量电流等待时间          |          | Tmcw  | 100  |     | ns |

| CLEN 地址持续时间       |          | Tadhc | 20   |     | ns |

### 8.2.3.8 MTP 单元电流配置

通过配置 MTP BG Trim register (BG\_I\_LC, BG\_I\_MC) 数值可用于调整 NNC6121 内置单元电流，具体寄存器地址及配置如下。

| Bit   | Field Name | Attribute | Default | Field Description |

|-------|------------|-----------|---------|-------------------|

| 31: 8 | -          | R0        | 0       | Reserved          |

| 7: 4  | BG_I_LC    | RW        | 0x8     | Analog trim       |

| 3: 0  | BG_I_MC    | RW        | 0x8     | Analog trim       |

通过调整 BG\_I\_LC, BG\_I\_MC 对应数值，可相应修改电流源单位电流系数，用于减少或增加单位刺激电流，具体对应关系如下表所示。

| BG_I_MC<3: 0> | 单位电流系数    | BG_I_LC<3: 0> | 单位电流系数    |

|---------------|-----------|---------------|-----------|

| 0             | (32/32) I | 0             | (32/32) I |

| 1             | (33/32) I | 1             | (31/32) I |

| 2             | (34/32) I | 2             | (30/32) I |

| 3             | (35/32) I | 3             | (29/32) I |

| 4             | (36/32) I | 4             | (28/32) I |

| 5             | (37/32) I | 5             | (27/32) I |

| 6             | (38/32) I | 6             | (26/32) I |

| 7             | (39/32) I | 7             | (25/32) I |

| 8             | (40/32) I | 8             | (24/32) I |

| 9             | (41/32) I | 9             | (23/32) I |

| 10            | (42/32) I | 10            | (22/32) I |

| 11            | (43/32) I | 11            | (21/32) I |

| 12            | (44/32) I | 12            | (20/32) I |

| 13            | (45/32) I | 13            | (19/32) I |

| 14            | (46/32) I | 14            | (18/32) I |

| 15            | (47/32) I | 15            | (17/32) I |

注：当 BG\_I\_LC = 0, BG\_I\_MC = 15 时，NNC6121 内置单元电流可设置为最大，最高可输出 100mA 刺激电流。

## 8.3 系统控制器 (SCU)

### 8.3.1 PMU

默认情况下，系统或上电复位后，MCU 处于运行模式。在运行模式下，CPU 由 HCLK 计时（默认是 HSI RC 的 8MHz），并执行程序代码。当 CPU 不需要保持运行时，有几种低功耗模式可用于节省电力。当某些应用不使用 RTC 时，可以通过软件禁用 LSI RC（约 32kHz）和 LSE OSC（带外部晶振，精确 32.768kHz），以节省电力。在 SYSCTRL 寄存器中也有外设启用位，如果一些外设没有使用，用户可以禁用外设来门控他们的时钟。

支持五种电源模式：

- 运行模式：正常运行模式，CPU 以高频时钟运行，所有外设均可激活。

- 睡眠模式：HCLK 被门控。CPU/所有 AHB 外设时钟关闭，所有 APB 外设和 CPU 核外设（如 NVIC、SysTick 等）都可以在中断或事件发生时运行并唤醒 CPU。

- 低功耗运行模式：系统时钟（SYSCLK）切换到大约 32kHz 的 LFCLK。为了节省电力，用户可以将程序复制到 SRAM 中执行。

- 低功耗睡眠模式：系统时钟（SYSCLK）切换到大约 32kHz 的 LFCLK。和睡眠模式一样，HCLK 是门控的。

- 停止模式：禁用 HSI RC。LFCLK 可以一直运行。

此外，可以通过以下方法之一来降低运行模式下的功耗：

- 降低系统时钟；

- 当未使用 APB 和 AHB 外设时，门控时钟。

如果 SCR 的 SLEEPONEXIT 位设置为 1，当处理器完成异常处理程序的执行并返回到线程模式时，它立即进入睡眠模式。在只在发生中断时需要处理器运行的应用程序中使用此机制。

通常，处理器只有在检测到具有足够优先级的异常导致异常输入时才会被唤醒。

一些嵌入式系统可能必须在处理器唤醒之后，在执行中断处理程序之前执行系统恢复任务。要实现这一点，请将 PRIMASK 位设置为 1。如果到达已启用的中断，且其优先级高于当前异常优先级，则处理器会醒来，但不会执行中断处理程序，直到处理器将 PRIMASK 初始屏蔽设置为零。

表 8 低功耗模式汇总

| 模式名称          | 条目                                    | 唤醒源                             | 唤醒系统时钟        | 对时钟的影响               |

|---------------|---------------------------------------|---------------------------------|---------------|----------------------|

| 睡眠（现在睡眠或退出睡眠） | WFI 或从 ISR 返回                         | 任何中断                            | 与进入睡眠模式前相同    | HCLK 关               |

|               | WFE                                   | 唤醒事件                            |               |                      |

| 低功耗运行         | SYSCLK_SEL 设置为 2' b1x                 | SYSCLK_SEL 设置为 2' b0x           | 无变化           | 无                    |

| 低功耗睡眠         | SYSCLK_SEL 设置为 2' b1x + WFI 或从 ISR 返回 | 任何中断                            | 与进入低功耗睡眠模式前相同 | HCLK 关               |

|               | SYSCLK_SEL 设置为 2' b1x + WFE           | 唤醒事件                            |               |                      |

| 停止            | SLEEPDEEP 位 + WFI 或从 ISR 或 WFE 返回     | 任何 EXTI 行（在 EXTI 寄存器中配置）特定的外设事件 | HSI RC        | 除 LSI 和 LSE 外，所有时钟关闭 |

表 9 取决于工作模式的功能

| 功能      | 运行 | 睡眠 | 低功耗运行 | 低功耗睡眠 | 停止 |

|---------|----|----|-------|-------|----|

| CPU     | Y  | -  | Y     | -     | -  |

| MTP 内存  | Y  | -  | Y     | -     | -  |

| SRAM    | Y  | -  | Y     | -     | -  |

| HSI     | 0  | 0  | 0     | 0     | -  |

| LSI     | 0  | 0  | 0     | 0     | 0  |

| LSE     | 0  | 0  | 0     | 0     | 0  |

| LVD     | 0  | 0  | 0     | 0     | 0  |

| 波形信号发生器 | 0  | 0  | 0     | 0     | -  |

| RTC     | 0  | 0  | 0     | 0     | 0  |

| UART    | 0  | 0  | 0     | 0     | -  |

| I2C     | 0  | 0  | 0     | 0     | -  |

| SPI     | 0  | 0  | 0     | 0     | -  |

| 定时器/双定时 | 0  | 0  | 0     | 0     | -  |

| WDT     | 0  | 0  | 0     | 0     | -  |

| PWM     | 0  | 0  | 0     | 0     | -  |

| GPIOs   | 0  | 0  | 0     | 0     | 0  |

Y = 确定 0 = 可选

### 8.3.2 复位控制

NNC6121 复位控制包括电源复位和系统复位两种复位控制。上电复位，称为冷复位，在上电期间重置整个系统。系统复位重置处理器除 DBG 控制和 RTC 以外的 CPU 核和外设 IP 组件。

电源复位由电源接通复位和电源关闭复位（POR/PDR 复位）产生。电源复位将所有寄存器设置为其复位值。当内部 LDO 稳压器准备提供 1.8V 电源时，有功信号较低的功率复位将被取消。下电时，PDR 阈值电压可配置为 xxx（待定例）。RESET 复位服务例程向量固定在内存映射中的地址 0x0000\_0004。

调试逻辑和 RTC 只能通过 POR/PDR 复位。

系统复位由以下事件引起：

- 上电复位

- 外部复位引脚

- 看门狗定时器复位

- Cortex-M0 AIRCR 寄存器中的 SYSRESETREQ 位被设置为软复位

- CPU 锁定（当 CPU 处于 HardFault 或 NMI 处理程序中时，会发生另一个 HardFault 事件）

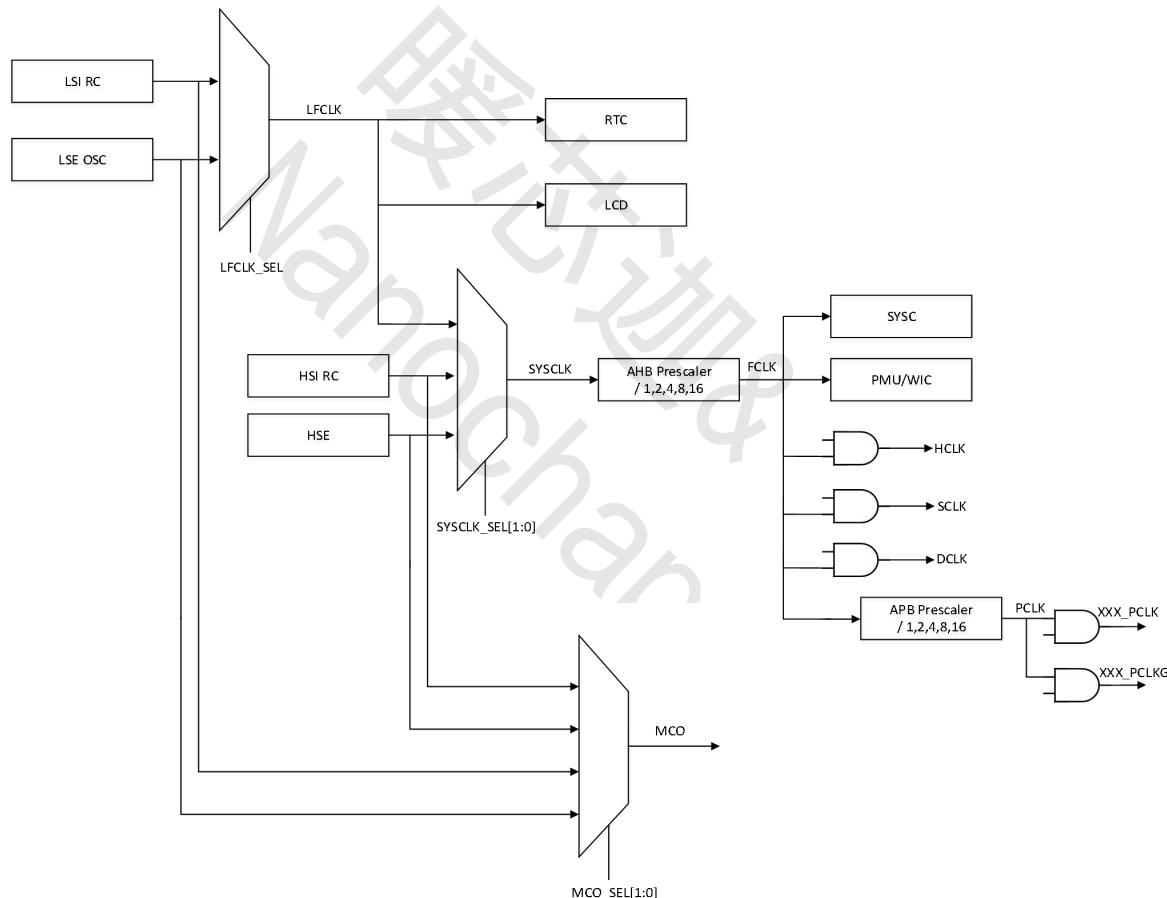

### 8.3.3 时钟控制

#### 8.3.3.1 时钟树结构

可以使用四种不同的时钟源：

- **HSI RC** - 高速全集成 RC 振荡器产生 HSI 时钟（约 4-32MHz）

- **HSE** - 高速外部时钟（高达 32MHz）

- **LSI RC** - 低速全集成 RC 振荡器产生 LSI 时钟（约 32KHz）

- **LSE OSC** - 带外部晶体谐振器的低速振荡器（精确 32.768KHz）

时钟树结构如下：

图 7 时钟树

可以选择以下时钟之一作为系统时钟 (SYSCLK) :

- LFCLK (来自 LSI 或 LSE)

- HSI

- HSE

系统时钟最大频率为 32MHz。系统复位时，将选择 HSI 时钟作为系统时钟。

只有当目标时钟源准备好时，才会发生时钟源切换。

LFCLK 可以从 LSI 或 LSE 中选择。可以通过软件禁用 LSI 和 LSE 时钟。

对于 LSE 振荡器，正常运行时，将 LSE\_OSCEN 和 LSE\_CLKEN 设置为 1。在待机状态下，将 LSE\_CLKEN 设置为 0。可以禁用 XTALOUTCORE 的时钟输出，同时保持振荡器核运行。如果需要通过输入引脚将时钟信号驱动到芯片中进行测试，则在单元中包含一个旁路多路复用器，将 INVINPAD 驱动的时钟信号直接路由到 XTALOUTCORE。要启用此功能，请将 OSCEN 设置为 0，这也将关闭振荡器核。

### 8.3.3.2 不同电源模式下的时钟说明

- AHB 和 APB 外设时钟可以通过软件禁用。

- 睡眠和低功率睡眠模式停止 HCLK。

- 停止模式停止所有时钟，除 LSI 和 LSE 外，HSI RC 被禁用，当离开停止模式时，HSI 自动成为系统时钟。

- MCO 引脚输出，彼此独立，从 LSI/LSE/HSI/HSE 中选择时钟。

- 下表显示了每个低功耗模式下的时钟状态（开/关/用户）。

表 10 不同电源模式下的时钟描述

| 时钟     | 运行      | LP 运行   | 睡眠      | LP 睡眠   | 停止 | 描述                              |

|--------|---------|---------|---------|---------|----|---------------------------------|

| LSI    |         | 开       |         |         |    | 32KHz 内 RC 振荡器                  |

| LSE    |         | 选择取决于用户 |         |         |    | 32.768KHz 晶体振荡器                 |

| LFCLK  | 用户      | 用户      | 用户      | 用户      | 用户 | 从 LSI 和 LSE 切换低频时钟              |

| HSI    | 开       | 用户      | 开       | 开       | 关  | HSI RC 4~32MHz                  |

|        | 选择取决于用户 |         | 选择取决于用户 | 选择取决于用户 | 用户 |                                 |

| HSE    | 用户      | 用户      | 用户      | 用户      | 用户 | 高达 32MHz 的外部时钟                  |

| SYSCLK | 开       | 开       | 开       | 开       | 关  | 从 HSI, HSE 和 LFCLK 切换系统时钟       |

| FCLK   | 开       | 开       | 开       | 开       | 关  | 从 SYSCLK 分离的 AHB 自由运行的时钟        |

| HCLK   | 开       | 开       | 关       | 关       | 关  | 用于 CPU/MTP/SRAM/GPIO 的 AHB 总线时钟 |

| SCLK   | 开       | 开       | 开       | 开       | 关  | 用于 NVIC 的 CPU 核系统时钟             |

| DCLK   | 动态      | 动态      | 动态      | 动态      | 关  | CPU 核调试时钟，当没有调试请求时，它被门控         |

| PCLK   | 开       | 开       | 开       | 开       | 关  | APB 自由运行时钟                      |

| PCLKG  | 动态      | 动态      | 关       | 关       | 关  | APB 门控总线时钟，当没有 APB 周期时，它是门控的    |

### 8.3.3.3 时钟开关顺序

当 SYSCLK 从 HSI 切换到 HSE 时，请按如下顺序配置：

- 1) 确保 HSE 时钟正常运行；

- 2) 将 SYSCLK\_SEL 设置为 2'b01；

- 3) 轮询 SYSCLK\_SWSTS 为 2'b01；

4) 将 HSI\_EN 设置为 0。

**当将 SYSCLK 从 HSI 切换到 LFCLK 时，按以下顺序配置：**

- 1) 确保 LFCLK 运行正常，如需更换 LFCLK 源，请先执行 LFCLK 开关顺序；

- 2) 将 SYSCLK\_SEL 设置为 2'b1x；

- 3) 轮询 SYSCLK\_SWSTS 为 2'b1x；

- 4) 将 HSI\_EN 设置为 0。

**当 LFCLK 从 LSI 切换到 LSE 时，请按照如下顺序进行配置：**

- 1) 将 LSE\_OSCEN 和 LSE\_CLKEN 均设置为 1；

- 2) 等待 LSE 稳定（稳定时间待定）；

- 3) 将 LFCLK\_SEL 设置为 1；

- 4) 轮询 LFCLK\_SWSTS 为 1；

- 5) 将 LSI\_EN 设置为 0。

表 11 SYSCTRL 寄存器

| Offset | 首字母缩写      | 寄存器描述                   |

|--------|------------|-------------------------|

| 00h    | CLK_CFG    | 时钟配置寄存器                 |

| 04h    | HSI_CTRL   | HSI 控制寄存器               |

| 08h    | LSI_CTRL   | LSI 控制寄存器               |

| 0Ch    | LSE_CTRL   | LSE 控制寄存器               |

| 10h    | AHB_CLKEN  | AHB 外设时钟启用寄存器           |

| 14h    | APB_CLKEN  | APB 外设时钟启用寄存器           |

| 18h    | PERI_CLKEN | 外设工作时钟启用寄存器             |

| 1Ch    | SLP_PCLKEN | 在睡眠/停止模式下启用 APB 外设时钟寄存器 |

| 20h    | RST_CTRL   | 复位控制寄存器                 |

| 24h    | RST_FLAG   | 复位标志寄存器                 |

| 28h    | PRST_KEY   | 外设复位启用密钥寄存器             |

| 2Ch    | AHB_RST    | AHB 外设复位寄存器             |

| 30h    | APB_RST    | APB 外设复位寄存器             |

| 34h    | SYS_CFG    | 系统配置寄存器                 |

| 38h    | PMU_CTRL   | PMU 控制寄存器               |

**偏移地址：03-00h****时钟配置寄存器**

| 位      | 字段名              | 属性 | 默认 | 字段描述                                                                                               |

|--------|------------------|----|----|----------------------------------------------------------------------------------------------------|

| 31: 18 | -                | RO | 0  | 预留的                                                                                                |

| 17: 16 | MCO_SEL          | RW | 0  | MCU 时钟输出选择<br>00: HSI<br>01: HSE<br>10: LSI<br>11: LSE                                             |

| 15     | -                | RO | 0  | 预留的                                                                                                |

| 14: 12 | APB_PRES         | RW | 0  | APB 时钟预分频<br>0xx: PCLK 未分频<br>100: PCLK2 分频<br>101: PCLK4 分频<br>110: PCLK8 分频<br>111: PCLK16 分频    |

| 11     | -                | RO | 0  | 预留的                                                                                                |

| 10: 8  | AHB_PRES         | RW | 0  | AHB 时钟预分频<br>0xx: HCLK 未分频<br>100: HCLK2 分频<br>101: HCLK4 分频<br>110: HCLK8 分频<br>111: HCLK16 分频    |

| 7: 6   | -                | RO | 0  | 预留的                                                                                                |

| 5      | LFCLK_SWS<br>TS  | RO | 0  | LFCLK 开关状态<br>0: LSI 为 LFCLK<br>1: LSE 为 LFCLK                                                     |

| 4      | LFCLK_SEL        | RW | 0  | LFCLK 开关选择<br>0: LSI 为 LFCLK<br>1: LSE 为 LFCLK                                                     |

| 3: 2   | SYSCLK_SW<br>STS | RO | 0  | 系统时钟开关状态<br>00: RCHF 为系统时钟<br>01: EXTHF 为系统时钟<br>1x: LFCLK 为系统时钟                                   |

| 1: 0   | SYSCLK_SEL       | RW | 0  | 系统时钟开关选择<br>00: HSI 为系统时钟<br>01: HSE 为系统时钟<br>1x: LFCLK 为系统时钟<br>当 MCU 退出停止模式时，硬件强制设置为 00（HSI 选择）。 |

偏移地址： 07-04h

## HSI 控制寄存器

| 位     | 字段名      | 属性 | 默认  | 字段描述                                                                                                                                                  |

|-------|----------|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31: 6 | -        | RO | 0   | 预留的                                                                                                                                                   |

| 5: 4  | HSI_FREC | RW | 01b | HSI OSC 频率选择<br>00: 4MHz<br>01: 8MHz<br>10: 16MHz<br>11: 32MHz                                                                                        |

| 3: 1  | -        | RO | 0   | 预留的                                                                                                                                                   |

| 0     | HSI_EN   | RW | 1   | HSI OSC 时钟启用<br>由软件设置和清除。<br>当进入停止模式时，通过硬件清除以停止 HSI OSC。<br>当 HSI OSC 直接或间接用作系统时钟时（当离开停止模式时），硬件<br>强制保持 HSI OSC ON<br>0: HSI OSC OFF<br>1: HSI OSC ON |

偏移地址： 0B-08h

## LSI 控制寄存器

| 位     | 字段名    | 属性 | 默认 | 字段描述                      |

|-------|--------|----|----|---------------------------|

| 31: 1 | -      | RO | 0  | 预留的                       |

| 0     | LSI_EN | RW | 1  | LSI 启用位<br>0: 禁用<br>1: 启用 |

偏移地址： 0F-0Ch

## LSE 控制寄存器

| 位      | 字段名       | 属性 | 默认 | 字段描述                                 |

|--------|-----------|----|----|--------------------------------------|

| 31: 29 | -         | RO | 0  | 预留的                                  |

| 1      | LSE_CLKEN | RW | 0  | LSE 时钟启用位<br>0: 禁用时钟输出<br>1: 启用时钟输出  |

| 0      | LSE_OSCEN | RW | 0  | LSE 振荡器启用位<br>0: 关闭振荡器核<br>1: 开启振荡器核 |

偏移地址： 13-10h**AHB 外设时钟启用寄存器**

| 位     | 字段名             | 属性 | 默认   | 字段描述                                                                |

|-------|-----------------|----|------|---------------------------------------------------------------------|

| 31: 4 | -               | RO | 0    | 预留的                                                                 |

| 2: 0  | AHB_PORT_C_LKEN | RW | 111b | 位 2: MTP 寄存器访问 HCLK 启用位<br>位 1: EXTI HCLK 启用位<br>位 0: GPIO HCLK 启用位 |

偏移地址： 17-14h**APB 外设时钟启用寄存器**

| 位      | 字段名            | 属性 | 默认 | 字段描述                                                                                                                                                                                                                                                                                                                      |

|--------|----------------|----|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31: 16 | -              | RO | 0  | 预留的                                                                                                                                                                                                                                                                                                                       |

| 15: 0  | APB_PORT_CLKEN | RW | 0  | 位 15: RTC PCLK 启用位<br>位 14: 模拟控制 PCLK 启用位<br>位 13: 预留位<br>位 12: 波形发生器 PCLK 启用位<br>位 11: 预留位<br>位 10: 双定时器 PCLK 启用位<br>位 9: 定时器 1PCLK 启用位<br>位 8: 定时器 0PCLK 启用位<br>位 7: PWM PCLK 启用位<br>位 6: WDT PCLK 启用位<br>位 5: I2C1 PCLK 启用位<br>位 4: 预留位<br>位 3: SPI1 PCLK 启用位<br>位 2: SPI0 PCLK 启用位<br>位 1: UART1 PCLK 启用位<br>位 0: 预留位 |

偏移地址： 1B-18h**外设工作时钟启用寄存器**

| 位     | 字段名       | 属性 | 默认 | 字段描述                         |

|-------|-----------|----|----|------------------------------|

| 31: 2 | -         | RO | 0  | 预留的                          |

| 1     | -         | RW | 0  | 预留位                          |

| 0     | RTC_CLKEN | RW | 0  | RTC 工作时钟启用<br>0: 禁用<br>1: 启用 |

偏移地址： 1F-1Ch

## APB 在睡眠/停止模式下启用外设时钟寄存器

| 位      | 字段名               | 属性 | 默认     | 字段描述                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|-------------------|----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31: 16 | -                 | RO | 0      | 预留的                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 15: 0  | APB_SLP_C<br>LKEN | RW | 0xFFFF | 位 15: RTC PCLK 在睡眠和停止模式下启用<br>位 14: 模拟控制 PCLK 在睡眠和停止模式下启用<br>位 13: 预留位<br>位 12: 波形发生器 PCLK 在睡眠和停止模式启用<br>位 11: 预留位<br>位 10: 双定时器 PCLK 在睡眠和停止模式下启用<br>位 9: 定时器 1PCLK 在睡眠和停止模式下启用<br>位 8: 定时器 0PCLK 在睡眠和停止模式下启用<br>位 7: PWM PCLK 在睡眠和停止模式下启用<br>位 6: WDT PCLK 在睡眠和停止模式下启用<br>位 5: I2C1 PCLK 在睡眠和停止模式下启用<br>位 4: 预留位<br>位 3: SPI1 PCLK 在睡眠和停止模式下启用<br>位 2: SPI0 PCLK 在睡眠和停止模式下启用<br>位 1: UART1 PCLK 在睡眠和停止模式下启用<br>位 0: 预留位 |

偏移地址： 23-20h

## 复位控制寄存器

| 位      | 字段名                | 属性 | 默认 | 字段描述                          |

|--------|--------------------|----|----|-------------------------------|

| 31: 30 | -                  | RO | 0  | 预留的                           |

| 0      | LOCKUP_RE<br>SETEN | RW | 0  | CPU 锁定复位启用位<br>0: 禁用<br>1: 启用 |

偏移地址： 27-24h

## 复位标志寄存器

| 位     | 字段名         | 属性   | 默认 | 字段描述                                                                             |

|-------|-------------|------|----|----------------------------------------------------------------------------------|

| 31: 5 | -           | RO   | 0  | 预留的                                                                              |

| 4     | PINRST_FLAG | RW1C | 0  | 复位引脚标志<br>该位由 NRST 引脚复位来设置<br>通过写入此位或通过 POR 来清除<br>0: 未发生复位引脚低电平<br>1: 发生复位引脚低电平 |

| 3     | LOCKUPRST_  | RW1C | 0  | 锁定复位标志                                                                           |

|   |              |      |   |                                                                                                    |

|---|--------------|------|---|----------------------------------------------------------------------------------------------------|

|   | FLAG         |      |   | 当锁定复位发生时，该位由硬件设置<br>在这个位上写入 1，或者通过 POR 来清除<br>0：未发生锁定复位<br>1：发生锁定复位                                |

| 2 | WDTRST_FLAG  | RW1C | 0 | 看门狗复位标志<br>当看门狗复位发生时，该位由硬件设置<br>在这个位上写入 1，或者通过 POR 来清除<br>0：未发生看门狗复位<br>1：发生看门狗复位                  |

| 1 | SOFTRST_FLAG | RW1C | 0 | 软件复位标志<br>当软件在 NVIC 空间中写入 SYSRESETREQ 时，该位由硬件设置<br>在这个位上写入 1，或者通过 POR 来清除<br>0：未发生软件复位<br>1：发生软件复位 |

| 0 | PORRST_FLAG  | RW1C | 1 | POR/PDR 复位标志<br>当 POR/PDR 复位发生时，该位由硬件设置<br>在这位上写 1 就可以清除<br>0：未发生 POR/PDR 复位<br>1：发生 POR/PDR 复位    |

偏移地址： 2B-28h**外设复位启用密钥寄存器**

| 位     | 字段名      | 属性 | 默认 | 字段描述                                                                           |

|-------|----------|----|----|--------------------------------------------------------------------------------|

| 31: 0 | PRST_KEY | WO | 0  | 外设复位启用密钥寄存器<br>写入 “0x1A2B_3C4D” 表示开启外设软复位功能，写入其他值表示禁用外设软复位功能<br>只写，读取此寄存器返回 0。 |

偏移地址： 2F-2Ch**AHB 外设复位寄存器**

| 位    | 字段名          | 属性 | 默认 | 字段描述                                                    |

|------|--------------|----|----|---------------------------------------------------------|

| 1    | -            | RO | 0  | 预留的                                                     |

| 2: 0 | AHB_PORT_RST | RW | 0  | 高电平<br>位 2：MTP 寄存器访问复位位<br>位 1：EXTI 复位位<br>位 0：GPIO 复位位 |

偏移地址： 33-30h

## APB 外设复位寄存器

| 位      | 字段名              | 属性 | 默认 | 字段描述                                                                                                                                                                                                                                                                |

|--------|------------------|----|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31: 16 | -                | RO | 0  | 预留的                                                                                                                                                                                                                                                                 |

| 15: 0  | APB_PORT_R<br>ST | RW | 0  | 高电平<br>位 15: RTC 复位位<br>位 14: 模拟控制复位位<br>位 13: 预留位<br>位 12: 波形发生器复位位<br>位 11: 预留位<br>位 10: 双定时器复位位<br>位 9: 定时器 0 复位位<br>位 8: 定时器 1 复位位<br>位 7: PWM 复位位<br>位 6: WDT 复位位<br>位 5: I2C1 复位位<br>位 4: 预留位<br>位 3: SPI1 复位位<br>位 2: SPI0 复位位<br>位 1: UART1 复位位<br>位 0: 预留位 |

偏移地址： 37-34h

## 系统配置寄存器

| 位      | 字段名       | 属性 | 默认 | 字段描述                                                                                                                                                                                 |

|--------|-----------|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31: 10 | -         | RO | 0  | 预留的                                                                                                                                                                                  |

| 9: 8   | BOOT_MODE | RO | 0  | 引导引脚状态位选择的引导模式<br>该位为只读。表明 BOOT[1: 0]引脚选的引导模式<br>00: 基地址引导模式的 MTP 主阵列<br>01: MTP 高 4K 字节引导模式<br>1x: 嵌入式 SRAM 引导模式                                                                    |

| 7: 2   | -         | RO | 0  | 预留的                                                                                                                                                                                  |

| 1: 0   | REMAP     | RW | 0  | 内存映射选择位<br>这些位是由软件设置和清除的，这个位控制地址 0x0000_0000 的内部<br>映射，复位后，这些位在 BOOT 引脚选择的内存映射上<br>00: MTP 主阵列的基址在 0x0000_0000 的映射<br>01: MEP 高 4K 字节在 0x0000_0000 的映射<br>1x: SRAM 在 0x0000_0000 的映射 |

偏移地址： 3B-38h

### PMU 控制寄存器

| 位     | 字段名        | 属性 | 默认 | 字段描述                                                     |

|-------|------------|----|----|----------------------------------------------------------|

| 31: 6 | -          | RO | 0  | 预留的                                                      |

| 5: 4  | WKUP_DLY   | RW | 0  | 从停止模式唤醒时延迟时间<br>00: 1us<br>01: 2us<br>10: 4us<br>11: 8us |

| 3: 1  | -          | RO | 0  | 预留的                                                      |

| 0     | WKFREQ_SEL | RW | 0  | 从停止模式唤醒时选择 HSI 频率<br>0: 与进入停止模式前相同<br>1: 8MHz            |

## 8.4 CPU

### 8.4.1 概述

Cortex-M0 处理器是一个入门级的 32 位 ARM Cortex 处理器，专为广泛的嵌入式应用程序而设计。它建立在一个高度区域和功率优化的 32 位处理器核上，具有 3 级管道冯·诺伊曼架构。Cortex-M0 处理器实现了 ARMv6-M 架构，该架构基于 16 位 Thumb 指令集，并包含具有高代码密度的 Thumb-2 技术。

### 8.4.2 处理器配置

表 12 处理器配置

| 功能          | 选择项        | 配置     |

|-------------|------------|--------|

| 中断          | 1~32       | 32     |

| 数据字节序       | 小/大        | 小      |

| SysTick 定时器 | 存在或不存在     | 存在     |

| 监视点         | 0~2        | 2      |

| 断点          | 0~4        | 4      |

| 调试          | 存在或不存在     | 存在     |

| JTAGnSW     | JTAG 或 SWD | SWD    |

| 乘法器         | 快或小        | 快（单循环） |

| 复位所有寄存器     | 是或否        | 是      |

| WIC         | 存在或不存在     | 存在     |

### 8.4.3 核寄存器

表 13 核寄存器

| 名称       | 类型 | 描述                                                                      |

|----------|----|-------------------------------------------------------------------------|

| R0-R12   | RW | 通用寄存器                                                                   |

| SP (R13) | RW | 堆栈指针，SP 可以通过配置控制寄存器选择为 MSP 或 PSP<br>处理模式：MSP（主堆栈指针）<br>线程模式：PSP（进程堆栈指针） |

| LR (R14) | RW | 链接寄存器，它存储子例程、函数调用和异常的返回信息                                               |

| PC (R15) | RW | 程序计数器，它包含当前程序地址                                                         |

| APSR     | RW | 应用程序状态寄存器，它包含条件标志的当前状态                                                  |

| IESR     | RO | 中断程序状态寄存器，它包含当前 ISR 的异常号                                                |

| EPSR     | RO | 执行程序状态寄存器，它包含 Thumb 状态位                                                 |

| PRIMASK  | RW | 优先级屏蔽寄存器，它可以防止激活所有具有可配置优先级的异常                                           |

| CONTROL  | RW | 控制处理器处于线程模式时使用的堆栈                                                       |

#### 8.4.4 异常和中断

系统异常和中断由 NVIC 管理。中断管理功能由位于 SCS 连接的 PPB 总线内的若干可编程寄存器控制。NVIC：

- 支持 32 个中断和 1 个 NMI

- 灵活的中断管理（末尾连锁和迟到异常）

- 处理嵌套中断

- 矢量异常入口

- 中断屏蔽

- 四种中断优先级

当接受异常时，R0-R3、R12、R14、PC 和 xPSR 被自动推送到当前堆栈内存，LR 被更新为 EXC\_RETURN，在异常返回时使用。

在异常处理过程结束时，如果没有任何其他异常需要处理，则恢复先前存储在堆栈内存中的寄存器值，并恢复中断的程序。

如果 CPU 处于 HardFault 或 NMI 处理过程中，再次发生 HardFault，CPU 将进入锁定状态，CPU 核将被重置，如果设置了 LOCKUPRESET，则允许系统复位。

表 14 中断向量表

| 位置    | IRQ 号 | 异常类型                        | 优先级     | 向量地址        |

|-------|-------|-----------------------------|---------|-------------|

| 0     | -     | 初始 SP 值                     | -       | 0x0000_0000 |

| 1     | -     | 复位                          | -3, 最高级 | 0x0000_0004 |

| 2     | -14   | NMI (WDT)                   | -2      | 0x0000_0008 |

| 3     | -13   | Hardfault                   | -1      | 0x0000_000C |

| 4-10  | -     | 预留的                         | -       | -           |

| 11    | -5    | SVC                         | 可配置     | 0x0000_002C |

| 12-13 | -     | 预留的                         | -       | -           |

| 14    | -2    | PendSV                      | 可配置     | 0x0000_0038 |

| 15    | -1    | SysTick                     | 可配置     | 0x0000_003C |

| 16    | 0     | LVD (EXTI line 24)          | 可配置     | 0x0000_0040 |

| 17    | 1     | RTC                         | 可配置     | 0x0000_0044 |

| 18    | 2     | COMPO (EXTI line 25)        | 可配置     | 0x0000_0048 |

| 19    | 3     | COMP1 (EXTI line 26)        | 可配置     | 0x0000_004C |

| 20    | 4     | GPIO0_7 (EXTI line 0-7)     | 可配置     | 0x0000_0050 |

| 21    | 5     | GPIO8_15 (EXTI line 8-15)   | 可配置     | 0x0000_0054 |

| 22    | 6     | GPIO16_23 (EXTI line 16-23) | 可配置     | 0x0000_0058 |

| 23    | 7     | MTP                         | 可配置     | 0x0000_005C |

| 24    | 8     | 预留位                         | 可配置     | 0x0000_0060 |

| 25    | 9     | 预留位                         | 可配置     | 0x0000_0064 |

| 26    | 10    | 预留位                         | 可配置     | 0x0000_0068 |

| 27    | 11    | 预留位                         | 可配置     | 0x0000_006C |

| 28    | 12    | 预留位                         | 可配置     | 0x0000_0070 |

| 29    | 13    | UART1                       | 可配置     | 0x0000_0074 |

| 30    | 14    | SPI0                        | 可配置     | 0x0000_0078 |

| 31    | 15    | SPI1                        | 可配置     | 0x0000_007C |

| 32    | 16    | 预留位                         | 可配置     | 0x0000_0080 |

| 33    | 17    | 预留位                         | 可配置     | 0x0000_0084 |

| 34    | 18    | I2C1 事件                     | 可配置     | 0x0000_0088 |

| 35    | 19    | I2C1 错误                     | 可配置     | 0x0000_008C |

|    |    |              |     |             |

|----|----|--------------|-----|-------------|

| 36 | 20 | PWM          | 可配置 | 0x0000_0090 |

| 37 | 21 | 基础 TIM0      | 可配置 | 0x0000_0094 |

| 38 | 22 | 基础 TIM1      | 可配置 | 0x0000_0098 |

| 39 | 23 | 双 TIM        | 可配置 | 0x0000_009C |

| 40 | 24 | 过温 (EXTI 29) | 可配置 | 0x0000_00A0 |

| 41 | 25 | -            | 可配置 | 0x0000_00A4 |

| 42 | 26 | -            | 可配置 | 0x0000_00A8 |

| 43 | 27 | -            | 可配置 | 0x0000_00AC |

| 44 | 28 | -            | 可配置 | 0x0000_00B0 |

| 45 | 29 | -            | 可配置 | 0x0000_00B4 |

| 46 | 30 | -            | 可配置 | 0x0000_00B8 |

| 47 | 31 | -            | 可配置 | 0x0000_00BC |

#### 8.4.5 调试

基本调试功能包括：

- 处理器暂停，单步操作

- 处理器核寄存器访问

- 四个硬件断点

- 两个监视点

- 无限软件断点（BKPT 指令）

- 全系统内存访问

- SWD 接口

## 8.5 Cortex-M0 外设

### 8.5.1 概述

私有外设总线（PPB）的地址映射为：

表 15 核外设寄存器区

| 地址                    | 核外设         |

|-----------------------|-------------|

| 0xE000E008–0xE000E00F |             |

| 0xE000ED00–0xE000ED3F | 系统控制块       |

| 0xE000E010–0xE000E01F | SysTick 定时器 |

| 0xE000E100–0xE000E4EF |             |

| 0xE000EF00–0xE000EF03 | 嵌套矢量中断控制器   |

### 8.5.2 嵌套矢量中断控制器

本节描述了嵌套矢量中断控制器（NVIC）和它使用的寄存器。NVIC 支持：

- 1 ~ 32 个中断

- 每个中断的可编程优先级为 0-192，步骤为 64。较高的级别对应较低的优先级，因此级别 0 是最高的中断优先级

- 中断信号的电平和脉冲检测

- 中断末尾连锁

- 外部不可屏蔽中断（NMI）

处理器在异常条目上自动堆叠其状态，并在异常退出时解除堆栈此状态，没有指令执行时间。这提供了低延迟的异常处理。

#### 8.5.2.1 寄存器

表 16 NVIC 寄存器

| 地址                        | 首字母缩写  | 类型 | 复位值        | 寄存器描述     |

|---------------------------|--------|----|------------|-----------|

| 0xE000E100                | ISET   | RW | 0x00000000 | 中断设置启用寄存器 |

| 0xE000E180                | ICER   | RW | 0x00000000 | 中断清除启用寄存器 |

| 0xE000E200                | ISPR   | RW | 0x00000000 | 中断设置挂起存器  |

| 0xE000E280                | ICPR   | RW | 0x00000000 | 中断解挂寄存器   |

| 0xE000E400–<br>0xE000E41C | IPR0–7 | RW | 0x00000000 | 中断优先寄存器   |

地址： 0xE000E100**中断启用设置寄存器**

| 位     | 字段名    | 属性 | 默认 | 字段描述                                                                                   |

|-------|--------|----|----|----------------------------------------------------------------------------------------|

| 31: 0 | SETENA | RW | 0  | <p>中断设置启用位</p> <p>写入：</p> <p>0=无作用<br/>1=启用中断。</p> <p>读取：</p> <p>0=中断禁用<br/>1=中断启用</p> |

地址： 0xE000E180**中断启用设置寄存器**

| 位     | 字段名    | 属性 | 默认 | 字段描述                                                                                  |

|-------|--------|----|----|---------------------------------------------------------------------------------------|

| 31: 0 | CLRENA | RW | 0  | <p>中断清除启用位</p> <p>写入：</p> <p>0=无作用<br/>1=禁用中断</p> <p>读取：</p> <p>0=中断禁用<br/>1=中断启用</p> |

地址： 0xE000E200**中断解挂寄存器**

| 位     | 字段名     | 属性 | 默认 | 字段描述                                                                                                                        |

|-------|---------|----|----|-----------------------------------------------------------------------------------------------------------------------------|

| 31: 0 | CLRPEND | RW | 0  | <p>中断解挂位</p> <p>写入：</p> <p>0=无作用<br/>1=删除挂起状态的中断</p> <p>读取：</p> <p>0=中断未挂起<br/>1=中断挂起</p> <p>向 ICPR 位写入 1 不会影响相应中断的活动状态</p> |

地址： 0xE000E280**中断设置挂起寄存器**

| 位     | 字段名     | 属性 | 默认 | 字段描述                                   |

|-------|---------|----|----|----------------------------------------|

| 31: 0 | SETPEND | RW | 0  | <p>中断挂起控制位</p> <p>写入：</p> <p>0=无作用</p> |

|  |  |  |  |                                                                                                       |

|--|--|--|--|-------------------------------------------------------------------------------------------------------|

|  |  |  |  | 1=将中断状态更改为挂起<br>读取：<br>0=中断未挂起<br>1=中断挂起<br>将 1 写入与对应的 ISPR 位：<br>■ 挂起中断无作用<br>■ 一个被禁用的中断将中断的状态设置为挂起。 |

|--|--|--|--|-------------------------------------------------------------------------------------------------------|

地址： 0xE000E400–0xE000E41C

### 中断优先级寄存器

| 位      | 字段名        | 属性 | 默认 | 字段描述                                                                                                  |

|--------|------------|----|----|-------------------------------------------------------------------------------------------------------|

| 31: 24 | PRI_(4n+3) | RW | 0  | 每个优先级字段都有一个优先级值，0-192。该值越低，对应中断的优先级越高。处理器只实现了每个字段的位[7: 6]，位[5: 0]读为零，写忽略。这意味着将 255 写入优先级寄存器将值保存到 192。 |

| 23: 16 | PRI_(4n+2) | RW | 0  |                                                                                                       |

| 15: 8  | PRI_(4n+1) | RW | 0  |                                                                                                       |

| 7: 0   | PRI_(4n)   | RW | 0  |                                                                                                       |

### 8.5.3 系统控制块

SCB（系统控制块）提供系统实现信息和系统控制。这包括系统异常的配置、控制和报告。

表 17 SCB 寄存器

| 地址         | 首字母缩写 | 类型 | 复位值        | 寄存器描述        |

|------------|-------|----|------------|--------------|

| 0xE000ED00 | CPUID | RO | 0x410CC200 | CPUID 寄存器    |

| 0xE000ED04 | ICSR  | RW | 0x00000000 | 中断控制和状态寄存器   |

| 0xE000ED0C | AIRSR | RW | 0xFA050000 | 应用中断和复位控制寄存器 |

| 0xE000ED10 | SCR   | RW | 0x00000000 | 系统控制寄存器      |

| 0xE000ED14 | CCR   | RO | 0x00000204 | 配置和控制寄存器     |

| 0xE000ED1C | SHPR2 | RW | 0x00000000 | 系统处理优先级寄存器 2 |

| 0xE000ED20 | SHPR3 | RW | 0x00000000 | 系统处理优先级寄存器 3 |

地址： 0xE000ED00

### CPUID 寄存器

| 位      | 字段名 | 属性 | 默认   | 字段描述             |

|--------|-----|----|------|------------------|

| 31: 24 | 实现器 | RO | 0x41 | 实现器：<br>0x41=ARM |

| 23: 20 | 版本  | RO | 0    | 版本：<br>0x0=修订 0  |

| 19: 16 | 常数  | RO | 0xC  | 定义处理器体系结构的常数：    |

|       |     |    |       |                             |

|-------|-----|----|-------|-----------------------------|

|       |     |    |       | 0xC=ARMv6-M 架构              |

| 15: 4 | 部件号 | RO | 0xC20 | 处理器的部件号：<br>0xC20=Cortex-M0 |

| 3: 0  | 修订  | RO | 0     | 修订号：<br>0x0=补丁 0            |

地址： 0xE000ED04

### 中断控制与状态寄存器

| 位      | 字段名        | 属性 | 默认 | 字段描述                                                                                                                                                                                                                          |

|--------|------------|----|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31     | NMIPENDSET | RW | 0  | NMI 设置挂起位。<br>写入：<br>0=无作用<br>1=将 NMI 异常状态变更为挂起<br>读取：<br>0=NMI 异常不挂起<br>1=NMI 异常挂起<br>因为 NMI 是最高优先级的异常,通常处理器一旦检测到对这个位写 1,就会进入 NMI 异常处理程序。然后进入处理程序将此位清除为 0。这意味着只有当处理器 ix 执行 NMI 异常处理程序时, NMI 信号被重新声明时, NMI 异常处理程序对该位的读取才返回 1。 |

| 30: 29 | -          | RO | 0  | 预留的                                                                                                                                                                                                                           |

| 28     | PENDSVSET  | RW | 0  | PendSV 设置挂起位。<br>写入：<br>0=无作用<br>1=将 PendSV 异常状态变更为挂起<br>读取：<br>0=PendSV 异常不挂起<br>1=PendSV 异常挂起<br>在这个位上写 1 是设置 PendSV 异常状态变更为挂起的唯一方式。                                                                                        |

| 27     | PENDSVCLR  | WO | 0  | PendSV 解挂位。<br>写入：<br>0=无作用<br>1=从 PendSV 异常中移除挂起状态                                                                                                                                                                           |

| 26     | PENDSTSET  | RW | 0  | SysTick 异常设置挂起位<br>写入：<br>0=无作用<br>1=将 sysTick 异常状态变更为挂起<br>读取：<br>0=SysTick 异常不挂起<br>1=SysTick 异常挂起                                                                                                                          |

| 25     | PENDSTCLR  | WO | 0  | SysTick 异常解挂位<br>写入：<br>0=无作用<br>1=从 SysTick 异常中移除挂起状态                                                                                                                                                                        |

| 24: 23 | -          | RO | 0  | 预留的                                                                                                                                                                                                                           |

|        |                 |    |   |                                                       |

|--------|-----------------|----|---|-------------------------------------------------------|

| 22     | ISRPENDIN<br>G  | RO | 0 | 中断挂起标志，不包括 NMI 和故障：<br>0=中断未挂起<br>1=中断挂起              |

| 21: 18 | -               | RO | 0 | 预留的                                                   |

| 17: 12 | VECTPENDI<br>NG | RO | 0 | 最高优先级挂起的启用异常的异常号：<br>0=没有挂起的异常<br>非零=最高优先级挂起的启用异常的异常号 |

| 11: 6  | -               | RO | 0 | 预留的                                                   |

| 5: 0   | VECTACTI<br>VE  | RO | 0 | 包含活动异常号：<br>0=线程模式<br>非零=当前活动异常的异常号                   |

**地址：** 0xE000ED0C

### 应用中断和复位控制寄存器

| 位      | 字段名               | 属性 | 默认     | 字段描述                                                    |

|--------|-------------------|----|--------|---------------------------------------------------------|

| 31: 16 | VECTKEY           | RW | 0xFA05 | 寄存器密钥<br>写入时，将 0x05FA 写入 VECTKEY，否则写入将被忽略<br>读取为 0xFA05 |

| 15     | ENDIANESS         | RO | 0      | 实现了数据字节顺序：<br>0=小端<br>1=大端                              |

| 14: 3  | -                 | RO | 0      | 预留的                                                     |

| 2      | SYSRESETR<br>EQ   | WO | 0      | 系统复位请求：<br>0=无作用<br>1=请求系统级复位<br>该位读取为 0                |

| 1      | VECTCLRAC<br>TIVE | WO | 0      | 仅供调试使用。这个位读为 0。当写入寄存器时，你必须将 0 写入这个位，否则行为是不可预测的。         |

| 0      | -                 | RO | 0      | 预留的                                                     |

**地址：** 0xE000ED10

### 系统控制寄存器

| 位     | 字段名       | 属性 | 默认 | 字段描述                                                                                                                                                                         |

|-------|-----------|----|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31: 5 | -         | RO | 0  | 预留的                                                                                                                                                                          |

| 4     | SEVONPEND | RW | 0  | 发送事件挂起位：<br>0=只有启用的中断或事件才能唤醒处理器，禁用的中断将被排除在外<br>1=启用的事件和所有中断(包括禁用的中断)都可以唤醒处理器。<br>当事件或中断进入挂起状态时，事件信号将从 WFE 唤醒处理器。如果处理器没有等待事件，则该事件将被注册并影响下一个 WFE。<br>处理器也会在 SEV 指令或外部事件执行时被唤醒。 |

| 3     | -         | RO | 0  | 预留的                                                                                                                                                                          |

| 2     | SLEEPDEEP | RW | 0  | 控制处理器是否使用睡眠或深度睡眠作为低功耗模式：<br>0=睡眠                                                                                                                                             |

|   |             |    |   |                                                                                                     |

|---|-------------|----|---|-----------------------------------------------------------------------------------------------------|

|   |             |    |   | 1=深度睡眠                                                                                              |

| 1 | SLEEPONEXIT | RW | 0 | 处理模式返回线程模式时表明退出后睡眠：<br>0=返回线程模式时不要睡眠<br>1=从 ISR 返回线程模式进入睡眠或深睡眠<br>将该位设置为 1 可以使中断驱动的应用程序避免返回空的主应用程序。 |

| 0 | -           | RO | 0 | 预留的                                                                                                 |

地址： 0xE000ED14

#### 配置和控制寄存器

| 位      | 字段名             | 属性 | 默认 | 字段描述                                                                                  |

|--------|-----------------|----|----|---------------------------------------------------------------------------------------|

| 31: 10 | -               | RO | 0  | 预留的                                                                                   |

| 9      | STKALIGN        | RO | 1  | 总是读取为 1，指示异常条目上的 8 字节堆栈对齐。在异常进入时，处理器使用堆叠 PSR 的[9]位来指示堆栈对齐。在从异常返回时，它使用这个堆叠位来恢复正确的堆栈对齐。 |

| 8: 4   | -               | RO | 0  | 预留的                                                                                   |

| 3      | UNALIGN_T<br>RP | RO | 1  | 始终读取为 1，表示所有未对齐的访问都会生成硬故障。                                                            |

| 2: 0   | -               | RO | 0  | 预留的                                                                                   |

地址： 0xE000ED1C

#### 系统处理优先级寄存器 2

| 位      | 字段名    | 属性 | 默认 | 字段描述                  |

|--------|--------|----|----|-----------------------|

| 31: 24 | PRI_11 | RW | 0  | 系统处理程序 11 SVCALL 的优先级 |

| 23: 0  | -      | RO | 0  | 预留的                   |

地址： 0xE000ED20

#### 系统处理优先级寄存器 3

| 位      | 字段名    | 属性 | 默认 | 字段描述                     |

|--------|--------|----|----|--------------------------|

| 31: 24 | PRI_15 | RW | 0  | 系统处理程序优先级 15， SysTick 异常 |

| 23: 16 | PRI_14 | RW | 0  | 系统处理程序 14 的优先级， PendSV   |

| 15: 0  | -      | RO | 0  | 预留的                      |

### 8.5.4 SysTick 定时器

当启用时，定时器从重新加载值开始倒数到零，在下一个时钟周期中重新加载（包装到）SYST\_RVR 中的值，然后在随后的时钟周期中递减。将 0 的值写入 SYST\_RVR 将在下一次换行时禁用计数器。当计数器转换为 0 时，COUNTFLAG 状态位被设置为 1。读取 SYST\_CSR 将 COUNTFLAG 位清除为 0。当处理器停止调试时，计数器不会递减。

软件可以配置 SysTick 定时器选择 SCLK 作为它的时钟源，或一个替代时钟源：FCLK 时钟 8 分频。

#### 8.5.4.1 寄存器

表 18 SysTick 定时器寄存器

| 地址         | 首字母缩写      | 类型 | 复位值        | 寄存器描述            |

|------------|------------|----|------------|------------------|

| 0xE000E010 | SYST_CSR   | RO | 0x00000000 | SysTick 控制与状态寄存器 |

| 0xE000E014 | SYST_RVR   | RW | 0x00000000 | SysTick 重新加载值寄存器 |

| 0xE000E018 | SYST_CVR   | RW | 0x00000000 | SysTick 当前值寄存器   |

| 0xE000E01C | SYST_CALIB | RW | 0x00000000 | SysTick 校准值寄存器   |

**地址：** 0xE000E010

#### SysTick 控制与状态寄存器

| 位      | 字段名       | 属性 | 默认 | 字段描述                                                                  |

|--------|-----------|----|----|-----------------------------------------------------------------------|

| 31: 17 | -         | RO | 0  | 预留的                                                                   |

| 16     | COUNTFLAG | RO | 0  | 如果计时器自该寄存器最后一次读取以来计数为 0，则返回 1                                         |

| 15: 3  | -         | RO | 0  | 预留的                                                                   |

| 2      | CLKSOURCE | RW | 0  | 选择 SysTick 定时器源：<br>0=外部参考时钟<br>1=处理器时钟                               |

| 1      | TICKINT   | RW | 0  | 启用 SysTick 异常请求：<br>0=倒数到零不会断言 SysTick 异常请求<br>1=倒数到零来断言 SysTick 异常请求 |

| 0      | ENABLE    | RW | 0  | 启用计数器：<br>0=禁用计数器<br>1=启用计数器                                          |

**地址：** 0xE000E014

#### SysTick 控制与状态寄存器

| 位      | 字段名    | 属性 | 默认 | 字段描述                                                                                                                    |

|--------|--------|----|----|-------------------------------------------------------------------------------------------------------------------------|

| 31: 24 | -      | RO | 0  | 预留的                                                                                                                     |

| 23: 0  | RELOAD | RW | 0  | 当计数器启用并且达到 0 时加载到 SYST_CVR 的值。<br>RELOAD 值可以是 0x00000001-0x00FFFFFF 范围内的任何值。您可以编程值 0，但这无效，因为当从 1 计算到 0 时，SysTick 异常请求和计 |

|  |  |  |  |                                                                                                   |

|--|--|--|--|---------------------------------------------------------------------------------------------------|

|  |  |  |  | 数标志被激活。<br>要生成具有 N 个处理器时钟周期的多次激发定时器，请使用重加载值 N-1。例如，如果每 100 个时钟脉冲需要一次 SysTick 中断，则将 RELOAD 设置为 99。 |

|--|--|--|--|---------------------------------------------------------------------------------------------------|

地址： 0xE000E018

#### SysTick 当前值寄存器

| 位      | 字段名     | 属性 | 默认 | 字段描述                                                                 |

|--------|---------|----|----|----------------------------------------------------------------------|

| 31: 24 | -       | RO | 0  | 预留的                                                                  |

| 23: 0  | CURRENT | RW | 0  | 读取返回 SysTick 计数器的当前值。<br>写入任何值都会清除字段 0，也会清除 SYST_CSR.COUNTFLAG 位到 0。 |

地址： 0xE000E01C

#### SysTick 校准值寄存器

| 位      | 字段名   | 属性 | 默认 | 字段描述                 |

|--------|-------|----|----|----------------------|

| 31     | NOREF | RO | 0  | 读取为零，表示提供单独的参考时钟。    |

| 30     | SKEW  | RO | 1  | 读取为 1, 10 ms 的校准值不准确 |

| 29: 24 | -     | RO | 0  | 预留的                  |

| 23: 0  | TENMS | RO | 0  | 校准值不可用               |

## 8.6 通用输入/输出 (GPIO)

### 8.6.1 概述

GPIO 块实现了一个具有 19 个 I/O 的 AHB-Lite 接口的通用 I/O 块，其中每个 I/O 都可以通过内存映射寄存器独立配置。通过 AHB 接口，所有寄存器都是可读可写的。

实际控制信号功能和计数可能会根据所选择的第三方 IOPAD 型号而发生变化。

#### 8.6.1.1 功能列表

- 输入输出方向控制

- 每个引脚弱上拉/下拉

- 输出推挽/开漏启用控制

- 输出位设置/复位控件，支持原子读/修改写操作

- 输出驱动器强度选择

- 输入缓冲区选择 (CMOS/施密特)

- 切换速率选择

- 模拟通道启用

- 替代功能

- 两个 HCLK 循环切换输出能力

### 8.6.2 功能描述

#### 8.6.2.1 三态数字 I/O 单元

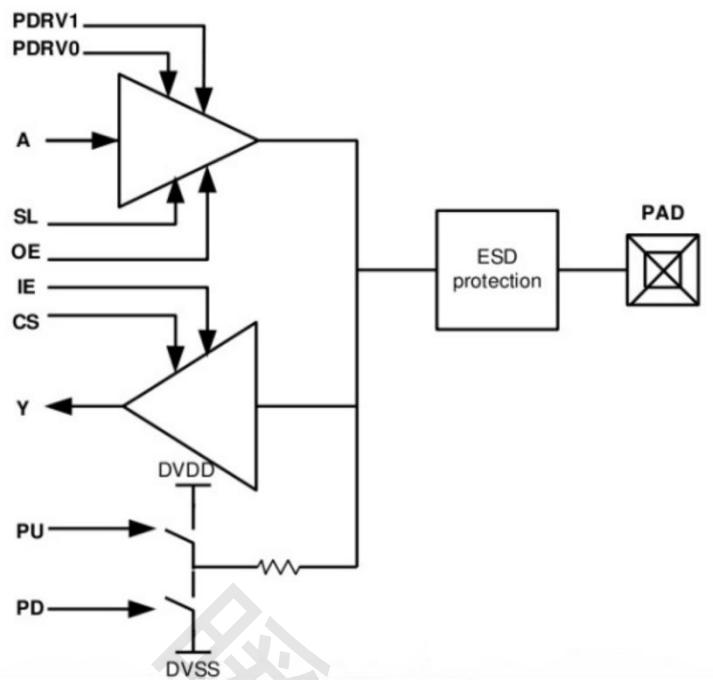

I/O 板是一个 5V 三态双向 I/O 板，具有 4mA、8mA、12mA 和 16mA 的可编程输出驱动强度。它可以被编程为 CMOS 输入或施密特触发器输入，带或不带上拉/下拉。在快速转换 16mA 驱动强度模式下，它可以在 100MHz 的频率下以 30pF 的电容性负载运行。控制引脚 PDRV0、PDRV1、SL、CS 的使用如寄存器表所示。

图 8 I/O 单元功能示意图

单元格的逻辑操作如下所示。

表 19 逻辑操作表

## 驱动器功能

| 输入 |    |    |   | 输出   |

|----|----|----|---|------|

| OE | PU | PO | A | PAD  |

| 0  | 0  | 0  | X | Hi-Z |

| 0  | 0  | 1  | X | 弱 0  |

| 0  | 1  | 0  | X | 弱 1  |

| 0  | 1  | 1  | X | Hi-Z |

| 1  | X  | X  | 0 | 0    |

| 1  | X  | X  | 1 | 1    |

## 接收器功能

| 输入 |    |    |     | 输出 |

|----|----|----|-----|----|

| IE | PU | PD | PAD | Y  |

| 0  | X  | X  | X   | 0  |

| 1  | X  | X  | 0   | 0  |

| 1  | X  | X  | 1   | 1  |

| 1  | 0  | 1  | 弱 0 | 0  |

| 1  | 1  | 0  | 弱 1 | 1  |

## 8.6.2.2 替代功能多路复用器

设备 I/O 引脚通过多路复用器连接到板上外设/模块，该多路复用器一次只允许一个外设备用功能连接到一个 I/O 引脚。这样，同一 I/O 引脚上可用的外设之间就不会发生冲突。

通过配置 GPIO\_ALTF 寄存器，每个 I/O 有 4 个替代功能。GPIOx\_ALTF[1: 0]配置为 2'b11 时，pad 用于模拟功能。详细的替代功能映射信息显示在寄存器表中。

复位后多路复用器选择为替代功能 0。GPIO0/1 默认为调试引脚：SWCLK 和 SWDIO。复位后 SWCLK 为下拉，SWDIO 为上拉。

#### 8.6.2.3 输入配置

当通过配置 GPIO\_IE 寄存器将 GPIO 引脚配置为输入时：

- 可选择施密特触发器或 CMOS 输入

- 可以选择弱的上拉电阻或下拉电阻

- 在每个 AHB 时钟周期中，I/O 引脚上的数据被采样到输入数据寄存器中

- 对输入数据寄存器的读访问提供了 I/O 状态

#### 8.6.2.4 输出配置

当通过配置 GPIO\_OE 寄存器将 GPIO 引脚配置为输出时：

- 可选择开漏模式推挽模式

- 可以选择弱的上拉电阻或下拉电阻

- 输出转换速率可配置为快或慢

- 输出驱动强度可配置为 4mA/8mA/12mA/16mA

#### 8.6.2.5 模拟功能

当 GPIO 引脚配置为模拟功能时：

- 禁用输出

- 禁用输入

- 禁用上拉和下拉

- 对输入数据寄存器的读访问返回 0

- 如果 I/O 用于多个模拟功能，则只能同时启用一个功能

#### 8.6.2.6 I/O 数据按位处理

对于 GPIO\_DATAOUT 中的每个位，对应 GPIO\_bitsET 寄存器和 GPIO\_bit CLR 寄存器中的两个控制位。当写 1 到 GPIO\_bitsET[i] 时，设置对应的 DATAOUT[i] 位。当写 1 到 GPIO\_bit CLR[i] 时，复位对应的 DATAOUT[i] 位。

将 GPIO\_bitsET[i] 或 GPIO\_BICLR[i] 中的任何位写入 0 对 GPIO\_DATAOUT 中的相应位没有任何影响。如果试图同时设置和重置 GPIO\_bitset 和 GPIO\_bit CLR 中的位，则设置操作优先。

从 GPIO\_DATAOUT 读取，GPIO\_bitsET 或 GPIO\_bit CLR 都返回当前的 DATAOUT 值。

逐位处理的目的是允许对任何 GPIO\_DATAOUT 寄存器进行原子读/修改访问。这样，在读取访问和修改访问之间就不会有发生 IRQ 的风险。

## 8.6.3 寄存器

表 20 GPIO 寄存器

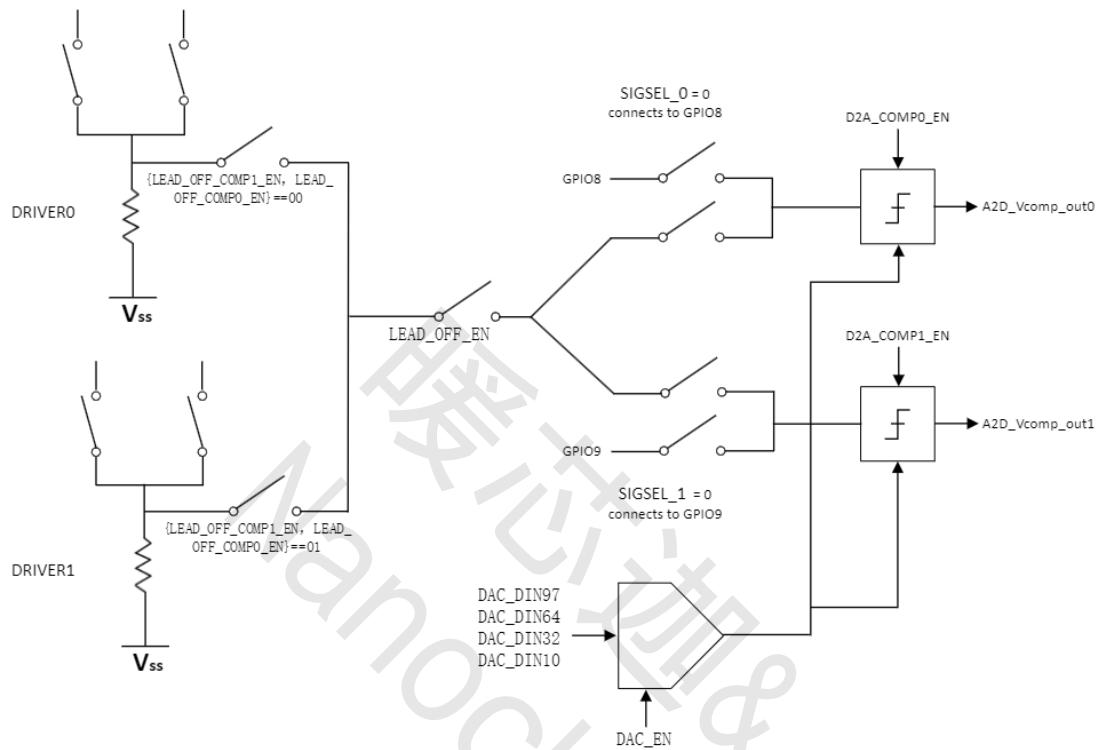

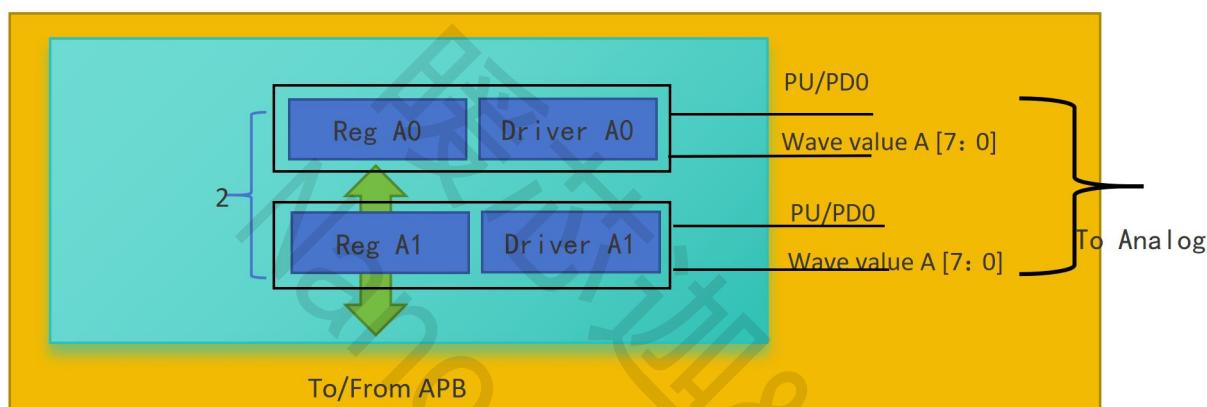

| 偏移  | 首字母缩写        | 寄存器描述                |