# Haawking\_DSC280103Px\_数字信号控制器

## 数据手册

V2. 1

北京中科昊芯科技有限公司

2024 年 8 月

## 历史版本记录

| 版本号    | 内容描述                                                                                                 | 时间         |

|--------|------------------------------------------------------------------------------------------------------|------------|

| V0.0.1 | 2.3 引脚分配的做成                                                                                          | 2022.11.11 |

| V0.0.2 | 初版做成                                                                                                 | 2022.11.15 |

| V0.0.3 | 2.2 产品编码添加, 2.3 引脚分配视图更新                                                                             | 2022.11.16 |

| V0.0.4 | 根据 20221119 版初审意见, 修改如下: 2.1 器件特性列表中删除无关模块; 2.2 产品编码中的 280103 归纳为一个产品系列; 2.3 引脚分配视图: 将 PIN1 放到左下一的位置 | 2022.11.21 |

| V0.0.5 | 添加 7. 机械数据、8. 订货信息                                                                                   | 2022.12.19 |

| V0.6   | 移除 X1 和 X2 片载振荡器功能                                                                                   | 2022.12.22 |

| V0.7   | 更新产品后缀为 S, 优化文档                                                                                      | 2024.08.15 |

|        |                                                                                                      |            |

|        |                                                                                                      |            |

|        |                                                                                                      |            |

|        |                                                                                                      |            |

|        |                                                                                                      |            |

|        |                                                                                                      |            |

|        |                                                                                                      |            |

|        |                                                                                                      |            |

# 目录

|                                    |    |

|------------------------------------|----|

| 1. 器件概述 .....                      | 5  |

| 1. 1 产品特性 .....                    | 5  |

| 1. 2 应用 .....                      | 6  |

| 2. DSC280103Px 简介 .....            | 7  |

| 2. 1 器件特性 .....                    | 7  |

| 2. 2 产品编码 .....                    | 8  |

| 2. 3 引脚分配 .....                    | 9  |

| 2. 4 信号说明 .....                    | 10 |

| 3. 功能概述 .....                      | 14 |

| 3. 1 系统架构 .....                    | 14 |

| 3. 2 内存映射 .....                    | 15 |

| 3. 3 简要说明 .....                    | 16 |

| 3. 3. 1 HXS320F280103Px DSC .....  | 16 |

| 3. 3. 2 内存总线 .....                 | 16 |

| 3. 3. 3 外设总线 .....                 | 16 |

| 3. 3. 4 实时 JTAG 和分析 .....          | 16 |

| 3. 3. 5 闪存 .....                   | 17 |

| 3. 3. 6 M0、M1、L0、L1 SARAM .....    | 17 |

| 3. 3. 7 引导 ROM .....               | 18 |

| 3. 3. 7. 1 JTAG 引导模式 .....         | 18 |

| 3. 3. 7. 2 GetMode 获取模式 .....      | 19 |

| 3. 3. 7. 3 引导加载器使用的外设引脚 .....      | 19 |

| 3. 3. 8 安全性 .....                  | 19 |

| 3. 3. 9 外设中断扩展（PIE）模块 .....        | 20 |

| 3. 3. 10 外部中断（XINT1-XINT3） .....   | 21 |

| 3. 3. 11 内部振荡器、外部振荡器和 PLL .....    | 21 |

| 3. 3. 12 看门狗 .....                 | 21 |

| 3. 3. 13 外设时钟 .....                | 21 |

| 3. 3. 14 低功耗模式 .....               | 21 |

| 3. 3. 15 通用输入/输出（GPIO）复用器 .....    | 22 |

| 3. 3. 16 32 位 CPU 定时器（0,1,2） ..... | 22 |

| 3. 3. 17 控制外设 .....                | 23 |

| 3. 3. 18 串行端口外设 .....              | 23 |

| 3. 4 寄存器映射 .....                   | 24 |

|                                         |    |

|-----------------------------------------|----|

| 3.5 器件仿真寄存器 .....                       | 25 |

| 3.6 中断系统 .....                          | 25 |

| 3.7 VREG/BOR/POR .....                  | 28 |

| 3.7.1 VREG .....                        | 28 |

| 3.7.1.1 使用片上 VREG .....                 | 28 |

| 3.7.1.2 不使用片上 VREG .....                | 29 |

| 3.7.2 片上上电复位 (POR) 和掉电复位 (BOR) 电路 ..... | 29 |

| 3.8 系统控制 .....                          | 30 |

| 3.8.1 内部零引脚振荡器 .....                    | 32 |

| 3.8.2 晶体振荡器选项 .....                     | 33 |

| 3.8.3 基于 PLL 的时钟模块 .....                | 33 |

| 3.9 低功耗模块 .....                         | 34 |

| 4. 外设 .....                             | 36 |

| 4.1 模拟器件 .....                          | 36 |

| 4.1.1 ADC 特性 .....                      | 36 |

| 4.1.2 比较器模块 .....                       | 41 |

| 4.2 同步串行通信接口 (SPI) 模块 .....             | 41 |

| 4.3 异步串行通信接口 (SCI) 模块 .....             | 43 |

| 4.4 内部集成电路接口 (I2C) 模块 .....             | 45 |

| 4.5 增强型 PWM 模块 (ePWM1/2/3/4) .....      | 47 |

| 4.6 高分辨率 PWM 模块 (HRPWM) .....           | 50 |

| 4.7 增强型脉冲捕获模块 (eCAP) .....              | 50 |

| 4.8 增强型正交编码器模块 (eQEP) .....             | 52 |

| 4.9 JTAG 端口 .....                       | 55 |

| 4.10 GPIO 控制寄存器 .....                   | 57 |

| 4.11 直接存储访问存储单元 (DMA) .....             | 61 |

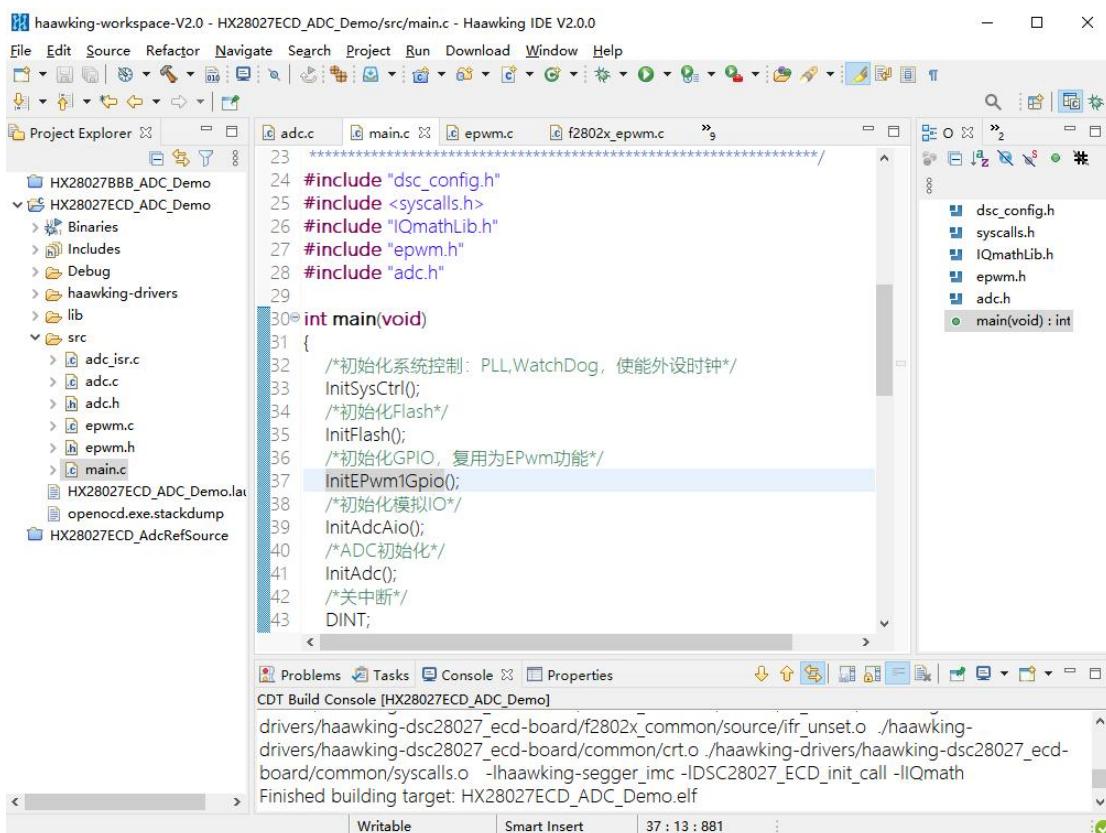

| 5. 开发支持 .....                           | 66 |

| 5.1 集成开发环境 Haawking IDE .....           | 66 |

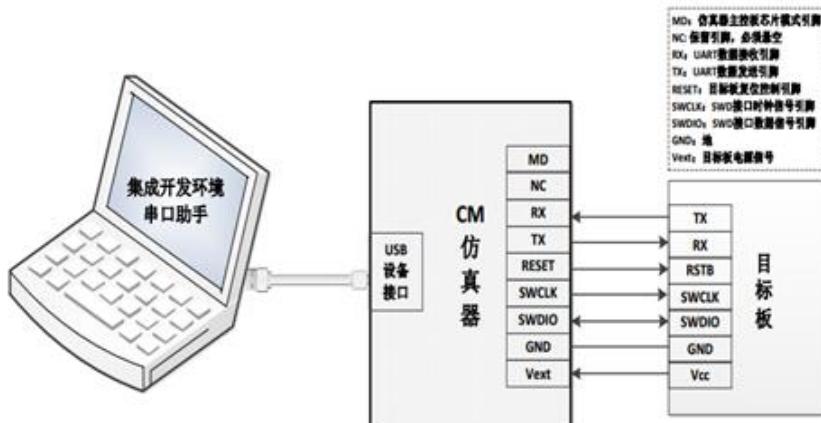

| 5.2 仿真器 .....                           | 68 |

| 5.2.1 简介 .....                          | 68 |

| 5.2.2 概览 .....                          | 68 |

| 5.2.2.1 特性 .....                        | 68 |

| 5.3 串口下载器 .....                         | 69 |

| 6. 电气规范 .....                           | 71 |

| 6.1 绝对最大额定值 .....                       | 71 |

| 6.2 建议的运行条件 .....                       | 71 |

| 6.3 ESD 额定值 .....                       | 72 |

| 6.4 电气特性 .....                          | 72 |

---

|                   |    |

|-------------------|----|

| 6. 5 电流功耗 .....   | 74 |

| 6. 6 散热设计考虑 ..... | 75 |

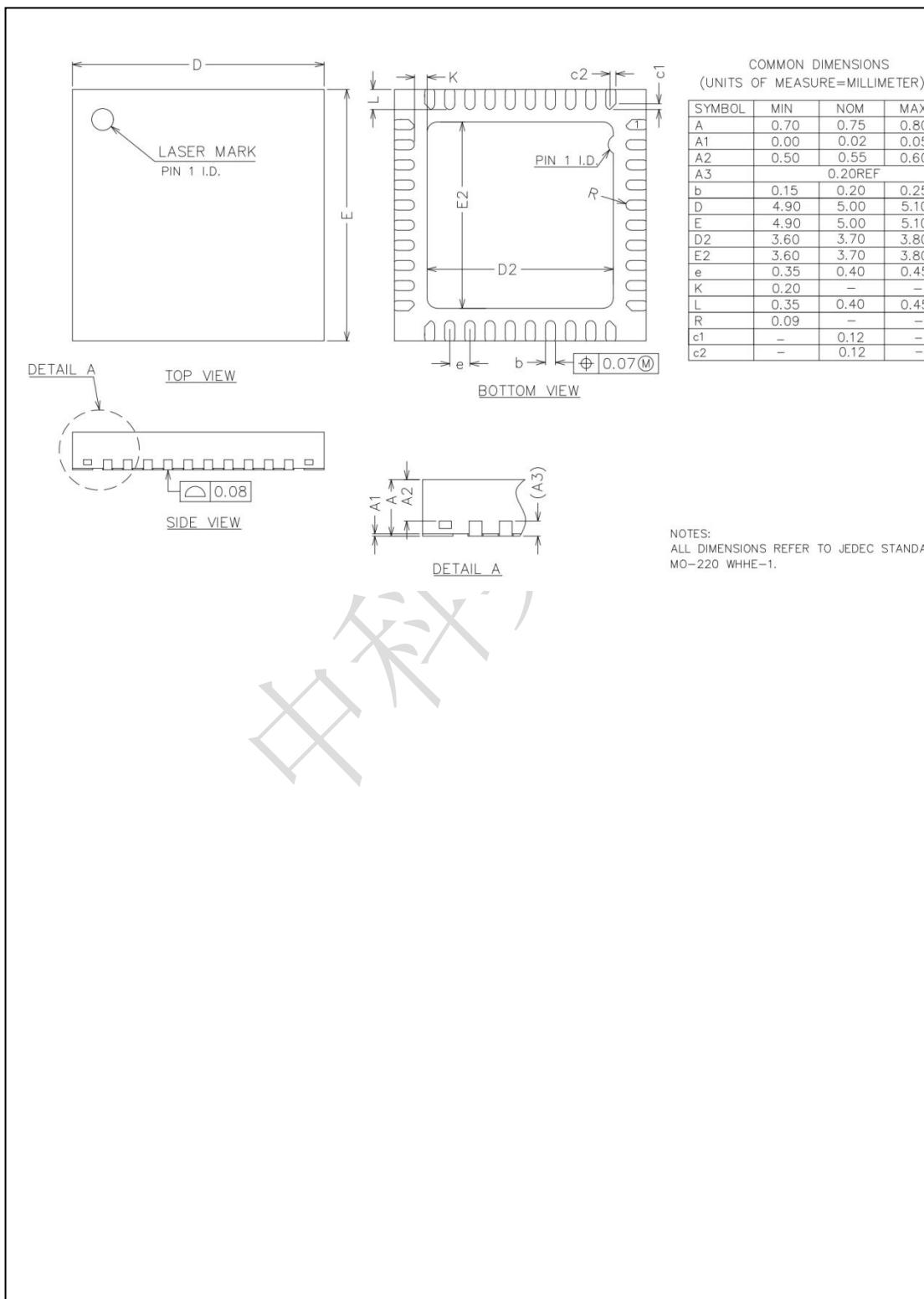

| 7. 热特性/机械数据 ..... | 76 |

| 7. 1 QFN40 .....  | 76 |

| 8. 订货信息 .....     | 77 |

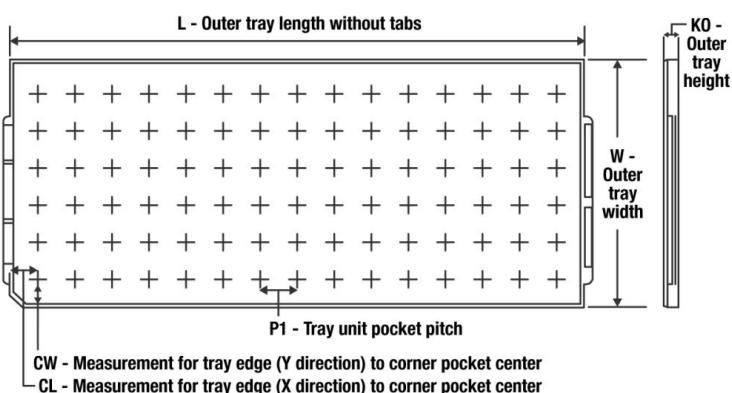

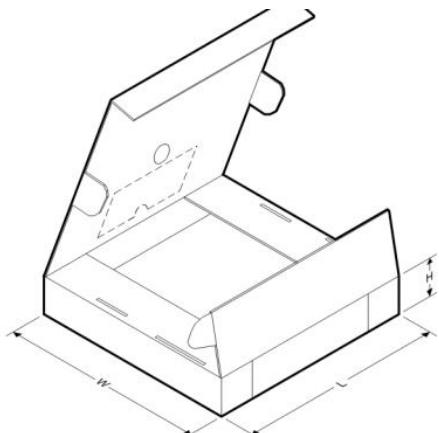

| 8. 1 封装信息 .....   | 77 |

| 8. 2 托盘信息 .....   | 77 |

| 8. 3 包装盒尺寸 .....  | 78 |

中科昊芯

# 1. 器件概述

## 1.1 产品特性

### 高能效 32 位处理器 (H28x 内核)

- ✓ 主频 120MHz (周期 8.33ns)

- ✓ 哈佛 (Harvard) 总线架构

- ✓ 硬件乘法/除法单元

- ✓ 6 通道高速 DMA

- ✓ 快速中断响应和处理

- ✓ 统一存储器编程模型

- ✓ 高效代码 (使用 C/C++ 和汇编语言)

### 增强型控制外设

- ✓ 增强型脉宽调制器 (ePWM)

- ✓ 高分辨率 PWM (HRPWM)

- ✓ 增强型捕获 (eCAP)

- ✓ 增强型正交编码器脉冲 (eQEP)

- ✓ 模数转换器 (ADC)

- ✓ 片载温度传感器

- ✓ 比较器

### 芯片及系统开销

- ✓ 3.3V 单电源供电

- ✓ 无上电顺序要求

- ✓ 集成上电和掉电复位

- ✓ 代码安全模块

- ✓ ADC 外部参考源

### 时钟和系统控制

- ✓ 两个内部 12MHz 零引脚振荡器

- ✓ 片载振荡器/外部时钟输入

- ✓ 看门狗定时器模组功能

- ✓ 支持锁相环路 (PLL) 倍频系数动态调整

- 多达 21 个具有输入滤波功能、可单独编程的多路复用 GPIO

- ✓ 可支持所有外设中断的外设中断扩展 (PIE) 模块

- ✓ 三个 32 位 CPU 定时器

- ✓ 每个 ePWM 模块中包含独立的 32 位定时器

- ✓ 片载存储器

- ✓ 闪存, SRAM, OTP, 引导 ROM 可用

- 128 位安全密钥/锁

- ✓ 保护安全内存块

- ✓ 防止固件逆向工程

- 串行端口外设

- ✓ 一个 SCI (UART) 模块

- ✓ 一个 SPI 模块

- ✓ 一个内部集成电路 (I2C) 总线

- 高级仿真特性

- ✓ 分析和断点功能

### 封装选项

- ✓ 40-PIN 方形扁平无引脚 (QFN) 封装

### 温度选项

- ✓ 工作温度 S: -40° C 至 125° C

## 1.2 应用

- 电器

- 楼宇自动化

- 电动汽车、混合动力电动汽车（EV/HEV）动力传动

- 工厂自动化

- 电网基础设施

- 医疗、保健与健身

- 电机驱动器

- 电力传送

- 电信基础设施

- 光伏逆变器

中科昊芯

## 2. DSC280103Px 简介

### 2.1 器件特性

表 2-1 DSC280103Px 器件的特性

| 功能             |                 | HXS320F280103PM5S (H) |

|----------------|-----------------|-----------------------|

| 封装类型           |                 | 40 引脚<br>M5<br>QFN    |

| 时钟主频 (MHz)     |                 | 120                   |

| 指令周期 (ns)      |                 | 8.33ns                |

| 硬件乘法/除法单元      |                 | 32-bit                |

| 片内闪存 (Byte)    |                 | 128K                  |

| 片载 SRAM (Byte) |                 | 20K                   |

| 代码安全 CSM 模块    |                 | 支持                    |

| 引导 ROM         |                 | 支持                    |

| 一次可编程 OTP      |                 | 8K                    |

| 高速 DMA 模块通道    |                 | 6                     |

| ePWM 模块        |                 | 4                     |

| ePWM 通道        |                 | 4×2                   |

| 看门狗定时器         |                 | 支持                    |

| 12 位 ADC       | 转换速率 Msps       | 1Msps                 |

|                | 转换时间            | 1us <sup>(1)</sup>    |

|                | 通道              | 10                    |

|                | 温度传感器           | 支持                    |

| 32 位 CPU 定时器   |                 | 3                     |

| 高分辨率 HRPWM 模块  |                 | 4                     |

| 集成 DAC 的比较器    |                 | 2                     |

| 内部集成电路 I2C     |                 | 1                     |

| 串行外设接口 SPI     |                 | 1                     |

| 串行通信接口 SCI     |                 | 1                     |

| IO 引脚          | GPIO            | 21                    |

|                | AI0             | 4                     |

| 外部中断           |                 | 3                     |

| 电源电压 (标称值)     |                 | 3.3v                  |

| 工作温度           | -40° C 至 125° C | 支持                    |

(1) : HXS320F280103Px 内部有两个 ADC 转换器, 可以同时采样转换两个通道, 可达到两倍的等效最高采样率, 但同一个 ADC 转换器的转换时间不会缩减。ADC 的采样率和有效位数 (ENOB) 的参数如下:

| ADC 模块时钟    | 采样速率     | ENOB    |

|-------------|----------|---------|

| 15MHz (推荐值) | 1MSPS    | 11bit   |

| 20MHz       | 1.33MSPS | 10.3bit |

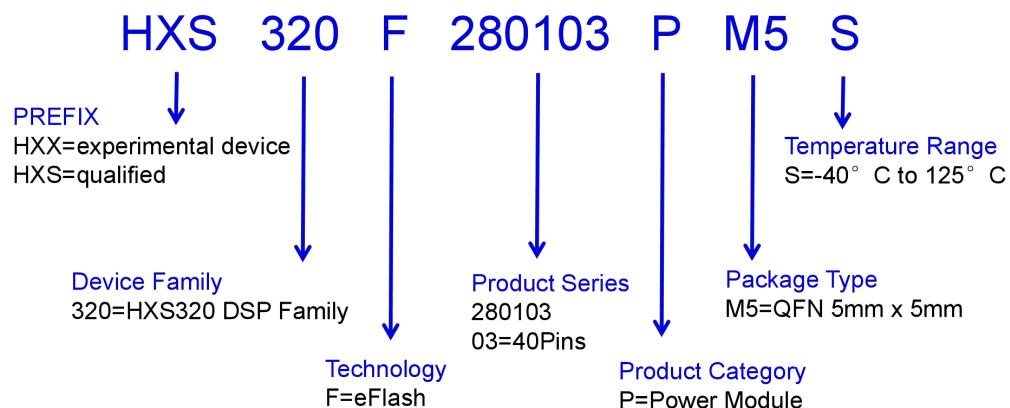

## 2. 2 产品编码

丝印 Marking 说明

ABCD-YYMMSF : ABCD 表示硅片的版本

YY 表示生产年份编号

MM 表示生产月份编号

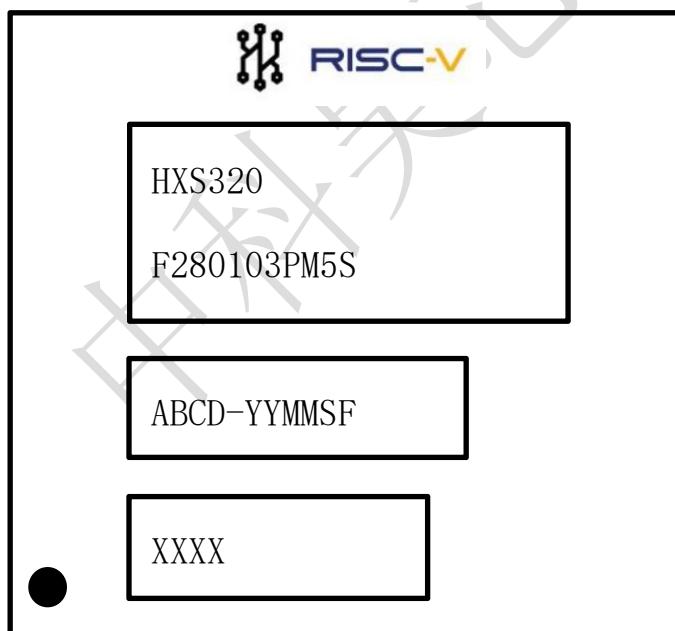

## 2.3 引脚分配

下图所示为 DSC280103Px 40-PIN QFN 封装，引脚分配示意图。

图 2-1 DSC280103Px 40-PIN QFN (顶视图)

## 2.4 信号说明

表 2-2 对这些信号进行了说明。除 JTAG 引脚以外，引脚的 GPIO 功能是复位时的默认功能，除非另外注明。下面列出的外设信号是供替换的功能。有些外设功能并不在所有器件上提供。详细信息请见表 2-1。输入是 3.63V 耐压。所有 GPIO 引脚为 I/O/Z 且有一个内部上拉电阻器，此内部上拉电阻器可每个引脚上有选择性的启用/禁用。这一特性只适用于 GPIO 引脚。PWM 引脚上的上拉电阻在复位时并不启用。其它 GPIO 引脚上的上拉电阻复位时被启用。AIO 引脚没有内部上拉电阻。

表 2-2 信号说明

| 名称                          | 引脚编号  | 说明                                                                                                                                                                                                                                                                                  |

|-----------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | QFN40 |                                                                                                                                                                                                                                                                                     |

| TRSTn                       | 1     | <p>使用内部下拉电阻进行 JTAG 测试复位，当被驱动为高电平时，使扫描系统获得器件运行的控制权。如果这个信号未连接或者被驱动至低电平，此器件在功能模式下运转，并且测试复位信号被忽略。</p> <p>注释：是一个高电平有效测试引脚并且必须在正常器件运行期间一直保持低电平。在这个引脚上需要一个外部下拉电阻器。这个电阻器的值应该基于适用于这个设计的调试器推进源代码的驱动强度。通常一个 <math>2.2\text{k}\Omega</math> 电阻器可提供足够的保护。由于这是应用专用的，建议针对调试器和应用正确运行对每个目标板进行验证。</p> |

| XRSn                        | 2     | <p>器件复位。导致器件终止执行。PC 将指向包含在位置 0x7fb600 中的地址。当被置为高电平时，在 PC 指向的位置开始执行。当一个安全装置复位发生时，这个引脚被 DSP 驱动至低电平。安全装置复位期间，在 512 个 OSCCLK 周期的安全装置复位持续时间内，引脚被驱动为低电平。这个引脚的输出缓冲器是一个有内部上拉电阻的开漏器件。建议由一个开漏器件驱动这个引脚。</p>                                                                                    |

| ADCINA4/<br>COMP2A/<br>AI04 | 3     | <p>ADC 组 A，通道 4 输入引脚<br/>比较器输入 2A<br/>模拟输入/输出 4 引脚</p>                                                                                                                                                                                                                              |

| ADCINA7                     | 4     | ADC 组 A，通道 7 输入引脚                                                                                                                                                                                                                                                                   |

| ADCINA3                     | 5     | ADC 组 A，通道 3 输入引脚                                                                                                                                                                                                                                                                   |

| ADCINA1                     | 6     | ADC 组 A，通道 1 输入引脚                                                                                                                                                                                                                                                                   |

| ADCINA2                     | 7     | ADC 组 A，通道 2 输入引脚                                                                                                                                                                                                                                                                   |

| 名称                                        | 引脚编号 | 说明                                                                                                                                                             |

|-------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADCINA0/<br>$V_{REFHI}$                   | 8    | ADC 组 A, 通道 0 输入引脚<br>外部参考电压正极(只有 ADC 模块支持外部参考电压模式时时有效)                                                                                                        |

| $V_{DDA}$                                 | 9    | 模拟电源引脚                                                                                                                                                         |

| $V_{SSA}$                                 | 10   | 模拟地引脚                                                                                                                                                          |

| ADCINB2/<br>COMP1B/<br>AI010              | 11   | ADC 组 B, 通道 2 输入引脚<br>比较器 1 输入 B<br>模拟输入/输出 10 引脚                                                                                                              |

| ADCINB3                                   | 12   | ADC 组 B, 通道 3 输入引脚                                                                                                                                             |

| ADCINB4/<br>COMP2B/<br>AI012              | 13   | ADC 组 B, 通道 4 输入引脚<br>比较器 2 输入 B<br>模拟输入/输出 12 引脚                                                                                                              |

| ADCINB7                                   | 14   | ADC 组 B, 通道 7 输入引脚                                                                                                                                             |

| GPIO34/<br>COMP2OUT                       | 15   | 通用输入/输出引脚 34<br>比较器 2 输出引脚(0)                                                                                                                                  |

| GPIO35/<br>TDI                            | 16   | 通用输入/输出引脚 35<br>带有内部上拉电阻的 JTAG 测试数据输入 (TDI)。 TDI 在 TCK 的上升沿上所选择的寄存器 (指令或者数据) 内计时。                                                                              |

| GPIO36/<br>TMS                            | 17   | 通用输入/输出引脚 36<br>带有内部上拉电阻器的 JTAG 测试模式选择 (TMS)。 这个串行控制输入在 TCK 上升沿上的 TAP 控制器中计时。                                                                                  |

| GPIO37/<br>TDO                            | 18   | 通用输入/输出引脚 37<br>JTAG 扫描输出, 测试数据输出 (TDO)。 所选寄存器 (指令或者数据) 的内容被从 TCK 下降沿上的 TDO 移出。 (0/Z 8mA 驱动)                                                                   |

| GPIO38/<br>XCLKIN(TCK)                    | 19   | 通用输入/输出引脚 38<br>JTAG 测试时钟引脚, 带有内部上接电阻器<br>这个引脚被用于从一个外部 3.3V 振荡器反馈入一个时钟。                                                                                        |

| GPIO18/<br>SPICLK/<br>SCITXDA/<br>XCLKOUT | 20   | 通用输入/输出引脚 18<br>SPI-A 时钟输入/输出引脚<br>SCI-A 输出引脚<br>取自 SYSCLKOUT 的输出时钟。 XCLKOUT 或者 SYSCLKOUT 的频率一样、或者为其一半, 或<br>为其四分之一。这是由位 18: 16 (XTIMCLK) 和在 XINTCNF2 寄存器中的位 2 |

| 名称                                                       | 引脚编号 | 说明                                                                                                                                                                                   |

|----------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                          |      | (CLKMODE) 控制的。 复位时, XCLKOUT=SYSCLKOUT/4。通过将 XINTCNF2 [CLKOFF] 设定为 1, XCLKOUT 信号可被关闭。与其它 GPIO 引脚不同, 复位时, 不将 XCLKOUT 引脚置于一个高阻抗状态。 (0/Z, 8mA 驱动)                                        |

| GPIO19/<br>XCLKIN/<br><br>SPISTEAn/<br>SCIRXDA/<br>ECAP1 | 21   | 通用输入/输出引脚 19<br>这个引脚被用于从一个外部 3.3V 振荡器反馈入一个时钟。在这种情况下, X1 引脚必须连接到 GND。如果使用到了晶振/谐振器 (或 1.9V 外部振荡器被用来把时钟馈入 X1 引脚), 此引脚必须连接到 GND。<br>SPI-A 从器件发送使能 (I/O)<br>SCI-A 接收 (I)<br>增强型捕获 1 输入/输出 |

| GPIO17/<br>SPISOMIA<br>EQEP1S<br>TZ3n                    | 22   | 通用输入/输出引脚 17<br>SPI-A 从器件输出 (O), 主器件输入 (I)<br>增强型正交编码脉冲器 S<br>错误联防输入 3 引脚 (I)                                                                                                        |

| GPIO16/<br>SPISIMOA/<br>EQEPI/<br>TZ2n                   | 23   | 通用输入/输出引脚 16<br>SPI-A 主器件输出 (O), 从器件输入 (I)<br>增强型正交编码脉冲器 I<br>错误联防输入 2 引脚 (I)                                                                                                        |

| GPIO1/<br>EPWM1B/<br>COMP1OUT                            | 24   | 通用输入/输出引脚 1<br>增强型 PWM1 输出 B (O) 引脚<br>比较器 1 输出引脚                                                                                                                                    |

| GPIO0/<br>EPWM1A                                         | 25   | 通用输入/输出引脚 0<br>增强型 PWM1 输出 A (O) 引脚                                                                                                                                                  |

| TEST                                                     | 26   | 未使用, 悬空                                                                                                                                                                              |

| GPIO32/<br>SDAA/<br>EPWMSYNCI/<br>ADCSOCDAO              | 27   | 通用输入/输出引脚 32<br>I2CA 数据开漏双向端口 (I/OC)<br>增强型 PWM 外部同步脉冲输入 (I)<br>ADC 转换启动 A (O)                                                                                                       |

| V <sub>DD</sub>                                          | 28   | CPU 和逻辑数字电源引脚                                                                                                                                                                        |

| VREGENZn                                                 | 29   | 内部 VREG 启用/禁用。拉低启用内部电压调节器 (VREG), 拉高禁用 VREG。                                                                                                                                         |

| V <sub>DDIO</sub>                                        | 30   | 数字 I/O 电源引脚                                                                                                                                                                          |

| GPIO2/                                                   | 31   | 通用输入/输出引脚 2                                                                                                                                                                          |

| 名称                                           | 引脚编号 | 说明                                                                                  |

|----------------------------------------------|------|-------------------------------------------------------------------------------------|

| EPWM2A/                                      |      | 增强型 PWM2 输出 A (O) 引脚                                                                |

| GPIO3/<br>EPWM2B/<br>COMP2OUT/               | 32   | 通用输入/输出引脚 3<br>增强型 PWM2 输出 B (O) 引脚<br>比较器 2 输出引脚                                   |

| GPIO4/<br>EPWM3A/                            | 33   | 通用输入/输出引脚 4<br>增强型 PWM3 输出 A 引脚 (O)                                                 |

| GPIO5/<br>EPWM3B/<br>ECAP1/                  | 34   | 通用输入/输出引脚 5<br>增强型 PWM3 输出 B (O) 引脚<br>增强型捕获 1 输入/输出                                |

| GPIO6/<br>EPWM4A/<br>EPWMSYNCI/<br>EPWMSYNCO | 35   | 通用输入/输出引脚 6<br>增强型 PWM4 输出 A 引脚 (O)<br>增强型 PWM 外部同步脉冲输入 (I)<br>增强型 PWM 外部同步脉冲输出 (O) |

| GPIO7/<br>EPWM4B/<br>SCIRXDA                 | 36   | 通用输入/输出引脚 7<br>增强型 PWM4 输出 B (O) 引脚<br>SCI 接收数据 (I)                                 |

| V <sub>DD</sub>                              | 37   | CPU 和逻辑数字电源引脚                                                                       |

| GPIO12/<br>TZ1/<br>SCITXDA/<br>EQEP1A        | 38   | 通用输入/输出引脚 12<br>错误联防输入 1 引脚 (I)<br>SCI 传输数据 (O)<br>增强型正交编码脉冲器 1A                    |

| GPIO28/<br>SCIRXDA/<br>SDAA/<br>TZ2          | 39   | 通用输入/输出引脚 28<br>SCI 接收数据 (I)<br>I2C 数据开漏双向端口 (I/OC)<br>错误联防输入 2 引脚 (O)              |

| GPIO29<br>SCITXDA<br>SCLA<br>TZ3n            | 40   | 通用输入/输出 29 引脚<br>SCI-A 传输引脚<br>I2C 时钟开漏双向端口 (I/OC)<br>错误联防输入 3 引脚                   |

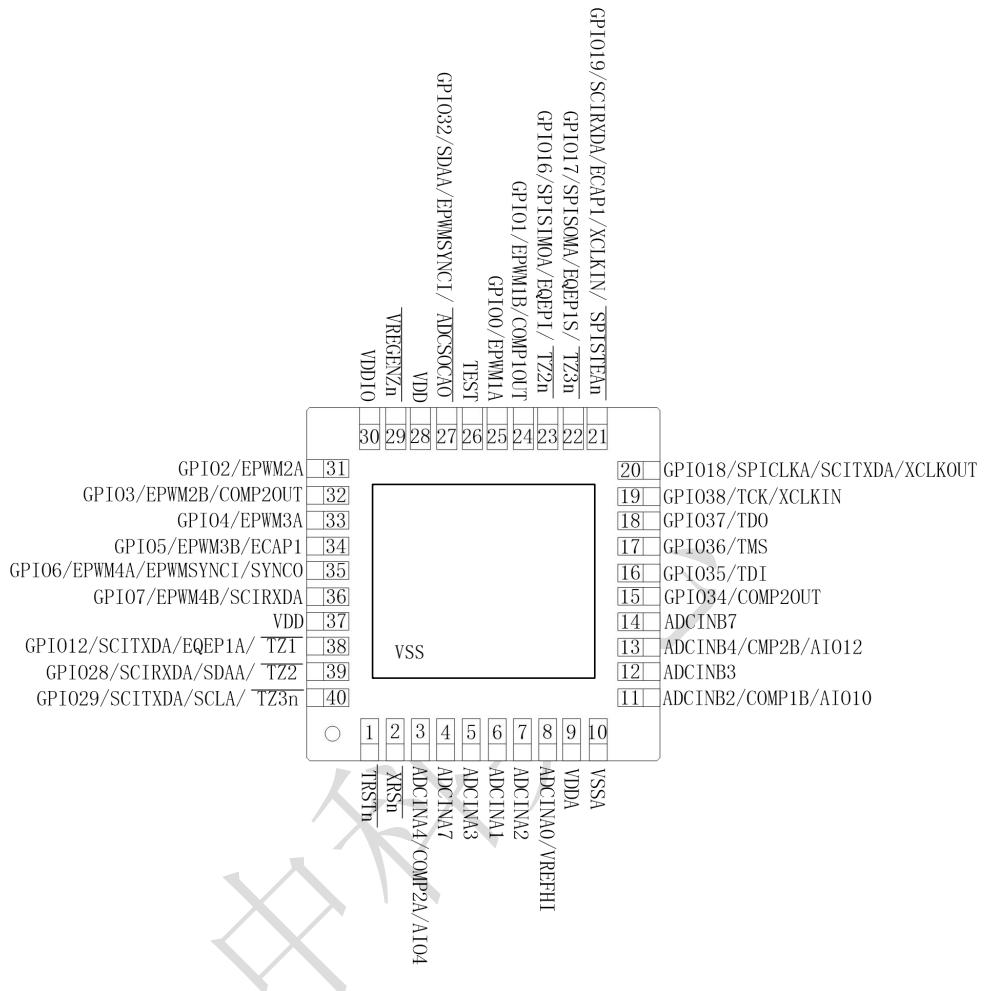

### 3. 功能概述

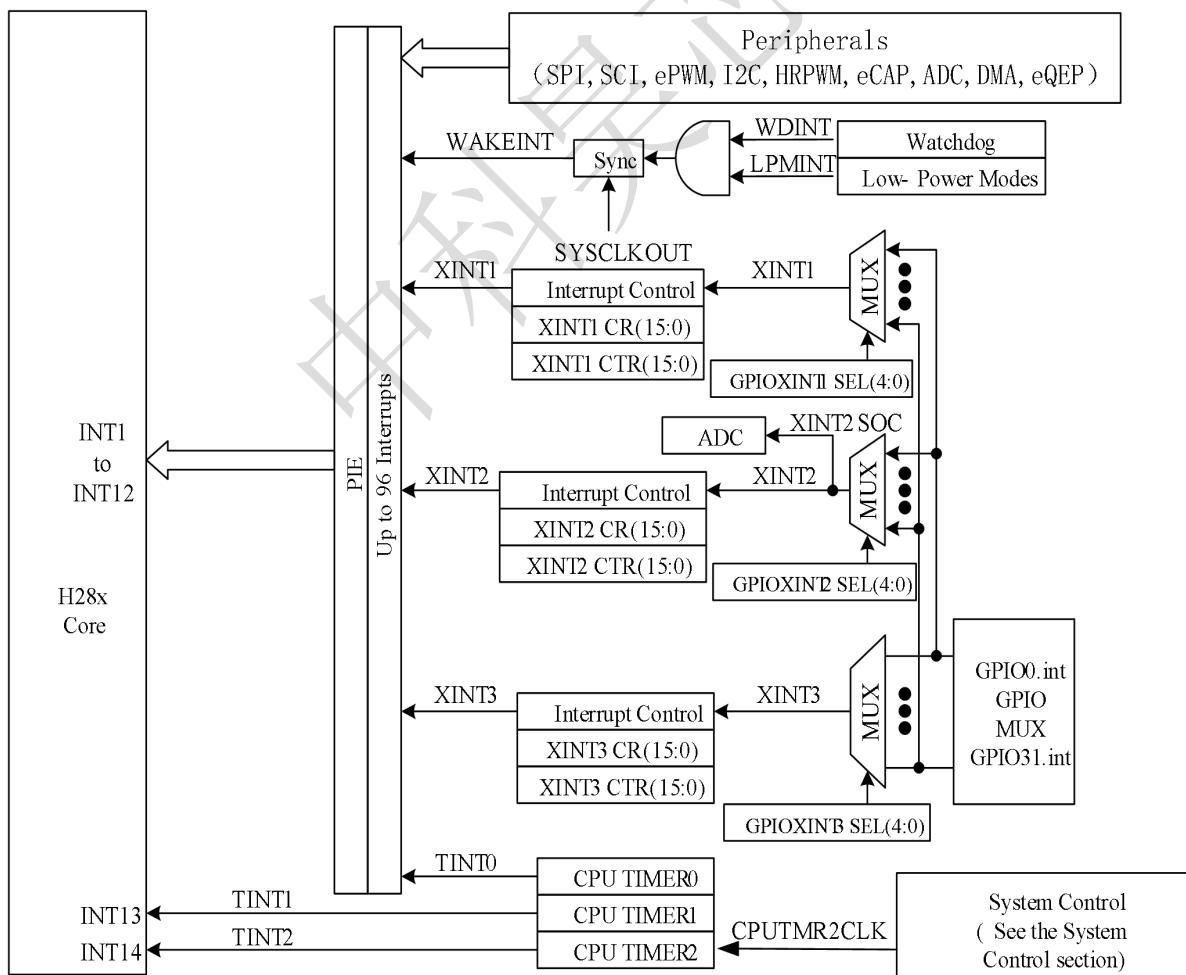

#### 3.1 系统架构

图 3-1 HXS320F280103PX 芯片架构图

### 3.2 内存映射

表 3-1 Peripheral frame 0 模块内存映射

| 序号  | 设备                             | 地址范围 (不含最高地址)                                                     | 大小 (Bytes)        |

|-----|--------------------------------|-------------------------------------------------------------------|-------------------|

| 1.  | M0                             | 0x00 0000~0x00 0800                                               | 2K                |

| 2.  | M1                             | 0x00 0800~0x00 1000                                               | 2K                |

|     | Res.                           | 0x00 1000~0x00 1400                                               |                   |

| 3.  | ADC                            | 0x00 1400~0x00 1800                                               | 1K                |

| 4.  | Timer/PIE                      | 0x00 1800~0x00 1C00                                               | 1K                |

| 5.  | DMA                            | 0x00 1C00~0x00 2000                                               | 1K                |

|     | Res.                           | 0x00 2000~0x00 A000                                               |                   |

| 8.  | L0(0)                          | 0x01 0000~0x01 2000<br>(Dual Mapped)                              | 8K                |

| 9.  | L1                             | 0x01 2000~0x01 4000                                               | 8K                |

|     | Res.                           | 0x01 8000~0x70 0000                                               |                   |

| 10. | Flash<br>OTP<br>Flash Register | 0x7C 0000~0x7E 0000<br>0x7A 0000~0x7A 2000<br>0x7A F800~0x7A F900 | 128K<br>8K<br>256 |

| 11. | L0(1)                          | 0x7F 0000~0x7F 2000<br>(Dual Mapped)                              | 8K                |

|     | Res.                           | 0x7F 4000~0x7F C000                                               |                   |

| 12. | Bootrom                        | 0x7F 8000~0x80 0000                                               | 32K               |

表 3-2 peripheral frame 1 模块内存映射

| 序号 | 设备         | 地址范围 (不含最高地址)       | 大小 (Bytes) |

|----|------------|---------------------|------------|

| 1. | Debug      | 0x00 A000~0x00 B000 | 4K         |

| 2. | PWMx4      | 0x00 B000~0x00 C000 | 4K         |

| 3. | Comparator | 0x00 C000~0x00 C400 | 1K         |

|    | Res.       | 0x00 C400~0x00 D000 |            |

| 4. | CAP        | 0x00 D000~0x00 D400 | 1K         |

| 5. | QEP        | 0x00 D400~0x00 D800 | 1K         |

| 6. | GPIO       | 0x00 D800~0x00 DC00 | 1K         |

| 7. | SYSCTRL    | 0x00 DC00~0x00 E000 | 1K         |

表 3-3 peripheral frame 2 模块内存映射

| 序号 | 设备  | 地址范围 (不含最高地址)       | 大小 (Bytes) |

|----|-----|---------------------|------------|

| 1. | SCI | 0x00 E000~0x00 E400 | 1K         |

| 2. | I2C | 0x00 E400~0x00 E800 | 1K         |

| 3. | SPI | 0x00 E800~0x00 EC00 | 1K         |

### 3. 3 简要说明

#### 3. 3. 1 HXS320F280103Px DSC

HXS320F280103PX DSC 系列是中科昊芯定点 DSC 平台上的产品，基于 RISC-V 开放指令集架构 H28x。它支持高效的 C/C++ 引擎，此引擎不但能够让用户能够用高级语言开发他们的控制系统软件，还能够使用 C/C++ 开发数学算法。此器件在处理 DSP 算术任务时与处理系统控制任务时同样有效，而系统控制任务通常由微控制器器件处理。这样的效率在很多系统中省却了对第二个处理器的需要。

#### 3. 3. 2 内存总线

与很多 DSP 类型器件一样，多总线被用于在内存和外设以及 CPU 之间移动数据。HXS320F280103Px 内存总线架构包含一个程序总线、数据总线和 DMA 总线。程序总线由 32 条地址线路和 32 条数据线路组成。数据总线由 23 条地址线和 64 条数据线组成。多总线结构，通常称为哈佛总线，使得 HXS320F280103Px 能够在一个单周期内取一个指令、读写一个数据值。对所有连接在内存总线上的外设和内存访问时具有一定的优先级。总的来说，内存总线访问的优先级可概括如下：

- 1、数据总线具有最高优先级；

- 2、程序总线和 DMA 总线具有较低的平等优先级。

#### 3. 3. 3 外设总线

为了实现不同中科昊芯 DSP 系列器件间的外设迁移，HXS320F280103Px 器件采用一个针对外设互连的外设总线标准。外设总线桥复用了多种总线。

#### 3. 3. 4 实时 JTAG 和分析

HXS320F280103Px 器件使用标准的 IEEE1149.1 JTAG 接口。此外，器件支持实时运行模

式，在处理器正在运行、执行代码并且处理中断时，可修改存储器内容、外设寄存器内容。用户也可以通过非时间关键代码进行单步操作，同时可在没有干扰的情况下启用即将被处理的时间关键中断。此器件在 CPU 内硬件实现实时模式。这是 HXS320F280103Px 器件的独特功能，无需软件监控。此外，还提供了特别分析硬件以实现硬件断点或者数据/地址观察点的设置并当一个匹配发生时生成不同的用户可选断点事件。

这些设备不支持边界扫描；但是，如果有 IDCODE 和旁路功能，则可用考虑到以下因素。默认情况下 IDCODE 不提供。用户必须经过一系列的移位 IR 和移位 JTAG 的 DR 状态以获得 IDCODE。用于旁路指令，第一个移位的 DR 值将为 1。

### 3.3.5 闪存

HXS320F280103PX 器件包含 128KB 的嵌入式闪存存储器，其地址范围为 0x7C0000–0x7E0000，被分别放置在 64 个 2KB 扇区内。该器件还包含一个 8KB 的 OTP 内存，其地址范围为 0x7A0000–0x7A2000。用户能够在不改变其它扇区的同时单独擦除、编辑和验证一个闪存扇区。然而，不能使用闪存的一个扇区或者这个 OTP 来执行擦除/编辑其它扇区的闪存算法。

HXS320F280103PX 器件提供了特殊内存流水线操作以使闪存模块实现更高的性能。闪存 /OTP 被映射到程序和数据空间；因此它可被用于执行代码或者存储数据信息。

地址 0x7DFFE8–0x7FFFF 为数据变量保留且不能包含程序代码，此处为密码区和复位向量区。

### 3.3.6 M0、M1、L0、L1 SARAM

所有器件包含这四块单周期访问内存 M0、M1、L0、L1。复位时堆栈指针指向块 M1 的开始位置。M0 和 M1 块与所有其它 HXS320F280103PX 器件上的内存块一样被映射到程序和数据空间。因此，用户能够使用 M0 和 M1 来执行代码或者存储数据变量。分区在连接器内执行。HXS320F280103PX 器件提供了一个到编程器的统一内存映射。这使得用高级语言编程变得更加容易。

HXS320F280103PX 内置四个 SARAM 存储器：

- M0: SRAM 2K x 8 (0-wait), 映射到程序和数据地址空间, 既可用于执行程序又可用于存储器数据。

- M1: SRAM 2K x 8 (0-wait), 映射到程序和数据地址空间, 既可用于执行程序又可用于存储器数据。

- L0: SRAM 8K x 8 (0-wait), 代码安全区域, 同样映射到程序和数据存储器。

- L1: SRAM 8K x 8 (0-wait), 同样映射到程序和数据存储器。

以上存储器均连接 peripheral frame 0

### 3.3.7 引导 ROM

引导 ROM 由厂家使用引导载入软件进行设定。引导 ROM 程序在器件复位并检查了几个 GPIO 引脚后执行以确定应该进入哪一个引导模式。例如, 用户可以选择执行已经出现在内部闪存中的代码或者通过几个串行端口中的一个将全新的软件下载至内部 RAM。还有其它的引导模式。引导 ROM 还包含用于数学相关算法中的标准表, 例如 SIN/COS 波形。

表格 3-4 引导模式选择

| 模式   | GPIO37/TDO | GPIO34/COMP2OUT | TRSTn | 模式                |

|------|------------|-----------------|-------|-------------------|

| 3    | 1          | 1               | 0     | 获取模式<br>(GetMode) |

| 2    | 1          | 0               | 0     | 等待模式              |

| 1    | 0          | 1               | 0     | SCI 模式            |

| 0    | 0          | 0               | 0     | FLASH 启动          |

| JTAG | x          | x               | 1     | JTAG 模式           |

#### 3.3.7.1 JTAG 引导模式

当仿真器被连接时, GPIO37/TDO 引脚不能被用于引导模式选择。在这种情况下, 引导 ROM 检测一个被连接的仿真器并使用 PIE 矢量表中两个被保留的 SARAM 位置内的内容来确定引导模式。如果两个位置内的内容均无效, 那么使用等待引导选项。可在仿真引导中访问所有引导模式选项。

### 3.3.7.2 GetMode 获取模式

GetMode 的默认运行状态选项为引导至闪存。通过在 OTP 中设定两个位置，这个运行状态能够被改变为其它的引导选项。如果两个 OTP 位置的内容均为无效，那么引导至闪存。可指定下列加载器中的一个：SCI、SPI、I2C 或者 OTP。

### 3.3.7.3 引导加载器使用的外设引脚

表格 3-5 显示了每一个外设引导加载器所使用的 GPIO 引脚。

表格 3-5 外设引导加载引脚使用情况

| 引导加载器 | 外设加载器引脚                                                                        |

|-------|--------------------------------------------------------------------------------|

| SCI   | SCIRXDA (GPIO28)<br>SCITXDA (GPIO29)                                           |

| 并行引导  | 数据(GPIO[7:0])<br>HXS320F280103PX 控制(GPIO16)<br>主机控制(GPIO12)                    |

| SPI   | SPISIMOA (GPIO16)<br>SPISOMIA (GPIO17)<br>SPICLKA (GPIO18)<br>SPISTEA (GPIO19) |

| IIC   | SDAA (GPIO32)<br>SCLA (GPIO29)                                                 |

### 3.3.8 安全性

此器件支持高级安全性以保护用户固件不受反向工程的损坏。这个安全性特有一个 128 位密码（针对 16 个等待状态的硬编码），此密码由用户编辑入闪存。一个代码安全模块(CSM)用于保护闪存/OTP 和 LOSARAM 块。这个安全特性防止未经授权的用户通过 JTAG 端口检查内存内容，从外部内存执行代码或者试图引导加载一些将会输出安全内存内容的恶意软件。为了启用到安全块的访问，用户必须写入与存储在闪存密码位置内的值相匹配的正确的 128 位 KEY (密钥) 值。除了 CSM，仿真代码安全逻辑电路 (ECSL) 也已经被实现来防止未经授权的用户安全代码。在仿真器连接时，任何对于闪存、用户 OTP，或者 L0 内存的

代码或者数据访问将触发 ECSL 错误并返回 0 值。为了实现安全代码仿真，同时保持 CSM 安全内存读取，用户必须向 KEY 寄存器的低 64 位写入正确的值，这个值与存储在闪存密码位置的低 64 位的值相符合。请注意仍须执行闪存内所有 128 位密码的读取。如果密码位置的低 64 位为全 1（未被编辑），那么无须符合 KEY 值。当使用闪存内设定的密码位置开始调试一个器件时（也就是说，调试是安全的），仿真器需一些时间来控制 CPU。在此期间，CPU 将开始运行，并可能执行一个访问 受保护 ECSL 区的指令。如果这一情况发生，ECSL 将发生错误并使仿真器读取返回 0。这个问题有两个解决方案：

1. 首先是使用在等待中复位的仿真模式，该模式将保持器件在复位状态直到仿真器获得控制权。仿真器必须支持此选项的这种模式。

2. 第二种选择是使用“分支至检查引导模式”引导选项。这将进入一个路，并不断轮询引导模式选择引脚。通过重新映射 PC 到另一个地址，或通过把引导模式选择引脚更改为所需的引导模式，用户可以选择此引导模式，然后在仿真器被连接时退出这种模式。

**注：**

- 此处有关于 CSM 当代码安全密码被编辑时，0x7DFFF0 到 0x7DFFFC 间的所有地址不能被用作程序代码或者数据。这些位置必须被设定为 0xFFFFFFFF。

- 地址 0x7DFFF0–0x7DFFFC 为数据保留且不能包含程序代码。128 位密码（位于 0x7DFFF0–0x7DFFFF）不能被设定为全 0，否则将永久锁住此器件。

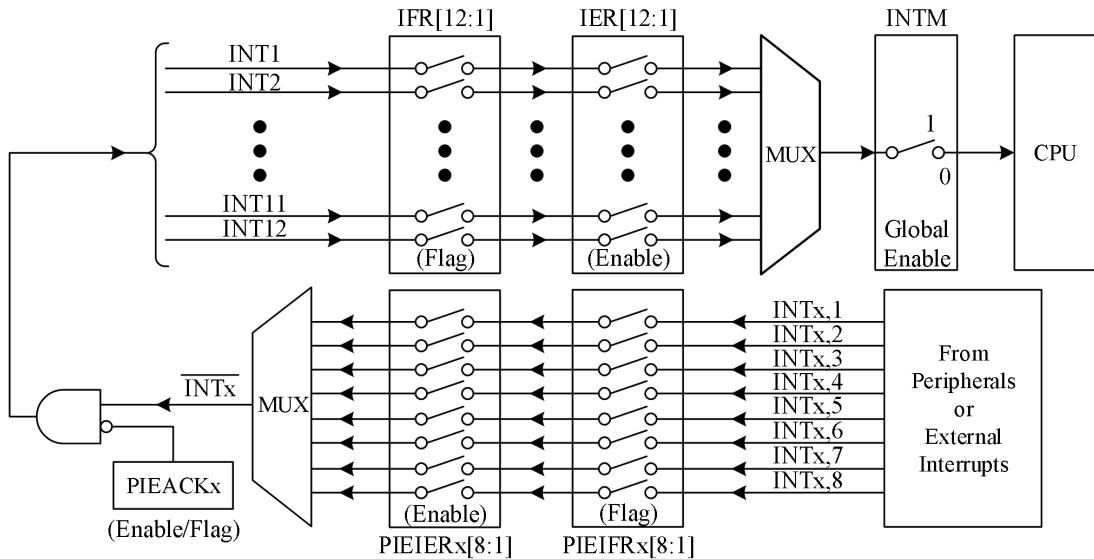

### 3.3.9 外设中断扩展（PIE）模块

PIE 块将许多中断源复用至中断输入的较小的集合中。PIE 块能够支持多达 96 个外设中断。

在 HXS320F280103PX 中，96 个中断中的 36 个被外设使用。96 个中断被分成 8 组，每组被提供 12 个 CPU 中断线（INT1 或者 INT12）中的 1 个。96 个中断中的每一个中断由其存储在一个可被用户写覆盖的专用 RAM 块中的矢量支持。在处理这个中断时，这个矢量由 CPU 自动抽取。抽取这个矢量以及保存关键 CPU 寄存器将花费 8 个 CPU 时钟周期。因此 CPU 能够对中断事件作出快速响应。可以通过硬件和软件控制中断的优先级。每个中断都可以在 PIE 块内启用或禁用。

### 3.3.10 外部中断 (XINT1-XINT3)

器件 HXS320F280103PX 支持三个屏蔽的外部中断 (XINT1 – XINT3)。选择用于负，正或负和正边沿触发，也可以选择启用/禁用这些中断，它还包含一个 16 位自由运行计数器，该计数器重置为零，可用于为中断准确地打上时间戳。没有用于外部中断的专用引脚，XINT1，XINT2 和 XINT3 中断可以配置为 GPIO0 – GPIO31 引脚的输入。

### 3.3.11 内部振荡器、外部振荡器和 PLL

该器件可以由两个内部零引脚振荡器，一个外部振荡器或一个晶体连接到片上振荡器电路（仅限 48 引脚器件），并提供了一个 PLL，最多可支持 12 个输入时钟缩放比例，PLL 比例可以在软件中即时更改，从而使用户能够如果需要低功率运行，则按比例缩小工作频率，可以在旁路模式下设置 PLL 模块。

### 3.3.12 看门狗

每个 HXS320F280103PX 器件包含一个看门狗电路——内部监控 CPU 看门狗。用户软件必须在特定的周期内定期复位 CPU 看门狗计数器；否则 CPU 看门狗将产生一个复位信号复位处理器。如果需要可将 CPU 看门狗禁用。

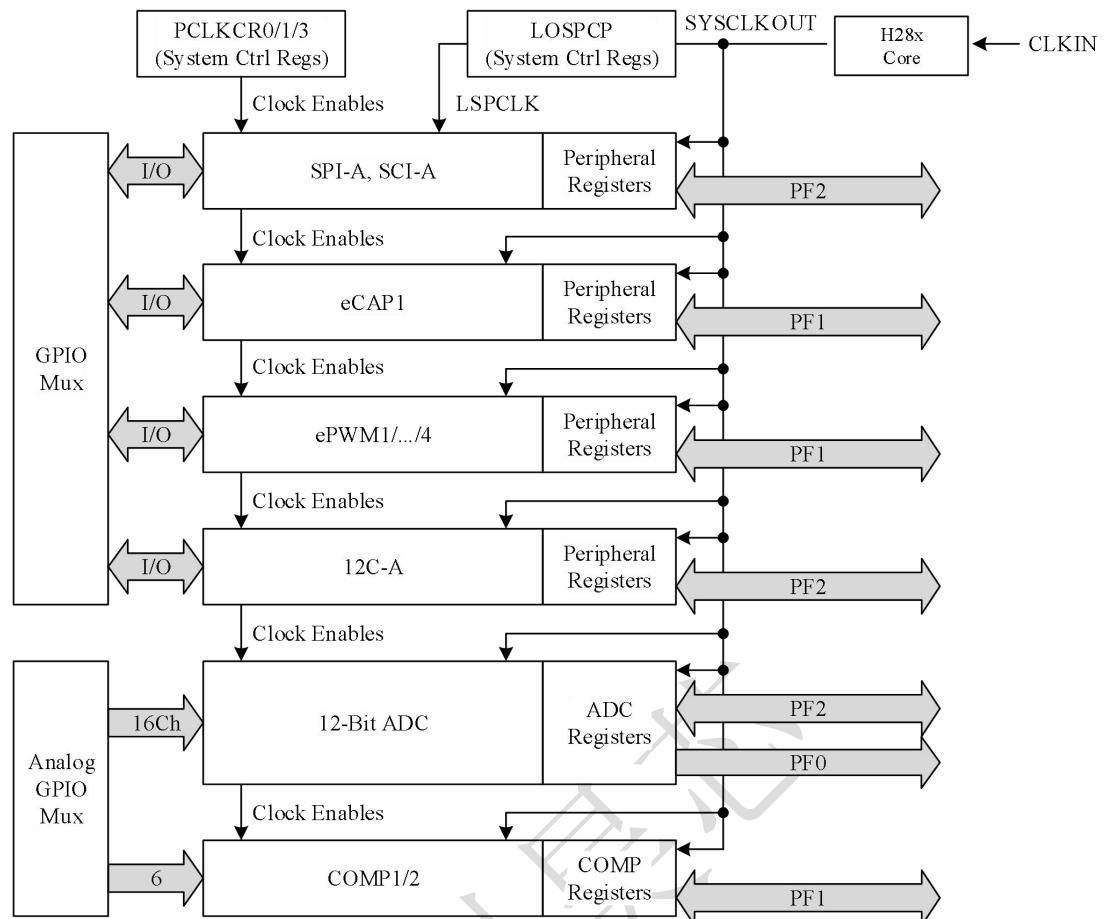

### 3.3.13 外设时钟

在外设闲置时，到每一个独立外设的时钟可被启用或禁用以减少功耗。此外，到串行端口（除了 I2C 之外）和 ADC 时钟的系统时钟可相对于 CPU 时钟进行缩放。这样可去除外设时序到逐渐增加的 CPU 时钟速度的耦合。

### 3.3.14 低功耗模式

HXS320F280103PX 器件是完全静态 CMOS 器件。提供三个低功耗模式：

- **IDLE:** 将 CPU 置于低功耗模式。可有选择性地关闭外设时钟并且只有那些在 IDLE 期间必须运行的外设保持运行状态。来自使能外设的已启用的中断或者看门狗将处理器从 IDLE 模式中唤醒。

- **STANDBY:** 关闭到 CPU 和外设的时钟。在这个模式下振荡器和 PLL 仍然运行。一个外部中断事件将唤醒处理器和外设。唤醒操作在检测到中断事件之后的下一个时钟周期执行。

- **HALT:** 该模式会关断器件并将器件置于尽可能低的功耗模式中。HALT 模式在内部零引脚振荡器被用作时钟源时默认关闭。为了防止这些振荡器被关闭，可配置 CLKCTL 寄存器内的 INTOSCnHALTI 位。这样零引脚振荡器可在这个模式下被用于为 CPU 看门狗计时。如果片载晶体振荡器被用作时钟源，在这个模式中它将被关闭。在此模式下可由一个复位信号或者外部信号（通过一个 GPIO 引脚）以及 CPU 看门狗唤醒。

在试图将器件置于 HALT 或者 STANDBY 模式前，CPU 时钟(OSCCLK) 和 WDCLK 信号应来自同一个时钟源。

### 3.3.15 通用输入/输出 (GPIO) 复用器

HXS320F280103PX 大多数的外设信号与通用输入/输出(GPIO)信号复用。这个复用使得用户能够在外设信号或者功能不使用时将一个引脚用作 GPIO。复位时所有 GPIO 引脚被配置为输入。针对 GPIO 模式或者外设信号模式，用户能够独立设定每一个引脚。对于特定的输入引脚，用户也可以选择输入限定周期的数量。这是为了过滤掉有害的噪音毛刺脉冲。GPIO 信号也可被用于使器件脱离特定低功耗模式。

### 3.3.16 32 位 CPU 定时器 (0, 1, 2)

CPU 定时器 0、1 和 2 是完全一样的 32 位定时器，这些定时器带有可预先设定的周期和 16 位时钟预分频。此定时器有一个 32 位倒计数寄存器，此寄存器在计数器达到 0 时生成一个中断。这个计数器的减量为被预分频值设置所分频的 CPU 时钟速度的值。当此计数器达到 0 时，它自动重新载入一个 32 位的周期值。

CPU 定时器 0 为通用定时器，并连接到 PIE 模块。CPU 定时器 1 同样为通用定时器，并可以被连接到 CPU 的 INT13。CPU 定时器 2 为 DSP 预留，并且连接到 CPU 的 INT14。如果 DSP 未被使用，CPU 定时器 2 也可作为通用定时器使用。

CPU 定时器 2 可由下列任何一种方式进行计时：

- SYSCLKOUT（默认）

- 内部零引脚振荡器 1 (INTOSC1)

- 内部零引脚振荡器 2 (INTOSC2)

- 外部时钟源

### 3. 3. 17 控制外设

HXS320F280103PX 支持以下用于嵌入式控制和通信的外设：

- **ePWM:** 增强型 PWM 外设支持针对前缘/后缘边沿、被锁存的/逐周期机制的独立的/互补的 PWM 生成，可调节死区生成。一些 PWM 引脚支持 HRPWM 高分辨率占空比和周期特性。HXS320F2803X 器件上的类型 1 模块也支持增强的死区分辨率、增强型片上系统(SOC) 和中断生成和包括基于比较器输出的触发功能的高级触发。

- **eCAP:** 此增强型捕获外设使用一个 32 位时基并在连续/单次捕获模式中记录多达四个可编程事件。这个外设也被可被配置为生成一个辅助 PWM 信号。

- **eQEP:** 增强型 QEP 外设使用一个 32 位位置计数器，使用捕获单元和一个 32 位单元定时器分别支持低速测量和高速测量。这个外设有一个看门狗定时器来检测电机停转和输入错误检测逻辑电路来识别 QEP 信号中的同步边沿转换。

- **ADC:** ADC 模块是一个 12 位转换器。根据器件的不同它有多达 10 个单端通道输出引脚。它包含两个用于同步采样的单元。

- **比较器:** 每个比较器块由一个模拟比较器连同一个为比较器的输入供电的内部 10 位基准组成。

### 3. 3. 18 串行端口外设

HXS320F280103PX 器件支持下列的串行通信外设：

- **SPI:** SPI 是一个高速、同步串行 I/O 端口，此端口可在设定的位传输速率上将一个设定长度（1 至 16 位）的串行比特流移入和移出器件。SPI 常用于 MCU 和外部外设或者其它处理器之间的通信。典型应用包括外部 I/O 或者从诸如移位寄存器、显示驱动器和 ADC 等器件的外设扩展。多器件通信由 SPI 主控/受控操作支持。SPI 包含一个用于减

少中断处理开销的 4 级接收和发送 FIFO。

- SCI:** 串行通信接口是一个两线制异步串行端口，通常被称为 UART。SCI 包含一个用于减少中断处理开销的 4 级接收和发送 FIFO。

- I2C:** 内部集成电路 (I2C) 模块提供一个 MCU 和其它器件（符合飞利浦半导体内部 IC 总线 (I2C-bus) 规范版本 2.1 并由一个 I2C-bus 相连）间的接口。通过这个 I2C 模块，连接在这个两线制总线上的外部组件能够发送 8 位数据到 MCU 或者从 MCU 接收 8 位数据。I2C 包含一个用于减少中断处理开销的 4 级接收和发送 FIFO。

### 3.4 寄存器映射

表 3-7 HXS320F280103PX 寄存器映射表

| 名称             | 地址范围              | 大小 (字节) | EALLOW 保护 |

|----------------|-------------------|---------|-----------|

| Flash 控制寄存器    | 0x7AF800—0x7AF900 | 256     | 是         |

| CSM 寄存器        | 0x7AF804—0x7AF810 | 16      | 是         |

| ADC 结果寄存器 (只读) | 0x149C—0x1800     | 868     | 否         |

| CPU 定时器 0/1/2  | 0x1800—0x1900     | 256     | 是         |

| PIE 寄存器        | 0x1900—0x1968     | 104     | 是         |

| PIE 向量表        | 0x1A00—0x1C00     | 512     | 是         |

| DMA 寄存器        | 0x1C00—0x2000     | 512     | 否         |

| 比较器 1          | 0xC000—0xC080     | 128     | 是         |

| 比较器 2          | 0xC080—0xC0C0     | 128     | 是         |

| ePWM1+HRPWM1   | 0xB000—0xB400     | 1024    | 是         |

| ePWM2+HRPWM2   | 0xB400—0xB800     | 1024    | 是         |

| ePWM3+HRPWM3   | 0xB800—0xBC00     | 1024    | 是         |

| ePWM4+HRPWM4   | 0xBC00—0xC000     | 1024    | 是         |

| eCAP1 寄存器      | 0xD000—0xD400     | 1024    | 否         |

| eQEP1 寄存器      | 0xD400—0xD800     | 1024    | 否         |

| GPIO 寄存器       | 0xD800—0xDC00     | 1024    | 是         |

| 系统控制寄存器        | 0xDC00—0xE000     | 1024    | 是         |

| SPI-A 寄存器      | 0xE800—0xEC00     | 1024    | 否         |

| SCI-A 寄存器      | 0xE000—0xE400     | 1024    | 否         |

| 外部中断           | 0x1968—0x19E4     | 124     | 是         |

| ADC 寄存器        | 0x1400—0x149C     | 156     | 是         |

| IIC-A 寄存器      | 0xE400—0xE800     | 1024    | 否         |

注释：

- 如果寄存器受 EALLOW 保护，则在执行 EALLOW 指令之前，无法执行写操作。EDIS 指令禁用写操作以防止杂散代码或指针损坏寄存器内容。

- 闪存寄存器也受到代码安全模块 (CSM) 的保护。

### 3.5 器件仿真寄存器

表 3-8 器件仿真寄存器映射

| 名称        | 地址范围     | 大小   | 说明      |

|-----------|----------|------|---------|

| DEVICECNF | 0xDC80   | 4 字节 | 设备配置寄存器 |

| PARTID    | 0x7A3BFC | 4 字节 | 芯片型号    |

| CLASSID   | 0xDC84   | 4 字节 | 芯片系列号   |

| REVID     | 0xDC88   | 4 字节 | 芯片版本号   |

### 3.6 中断系统

下图显示了各种中断源是如何复用的。

图 3-2 PIE 模块互连示意图

图 3-3 PIE 中断映射示意图

表 3-9 PIE 外设中断向量表

| 中断向量入口  | INTx. 8                       | INTx. 7                     | INTx. 6                    | INTx. 5                      | INTx. 4                          | INTx. 3                          | INTx. 2                          | INTx. 1                          |

|---------|-------------------------------|-----------------------------|----------------------------|------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|

| INT1.y  | WAKEINT<br>(LPM/WD)<br>0x1A1C | TINTO<br>(TIMERO)<br>0x1A18 | ADCINT9<br>(ADC)<br>0x1A14 | XINT2<br>Ext int 2<br>0x1A10 | XINT1<br>Ext int 1<br>0x1A0C     | Reserved<br>—<br>0x1A08          | ADCINT2<br>(ADC)<br>0x1A04       | ADCINT1<br>(ADC)<br>0x1A00       |

| INT2.y  | Reserved<br>—<br>0x1A3C       | Reserved<br>—<br>0x1A38     | Reserved<br>—<br>0x1A34    | Reserved<br>—<br>0x1A30      | EPWM4_TZINT<br>(ePWM4)<br>0x1A2C | EPWM3_TZINT<br>(ePWM3)<br>0x1A28 | EPWM2_TZINT<br>(ePWM2)<br>0x1A24 | EPWM1_TZINT<br>(ePWM1)<br>0x1A20 |

| INT3.y  | Reserved<br>—<br>0x1A5C       | Reserved<br>—<br>0x1A58     | Reserved<br>—<br>0x1A54    | Reserved<br>—<br>0x1A50      | EPWM4_INT<br>(ePWM4)<br>0x1A4C   | EPWM3_INT<br>(ePWM3)<br>0x1A48   | EPWM2_INT<br>(ePWM2)<br>0x1A44   | EPWM1_INT<br>(ePWM1)<br>0x1A40   |

| INT4.y  | Reserved<br>—<br>0x1A7C       | Reserved<br>—<br>0x1A78     | Reserved<br>—<br>0x1A74    | Reserved<br>—<br>0x1A70      | Reserved<br>—<br>0x1A6C          | Reserved<br>—<br>0x1A68          | Reserved<br>—<br>0x1A64          | ECAP1_INT<br>(ECAP1)<br>0x1A60   |

| INT5.y  | Reserved<br>—<br>0x1A9C       | Reserved<br>—<br>0x1A98     | Reserved<br>—<br>0x1A94    | Reserved<br>—<br>0x1A90      | Reserved<br>—<br>0x1A8C          | Reserved<br>—<br>0x1A88          | Reserved<br>—<br>0x1A84          | EQEP1_INT<br>(eQEP1)<br>0x1A80   |

| INT6.y  | Reserved<br>—<br>0x1ABC       | Reserved<br>—<br>0x1AB8     | Reserved<br>—<br>0x1AB4    | Reserved<br>—<br>0x1AB0      | Reserved<br>—<br>0x1AAC          | Reserved<br>—<br>0x1AA8          | SPITXINTA<br>(SPI-A)<br>0x1AA4   | SPIRXINTA<br>(SPI-A)<br>0x1AA0   |

| INT7.y  | Reserved<br>—<br>0x1ADC       | Reserved<br>—<br>0x1AD8     | DINCH6<br>(DMA)<br>0x1AD4  | DINCH5<br>(DMA)<br>0x1AD0    | DINCH4<br>(DMA)<br>0x1ACC        | DINTCH3<br>(DMA)<br>0x1AC8       | DINTCH2<br>(DMA)<br>0x1AC4       | DINTCH1<br>(DMA)<br>0x1AC0       |

| INT8.y  | Reserved<br>—<br>0x1AFC       | Reserved<br>—<br>0x1AF8     | Reserved<br>—<br>0x1AF4    | Reserved<br>—<br>0x1AF0      | Reserved<br>—<br>0x1ACC          | Reserved<br>—<br>0x1AC8          | I2CINT2A<br>(I2C-A)<br>0x1AC4    | I2CINT1A<br>(I2C-A)<br>0x1AE0    |

| INT9.y  | Reserved                      | Reserved                    | Reserved                   | Reserved                     | Reserved                         | Reserved                         | SCITXINTA                        | SCIRXINTA                        |

|         | —                             | —                           | —                          | —                            | —                                | —                                | (SCI-A)                          | (SCI-A)                          |

|         | 0x1B1C                        | 0x1B18                      | 0x1B14                     | 0x1B10                       | 0x1B18                           | 0x1B14                           | 0x1B10                           | 0x1B00                           |

| INT10.y | ADCINT8<br>(ADC)<br>0x1B3C    | ADCINT7<br>(ADC)<br>0x1B38  | ADCINT6<br>(ADC)<br>0x1B34 | ADCINT5<br>(ADC)<br>0x1B30   | ADCINT4<br>(ADC)<br>0x1B2C       | ADCINT3<br>(ADC)<br>0x1B28       | ADCINT2<br>(ADC)<br>0x1B24       | ADCINT1<br>(ADC)<br>0x1B20       |

| INT11.y | Reserved<br>—<br>0x1B5C       | Reserved<br>—<br>0x1B58     | Reserved<br>—<br>0x1B54    | Reserved<br>—<br>0x1B50      | Reserved<br>—<br>0x1B4C          | Reserved<br>—<br>0x1B48          | Reserved<br>—<br>0x1B44          | Reserved<br>—<br>0x1B40          |

| INT12.y | Reserved<br>—<br>0x1B7C       | Reserved<br>—<br>0x1B78     | Reserved<br>—<br>0x1B74    | Reserved<br>—<br>0x1B70      | Reserved<br>—<br>0x1B6C          | Reserved<br>—<br>0x1B68          | Reserved<br>—<br>0x1B64          | XINT3<br>Ext int3<br>0x1B60      |

| INT13.y | Reserved<br>—                 | Reserved<br>—               | Reserved<br>—              | Reserved<br>—                | Reserved<br>—                    | Reserved<br>—                    | Reserved<br>—                    | TIMER1<br>(TIMER)                |

| 中断向量入口  | INTx. 8                 | INTx. 7                | INTx. 6                | INTx. 5                | INTx. 4                | INTx. 3                | INTx. 2                | INTx. 1                    |

|---------|-------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|----------------------------|

|         | 0x1B9C                  | 0x1B98                 | 0x1B94                 | 0x1B90                 | 0x1B8C                 | 0x1B88                 | 0x1B84                 | 0x1B80                     |

| INT14.y | Reserved<br>-<br>0xBBBC | Reserved<br>-<br>0xBB8 | Reserved<br>-<br>0xBB4 | Reserved<br>-<br>0xBB0 | Reserved<br>-<br>0xBAE | Reserved<br>-<br>0xBA8 | Reserved<br>-<br>0xBA4 | TIMER2<br>(TIMER)<br>0xBA0 |

|         |                         |                        |                        |                        |                        |                        |                        |                            |

表 3-10 PIE 配置和控制寄存器（基址为 0x1800）

| 名称       | 地址     | 描述                |

|----------|--------|-------------------|

| PIECTRL  | 0x1900 | PIE 控制寄存器         |

| PIEACK   | 0x1904 | PIE 确认寄存器         |

| PIEIER1  | 0x1908 | PIE, 中断第 1 组使能寄存器 |

| PIEIFR1  | 0x190C | PIE 中断第 1 组标志寄存器  |

| PIEIER2  | 0x1910 | PIE 中断第 2 组使能寄存器  |

| PIEIFR2  | 0x1914 | PIE 中断第 2 组标志寄存器  |

| PIEIER3  | 0x1918 | PIE 中断第 3 组使能寄存器  |

| PIEIFR3  | 0x191C | PIE 中断第 3 组标志寄存器  |

| PIEIER4  | 0x1920 | PIE 中断第 4 组使能寄存器  |

| PIEIFR4  | 0x1924 | PIE 中断第 4 组标志寄存器  |

| PIEIER5  | 0x1928 | PIE 中断第 5 组使能寄存器  |

| PIEIFR5  | 0x192C | PIE 中断第 5 组标志寄存器  |

| PIEIER6  | 0x1930 | PIE 中断第 6 组使能寄存器  |

| PIEIFR6  | 0x1934 | PIE 中断第 6 组标志寄存器  |

| PIEIER7  | 0x1938 | PIE 中断第 7 组使能寄存器  |

| PIEIFR7  | 0x193C | PIE 中断第 7 组标志寄存器  |

| PIEIER8  | 0x1940 | PIE 中断第 8 组使能寄存器  |

| PIEIFR8  | 0x1944 | PIE 中断第 8 组标志寄存器  |

| PIEIER9  | 0x1948 | PIE 中断第 9 组使能寄存器  |

| PIEIFR9  | 0x194C | PIE 中断第 9 组标志寄存器  |

| PIEIER10 | 0x1950 | PIE 中断第 10 组使能寄存器 |

| 名称       | 地址     | 描述                |

|----------|--------|-------------------|

| PIEIFR10 | 0x1954 | PIE 中断第 10 组标志寄存器 |

| PIEIER11 | 0x1958 | PIE 中断第 11 组使能寄存器 |

| PIEIFR11 | 0x195C | PIE 中断第 11 组标志寄存器 |

| PIEIER12 | 0x1960 | PIE 中断第 12 组使能寄存器 |

| PIEIFR12 | 0x1964 | PIE 中断第 12 组标志寄存器 |

| XINT1CR  | 0x1968 | 外部中断 1 配置寄存器      |

| XINT2CR  | 0x196C | 外部中断 2 配置寄存器      |

| XINT3CR  | 0x1970 | 外部中断 3 配置寄存器      |

| XINT1CTR | 0x1974 | 外部中断 1 计数器寄存器     |

| XINT2CTR | 0x1978 | 外部中断 2 计数器寄存器     |

| XINT3CTR | 0x197C | 外部中断 3 计数器寄存器     |

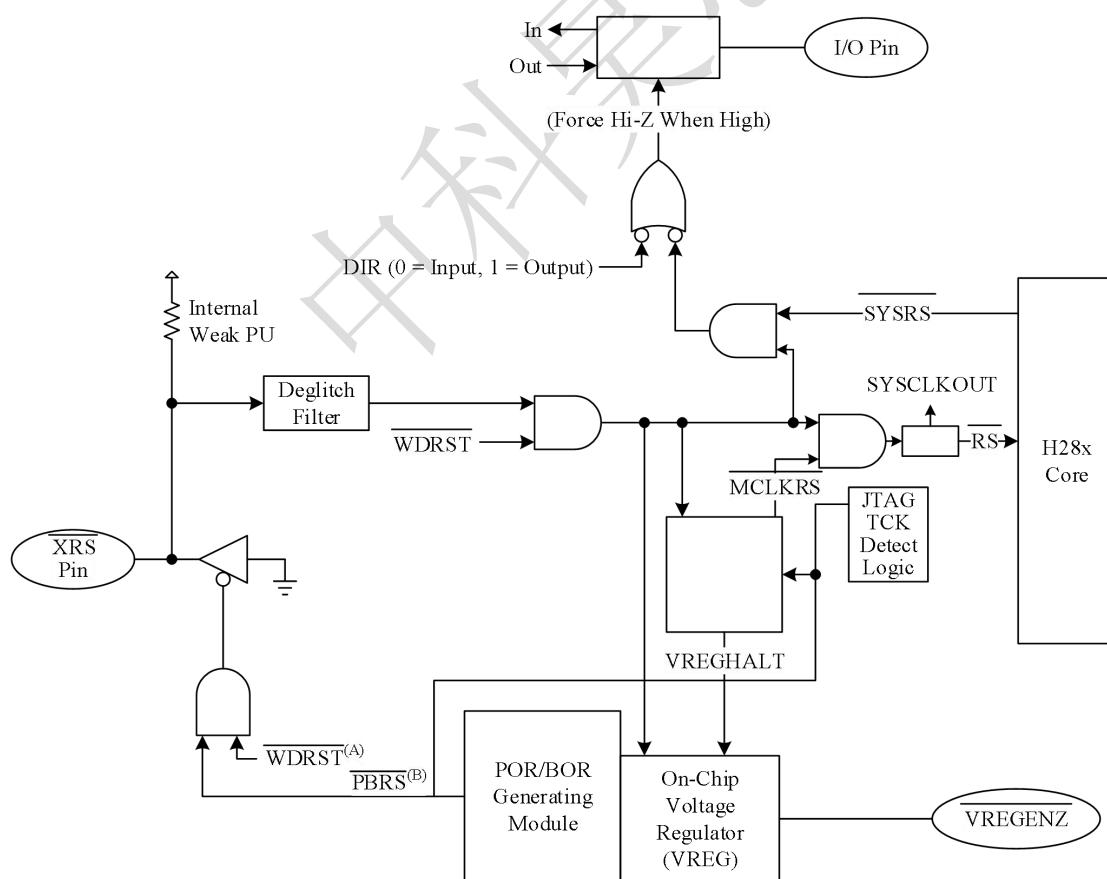

## 3.7 VREG/BOR/POR

虽然核心和 I/O 电路在两种不同的电压下工作，但这些设备具有片上稳压器（VREG）从  $V_{DDIO}$  电源产生  $V_{DD}$  电压。这消除了在应用板上使用第二个外部稳压器的成本和空间。此外，内部上电复位（POR）在通电和运行模式下，掉电复位（BOR）电路同时监视  $V_{DD}$  和  $V_{DDIO}$  轨道。

### 3.7.1 VREG

线性稳压器从  $V_{DDIO}$  电源产生核心电压 ( $V_{DD}$ )。因此，尽管每个  $V_{DD}$  引脚上都需要电容器来稳定所产生的的电压，但并不需要向这些引脚供电来操作设备。相反，如果电源或冗余成为应用程序的主要考虑因素，则可以禁用 VREG。

#### 3.7.1.1 使用片上 VREG

为了采用片载 VREG，VREGNZ 引脚应该被接至低电平并且适当的建议运行电压应该被用于  $V_{DDA}$  和  $V_{DDIO}$  引脚。在这个情况下，内核逻辑所需的  $V_{DD}$  电压将由 VREG 生成。为了实现 VREG 正确的调节，每一个  $V_{DD}$  引脚需要电容值为  $1.2 \mu F$  的电容器。这些电容应该被放置在尽可能接近  $V_{DD}$  引脚的位置。

### 3.7.1.2 不使用片上 VREG

为了节约能耗，也可禁用片载 VREG 并使用一个效率更高的外部稳压器将内核逻辑电压提供给  $V_{DD}$  引脚。为了启用这个选项，VREGNZ 引脚必须被接至高电平。

**注意：**芯片 Vreg 电压典型值为 1.57V。

### 3.7.2 片上上电复位 (POR) 和掉电复位 (BOR) 电路

两个片上监控电路，上电复位 (POR) 和掉电复位 (BOR) 从应用板上移除了监控  $V_{DD}$  和  $V_{DDIO}$  电源的负担。POR 的目的是在整个上电过程中，在整个设备中创建一个干净的复位。此触发点是一个非固定的，比 BOR 更低的触发点，将在器件运行期间监视  $V_{DD}$  或  $V_{DDIO}$  电源轨道的骤减操作 POR 功能总是出现在  $V_{DD}$  和  $V_{DDIO}$  电源轨道上。设备首次上电后 BOR 功能总是出现在  $V_{DDIO}$  上，并且当内部 VREG 启用时，出现在  $V_{DD}$  上 (VREGNZ 引脚被接至低电平)。当其中一个电压低于它们各自的触发点时两个功能连接至 XRS 引脚低电平。此外，当内部电压稳压器被启用时，一个过压保护电路将连接至 XRS 低电平，此时  $V_{DD}$  电源轨道上升至高于其触发点。图 3-4 显示 VREG、POR 和 BOR。

图 3-4 VREG+POR+BOR+复位信号连接

A. WDRST 为从 CPU-看门狗发出的复位信号

B. PBRS 是从 POR/BOR 发出的复位信号

### 3.8 系统控制

这一部分对振荡器和时钟机制、看门狗功能以及低功耗模式进行了说明。

所有系统控制寄存器都是受 EALLOW 保护的寄存器。

表 3-11 系统控制寄存器映射

| 地址偏移    | 寄存器         | 描述                  |

|---------|-------------|---------------------|

| 0xDC00h | XCLK        | XCLKOUT/XCLKIN 时钟控制 |

| 0xDC04h | PLLSTS      | PLL 状态寄存器           |

| 0xDC08h | PCLKCRO     | 外设时钟控制寄存器 0         |

| 0xDC0ch | PCLKCR1     | 外设时钟控制寄存器 1         |

| 0xDC10h | PCLKCR2     | 外设时钟控制寄存器 2         |

| 0xDC14h | PCLKCR3     | 外设时钟控制寄存器 3         |

| 0xDC18h | LOSPCP      | 低速外设时钟预分频寄存器        |

| 0xDC1ch | INTOSC1TRIM | 内部晶振校准寄存器 1         |

| 0xDC20h | INTOSC2TRIM | 内部晶振校准寄存器 2         |

| 0xDC24h | CLKCTL      | 时钟控制寄存器             |

| 0xDC28h | PLLCR       | PLL 控制寄存器           |

| 0xDC2ch | PLLLOCKPRD  | PLLLOCKPRD 寄存器      |

| 0xDC30h | LPMCR0      | 低功耗模式控制寄存器          |

| 0xDC34h | SCSR        | 系统控制状态寄存器           |

| 0xDC38h | WDCNTR      | 看门狗计数器寄存器           |

| 0xDC3ch | WDKEY       | 看门狗复位秘钥寄存器          |

| 0xDC40h | WDCR        | 看门狗控制寄存器            |

| 0xDC44h | JTAGDEBUG   | JTAG 控制寄存器          |

| 0xDC60h | BORCFG      | BOR 配置寄存器           |

| 0xDC80h | DEVICECNF   | 器件配置寄存器             |

| 0xDC84h | CLASSID     | CLASSID 寄存器         |

| 0xDC88h | REVID       | 芯片版本寄存器             |

注 1：这个表中的所有寄存器是受 EALLOW 保护的。

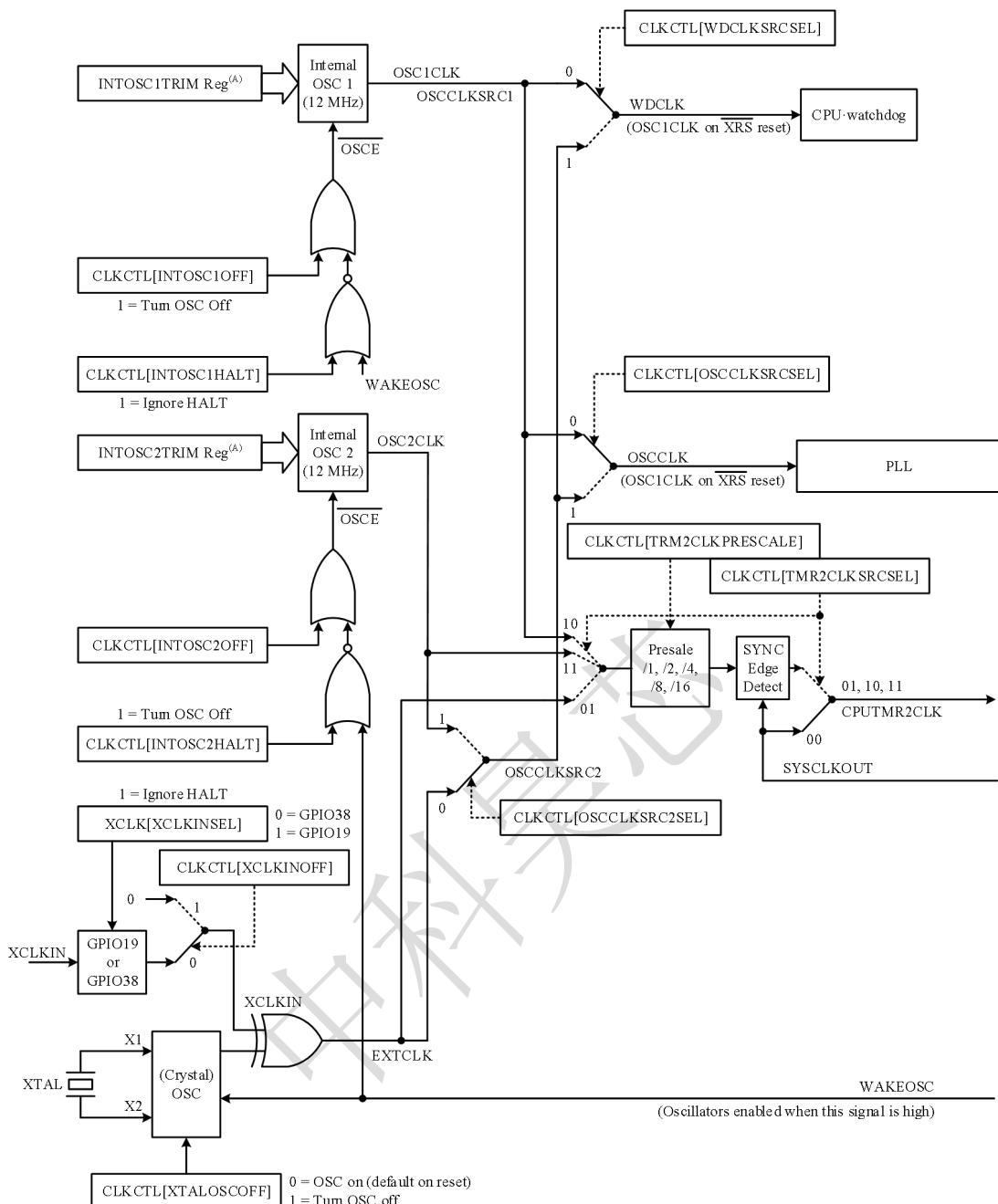

图 3-5 时钟及复位域

图 3-6 时钟树

A. 由 OTP 中的校正程序载入寄存器

### 3.8.1 内部零引脚振荡器

HXS320F280103PX 器件包含两个独立的内部零引脚振荡器。默认情况下两个振荡器在上电时全都打开，此时内部振荡器 1 是默认时钟源。为了降低功耗，用户可将不使用的振荡器关断。这些振荡器的中心频率由它们各自的振荡器调整寄存器决定，此寄存器在校准例程中被写入作为引导 ROM 执行的一部分。

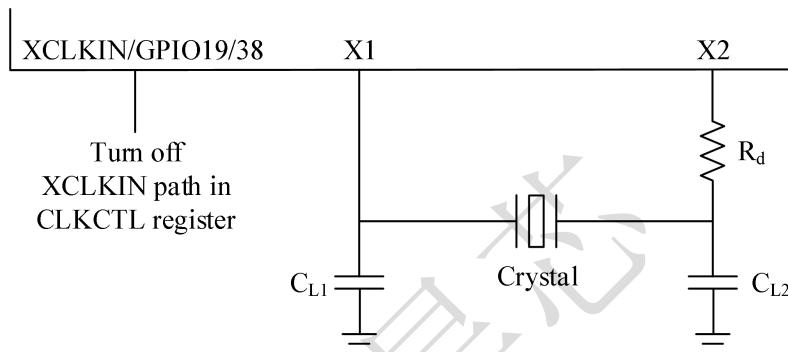

### 3.8.2 晶体振荡器选项

如果将系统 3.3V 外部振荡器用作时钟源，则应将 XCLKIN 用作时钟源。外部石英晶体的典型规格（基本模式，并联谐振）在以下列表中列出。此外，ESR 范围= 30 至  $150\Omega$ 。

表格 3-11 外部石英晶体的典型规格

| 频率 (MHz) | $R_d(\Omega)$ | $C_{L1}$ (pF) | $C_{L2}$ (pF) |

|----------|---------------|---------------|---------------|

| 5        | 2200          | 18            | 18            |

| 10       | 470           | 15            | 15            |

| 15       | 0             | 15            | 15            |

| 20       | 0             | 12            | 12            |

注： $C_{shunt}$  应该小于或等于 5pF。

图 3-7 使用片上晶体振荡器

- $C_{L1}$  和  $C_{L2}$  是电路板和不包括电容的组件的总电容，该值通常约为晶体负载值的两倍电容。

- 晶体的负载电容在晶振制造商的晶体规格中有所描述。

- 中科昊芯建议客户让谐振器/晶体供应商来表征他们的设备使用 MCU 芯片进行操作。谐振器/晶体供应商拥有调整震荡电路的设备和专业知识。供应商还可以建议 客户关于适当的元器件值将产生正确的启动整个工作范围内的稳定性。

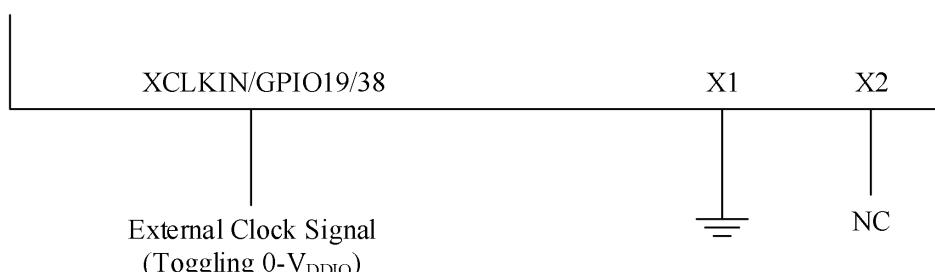

图 3-8 使用 3.3v 片外有源振荡器

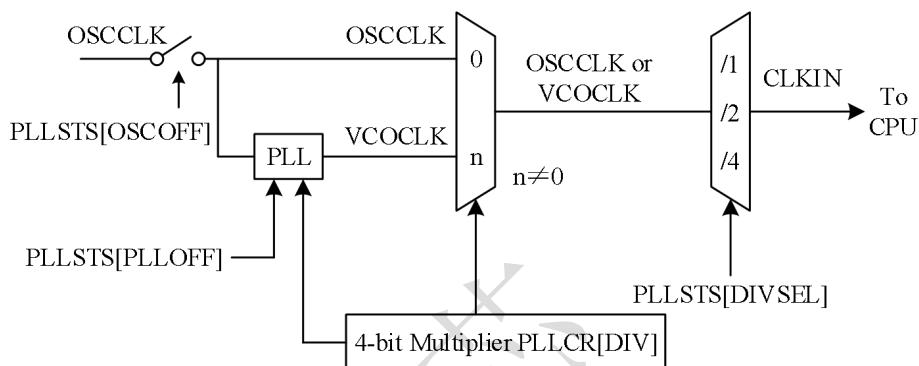

### 3.8.3 基于 PLL 的时钟模块

HXS320F280103PX 有一个基于片载 PLL 的时钟模块。这个模块为器件提供所有需要的时

钟信号以及对进入低功耗模式的控制。PLL 有一个 4 位比率控制 PLLCR[DIV] 来选择不同的 CPU 时钟速率。在写入 PLLCR 寄存器之前，看门狗模块应该被禁用。在 PLL 模式稳定后，它可被重新启用（如果需要的话），重新启用的时间为 1ms。输入时钟和 PLLCR[DIV] 位的选择方法应该是在 PLL (VCOCLK) 的输出频率至少为 50MHz 的时候再选择。

下图显示了 OSC 和 PLL 框图。

图 3-9 OSC 和锁相环模块

注意：

芯片 PLL 输入的时钟频率为 5~30MHz，VCO 的范围是 30MHz~300MHz。

### 3.9 低功耗模块

HXS320F280103PX 处理器的低功耗模式如下：

表 3-13 低功耗模式列表

| 模式      | LPMCR0[1:0] | OSCCLK                             | CLKIN | SYSCLKOUT | Exit                                        |

|---------|-------------|------------------------------------|-------|-----------|---------------------------------------------|

| IDLE    | 00          | On                                 | On    | On        | XRS,<br>看门狗中断，<br>任何中断                      |

| STANDBY | 01          | On<br>(看门狗还在运行)                    | Off   | Off       | XRS,<br>看门狗中断，<br>GPIO 端口 A 信号，<br>Debugger |

| HALT    | 1X          | Off<br>(osc 和 PLL<br>关断，看门<br>狗停止) | Off   | Off       | XRS，<br>GPIO 端口 A 信号，<br>Debugger, 看门狗      |

在各种低功耗模式下，处理器进行的操作如下表所示：

**IDLE 模式:** 处理器识别的任何使能的中断都存在该模式。只要 LPMCR0 位设置为 0, LPM 模块就不会在此模式下执行任何操作。

**STANDBY 模式:** 任何一个 GPIO 端口 A 信号(GPIO[31:0])能够将器件从 STANDBY 模式中唤醒。用户必须通过 GPIOLPMSEL 寄存器选择哪一个信号将器件唤醒。唤醒设备之前, OSCCLK 还可以对选定的信号进行确认。OSCCLK 的数量在 LPMCR0 寄存器中指定

**HALT 模式:** CPU 看门狗, XRS 和任何一个 GPIO 端口 A 信号(GPIO[31:0])可将器件从 HALT 模式中唤醒。用户在 GPIOLPMSEL 寄存器中选择信号。

HXS320F280103PX 处理器提供了两种选项在没有外部激励的情况下, 可自动从 HALT 和 STANDBY 模式唤醒

- 从 HALT 模式唤醒: 将 CLKCTL 寄存器中 WDHALTI 位置 1, 通过处理器看门狗复位将处理器从 HALT 模式唤醒。WDCR 寄存器中的 WDFLAG 位用来区别处理器的看门狗复位和设备复位。

- 从 STANDBY 模式唤醒: 将寄存器 LPMCR0 中的 WDINTE 位置 1, 通过 WAKEINT 中断将处理器从 STANDBY 模式唤醒。

## 4. 外设

### 4.1 模拟器件

#### 4.1.1 ADC 特性

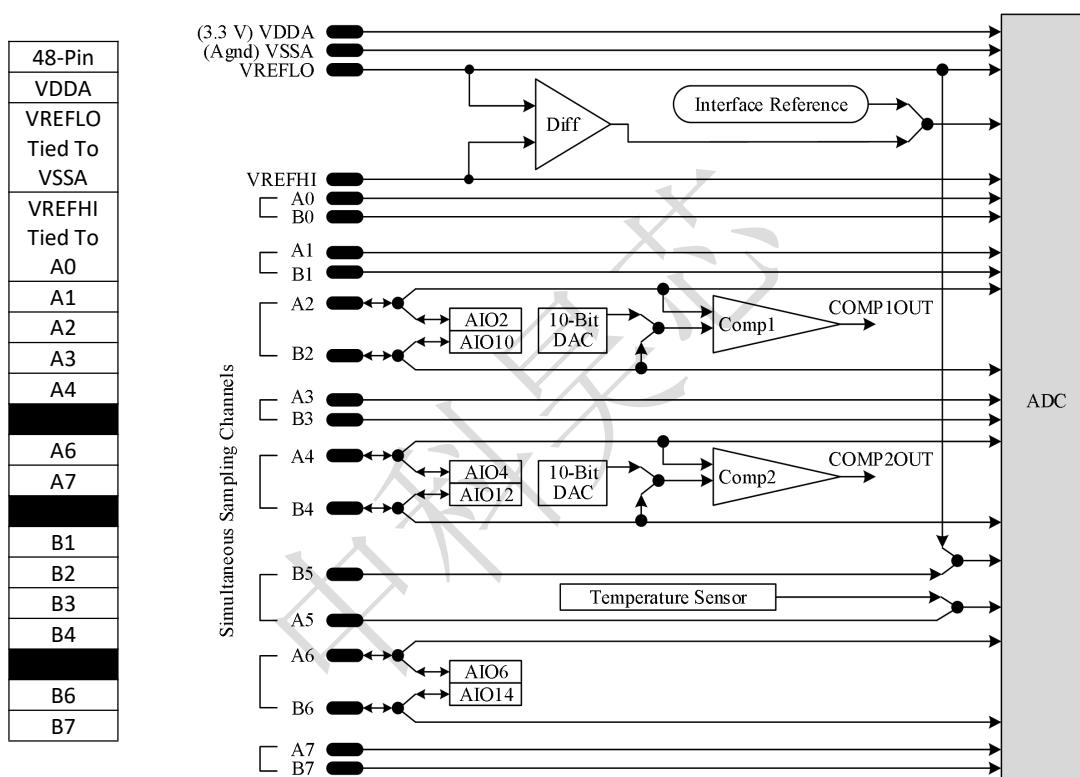

图 4-1 显示了模拟器件与 H28x 系统其余部分的交互。

图 4-1 模拟引脚配置

ADC 的核包含一个 12 位转换器, 转换器由两个采样电路供电。采样电路可以同时采样, 也可以按顺序采样。ADC 总共有多达 10 个模拟输入通道。转换器可被配置为使用一个内部带隙基准来创建真正的基于电压的转换。

与之前的 ADC 类型不同此 ADC 不是基于序列器的。用户很容易从单个触发器创建一系列转换。然而, 操作的基本原理是围绕配置的单个转换的开始, 称为 SOC 或转换的开始。

ADC 模块的功能包括:

内置双采样的 12 位 ADC 核心

同时采样或顺序采样模式全量程模拟输入: 0V 至 3.3V 固定。

电压由以下公式得出：

$$\begin{aligned}

\text{当 输入} \leqslant 0V, \quad & \text{数字值} = 0 \\

\text{当 } 0V < \text{输入} < 3.3 V, \quad & \text{数字值} = 4096 \times \frac{\text{模拟输入电压} - V_{REFLO}}{3.3} \\

\text{当 输入} \geqslant 3.3 V, \quad & \text{数字值} = 4095

\end{aligned}$$

- 最多 10 通道，多路输入

- 16 个 SOC，可配置触发器、采样窗口和通道

- 16 个结果寄存器（可单独寻址），用于存储转换值

- 多触发源

- 软件 - 软件立即启动

- ePWM 1 - 4

- GPIO XINT2

- CPU 计时器 0/1/2

- ADC 中断 1/2

- 9 个灵活的 PIE 中断，可配置任意转换后的中断请求

表 4-1 ADC 配置和控制寄存器

| 名称           | 地址     | EALLOW<br>保护 | 描述                     |

|--------------|--------|--------------|------------------------|

| ADCCTL1      | 0x1400 | 是            | 控制 1 寄存器               |

| ADCCTL2      | 0x1404 | 是            | 控制 2 寄存器               |

| ADCINTFLG    | 0x1408 | 否            | 中断标志寄存器                |

| ADCINTFLGCLR | 0x140C | 否            | 中断标志清除寄存器              |

| ADCINTOVF    | 0x1410 | 否            | 中断溢出寄存器                |

| ADCINTOVFCLR | 0x1414 | 否            | 中断溢出清除寄存器              |

| INTSEL1N2    | 0x1418 | 是            | 中断 1 和 2 选择寄存器         |

| INTSEL3N4    | 0x141C | 是            | 中断 3 和 4 选择寄存器         |

| INTSEL5N6    | 0x1420 | 是            | 中断 5 和 6 选择寄存器         |

| INTSEL7N8    | 0x1424 | 是            | 中断 7 和 8 选择寄存器         |

| INTSEL9N10   | 0x1428 | 是            | 中断 9 选择寄存器(保留中断 10 选择) |

| SOCPRICCTL   | 0x142C | 是            | SOC 优先级控制寄存器           |

| 名称                         | 地址              | EALLOW<br>保护 | 描述                       |

|----------------------------|-----------------|--------------|--------------------------|

| ADCSAMPLEMODE              | 0x1430          | 是            | 采样模式寄存器                  |

| ADCINTSOCSEL1              | 0x1434          | 是            | 中断 SOC 选择 1 寄存器 (8 通道)   |

| ADCINTSOCSEL2              | 0x1438          | 是            | 中断 SOC 选择 2 寄存器 (8 通道)   |

| ADCSOCFLG1                 | 0x143C          | 否            | SOC 标志 1 寄存器 (16 通道)     |

| ADCSOCFRC1                 | 0x1440          | 否            | SOC 力 1 寄存器 (16 通道)      |

| ADCSOCOVF1                 | 0x1444          | 否            | SOC 溢出 1 寄存器 (用于 16 通道)  |

| ADCSOCOVFCLR1              | 0x1448          | 否            | SOC 溢出清除 1 寄存器(用于 16 通道) |

| ADCSOCOCTL<br>~ADCSOC15CTL | 0x144C – 0x1488 | 是            | SOC0 控制寄存器到 SOC15 控制寄存器  |

| ADCREFTRIM                 | 0x148C          | 是            | 参考微调寄存器                  |

| ADCOFFTRIM                 | 0x1490          | 是            | 偏移微调寄存器                  |

| COMPHYSTCTL                | 0x1494          | 是            | 比较器滞后控制寄存器               |

| ADCREV                     | 0x1498          | 否            | ADC 版本号                  |

#### ADC 结果寄存器

| 名称                         | 地址              | EALLOW 保护 | 描述        |

|----------------------------|-----------------|-----------|-----------|

| ADCRESULT0~<br>ADCRESULT15 | 0x149C 至 0x1800 | 否         | ADC 结果寄存器 |

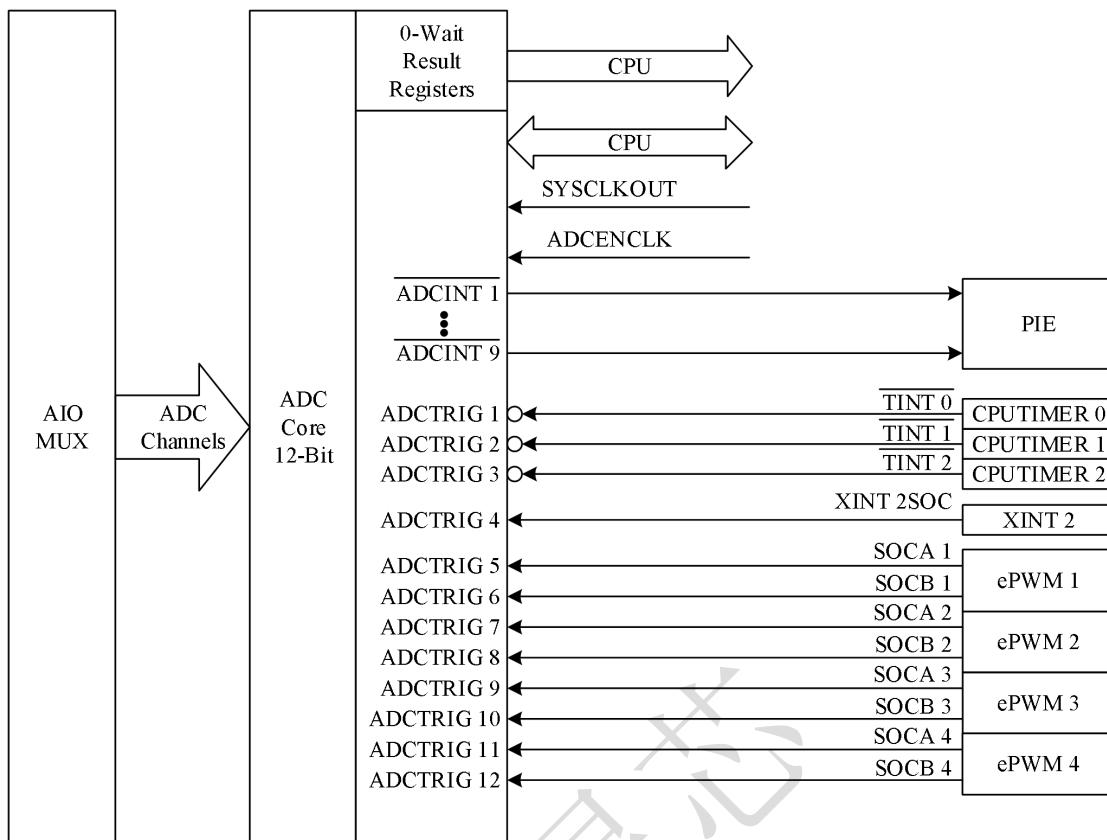

图 4-2 ADC 模块连接图

**ADC 连接（如果未使用 ADC）**

中科昊芯建议保持模拟电源引脚的连接，即使未使用 ADC。下面是一个如果应用程序中未使用 ADC，则应如何连接 ADC 引脚的摘要：

- VDDA – 连接到 VDDIO

- VSSA – 连接到 VSS

- VREFLO – 连接到 VSS

- ADCINAn、ADCINBn、VREFHI – 连接到 VSSA

在应用中使用 ADC 模块时，未使用的 ADC 输入引脚应连接到模拟地（VSSA）。

**注意：**

与 AIO 功能多路复用的未使用的 ADCIN 引脚不应直接连接到模拟地。它们应通过  $1\text{k}\Omega$  电阻器接地。这是为了防止错误代码将这些引脚配置为 AIO 输出，并将接地引脚驱动到逻辑高状态。

当不使用 ADC 时，确保 ADC 模块的时钟未打开以实现节能。

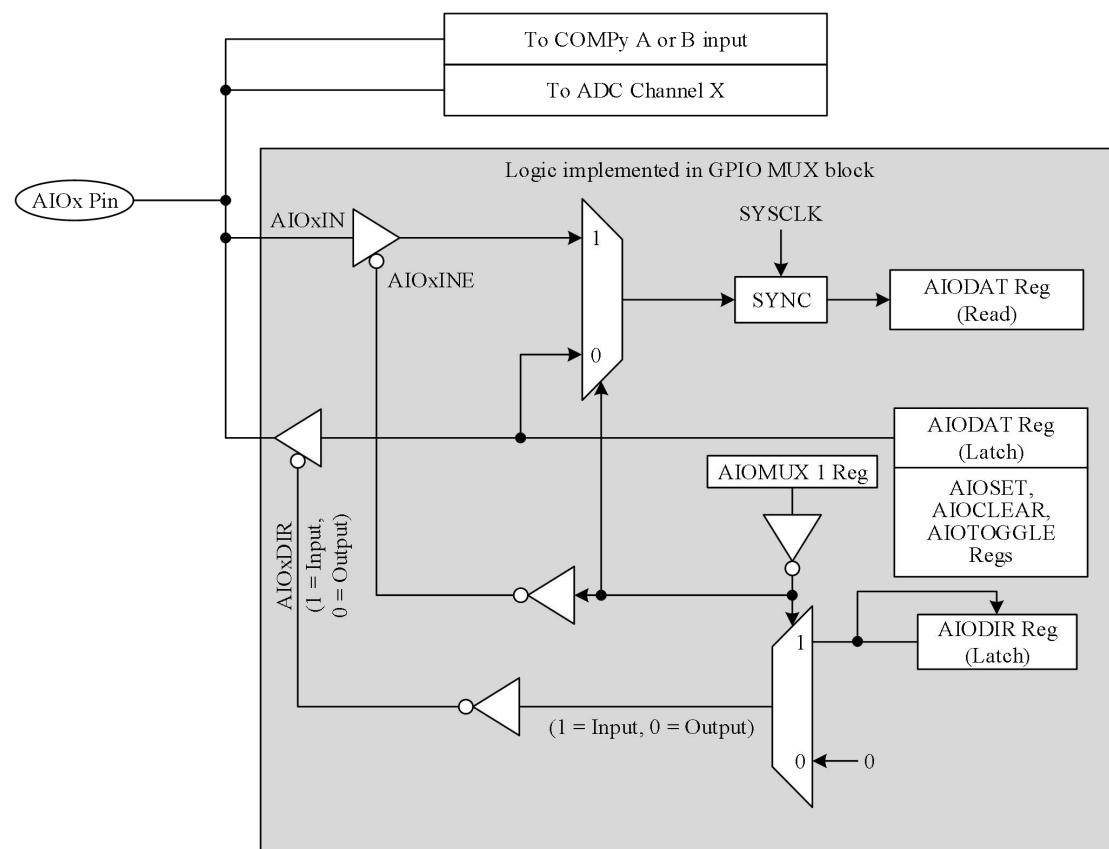

## ADC MUX 多路复选

ADC 通道和比较器功能始终可用。数字 I/O 功能仅在以下情况下可用 AIOMUX1 寄存器中的相应位为 0。在这种模式下，读取 AIODAT 寄存器反映实际的 pin 状态。

当 AIOMUX1 寄存器中的相应位为 1 时，数字 I/O 功能被禁用。在此模式下，读取 AIODAT 寄存器反映 AIODAT 寄存器的输出锁存，并且输入数字 I/O 缓冲区被禁用防止模拟信号产生噪音。

复位时，数字功能被禁用。如果引脚用作模拟输入，用户应保留 AIO 该 pin 的功能已禁用。

图 4-8 AIOx 引脚复用

## 4.1.2 比较器模块

下图显示了比较器模块与系统其余部分的交互。

图 4-9 比较器模块结构框图

表 4-2 比较器模块寄存器映射

| 名称                | 比较器 1  | 比较器 2  | EALLOW 保护 | 描述        |

|-------------------|--------|--------|-----------|-----------|

| COMPCTL           | 0xC000 | 0xC080 | 是         | 比较器控制寄存器  |

| COMPSTS           | 0xC004 | 0xC084 | 否         | 比较器状态寄存器  |

| DACCTL            | 0xC008 | 0xC088 | 否         | DAC 控制寄存器 |

| DACVAL            | 0xC00C | 0xC08C | 否         | DAC 值寄存器  |

| RAMPMAXREF_ACTIVE | 0xC010 | 0xC090 | 否         | 斜坡发生器最大值  |

| RAMPMAXREF_SHDW   | 0xC014 | 0xC094 | 否         | 参考（活动）寄存器 |

| RAMPDECVL_ACTIVE  | 0xC018 | 0xC098 | 否         | 斜坡发生器最大值  |

| RAMPDECVL_SHDW    | 0xC01C | 0xC09C | 否         | 参考（阴影）寄存器 |

| RAMPSTS           | 0xC020 | 0xC0A0 | 否         | 斜坡发生器衰减值  |

| DACEX             | 0xC024 | 0xC0A4 | 否         | （活动）寄存器   |

注释：比较器 2 仅适用于 48 针 PT 封装。

## 4.2 同步串行通信接口 (SPI) 模块

DSC280103PX 器件包括 1 个四引脚的同步串行通信接口 (SPI) 模块。SPI 是一个高速、同步串行 I/O 端口，此端口可在设定的位传输速率上将一个设定长度（1 至 16 位）的串行比特流移入和移出器件。通常，SPI 用于 DSP 和外部外设或者其它处理器之间的通信。典型应用包括外部 I/O 或者从诸如移位寄存器、显示驱动器和 ADC 等器件的外设扩展。多器件通

信由 SPI 的主控/受控操作支持。

SPI 模块的特性包括：

- 四个外部引脚：

- SPISOMI: SPI 从器件输出/主器件输入引脚

- SPISIMO: SPI 从器件输入/主器件输出引脚

- SPISTE: SPI 从器件发送使能引脚

- SPICLK: SPI 串行时钟引脚

**注释：**如果 SPI 模块未被使用，所有四个引脚可被用作 GPIO。

- 两个运行模式：主机模式和从机模式

- 波特率：共 125 个可编程的不同波特率以供使用。计算公式为：

当 SPIBRR = 3 到 127 时：

$$\text{SPI 波特率} = \frac{\text{LSPCLK}}{(\text{SPIBRR} + 1)}$$

当 SPIBRR = 0, 1, 或 2 时：

$$\text{SPI 波特率} = \frac{\text{LSPCLK}}{4}$$

其中：

LSPCLK = 设备低速外设时钟频率

SPIBRR = SPI 主机的 SPIBRR 的值

- 数据字长度：1~16 数据位

- 包括 4 种时钟模式（由时钟极性和时钟相位的位控制）：

- 无相位延迟的下降沿：SPICLK 高电平有效。SPI 在 SPICLK 信号的下降沿上发送数据，而在 SPICLK 信号的上升沿上接收数据。

- 有相位延迟的下降沿：SPICLK 高电平有效。SPI 在 SPICLK 信号下降沿的一半周期之前发送数据，而在 SPICLK 信号的下降沿上接收数据。

- 无相位延迟的上升沿：SPICLK 低电平无效。SPI 在 SPICLK 信号的上升沿上发送数据，而在 SPICLK 信号的下降沿上接收数据。

- 有相位延迟的上升沿：SPICLK 低电平无效。SPI 在 SPICLK 信号下降沿之前的半个周期发送数据，而在 SPICLK 信号的上升沿上接收数据。

- 同时接收和发送操作（发送功能可在软件中被禁用）

- 通过中断驱动或者轮询算法来完成发射器和接收器运行

- 9个 SPI 模块控制寄存器：位于控制寄存器内，帧开始地址 0xE800。

增强型特性：

- 4 级发送/接收 FIFO

- 经延迟的发送控制

- 支持双向 3 线 SPI 模式

- 借助 SPISTE 翻转的音频数据接收支持

表格 4-3 SPI-A 寄存器

| 地址      | 缩写       | 大小    | 受 EALLOW 保护 | 寄存器名称            |

|---------|----------|-------|-------------|------------------|

| 0xE800h | SPICCR   | 32bit | 否           | SPI-A 配置控制寄存器    |

| 0xE804h | SPICTL   | 32bit | 否           | SPI-A 运行控制寄存器    |

| 0xE808h | SPISTS   | 32bit | 否           | SPI-A 状态寄存器      |

| 0xE80ch | SPIBRR   | 32bit | 否           | SPI-A 波特率寄存器     |

| 0xE810h | SPIRXEMU | 32bit | 否           | SPI-A 接收仿真缓存寄存器  |

| 0xE814h | SPIRXBUF | 32bit | 否           | SPI-A 串行输入缓存寄存器  |

| 0xE818h | SPITXBUF | 32bit | 否           | SPI-A 串行输出缓存寄存器  |

| 0xE81ch | SPIDAT   | 32bit | 否           | SPI-A 串行数据寄存器    |

| 0xE820h | SPIFFTX  | 32bit | 否           | SPI-A FIFO 发送寄存器 |

| 0xE824h | SPIFFRX  | 32bit | 否           | SPI-A FIFO 接收寄存器 |

| 0xE828h | SPIFFCT  | 32bit | 否           | SPI-A FIFO 控制寄存器 |

| 0xE82ch | SPIPRI   | 32bit | 否           | SPI-A 优先级控制寄存器   |

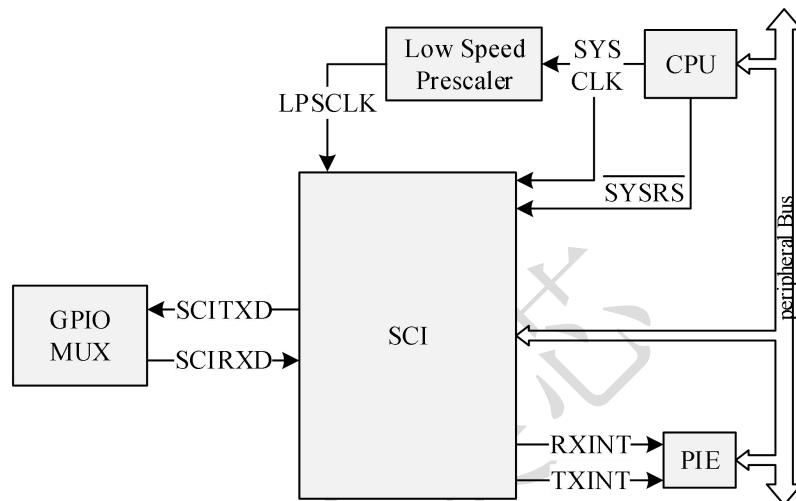

## 4.3 异步串行通信接口 (SCI) 模块

SCI 的基本功能如下：

- 对外两个数据信号与 GPIO 复用：SCITXD (Output)；SCIRXD (Input)；

- 波特率通过 16bit 寄存器可配置；

- 数据格式：start (1 bit) +data (1~8 bit 可配置) +地址数据标示 (1 bit, 仅 address mode) 奇偶位 (奇/偶/无) +结束位 (1/2 bit)

- 四种错误检测：parity, overrun, framing, 和 break detection

- 全双工和半双工

- 接收发送双缓存

- 接收发送可中断触发或者轮询状态寄存器触发

- 接收发送中断分别使能（BRKDT 除外）

- NRZ 格式传输

增强的功能：

- 硬件自动检测波特率

- 4 级接收发送 FIFO

图 4-10 SCI 连接关系图

| 理想波特率 | LSPCLK 时钟频率, 100MHz |       |      |

|-------|---------------------|-------|------|

|       | BRR                 | 实际波特率 | 误差%  |

| 2400  | 5207(1457h)         | 2400  | 0    |

| 4800  | 2603(A2Bh)          | 4800  | 0    |

| 9600  | 1301(515h)          | 9601  | 0.01 |

| 19200 | 650(28Ah)           | 19201 | 0.01 |

| 38400 | 324(144h)           | 38462 | 0.16 |

表 4-4 波特率配置

串行传输的时钟由 LSPCLK 根据 16bit 配置寄存器生成。最大比达特为 LSPCLK/16.

$$\text{BRR} = (\text{SCIHBAUD} \ll 8) + (\text{SCILBAUD})$$

$$\text{SCI Asynchronous Baud} = \text{LSPCLK} / ((\text{BRR} + 1) * 8)$$

$$\text{BRR} = \text{LSPCLK} / (\text{SCI Asynchronous Baud} * 8) - 1, \quad 0 < \text{BRR} < 65536$$

$$\text{BRR}=0 \text{ 时, } \text{SCI Asynchronous Baud} = \text{LSPCLK} / 16$$

表 4-5 SCI-A 寄存器

| 名称      | 地址      | 大小 (x32) | 说明            |

|---------|---------|----------|---------------|

| SCICCR  | 0xE000h | 1        | SCI-A 通信控制寄存器 |

| SCICTL1 | 0xE004h | 1        | SCI-A 控制寄存器 1 |

| 名称       | 地址      | 大小 (x32) | 说明               |

|----------|---------|----------|------------------|

| SCIHBaud | 0xE008h | 1        | SCI-A 波特率寄存器高位   |

| SCILBAUD | 0xE00Ch | 1        | SCI-A 波特率寄存器低位   |

| SCICTL2  | 0xE010h | 1        | SCI-A 控制寄存器 2    |

| SCIRXST  | 0xE014h | 1        | SCI-A 接收状态寄存器    |

| SCITXEMU | 0xE018h | 1        | SCI-A 模拟缓冲寄存器    |

| SCIRXBDF | 0xE01Ch | 1        | SCI-A 数据接收缓冲器    |

| SCITXBDF | 0xE020h | 1        | SCI-A 数据传输寄存器    |

| SCIFFTX  | 0xE024h | 1        | SCI-A FIFO 发送寄存器 |

| SCIFFRX  | 0xE028h | 1        | SCI-A FIFO 接收寄存器 |

| SCIFFCT  | 0xE02Ch | 1        | SCI-A FIFO 控制寄存器 |

| SCIPRI   | 0xE030h | 1        | SCI-A 优先级寄存器     |

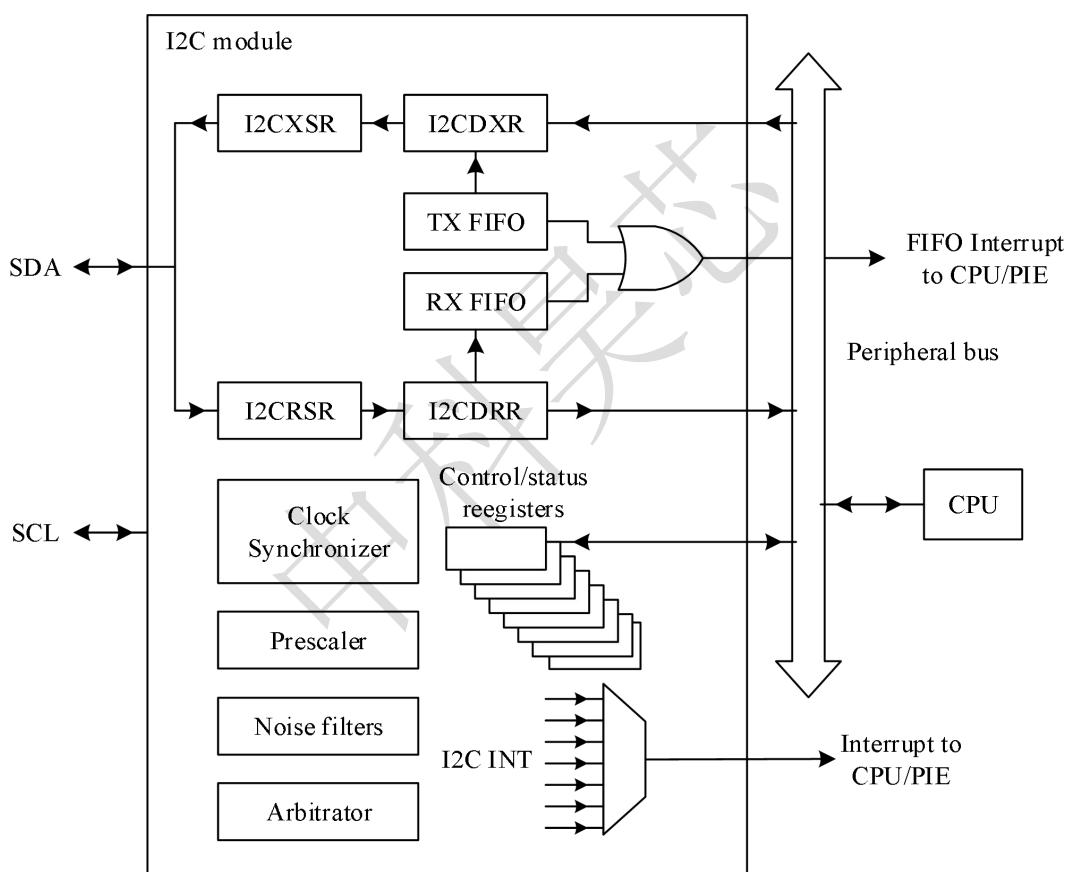

## 4.4 内部集成电路接口 (I2C) 模块

I2C 主要功能如下:

- 兼容 NXP I2C 标准规范 v2.1:

- 支持 8bit (1~7) 字节传输

- 支持 7 位寻址和 10 位寻址

- 支持广播

- 支持 START 模式

- 支持多主机-发送器和从机-接收器模式

- 支持多从机-发送器和主机-接收器模式

- 支持主机-发送/接受和从机-接受/发送的组合

- 速率 10kbps~400kbps (快速)

- 支持 4 X 16bit 接收和发送 FIFO

- 支持两个中断:

- I2C 中断 (接收数据 ready; 发送数据 ready; 寄存器访问 ready; 未收到 ACK; 仲裁失败; 检测到停止位; 从机被寻址)

- I2C FIFO 中断 (发送 FIFO 中断; 接收 FIFO 中断)

- 模块使能和禁止

- 支持自由数据传输模式

不支持的功能有:

- 高速模式

- CBUS 模式

### I2C 模块结构:

- 串行数据接口: SDA 和 SCL;

- 数据寄存器和数据 FIFO, 用于缓存 SDA 与 CPU 之间的数据;

- 控制和状态寄存器;

- 配置总线接口, 用于 CPU 配置 I2C 寄存器和 FIFO;

- 噪音滤波器, 过滤 SDA 和 SCL 噪声;

- 仲裁器;

- FIFO 中断产生逻辑;

图 4-11 I2C 模块结构图

表 4-6 IIC 模块寄存器映射

| 相对位移    | 名称      | 说明                 |

|---------|---------|--------------------|

| 0xE400h | I2COAR  | I2C 自有地址寄存器        |

| 0xE404h | I2CIER  | I2c 中断寄存器          |

| 0xE408h | I2CSTR  | I2c 状态寄存器          |

| 0xE40Ch | I2CCLKL | I2C 时钟分频器低 32 位寄存器 |

| 0xE410h | I2CCLKH | I2C 时钟分频器高 32 位寄存器 |

| 0xE414h | I2CCNT  | I2C 数据计数器寄存器       |

| 相对位移    | 名称      | 说明             |

|---------|---------|----------------|

| 0xE418h | I2CDRR  | I2C 数据接收寄存器    |

| 0xE41Ch | I2CSAR  | I2C 从机地址寄存器    |

| 0xE420h | I2CDXR  | I2C 数据传输寄存器    |

| 0xE424h | I2CMDR  | I2C 模式寄存器      |

| 0xE428h | I2CISRC | I2C 中断源寄存器     |

| 0xE42Ch | I2CEMDR | I2C 扩展模式寄存器    |

| 0xE430h | I2CPSC  | I2C 预分频寄存器     |

| 0xE434h | I2CFFTX | I2C FIFO 传输寄存器 |

| 0xE438h | I2CFFRX | I2C FIFO 接收寄存器 |

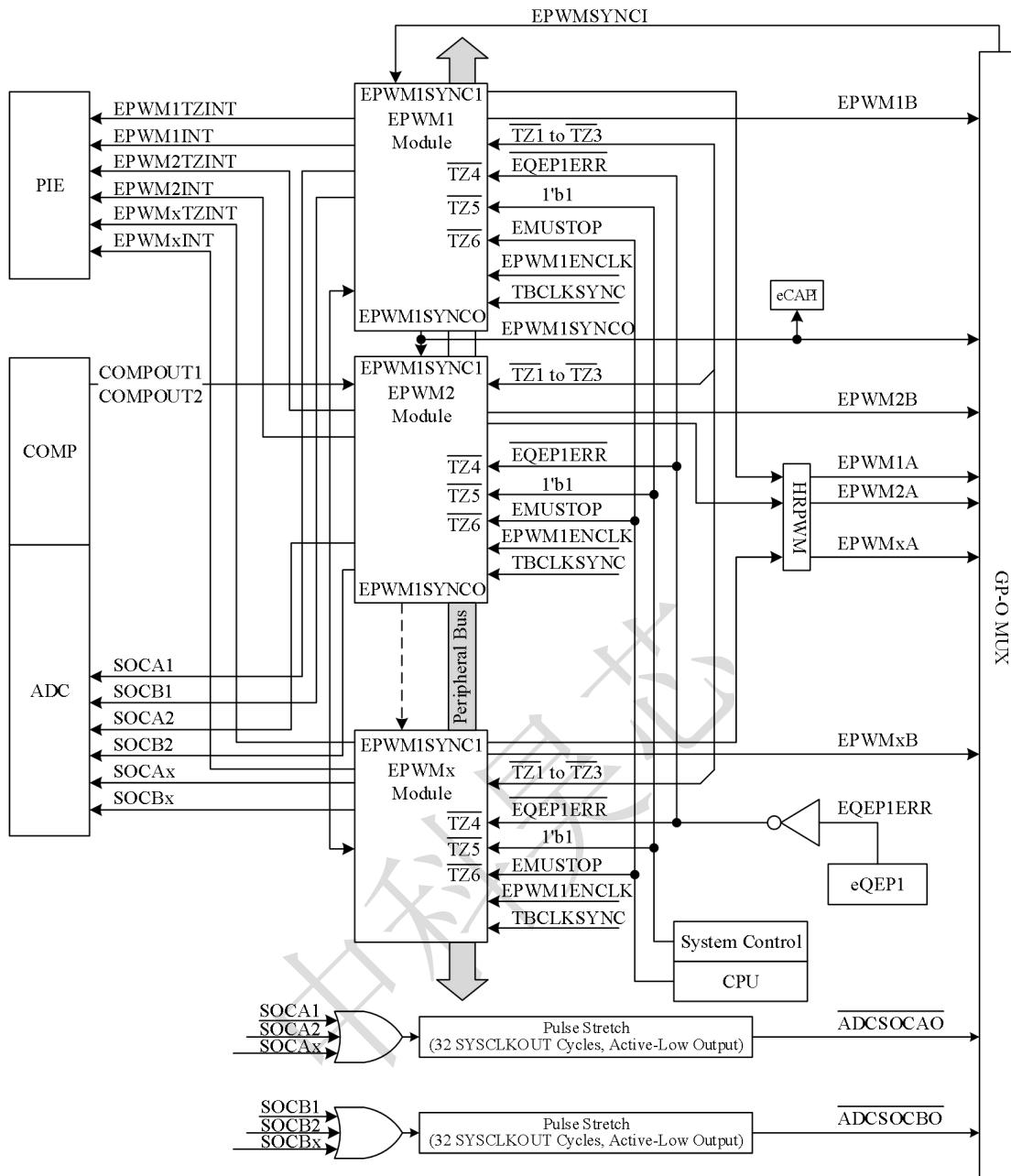

## 4. 5 增强型 PWM 模块 (ePWM1/2/3/4)

DSC280103PX 器件包括 4 路增强 PWM 模块每个 ePWM 模块支持：

- 专用 16 位 time-base 计数器，周期和频率可控；

- 每个 ePWM 模块有两个 PWM 输出 (EPWMxA, EPWMxB)，可配置为：

- 两个独立的单沿 PWM

- 两个独立的双沿对称 PWM

- 一个独立的双沿非对称 PWM

- 通过软件异步改写 PWM 信号。

- 相对于其他 ePWM 模块，可以编程对相位进行控制，从而支持滞后或超前操作。

- 逐周期地进行相位同步。

- 对上升沿和下降沿可以独立控制延迟，产生死区 (Dead Band)。

- 故障发生时，可以编程控制进行逐周期 (cycle-by-cycle) 或一次触发 (one-shot) 跳闸 (trip)。

- 跳闸能够强制 PWM 输出为高，低或高阻状态。

- 比较器模块的输出和跳闸区域的输入可以生成事件，已过滤的事件或跳闸条件。

- 所有事件都可以触发 CPU 中断和 ADC 开始转换 Start Of Conversion, SOC

- 可编程的事件预分频可最大程度地减少中断对 CPU 开销。

- 通过高频载波信号对 PWM 进行斩波。

多个 ePWM 模块通过时钟信号连接起来，通过同步机制使得多个 ePWM 模块在需要时，能够作为一个系统协同工作。另外，这种同步机制可以扩展到 eCAP 模块。模块也可以单独 (stand-alone) 运行。

图 4-12 ePWM 结构图

表 4-7 ePWM 模块寄存器映射

| 名称     | ePWM1  | ePWM2  | ePWM3  | ePWM4  | 说明             |

|--------|--------|--------|--------|--------|----------------|

| TBCTL  | 0xB000 | 0xB400 | 0xB800 | 0xBC00 | 时基控制寄存器        |

| TBSTS  | 0xB004 | 0xB404 | 0xB804 | 0xBC04 | 时基状态寄存器        |

| TBPHS  | 0xB008 | 0xB408 | 0xB808 | 0xBC08 | 时基相位寄存器        |

| TBCTR  | 0xB010 | 0xB410 | 0xB810 | 0xBC10 | 时基计数器寄存器       |

| TBPRD  | 0xB014 | 0xB414 | 0xB814 | 0xBC14 | 时基周期寄存器集       |

| CMPCTL | 0xB01C | 0xB41C | 0xB81C | 0xBC1C | 时基周期高分辨率寄存器    |

| CMPA   | 0xB020 | 0xB420 | 0xB820 | 0xBC20 | 计数器比较控制寄存器     |

| CMPB   | 0xB028 | 0xB428 | 0xB828 | 0xBC28 | 时基比较 HRPWM 寄存器 |

| CMPAM  | 0xB0B0 | 0xB4B0 | 0xB8B0 | 0xBCB0 | 计数器比较寄存器集      |

| 名称           | ePWM1  | ePWM2  | ePWM3  | ePWM4  | 说明                 |

|--------------|--------|--------|--------|--------|--------------------|

| AQCTLA       | 0xB02C | 0xB42C | 0xB82C | 0xBC2C | 计数器比较 B 寄存器集       |

| AQCTLB       | 0xB030 | 0xB430 | 0xB830 | 0xBC30 | Output 的操作限定符控制寄存器 |

| AQSFRC       | 0xB034 | 0xB434 | 0xB834 | 0xBC34 | Output 的操作限定符控制寄存器 |

| AQCSFRC      | 0xB038 | 0xB438 | 0xB838 | 0xBC38 | 动作限定符软件强制寄存器       |

| DBCTL        | 0xB03C | 0xB43C | 0xB83C | 0xBC3C | 死区发生器控制寄存器         |

| DBRED        | 0xB040 | 0xB440 | 0xB840 | 0xBC40 | 死区发生器上升沿延迟计数寄存器    |

| DBFED        | 0xB044 | 0xB444 | 0xB844 | 0xBC44 | 死区发生器下降沿延迟计数寄存器    |

| TZSEL        | 0xB048 | 0xB448 | 0xB848 | 0xBC48 | 跳闸区选择寄存器           |

| TZDCSEL      | 0xB04C | 0xB44C | 0xB84C | 0xBC4C | 跳闸区数字比较寄存器         |

| TZCTL        | 0xB050 | 0xB450 | 0xB850 | 0xBC50 | 跳闸区控制寄存器           |

| TZEINT       | 0xB054 | 0xB454 | 0xB854 | 0xBC54 | 跳闸区启用中断寄存器         |

| TZFLG        | 0xB058 | 0xB458 | 0xB858 | 0xBC58 | 跳闸区标志寄存器           |

| TZCLR        | 0xB05C | 0xB45C | 0xB85C | 0xBC5C | 跳闸区清除寄存器           |

| TZFRC        | 0xB060 | 0xB460 | 0xB860 | 0xBC60 | 跳闸区力寄存器            |

| ETSEL        | 0xB064 | 0xB464 | 0xB864 | 0xBC64 | 事件触发器选择寄存器         |

| ETPS         | 0xB068 | 0xB468 | 0xB868 | 0xBC68 | 事件触发器预刻度寄存器        |

| ETFLG        | 0xB06C | 0xB46C | 0xB86C | 0xBC6C | 事件触发标志寄存器          |

| ETCLR        | 0xB070 | 0xB470 | 0xB870 | 0xBC70 | 事件触发器清除寄存器         |

| ETFRC        | 0xB074 | 0xB474 | 0xB874 | 0xBC74 | 事件触发力寄存器           |

| PCCTL        | 0xB078 | 0xB478 | 0xB878 | 0xBC78 | PWM 斩波器控制寄存器       |

| HRCNFG       | 0xB080 | 0xB480 | 0xB880 | 0xBC80 | HRPWM 配置寄存器        |

| HRPWR        | 0xB084 | 0xB484 | 0xB884 | 0xBC84 | HRPWM 功耗寄存器        |

| HRMSTEP      | 0xB098 | 0xB498 | 0xB898 | 0xBC98 | HRPWM MEP 步进寄存器    |

| HRPCTL       | 0xB0A0 | 0xB4A0 | 0xB8A0 | 0xBCA0 | 高精度周期控制寄存器         |

| TBPRDHIRM    | 0xB0A8 | 0xB4A8 | 0xB8A8 | 0xBCA8 | HRPWM 周期镜像寄存器      |

| TBPRDMM      | 0xB0AC | 0xB4AC | 0xB8AC | 0xBCAC | 时机周期镜像寄存器          |

| CMPAHRM      | 0xB0B0 | 0xB4B0 | 0xB8B0 | 0xBCB0 | 高精度比较 A 镜像寄存器      |

| CMPAM        | 0xB0B4 | 0xB4B4 | 0xB8B4 | 0xBCB4 | 比较 A 镜像寄存器         |

| DCTRIPSEL    | 0xB0C0 | 0xB4C0 | 0xB8C0 | 0xBCC0 | 数字比较跳闸选择寄存器        |

| DCACTL       | 0xB0C4 | 0xB4C4 | 0xB8C4 | 0xBCC4 | 数字比较控制寄存器          |

| DCBCTL       | 0xB0C8 | 0xB4C8 | 0xB8C8 | 0xBCC8 | 数字比较 B 控制寄存器       |

| DCFCTL       | 0xB0CC | 0xB4CC | 0xB8CC | 0xB8CC | 数字比较滤波器控制寄存器       |

| DCCAPCTL     | 0xB0D0 | 0xB4D0 | 0xB8D0 | 0xBCD0 | 数字比较跳闸选择寄存器        |

| DCFOFFSET    | 0xB0D4 | 0xB4D4 | 0xB8D4 | 0xBCD4 | 数字比较捕获控制寄存器        |

| DCFOFFSETCNT | 0xB0D8 | 0xB4D8 | 0xB8D8 | 0xBCD8 | 数字比较滤波器偏移寄存器       |

| DCFWINDOW    | 0xB0DC | 0xB4DC | 0xB8DC | 0xBCDC | 数字比较滤波器偏移计数器寄存器    |

| DCFWINDOWCNT | 0xB0E0 | 0xB4E0 | 0xB8E0 | 0xBCE0 | 数字比较滤波器窗口寄存器       |

| DCCAP        | 0xB0E4 | 0xB4E4 | 0xB8E4 | 0xBCE4 | 数字比较滤波器窗口计数器寄存器    |

## 4.6 高分辨率 PWM 模块 (HRPWM)

该模块将多条延迟线组合在一个模块中，并使用一个简化的校准系统专用校准延迟链。每个 ePWM 模块有一条 HR 延迟链。

HRPWM 模块提供的 PWM 分辨率（时间粒度）明显优于现有的分辨率采用传统的数字 PWM 方法实现。HRPWM 模块的要点是：

- 显著扩展了传统衍生数字 PWM 的时间分辨率能力

- 此功能既可用于单边（占空比和相移控制）也可用于双边频率/周期调制的边缘控制。

- 更精细的时间粒度控制或边缘定位是通过对 CMPA 以及 ePWM 模块的相位寄存器的扩展来控制的。

- 在特定设备上可用时，HRPWM 功能仅在设备的 a 信号路径上提供（即，在 EPWMxA 输出上）。EPWMxB 输出具有传统的 PWM 功能。

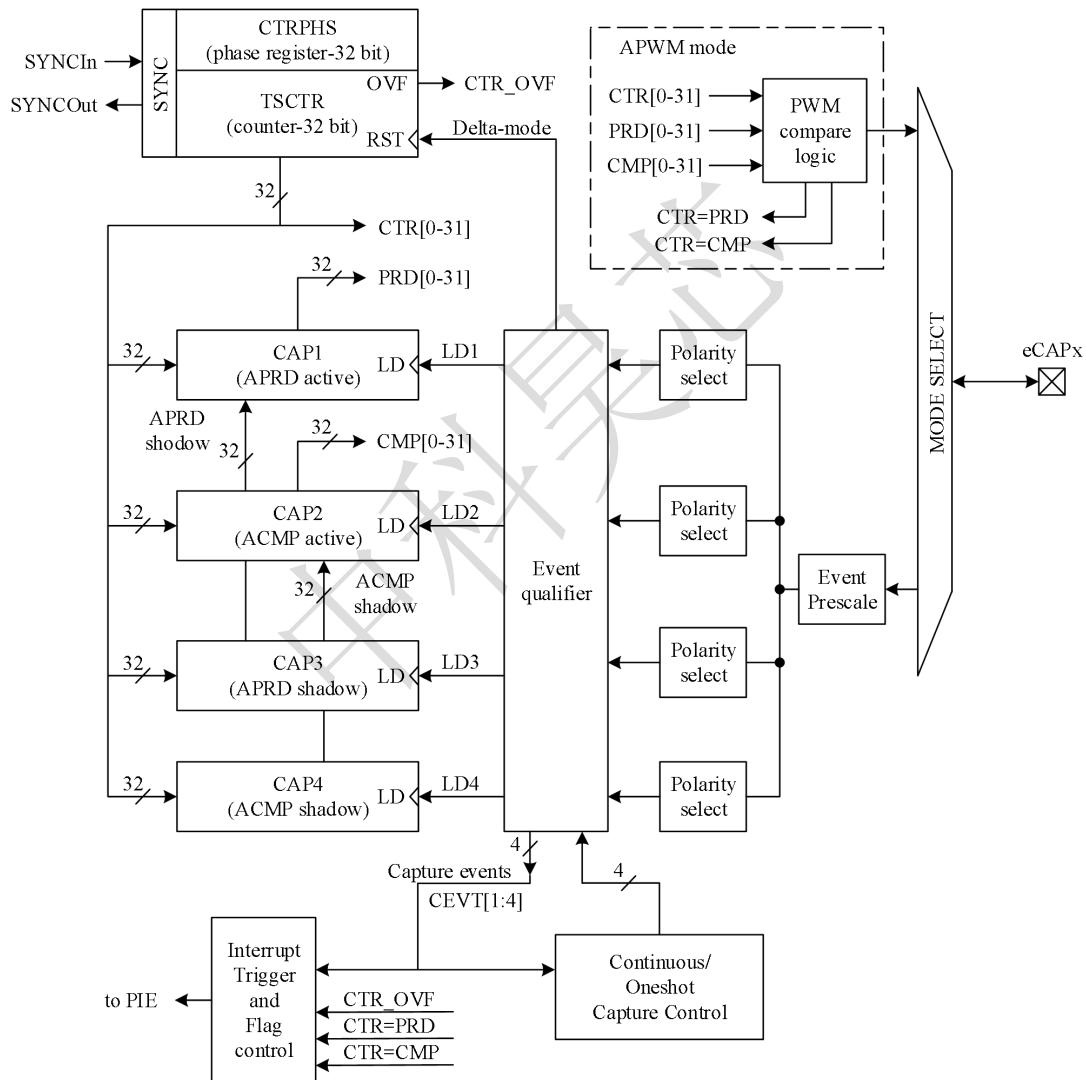

## 4.7 增强型脉冲捕获模块 (eCAP)

eCAP 包含以下功能：

- 4 个 32bit 事件捕获寄存器；

- 可选择 4 个沿触发采集事件；

- 每个采集事件可触发中断；

- 最大支持 4 个事件的单发射捕获；

- 支持 4 深度缓存的循环模式捕获；

- 绝对时间捕获；

- 差分模式捕获；

- 1 个信号输入；

- 不工作在捕获模式时，可配置为单通道 PWM 输出；

eCAP 主要包括以下资源：

- 专用信号输入；

- 32bit 计数器；

- 4 × 32bit 捕获器；

- 4 级序列发生器 (mod4) , 与外部序列沿同步;

- 4 个捕获事件均可独立选择上下沿触发;

- 信号输入可做 2~62 预分频;

- 通过单发射寄存器在 1~4 捕获事件后停止捕获;

- 通过 4 个 CAP 寄存器实现连续捕获;

- 四个捕获事件均可触发中断;

eCAP 可配置为捕获模式或者 APWM 模式，APWM 模式下，cap1、cap2 分配为周期寄存器和比较寄存器，cap3 和 cap4 是其 shadow 寄存器。

图 4-13 eCAP 功能结构图

表 4-8 eCAP 模块寄存器映射

| 地址偏移    | 寄存器    | 描述          |

|---------|--------|-------------|

| 0xD000h | TSCTR  | ECAP 时基计数器  |

| 0xD004h | CTRPHS | 计数器相位偏移值寄存器 |

| 地址偏移    | 寄存器    | 描述          |

|---------|--------|-------------|

| 0xD008h | CAP1   | CAP 寄存器 1   |

| 0xD00Ch | CAP2   | CAP 寄存器 2   |

| 0xD010h | CAP3   | CAP 寄存器 3   |

| 0xD014h | CAP4   | CAP 寄存器 4   |

| 0xD018h | ECCTL1 | CAP 控制寄存器 1 |

| 0xD01Ch | ECCTL2 | CAP 控制寄存器 2 |

| 0xD020h | ECEINT | CAP 中断使能寄存器 |

| 0xD024h | ECFLG  | CAP 中断标志寄存器 |

| 0xD028h | ECCLR  | CAP 中断清除器   |

| 0xD02Ch | ECFRC  | CAP 中断强制寄存器 |

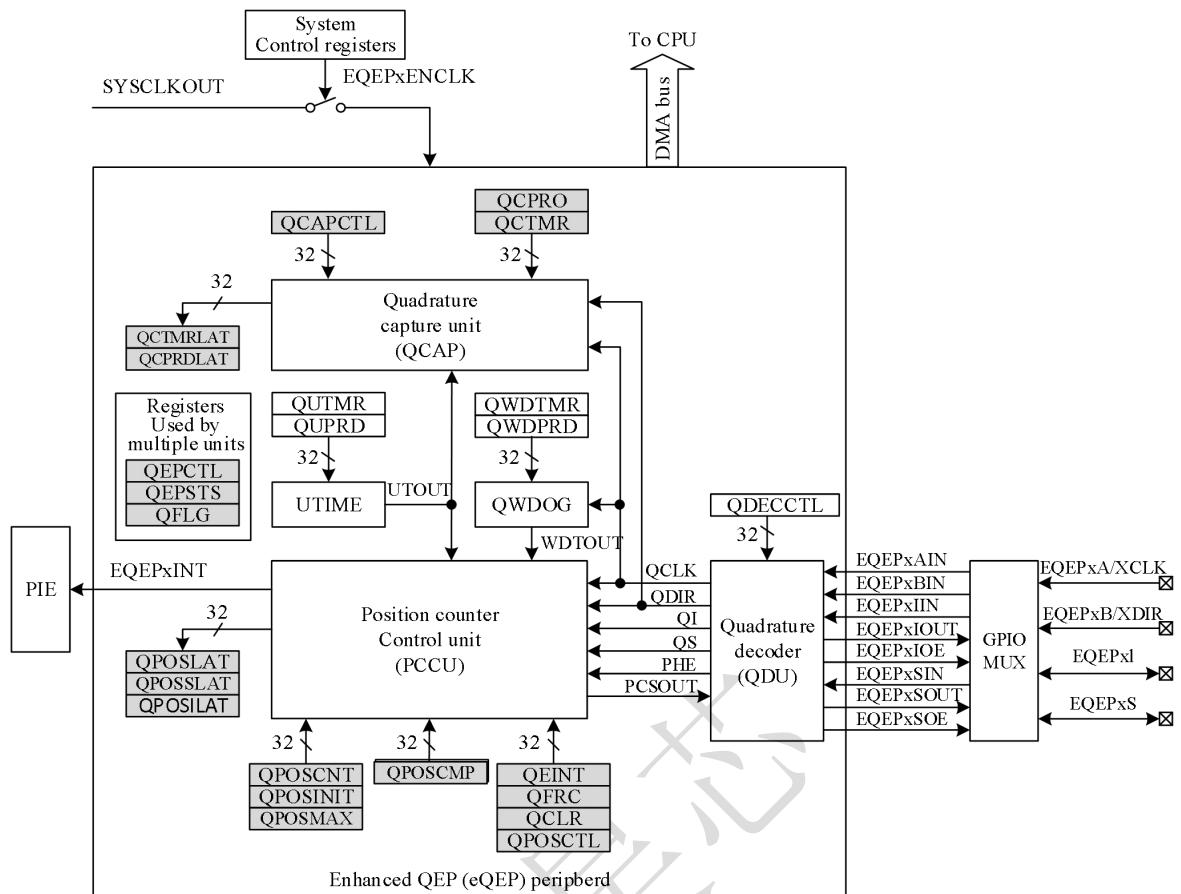

## 4.8 增强型正交编码器模块 (eQEP)

eQEP 主要功能单元有：

- GPIO MUX: 选择端口信号（由 GPIO 实现）；

- QDU: 正交解码器；

- PCCU: 用于位置测量的位置计数器和控制单元；

- QCAP: 用于低速测量的正交边沿捕获单元；

- UTIME: 用于测量速度或者频率的单位时间单元；

- QWDOG: 用于停止检测的看门狗；

图 4-14 eQEP 结构图

表 4-9 eQEP 模块寄存器映射

| 偏移      | 名称       | 描述                                                                                                                                                                 |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0xD400h | QPOSCNT  | 位置计数器, 32bit, 可读写, SYSRSn 下复位位 0h, 在 eqep 脉冲沿根据方向进行增计数/减计数, 表示运动的位置, 计数时该寄存器只读, 推荐在初始化时写该寄存器, QEPCTL 内的 QOPEN=0 时, 位置寄存器 Disable, 反之位置寄存器使能, 使能时向该寄存器写可能引发不可预知的问题。 |

| 0xD404h | QPOSINIT | 位置计数器初始化寄存器, 32bit, 可读写, SYSRSn 下复位位 0h, 用于存放选通 (strobe)、索引 (index)、软件初始化位置寄存器的值。                                                                                  |

| 0xD408h | QPOSMAX  | 最大位置计数寄存器, 32bit, 可读写, SYSRSn 下复位位 0h, 用于存放计数寄存器的最大值。                                                                                                              |

| 0xD40Ch | QPOSCMP  | 位置比较寄存器, 32bit, 可读写, SYSRSn 下复位位 0h, 与位置计数器的值进行比较, 匹配时产生同步输出或者中断                                                                                                   |

| 偏移      | 名称       | 描述                                                                                                                                                                                                            |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0xD410h | QPOSILAT | 索引位置锁存寄存器, 32bit, 只读, SYSRSn 下复位位 0h, 根据 QEPCTL 内 IEL 定义, 在索引 (index) 事件发生时将位置计数器的值锁存在此寄存器。                                                                                                                   |

| 0xD414h | QPOSSLAT | 选通位置锁存寄存器, 32bit, 只读, SYSRSn 下复位位 0h, 根据 QEPCTL 内 SEL 定义, 在选通 (strobe) 事件发生时, 将位置计数器的值锁存到该寄存器。                                                                                                                |

| 0xD418h | QOSLAT   | 位置计数器锁存寄存器, 32bit, 只读, SYSRSn 下复位位 0h, 在单位事件超时事件发生时, 将位置计数器的值锁存于此寄存器。                                                                                                                                         |

| 0xD41Ch | QUTMR    | 单位定时器寄存器, 32bit, 可读写, SYSRSn 下复位位 0h, 为单位事件产生提供基准, 当其值与单位周期值匹配时, 产生单位时间事件。                                                                                                                                    |

| 0xD420h | QUPRD    | 单位周期寄存器, 32bit, 可读写, SYSRSn 下复位位 0h, 为单位定时器提供周期值, 用于周期性的产生单位事件, 周期性的锁存位置信息, 并产生中断。                                                                                                                            |

| 0xD424h | QWDTMR   | 看门狗定时器寄存器, 16bit, 可读写, SYSRSn 下复位位 0h, 为看门狗提供时间基准检测电机是否停转, 当其值与看门狗周期值匹配时, 产生看门狗超时中断, 该寄存器在正交时钟边沿跳变时复位。                                                                                                        |

| 0xD428h | QWDPRD   | 看门狗周期寄存器, 16bit, 可读写, SYSRSn 下复位位 0h, 存放看门狗周期值, 用于产生看门狗超时中断。                                                                                                                                                  |

| 0xD42Ch | QDECCTL  | 编码控制器                                                                                                                                                                                                         |

| 0xD430h | QEPCCTL  | 控制寄存器, 详见本章第二节                                                                                                                                                                                                |

| 0xD434h | QCAPCTL  | 捕获控制寄存器, 详见本章第三节                                                                                                                                                                                              |

| 0xD438h | QPOSCTL  | 位置比较控制寄存器, 详见本章第四节                                                                                                                                                                                            |

| 0xD43Ch | QEINT    | 中断使能寄存器, Bit15:12, bit0 只读为 0, Bit11-1 分别为 UTO (单元事件超时)、IEL (index 事件锁存)、SEL (strobe 事件锁存)、PCM (位置比较匹配中断)、PCR (位置比较备好)、PCO (位置计数器上溢)、PCU (位置计数器下溢出)、WTO (看门狗超时)、QDC (正交方向转向)、PHE (正交相位错误)、PCE (位置计数器错误) 等中断使能 |

| 0xD440h | QFLG     | 中断标志寄存器, Bit15:12 只读为 0, Bit11:0 分别为 UTO (单元事件超时)、IEL (index 事件锁存)、SEL (strobe 事件锁存)、PCM                                                                                                                      |

| 偏移      | 名称       | 描述                                                                                                         |

|---------|----------|------------------------------------------------------------------------------------------------------------|

|         |          | (位置比较匹配中断)、PCR(位置比较备好)、PCO(位置计数器上溢)、PCU(位置计数器下溢出)、WTO(看门狗超时)、QDC(正交方向转向)、PHE(正交相位错误)、PCE(位置计数器错误)、INT等中断使能 |

| 0xD444h | QCLR     | 中断清除寄存器，对应中断清零                                                                                             |

| 0xD448h | QFRC     | 中断强制寄存器，对应中断强制为1                                                                                           |

| 0xD44Ch | QEPOSTS  | 状态寄存器，详见本章第五节                                                                                              |

| 0xD450h | QCTMR    | 捕获计时器，16bit，可读写，SYSRSn复位为0，为沿捕获单元提供时间基准                                                                    |

| 0xD454h | QCPRD    | 捕获周期寄存器，16bit，可读写，SYSRSn复位为0，在两个连续的eqep位置事件之间，保存捕获周期计数值                                                    |

| 0xD458h | QCTMRLAT | 捕获定时器锁存寄存器，16bit，可读写，SYSRSn复位为0，发生单位事件超时事件或者读取位置计数器时，将捕获计数器的值锁存在此寄存器中                                      |

| 0xD45Ch | QCPRDLAT | 捕获周期锁存寄存器，16bit，可读写，SYSRSn复位为0，发生单位时间超时事件或者读取位置计数器时，将捕获周期锁存在此寄存器中                                          |

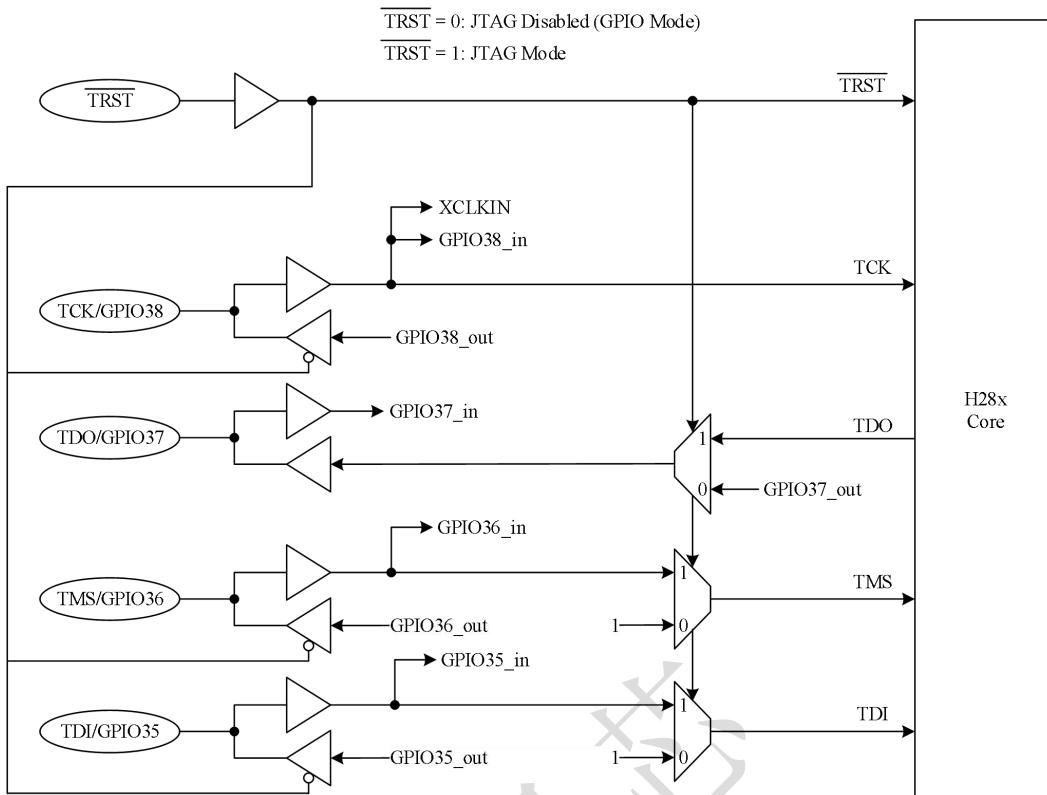

## 4. 9 JTAG 端口

JTAG 有 5 个端口：TRST，TCK，TDI，TMS，TDO，其中 TCK，TDI，TMS 及 TDO 同时作为 GPIO 端口，TRST 选择要么作为 JTAG 端口要么作为 GPIO 端口，如图 4-15 所示。

图 4-15 JTAG 端口多路复用示意图

注意：JTAG 端口也可以作为 GPIO 端口，在板级设计时，需注意连接这些端口的电路不能影响 JTAG 仿真，不能影响仿真器驱动这些端口进行调试。

TRST 信号结合 JTAG DEBUG 寄存器内的 JTAGDIS 位选择 JTAG 的功能。

| TRST | JTAGDIS bit | JTAG 端口模式                    |

|------|-------------|------------------------------|

| 0    | X           | GPIO 模式使能,JTAG 端口禁止          |

| 1    | 0           | JTAG 端口使能<br>(GPIOs 应当配置为输入) |

| 1    | 1           | GPIO 模式使能, JTAG 端口禁止         |

其中 JTAG DEBUG 寄存器地址为 0xDC44，受 EALLOW 保护。

JTAG DEBUG 寄存器位宽 16bits, bit[15:1]保留只读为 0, bit0 为 JTAGDIS- JTAG disable bit, 0- JTAG enable, 1- JTAG disable, 当 JTAG disable 时，JTAG 端口可用于 GPIO 功能，当 TRST=0 时，JTAGDIS 被复位为 0，当 TRST=1 时，可以通过 CPU 配置 JTAGDIS。

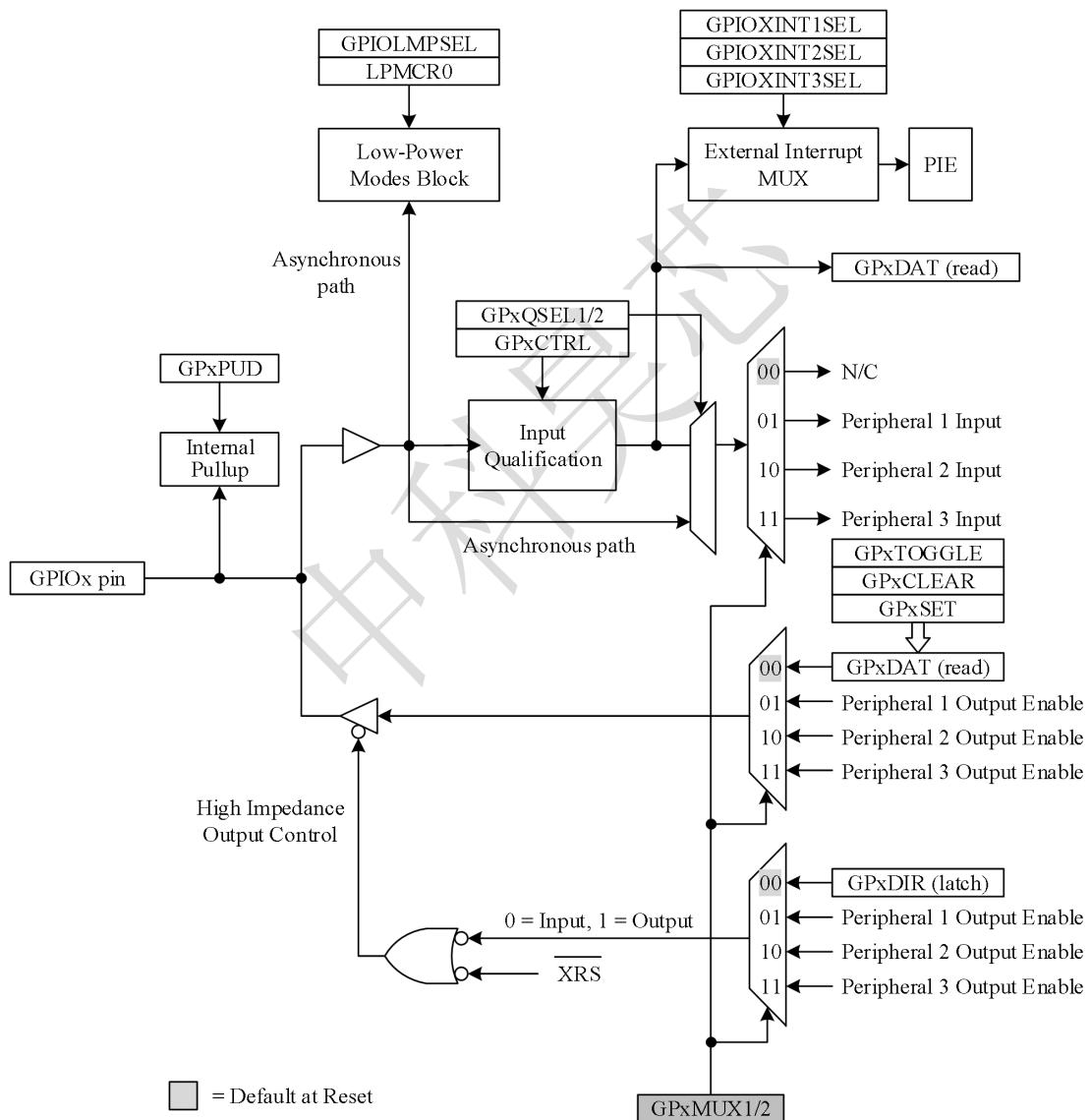

## 4. 10 GPIO 控制寄存器

GPIO 可以复用于片内的外设，并具有上下拉控制、输入信号滤波等功能。

### GPIO MUX 寄存器

表 4-10 GPIO 寄存器映射及说明

| 名称                             | 地址     | 描述                                |

|--------------------------------|--------|-----------------------------------|

| GPIO 控制寄存器 (EALLOW 保护)         |        |                                   |

| GPACTRL                        | 0xD810 | GPIO A 控制寄存器 (GPIO0 到 31)         |

| GPAQSEL1                       | 0xD818 | GPIO A 限定符选择 1 寄存器 (GPIO0 到 15)   |

| GPAQSEL2                       | 0xD81C | GPIO A 限定符选择 2 寄存器 (GPIO16 到 31)  |

| GPAMUX1                        | 0xD800 | GPIO A MUX 1 寄存器 (GPIO0 到 15)     |

| GPAMUX2                        | 0xD804 | GPIO A MUX 2 寄存器 (GPIO0 到 15)     |

| GPADIR                         | 0xD824 | GPIOA 方向寄存器 (GPIO0 到 31)          |

| GPAPUD                         | 0xD830 | GPIO A 上拉禁用寄存器 (GPIO0 到 31)       |

| GPBCTRL                        | 0xD814 | GPIO B 控制寄存器 (GPIO32 到 38)        |

| GPBQSEL1                       | 0xD820 | GPIO B 限定符选择 1 寄存器 (GPIO32 到 38)  |

| GPBMUX1                        | 0xD808 | GPIO B MUX 1 寄存器 (GPIO32 到 38)    |

| GPBDIR                         | 0xD828 | GPIO B 方向寄存器 (GPIO32 到 38)        |

| GPBPUD                         | 0xD834 | GPIO B 上拉禁用寄存器 (GPIO32 到 38)      |

| AIOMUX1                        | 0xD80C | 模拟, I/O mux 1 寄存器 (AI00 到 AI015)  |

| AIODIR                         | 0xD82C | 模拟, I/O 方向寄存器 (AI00 到 AI015)      |

| GPIO 数据寄存器 (非 EALLOW 保护)       |        |                                   |

| GPADAT                         | 0xD838 | GPIO A 数据寄存器 (GPIO0 到 31)         |

| GPASET                         | 0xD844 | GPIO A 数据置位寄存器 (GPIO0 到 31)       |

| GPACLEAR                       | 0xD848 | GPIO A 数据清除寄存器 (GPIO0 到 31)       |

| GPATOGGLE                      | 0xD84C | GPIO A 数据翻转寄存器 (GPIO0 到 31)       |

| GPBDAT                         | 0xD83C | GPIO B 数据寄存器 (GPIO32 到 38)        |

| GPBSET                         | 0xD850 | GPIO B 数据置位寄存器 (GPIO32 到 38)      |

| GPBCLEAR                       | 0xD854 | GPIO B 数据清除寄存器 (GPIO32 到 38)      |

| GPBToggle                      | 0xD858 | GPIO B 数据翻转寄存器 (GPIO32 到 38)      |

| AIODAT                         | 0xD840 | 模拟 I/O 数据寄存器 (AI00 到 AI015)       |

| AIOSET                         | 0xD85C | 模拟 I/O 数据置位寄存器 (AI00 到 AI015)     |

| AIOCLEAR                       | 0xD860 | 模拟 I/O 数据清除寄存器 (AI00 到 AI015)     |

| AIOTOGGLE                      | 0xD864 | 模拟 I/O 数据翻转寄存器 (AI00 到 AI015)     |

| GPIO 中断和低功耗模式选择寄存器 (EALLOW 保护) |        |                                   |

| GPIOXINT1SEL                   | 0xD868 | XINT1 GPIO 输入选择寄存器 (GPIO0 到 31)   |

| GPIOXINT2SEL                   | 0xD86C | XINT2 GPIO 输入选择寄存器 (GPIO0 到 31)   |

| GPIOXINT3SEL                   | 0xD870 | XINT3 GPIO 输入选择寄存器 (GPIO0 到 31)   |

| GPIOLOPMSEL                    | 0xD874 | LPM GPIO 选择寄存器 (GPIO0 到 31)       |

| GPIOGPDS                       | 0xD878 | GPIO 驱动电流控制寄存器 (GPIO0 到 31) (ECD) |

**GPIOA MUX 选择**

|           | 复位默认功能        | 外设 1            | 外设 2          | 外设 3          |

|-----------|---------------|-----------------|---------------|---------------|

| GPAMUX1 位 | GPAMUX1=00    | GPAMUX1=01      | GPAMUX1=10    | GPAMUX1=11    |

| 1-0       | GPIO0         | EPWM1A (0)      | Reserved      | Reserved      |

| 3-2       | GPIO1         | EPWM1B (0)      | Reserved      | COMP1OUT (0)  |

| 5-4       | GPIO2         | EPWM2A (0)      | Reserved      | Reserved      |

| 7-6       | GPIO3         | EPWM2B (0)      | Reserved      | COMP2OUT (0)  |

| 9-8       | GPIO4         | EPWM3A (0)      | Reserved      | Reserved      |

| 11-10     | GPIO5         | EPWM3B (0)      | Reserved      | ECAP1 (I/O)   |

| 13-12     | GPIO6         | EPWM4A (0)      | EPWMSYNC1 (I) | EPWMSYNC0 (0) |

| 15-14     | GPIO7         | EPWM4B (0)      | SCIRXDA (I)   | EQEPB (ECD)   |

| 17-16     | Reserved      | Reserved        | Reserved      | Reserved      |

| 19-18     | Reserved      | Reserved        | Reserved      | Reserved      |

| 21-20     | Reserved      | Reserved        | Reserved      | Reserved      |

| 23-22     | Reserved      | Reserved        | Reserved      | Reserved      |

| 25-24     | GPIO12        | TZ1 (I)         | SCITXDA (0)   | EQEP1A        |