广州润芯信息技术有限公司

**RX3603C**

北斗一代 RDSS 收发射频芯片

**广州润芯信息技术有限公司**

Guangzhou Runxin Information Technology CO. LTD

# **RX3603C**

## **北斗一代 RDSS 收发射频芯片**

### **产品规格书**

2016 年 7 月

V2.0

## 目录

|                      |    |

|----------------------|----|

| 目录 .....             | 2  |

| 概述 .....             | 3  |

| 应用领域 .....           | 3  |

| 特性 .....             | 3  |

| 结构框图 .....           | 3  |

| 直流特性 .....           | 4  |

| 交流特性 .....           | 4  |

| 极限值 .....            | 6  |

| 热阻 .....             | 6  |

| ESD 警告 .....         | 6  |

| 参数实测图 .....          | 7  |

| 管脚定义 .....           | 10 |

| 参考应用原理图 .....        | 13 |

| 功能模块描述 .....         | 16 |

| 低噪声放大器 .....         | 16 |

| 具有镜像抑制功能的下变频器 .....  | 16 |

| 带通滤波器 .....          | 16 |

| 自动增益控制放大器 .....      | 16 |

| 模数转换器 .....          | 16 |

| 频率综合器 .....          | 16 |

| 前置功率放大器(PPA) .....   | 16 |

| 发射 RC 滤波器 .....      | 16 |

| 串行通讯接口 .....         | 16 |

| 硬线控制端口使用说明 .....     | 17 |

| PWR_RX 端口使用说明 .....  | 17 |

| PWR_TX 端口使用说明 .....  | 17 |

| PWR_ADC 端口使用说明 ..... | 18 |

| GAIN_TX 端口使用说明 ..... | 18 |

| 数模转换器说明 .....        | 19 |

| 封装详细信息 .....         | 20 |

## 概述

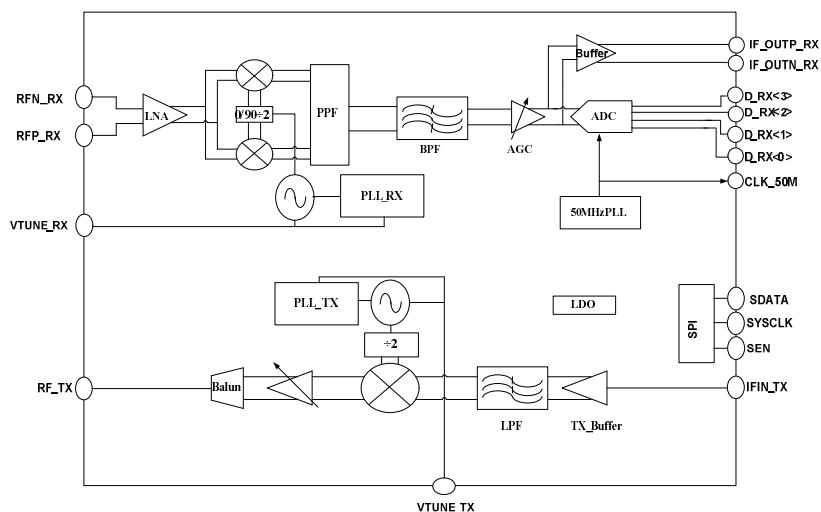

RX3603C 是一款针对北斗一代(RDSS)频点导航系统应用的射频芯片，包含 RDSS 接收通道和发射通道，支持接收发射通道同时独立工作。片上集成了具有镜频抑制功能的混频器 (Mixer)、中频带通滤波器 (BPF)、自动增益控制器 (AGC)、模数变换器 (ADC)、小数分频锁相环、PPA、Balun 和低压差线性稳压器 (LDO) 等电路，仅需很少的外围元器件即可工作。

在接收通道中，导航信号经过天线及射频带通滤波器 (SAW)，进入射频前端跨导放大器，经过放大、混频、滤波处理后通过模拟输出端口输出，供给数字基带进行处理。在发射通道中，发射基带信号经过发射机的低通滤波器后，经过上变频器和PPA，驱动外接PA，经天线发射出信号。

## 应用领域

- 车载导航终端

- Pad、手机等手持设备

- 船舶导航定位

- 个人定位终端

## 特性

## 结构框图

图 1 芯片系统框图

## 直流特性

环境温度  $T=25^{\circ}\text{C}$ ，IO 接口电压  $\text{VBAT\_TX}$  与  $\text{VBAT\_DIG}$  为 3.3V， $\text{VBAT}$ 、 $\text{VBAT\_RF}$  电压支持 1.8~3.3V。

表 1 直流特性

| 参数                               | 条件             | 最小值          | 典型值 | 最大值         | 单位 |

|----------------------------------|----------------|--------------|-----|-------------|----|

| 电流                               | RX 和 TX 通道同时工作 |              | 100 |             | mA |

|                                  | 仅 RX 通道工作      |              | 52  |             | mA |

|                                  | 仅 TX 通道工作      |              | 45  |             | mA |

|                                  | 待机模式           |              | 10  |             | uA |

| <b>数字输入端口参数</b>                  |                |              |     |             |    |

| 输入高电平 ( $\text{V}_{\text{IH}}$ ) |                | 0.7VBAT_DIG  |     |             | V  |

| 输入低电平 ( $\text{V}_{\text{IL}}$ ) |                |              |     | 0.3VBAT_DIG | V  |

| 输入低电流 ( $\text{I}_{\text{IH}}$ ) |                | -10          |     |             | uA |

| 输入高电流 ( $\text{I}_{\text{IL}}$ ) |                |              |     | 10          | uA |

| <b>数字输出端口参数</b>                  |                |              |     |             |    |

| 输出高电平 ( $\text{V}_{\text{OH}}$ ) |                | VBAT_DIG-0.4 |     |             | V  |

| 输出低电平 ( $\text{V}_{\text{OL}}$ ) |                |              |     | 0.4         | V  |

## 交流特性

测试环境：参考时钟频率  $f_{\text{REF}} = 10\text{MHz}$ ；环境温度  $T=25^{\circ}\text{C}$ ；

IO 接口电压  $\text{VBAT\_TX}=\text{VBAT\_DIG}=3.3\text{V}$ ， $\text{VBAT}=\text{VBAT\_RF}=1.8\text{V}$ 。

表 2 交流特性

| 项目                                 | 最小     | 典型             | 最大  | 单位  | 备注          |

|------------------------------------|--------|----------------|-----|-----|-------------|

| <b>接收机交流特性</b>                     |        |                |     |     |             |

| 中心频率                               |        | 2491.75        |     | MHz |             |

| 模拟中频输出信号峰峰值                        |        | 1 <sup>①</sup> |     | V   |             |

| 噪声系数                               |        | 5              | 7   | dB  |             |

| 接收机输入 $\text{P}_{-1\text{dB}}$ 压缩点 |        | -40            |     | dBm | 50dB 通道增益   |

| S11                                |        | -12            | -10 | dB  | 差分匹配到 100 欧 |

| 通道增益                               | 固定增益模式 | 35             |     | dB  |             |

|                                    | AGC 模式 | 40             |     | dB  |             |

| 中频                                 |        | 12.24          |     | MHz | 低本振         |

| 中频-3dB 带宽                          |        | 8.16           |     | MHz |             |

| 带外抑制（ $\pm 1.5$ 倍带宽）               |        | 20             |     | dB  |             |

| 发射通道交流特性             |      |         |                  |        |                |

|----------------------|------|---------|------------------|--------|----------------|

| 中心频率                 |      | 1615.68 |                  | MHz    |                |

| 输出匹配                 |      | 50      |                  | ohm    | 单端匹配到 50 欧     |

| S22                  |      | -12     | -10              | dB     |                |

| 输出功率                 | -0.5 |         | 2.5              | dBm    |                |

| Gain Step            |      | 1       |                  | dB     | 范围-0.5~2.5 dBm |

| 相位误差                 |      | 1.5     | 3                | degree | Pout<5dBm      |

| 本振泄露                 |      |         | -30              | dBc    | Pout<5dBm      |

| Output power variety | -1   |         | 1                | dB     |                |

| 发射通道锁相环特性 (PLL1)     |      |         |                  |        |                |

| 频率                   |      | 1615.68 |                  | MHz    |                |

| 相位噪声                 |      | -76     |                  | dBc/Hz | 0.1K           |

|                      |      | -87     |                  | dBc/Hz | 1K             |

|                      |      | -86     |                  | dBc/Hz | 10K            |

|                      |      | -95     |                  | dBc/Hz | 100K           |

|                      |      | -117    |                  | dBc/Hz | 1M             |

| 接收通道锁相环特性 (PLL2)     |      |         |                  |        |                |

| 频率                   |      | 2479.51 |                  | MHz    |                |

| 相位噪声                 |      | -73     |                  | dBc/Hz | 0.1K           |

|                      |      | -85     |                  | dBc/Hz | 1K             |

|                      |      | -87     |                  | dBc/Hz | 10K            |

|                      |      | -94     |                  | dBc/Hz | 100K           |

| ADC 采样时钟特性           |      |         |                  |        |                |

| 频率                   |      | 50      |                  | MHz    |                |

| 输出幅度                 |      |         | 3.3 <sup>②</sup> | V      |                |

| 时钟抖动                 |      | 25      |                  | ps     |                |

| 参考时钟特性               |      |         |                  |        |                |

| 输入参考时钟幅度             | 0.6  |         | 1.2              | Vpp    | 峰峰值            |

| 参考时钟频率               |      | 10      |                  | MHz    |                |

| 参考时钟输入阻抗             |      | 5       |                  | kΩ     |                |

备注①：接收通道中频输出驱动高阻（ $\geq 5K$ ）时，输出信号功率约 4dBm,输出信号幅度 Vpp 约为 1V（差分输出时其正负端 Vpp 均为 500mV 左右）；驱动 50Ω 时，输出信号功率约 2.5dBm,输出信号幅度 Vpp 约 840mV（差分输出时其正负端 Vpp 均为 400mV 左右）。

②：时钟输出幅度受负载影响，建议负载电容  $\leq 10pF$ 。

## 极限值

在任何情况下都不能超出表 3 所列的最大额定值的范围，超过额定值会永久性地损坏芯片。

表 3 极限值

| 参数     | 符号       | 取值                | 单位  |

|--------|----------|-------------------|-----|

| 直流电源电压 | VBAT_DIG | 3.6               | V   |

| 数字端口电压 |          | -0.3~VBAT_DIG+0.3 | V   |

| 工作温度   | TOP      | -40~85            | °C  |

| 贮藏温度   | TSTG     | -55~150           | °C  |

| 射频输入功率 |          | 0                 | dBm |

注：数字端口引脚：SEN、SYSCLK、SDATA

## 热阻

热阻  $\theta_{JA}$  仅针对最坏情况。

表 4 热阻

| 封装类型  | $\theta_{JA}$ | 单位    |

|-------|---------------|-------|

| QFN40 | 40            | °C /W |

## ESD 警告

|  |                                                                                       |

|--|---------------------------------------------------------------------------------------|

|  | ESD（静电泄放）敏感器件。带电荷的器件或电路板会自动泄放。尽管该器件已带有保护电路，高能量的静电泄放仍会导致器件损坏。因此，正确地预防静电泄放可避免性能恶化或功能损坏。 |

|--|---------------------------------------------------------------------------------------|

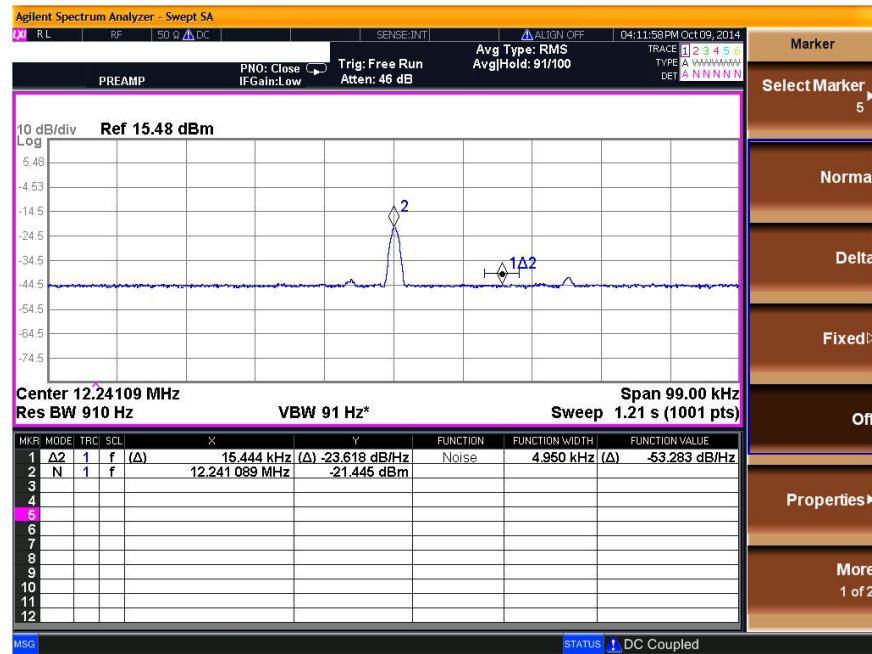

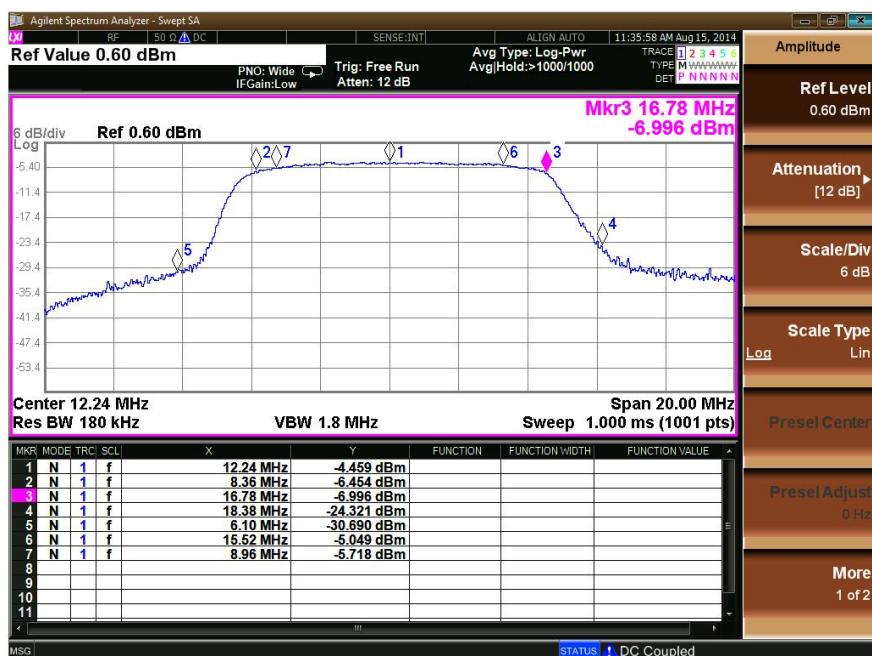

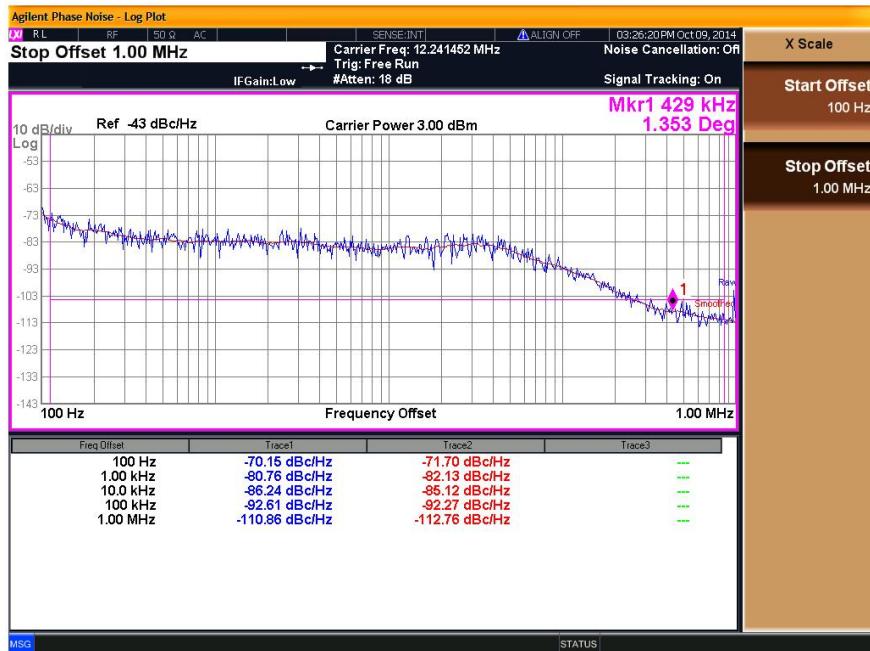

## 参数实测图

以下图表均基于 RX3603C 参考电路（见图 9）进行测试。

(a) 接收通道噪声系数测试。

图 2 RX 通道噪声系数，输入-114dBm, NF 为 5.8dB (线损 1dB)

(b) 接收通道滤波特性

图 3 接收中频滤波器

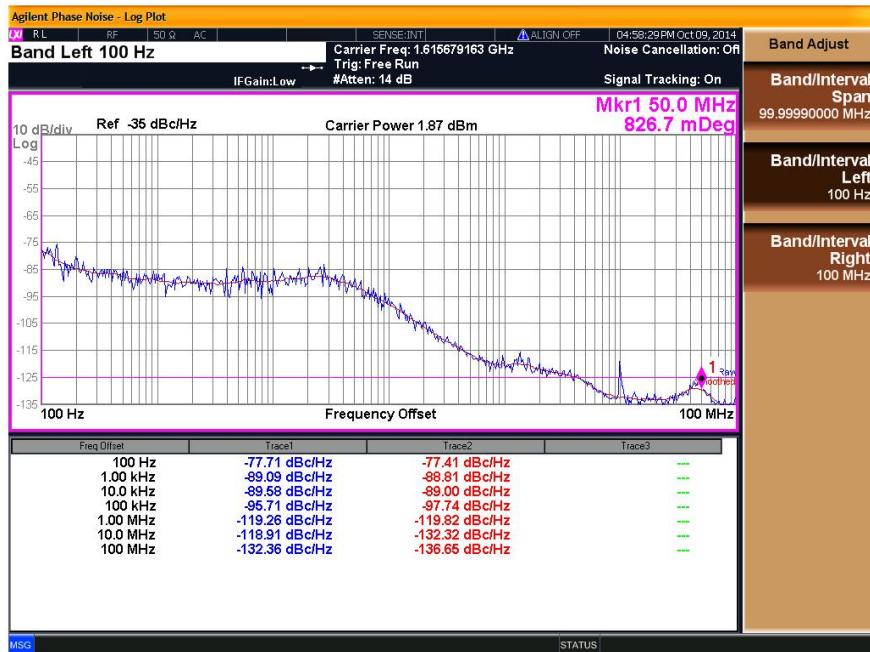

(c) 相位噪声

图 4 接收中频相位噪声

图 5 TX 发射相位噪声

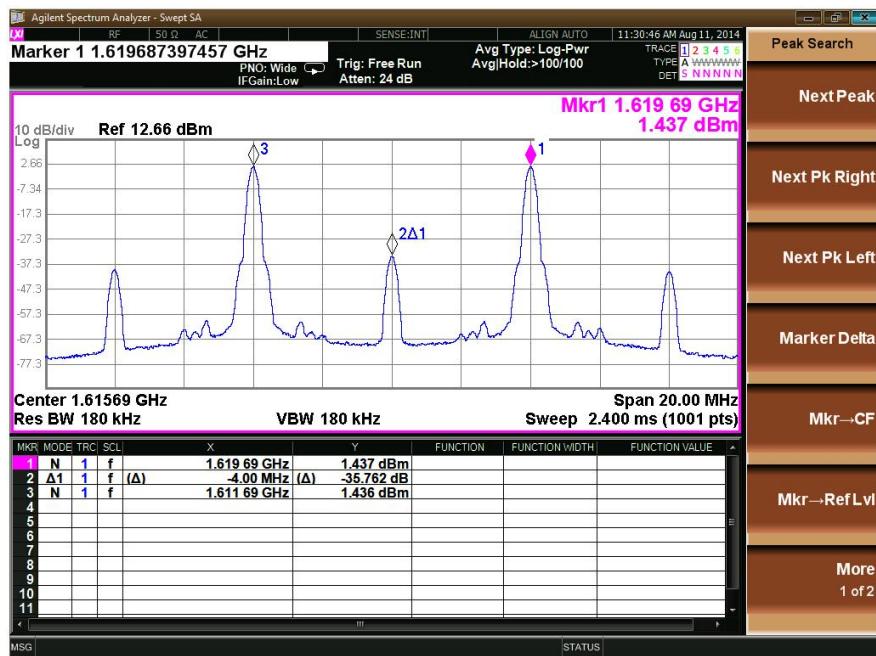

(d) 本振泄漏。

图 6 输出功率为 4.4dBm 时的本振抑制为 35dB

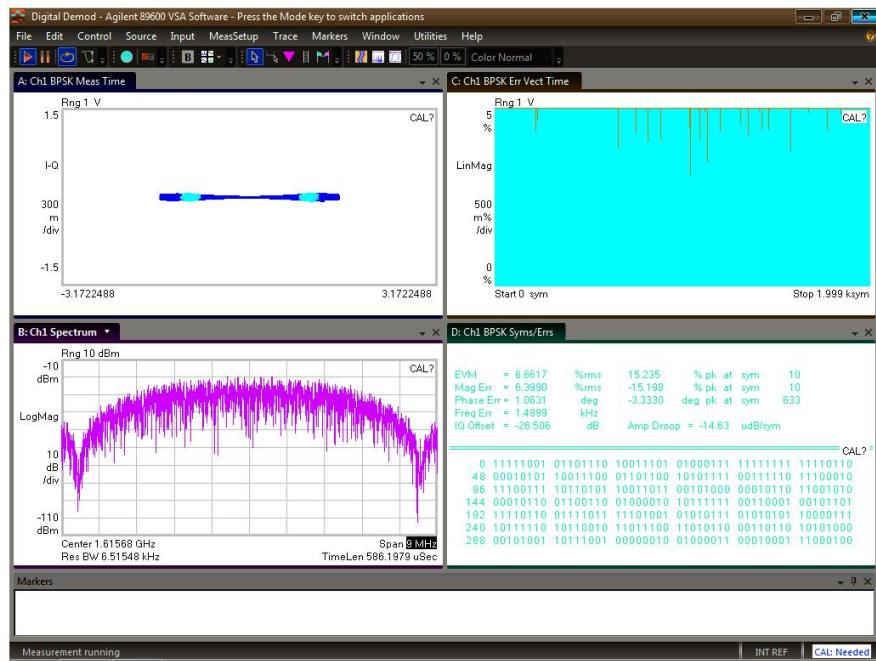

(e) 相位误差差

图 7 发射 EVM 测试, 相位误差为 1.06 度

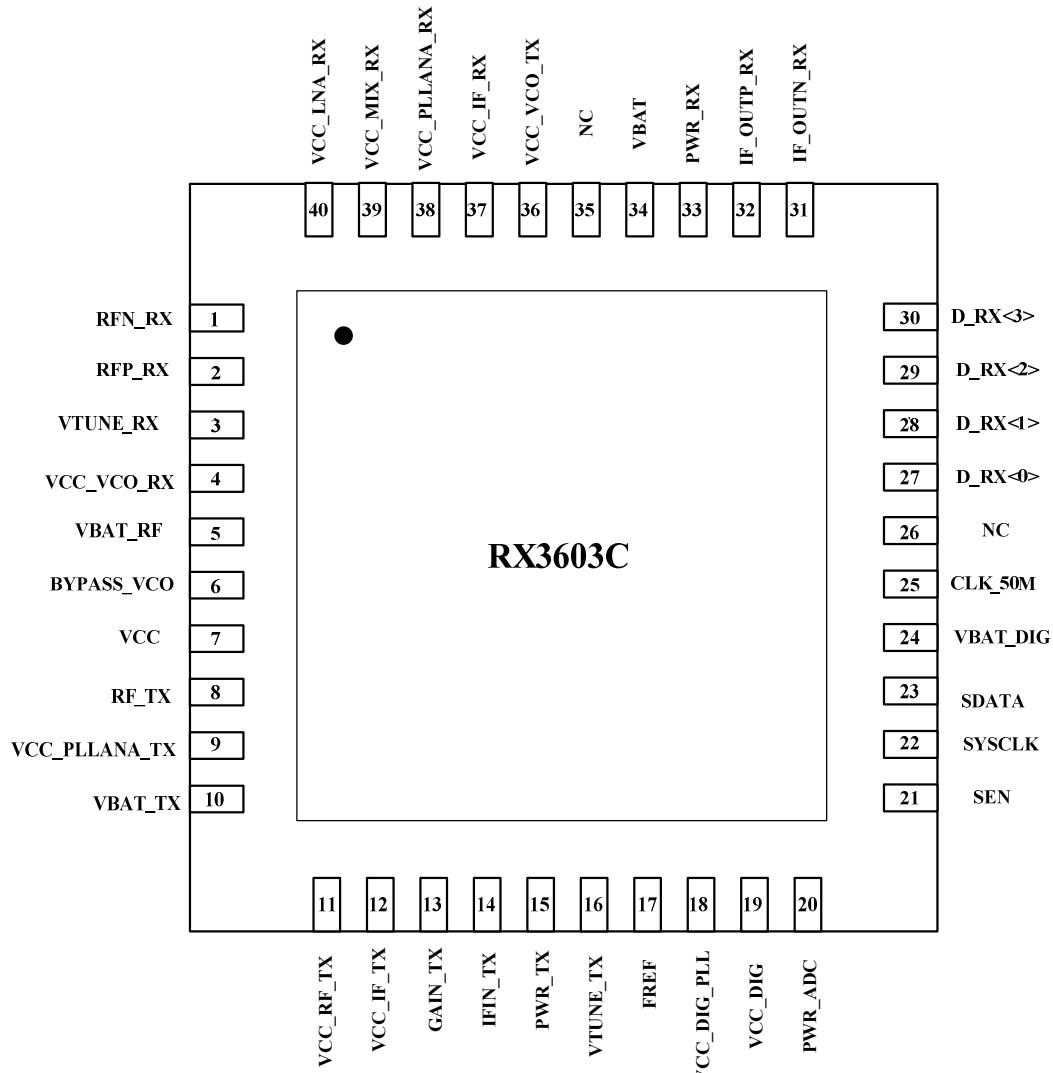

## 管脚定义

图 8 芯片管脚顶视图

表 5 管脚定义

| 序号 | 引脚名称       | I/O | 描述                                  | 备注                            |

|----|------------|-----|-------------------------------------|-------------------------------|

| 1  | RFN_RX     | I   | Negative input of RX LNA            | AC, 信号强度-110~-40dBm           |

| 2  | RFP_RX     | I   | Positive input of RX LNA            | AC, 信号强度-110~-40dBm           |

| 3  | VTUNE_RX   | I/O | RX PLL vtune control                | DC, 接环路滤波器                    |

| 4  | VCC_VCO_RX | I/O | VCO LDO output                      | DC, 1.15~1.25V, 需接 2.2uF 滤波电容 |

| 5  | VBAT_RF    | I   | power supply of RF&VCO&IF           | DC, 1.8~3.3V                  |

| 6  | BYPASS_VCO | I/O | the band-gap filter pin for VCO LDO | 接 10nF 滤波电容                   |

|    |               |     |                                      |                                                                                            |

|----|---------------|-----|--------------------------------------|--------------------------------------------------------------------------------------------|

| 7  | VCC           | I/O | LDO output                           | DC, 1.15~1.25V, 需接 2.2uF 滤波电容                                                              |

| 8  | RF_TX         | O   | Transmitter output                   | AC, 发射机输出                                                                                  |

| 9  | VCC_PLLANA_TX | I/O | PLL and B3 LDO output                | DC, 1.15~1.25V, 需接 2.2uF 滤波电容                                                              |

| 10 | VBAT_TX       | I   | power supply of transmitter          | DC, 3.3V                                                                                   |

| 11 | VCC_RF_TX     | I/O | transmitter RF LDO output            | DC, 1.15~1.25V, 需接 2.2uF 滤波电容                                                              |

| 12 | VCC_IF_TX     | I/O | transmitter IF LDO output            | DC, 1.15~1.25V, 需接 2.2uF 滤波电容                                                              |

| 13 | GAIN_TX       | I   | Transmitter channel gain control pin | DC, 0~1.2V                                                                                 |

| 14 | IFIN_TX       | I   | Transmitter input                    | DC, 0~3.3V 逻辑电平输入                                                                          |

| 15 | PWR_TX        | I   | Transmitter channel enable           | DC, 悬空或接高电平为发射机开启, 拉低为发射机关闭                                                                |

| 16 | VTUNE_TX      | I/O | TX PLL vtune control                 | DC, 接环路滤波器                                                                                 |

| 17 | FREF          | I   | 10MHz reference input                | AC, 10MHz, 需隔直, 输入幅度 0.8~2V                                                                |

| 18 | VCC_DIG_PLL   | I/O | PLL Digital LDO output               | DC 输入/输出, 1.15~1.25V, 需接 2.2uF 滤波电容                                                        |

| 19 | VCC_DIG       | I/O | Digital LDO output                   | DC 输入/输出, 1.15~1.25V, 需接两个 4.7uF 滤波电容                                                      |

| 20 | PWR_ADC       | I   | ADC enable                           | DC, 悬空或高电平打开ADC, 关闭模拟中频通道; 接地, 打开模拟中频; 也可通过SPI 控制, 使模拟和数字中频同时打开                            |

| 21 | SEN           | I   | SPI                                  | SPI 使能, 数字逻辑电路, 与 IO 电压匹配即可                                                                |

| 22 | SYSCLK        | I   |                                      | 不高于参考时钟频率                                                                                  |

| 23 | SDATA         | I/O |                                      | SPI 数据输入输出端口                                                                               |

| 24 | VBAT_DIG      | I   | power supply of DIG and DIG IO       | DC 输入, 在单端模拟中频输出时, 与单端输出 buffer 共用, 电压范围为 2.7~3.6V; 若数字中频输出, 则逻辑摆幅由该电压决定, 不低于 LVTTL 电平要求即可 |

| 25 | CLK_50M       | O   | 50MHz Clock output                   | AC, 50MHz。                                                                                 |

| 26 | NC            |     | Not connect                          | No connection                                                                              |

| 27 | D_RX<0>       | O   | RX Data output from ADC              | 默认补码输出, 逻辑摆幅在 1.5~3.3V 之间, 由 pin27 决定                                                      |

| 28 | D_RX<1>       | O   |                                      |                                                                                            |

| 29 | D_RX<2>       | O   |                                      |                                                                                            |

| 30 | D_RX<3>       | O   |                                      |                                                                                            |

| 31 | IF_OUTN_RX    | O   | RX analog IF output (negative)       | AC, 12.24 MHz。默认模式下, 模拟中频单端输出, 负端口无信号                                                      |

| 32 | IF_OUTP_RX    | O   | RX analog IF output (positive)       | AC, 12.24 MHz。默认模式下单端输出, 1Vpp                                                              |

| 33 | PWR_RX        | I   | power up/down RX channel             | DC, 通过接不同的电阻, 可实现RX通道D2S切换以及通道的打开和关闭, 详见使                                                  |

|    |               |     |                       | 用说明                                    |

|----|---------------|-----|-----------------------|----------------------------------------|

| 34 | VBAT          | I   | power supply of IF    | DC,1.8~3.3V                            |

| 35 | NC            |     | Not connect           | No connection                          |

| 36 | VCC_VCO_TX    | I/O | TX PLL VCO LDO output | DC 输入/输出, 1.15~1.25V, 需接 2.2uF<br>滤波电容 |

| 37 | VCC_IF_RX     | I/O | RX IF LDO output      | DC 输入/输出, 1.15~1.25V, 需接 2.2uF<br>滤波电容 |

| 38 | VCC_PLLANA_RX | I/O | RX IF LDO output      | DC 输入/输出, 1.15~1.25V, 需接 2.2uF<br>滤波电容 |

| 39 | VCC_MIX_RX    | I/O | RX MIXER LDO output   | DC 输入/输出, 1.15~1.25V, 需接 2.2uF<br>滤波电容 |

| 40 | VCC_LNA_RX    | I/O | RX MIXER LDO output   | DC 输入/输出, 1.15~1.25V, 需接 2.2uF<br>滤波电容 |

### 应用注意事项:

- 1、输入 10M 参考走线尽量短

- 2、VCC\_DIG 需外接两个 4.7uF 电容

- 3、RX 通道射频输入端和中频输出端应尽量远离

- 4、建议 50M 时钟输出端串联 82nH 的电感, 且尽量靠近芯片, 降低时钟的高次谐波干扰。

- 5、接收通道的输入走线应保证差分性

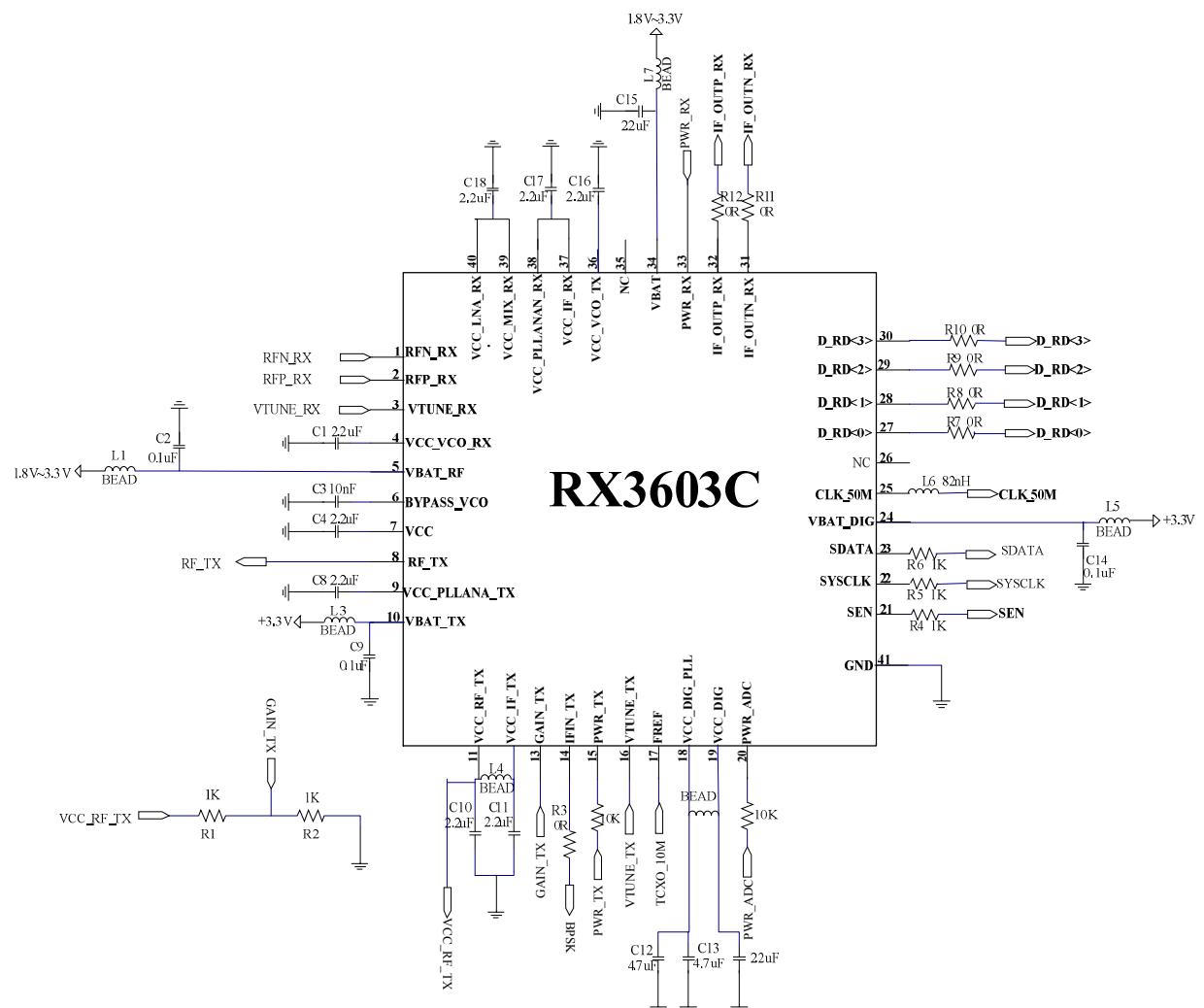

## 参考应用原理图

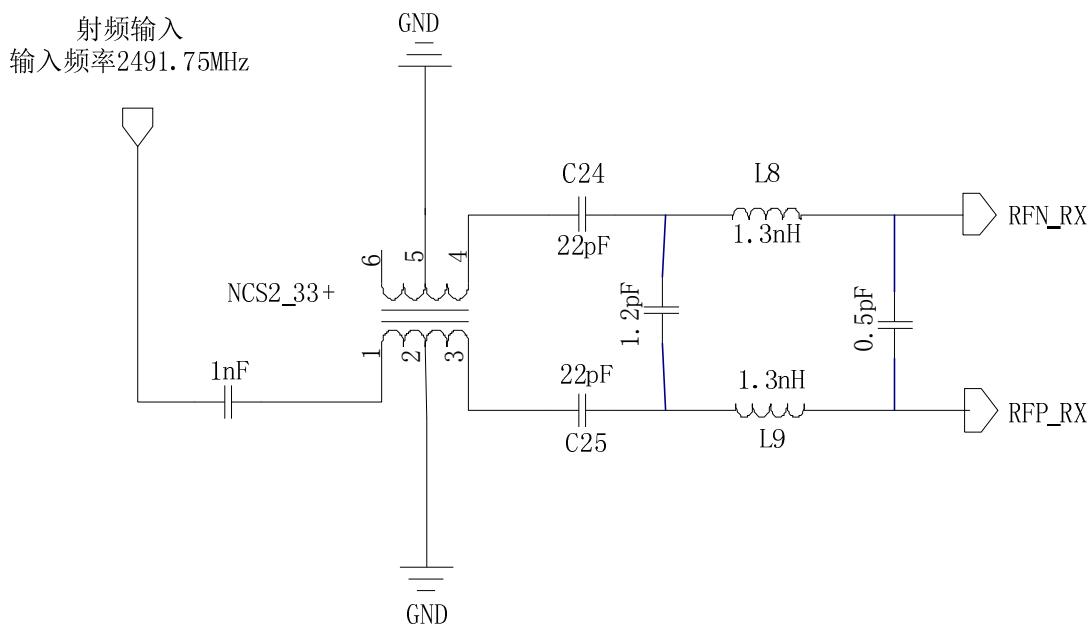

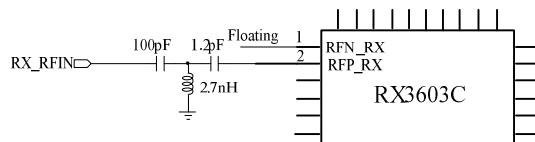

(a) RX 通道匹配网络

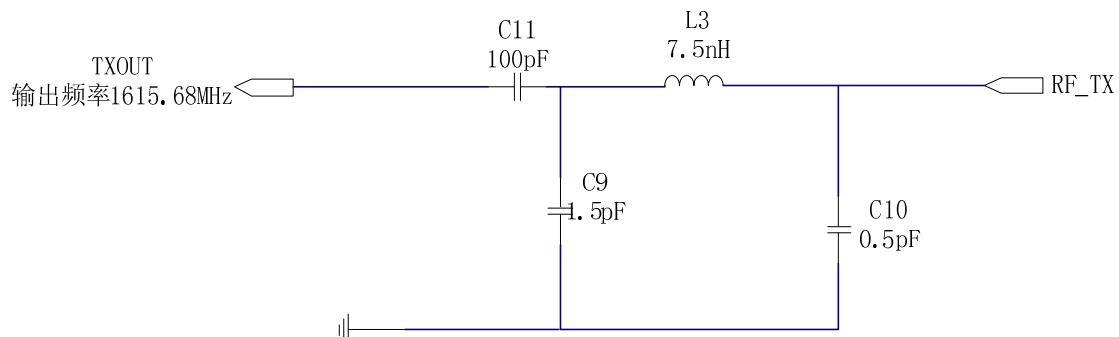

(b) TX 通道匹配网络

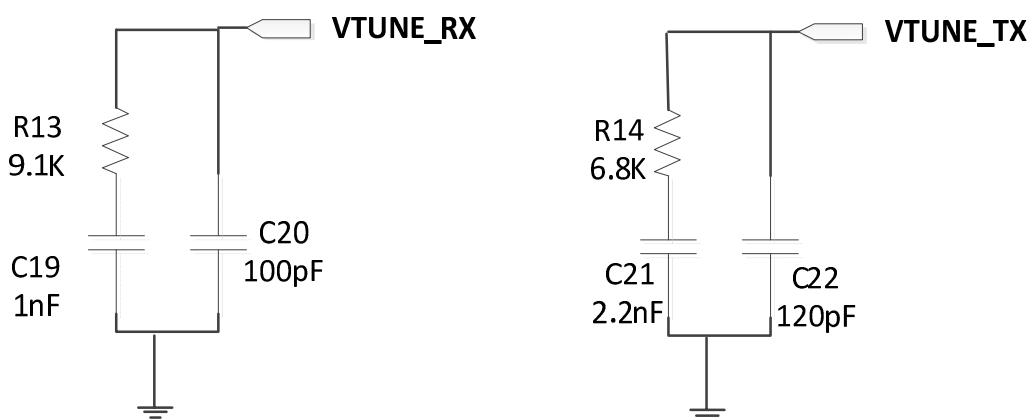

(b) 环路滤波

(d) 参考应用电路

图9 参考应用电路原理图

备注：RX 射频单端输入使用说明

图 10 RX 通道单端匹配网络

RX 通道射频单端输入使用时，参照图 10 的接法，1 脚 RFN\_RX 悬空，2 脚 RFP\_RX 接单端匹配网络。

**(备注：射频使用单端匹配网络时，相比差分匹配网络噪声系数恶化约 3dB)**

应用原理图中涉及到的元器件的型号及性能参数见下表 6

表 6 参考元器件型号及其部分性能参数

| 器件名称 | 器件型号       | 部分性能参数                            |

|------|------------|-----------------------------------|

| 巴伦   | NCS2-33+   | RD 通道中使用，频率范围：1500~3100MHz，差损：1dB |

| 晶振   | TXEBALSANF | 频率 10M，幅度 0.8~2V，工作电压 3V          |

注：图 9~10 中的匹配网络并不是唯一值，仅为开发板上匹配原件最优值，但射频 PCB 板间存在差异，如需得到更优匹配，需再次调试使其达到最优值。

## 功能模块描述

### 低噪声放大器

接收通道分使用了差分输入的低噪放，片内直接接混频器电路。低噪放是整个接收通道的关键模块，整个接收机通道的噪声系数在 7dB 以下。

### 具有镜像抑制功能的下变频器

低噪放输出接混频器，经下变频后得到相应的中频信号。同时，其内部集成多相滤波器(PPF)，可实现大于 30dB 以上的镜像抑制。

### 带通滤波器

中频带通滤波器采用切比雪夫带通滤波器，具有自校准功能。中频信号经过带通滤波器后，能有效滤除带外的干扰和杂散，避免 ADC 采样形成频谱混迭。

### 自动增益控制放大器

片上集成的自动增益控制放大器，能有效补偿实际应用中信号强弱的变化，使 ADC 的采样电路能够正常工作。AGC 电路提供大于 50dB 的动态范围。

### 模数转换器

芯片集成了 4 Bit Flash ADC，对 AGC 输出模拟信号进行采样，采样时钟频率为 50MHz。ADC 输出默认为 2bit, sign.mag 码输出。可通过 SPI 选择为偏移码，也可通过 SPI 配置为 4Bit。

### 频率综合器

片上集成了高性能的  $\Sigma$   $\Delta$  小数分频锁相环，全集成了鉴频鉴相器，电荷泵，环路滤波器，分频器，压控振荡器等模块电路。

### 前置功率放大器(PPA)

前置功率放大器(PPA)提供合适的功率以驱动后续外接功率放大器(PA)，同时完成匹配。在 RX3603C 的 PPA 设计中，还加入了功率控制功能，节省了射频 PGA 的使用。

### 发射 RC 滤波器

发射集成了低通滤波器，滤除了数字信号通过 DAC 转为模拟信号后的谐波等干扰信号。

### 串行通讯接口

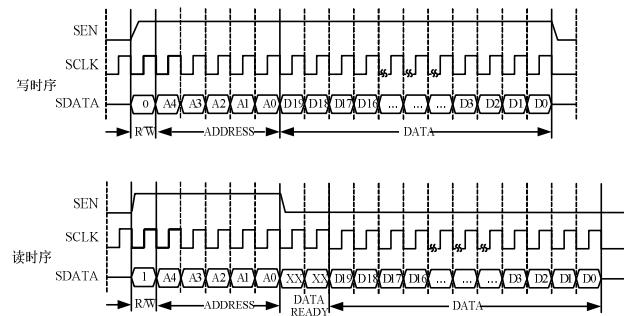

用户可通过串行通讯接口对 RX3603C 内部的 PLL，ADC 等模块进行配置。串行接口由时钟 (SCLK)、数据输入输出 (SDATA) 和使能 (SEN) 等信号线组成。**SCLK 时钟频率推荐为 50KHz~100KHz**。

通讯时序如图 11。建立通讯前，SCLK、SDATA、SEN 保持低电平，当开始通讯时 SCLK 需先发一个周期 CLK 以通知芯片做好通讯准备。在该 CLK 的下降沿，使 SEN 信号由低电平跳变为高电平，SDATA 上的数据开始被写入芯片内的缓存器，直到 SEN 信号由高电平跳回到低电平时结束。在 SCLK 的下降沿时 SDATA 信号可改变，SDATA 上的数据在 SCLK 上升沿时会被采样。

串行接口通讯时采用高位在前的方式，依次发送 1bit 读写标志位 (R/W)，**5bit 地址位 (ADDRESS)** 和 20bit 数据位 (DATA)。但在读操作时，发送完 **5bit 地址位** 后需要等待 2 个 CLK 才能收到 20bit 的数据。

图 11 SPI 时序图

## 硬线控制端口使用说明

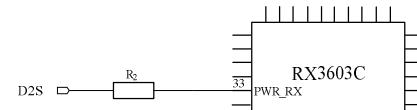

### PWR\_RX端口使用说明

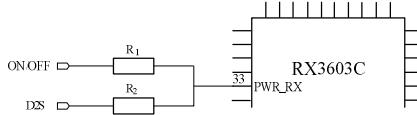

为节约芯片 pin 脚, 设计中对引脚PWR\_RX(pin33)进行了复用。如果此控制引脚悬空, 默认开启RX通道。而通过外接不同电阻, 可实现ON/OFF(通道开关)及D2S(模拟输出接口单端/差分切换)的功能。下面为管脚PWR\_RX 不同接法所实现的功能。(备注: 以下表格中所描述的高电平与VBAT\_DIG一致)

接法 1: 外接两个电阻同时控制

图 12 硬线 PWR\_RX 端口说明 1

表 7 硬线 PWR\_RX 端口外接两个电阻使用状态描述

| ON/OFF | D2S | 说明         | R1、R2 电阻选择                                                                |

|--------|-----|------------|---------------------------------------------------------------------------|

| 低电平    | X   | 通道关闭       |                                                                           |

| 高电平    | 低电平 | 通道工作, 差分输出 | $R_2=2R_1$ , $30K\Omega \leq R_1 \leq 60K\Omega$ , 推荐<br>$R_1=47 K\Omega$ |

| 高电平    | 高电平 | 通道工作, 单端输出 |                                                                           |

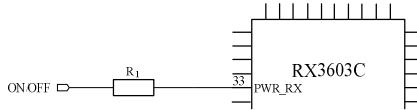

接法2: 只接一个电阻控制通道打开(默认单端输出)或关闭:

图 13 硬线 PWR\_RX 端口说明 2

表 8 硬线 PWR\_RX 端口外接单个电阻使用状态描述

| ON/OFF | 说明         | R1 电阻选择                                      |

|--------|------------|----------------------------------------------|

| 低电平    | 通道关闭       |                                              |

| 高电平/悬空 | 通道工作, 单端输出 | $R_1 \leq 100 K\Omega$ , 推荐 $R_1=47 K\Omega$ |

接法3: 只接一个电阻切换D2S :

图 14 硬线 PWR\_RX 端口说明 3

表 9 硬线 PWR\_RX 端口外接单个电阻且切换 D2S 使用状态描述

| D2S    | 说明   | R1 电阻选择                                                        |

|--------|------|----------------------------------------------------------------|

| 低电平    | 差分输出 |                                                                |

| 高电平/悬空 | 单端输出 | $700 K\Omega \leq R_2 \leq 900 K\Omega$ , 推荐 $R_2=800 K\Omega$ |

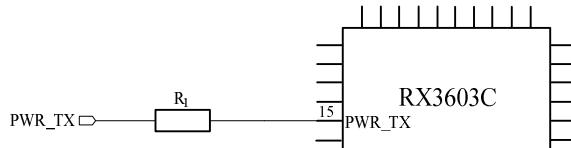

### PWR\_TX端口使用说明

硬线控制 PWR\_TX(pin15)引脚有两种用法: (1) 悬空或接高电平状态时, 默认发射机开启 (2) 直接接地, 发射机关闭。(备注: 以下表格中所描述的高电平与 VBAT\_DIG 一致)

图 15 硬线 PWR\_TX 端口外接一个电阻使用连接示意图

表 10 硬线 PWR\_TX 端口外接使用状态描述

| PWR_TX | 说明    | R1 电阻选择     |

|--------|-------|-------------|

| 低电平    | 发射机关闭 | 推荐 R1=10 KΩ |

| 高电平/悬空 | 发射机开启 |             |

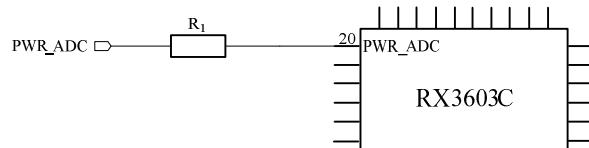

**PWR\_ADC 端口使用说明**

硬线控制 PWR\_ADC(pin20)引脚有两种用法：(1) 悬空或接高电平状态时，打开 ADC，关闭模拟中频通道 (2) 直接接地，打开模拟中频输出方式。（备注：以下表格中所描述的高电平与 VBAT\_DIG 一致）

图 16 硬线 PWR\_ADC 端口外接一个电阻使用连接示意图

表 11 硬线 PWR\_ADC 端口外接使用状态描述

| PWR_ADC | 说明                  | R1 电阻选择     |

|---------|---------------------|-------------|

| 低电平     | 模拟中频输出方<br>式,ADC 关闭 | 推荐 R1=10 KΩ |

| 高电平/悬空  | 数字中频输出方<br>式,ADC 开启 |             |

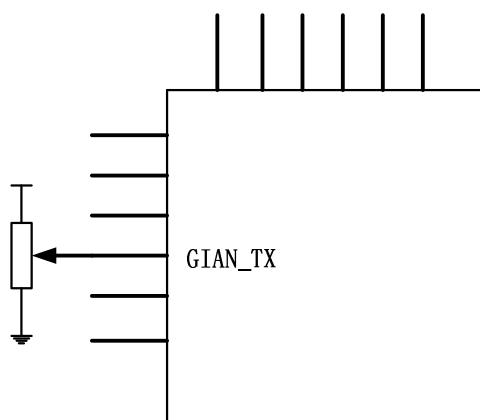

**GAIN\_TX 端口使用说明**

GAIN\_TX 可以控制发射机的发射功率输出，控制范围为-1.5dBm~5.5dBm。此 pin 端可以外接一个可调电位器，电位器的电源接 pin12 (VCC\_IF\_TX)，另外一端接地，其电路见图 17。输入电压与输出功率的对应关系如表 12。

图 17 GAIN\_TX 端口说明

表 12 输入控制电压与发射功率对应关系

|          |        |           |           |          |

|----------|--------|-----------|-----------|----------|

| 输入电压 V   | 0~0.24 | 0.24~0.36 | 0.36~0.48 | 0.48~0.6 |

| 发射功率 dBm | -0.5   | 0.5       | 1.5       | 2.5      |

注: GAIN\_TX 的输入电压超过 0.6V 时, 发射功率会压缩, 较难保证 1dB 步进, 且此时发射相位误差较大, 建议使用 GAIN\_TX 的输入电压  $\leq 3$  dBm。

## 数模转换器说明

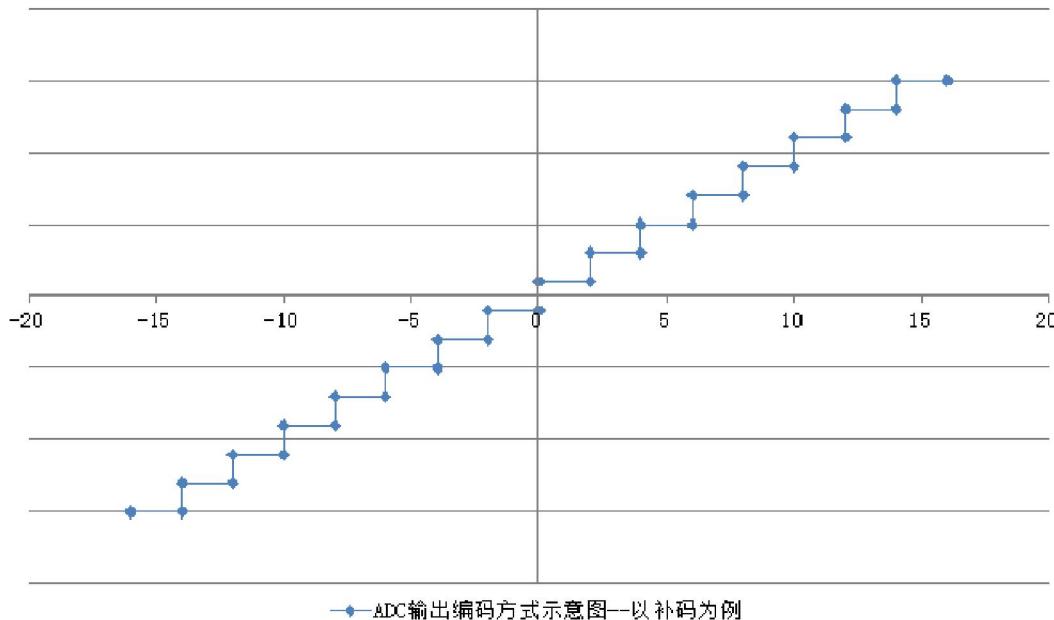

RX3603C 系列芯片内部集成了四位数模转换器 (ADC), 采用 FLASH 结构, ADC 采样时钟可由内部时钟频率合成器提供, 时钟频率各款芯片略有差异, 具体见附表。RD 通道默认上电 ADC 使用 2bit 输出, 2bitADC 的输出有两种编码方式, 具体见下表 13。

表 13 2bit 模式下的编码方式

| 整数值 | 原码/偏移码 | sign mag 码 |

|-----|--------|------------|

| -3  | 00     | 11         |

| -1  | 01     | 10         |

| 1   | 10     | 00         |

| 3   | 11     | 01         |

备注: 该芯片中, 原码与偏移码概念相同。

图 18 ADC 输出编码方式示意图

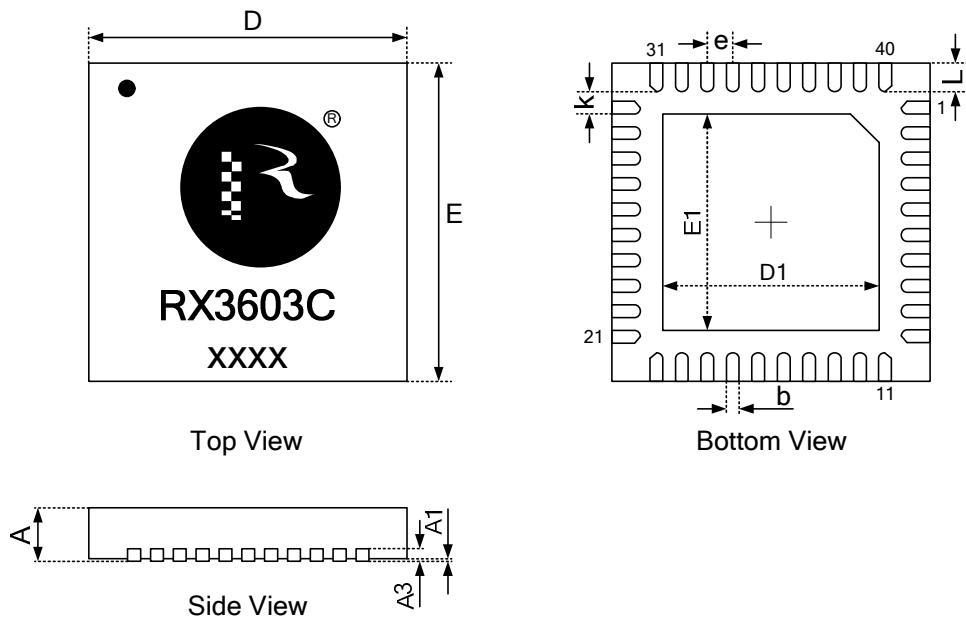

## 封装详细信息

### 40 引脚 QFN 塑封—— $5 \times 5 \times 0.8 \text{ mm}$

图 19 封装尺寸图

表 14 封装尺寸表

| Symbol | 尺寸(毫米)      |             | 尺寸(英寸)      |             |

|--------|-------------|-------------|-------------|-------------|

|        | Min.        | Max.        | Min.        | Max.        |

| A      | 0.700/0.800 | 0.800/0.900 | 0.028/0.031 | 0.031/0.035 |

| A1     | 0.000       | 0.050       | 0.000       | 0.002       |

| A3     | 0.203REF    |             | 0.008REF    |             |

| D      | 4.924       | 5.076       | 0.194       | 0.200       |

| E      | 4.924       | 5.076       | 0.194       | 0.200       |

| D1     | 3.300       | 3.500       | 0.130       | 0.138       |

| E1     | 3.300       | 3.500       | 0.130       | 0.138       |

| k      | 0.200MIN    |             | 0.008MIN    |             |

| b      | 0.150       | 0.250       | 0.006       | 0.010       |

| e      | 0.400TYP    |             | 0.016TYP    |             |

| L      | 0.324       | 0.476       | 0.013       | 0.019       |