## サイプレスはインフィニオンテクノロジーズになりました

この表紙に続く文書には「サイプレス」と表記されていますが、これは同社が最初にこの製品を開発したからです。新規および既存のお客様いずれに対しても、引き続きインフィニオンがラインアップの一部として当該製品をご提供いたします。

### 文書の内容の継続性

下記製品がインフィニオンの製品ラインアップの一部として提供されたとしても、それを理由としてこの文書に変更が加わることはありません。今後も適宜改訂は行いますが、変更があった場合は文書の履歴ページでお知らせします。

### 注文時の部品番号の継続性

インフィニオンは既存の部品番号を引き続きサポートします。ご注文の際は、データシート記載の注文部品番号をこれまで通りご利用下さい。

## エラー訂正コード (ECC) 内蔵の 8M ビット (512K×16 ビット) スタティック RAM

### 特長

- 超低スタンバイ電流

- 標準スタンバイ電流 : 1.4 $\mu$ A

- 最大スタンバイ電流 : 6.5 $\mu$ A

- 高速 : 45ns

- 電圧範囲 : 1.65V ~ 3.6V

- シングルビット エラー訂正用の組込みエラー訂正コード (ECC)

- 1.0V データ保持

- トランジスタ - トランジスタ ロジック (TTL) と互換性のある入出力

- 鉛フリー 48 ポール VFBGA、44 ピン TSOP II および 48 ピン TSOP I のパッケージ

### 機能説明

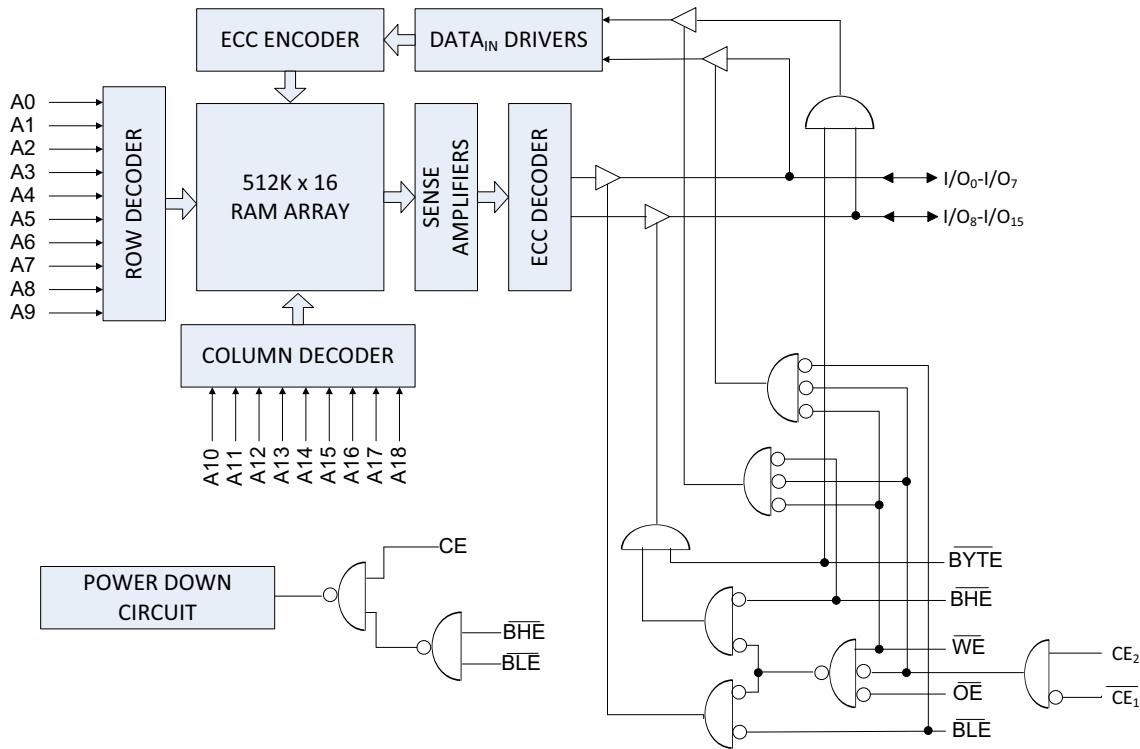

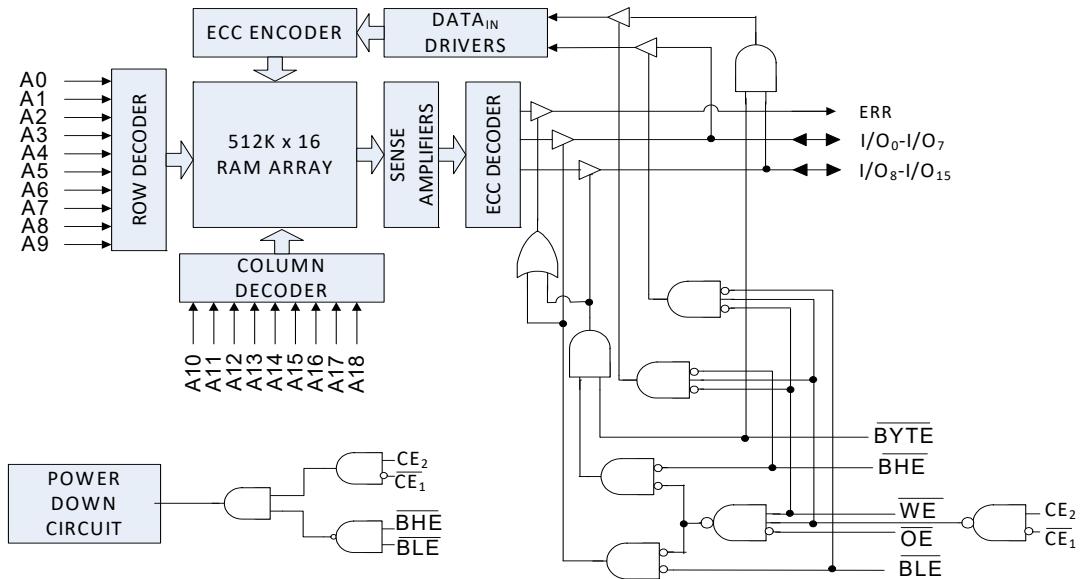

CY62157G と CY62157GE は組込みエラー訂正コード (ECC) を内蔵した高性能 CMOS 低電力 (MoBL<sup>®</sup>) SRAM デバイスです。ECC ロジックは、アクセスされた場所でシングルビットエラーを検出して訂正できます。

本デバイスは、デュアル チップ イネーブル オプションで提供されています。デュアル チップ イネーブル デバイスは、両方のチップ イネーブル入力を ( $CE_1$  を LOW に、 $CE_2$  を HIGH に) アサートすることでアクセスされます。

データ書き込みは、書き込みイネーブル入力 ( $\overline{WE}$ ) を LOW にアサートし、データとアドレスをデバイスのそれぞれデータ ピン ( $I/O_0$  ~  $I/O_{15}$ ) とアドレス ピン ( $A_0$  ~  $A_{18}$ ) に提供することによって実行されます。上位バイト イネーブル (BHE) と下位バイト イネーブル (BLE) の入力はバイト書き込みを制御し、対応する  $I/O$  ライン上のデータを指定されたメモリ位置に書き込みます。BHE は  $I/O_8$  ~  $I/O_{15}$  を制御し、BLE は  $I/O_0$  ~  $I/O_7$  を制御します。

データ読み出しは、出力イネーブル ( $\overline{OE}$ ) 入力をアサートして、必要なアドレスをアドレス ラインに提供することによって実行されます。読み出しデータは、 $I/O$  ライン ( $I/O_0$  ~  $I/O_{15}$ ) 上でアクセスできます。バイトアクセスは、必要なバイト イネーブル信号 (BHE、BLE) をアサートして、指定されたアドレス位置からデータの上位バイトまたは下位バイトのいずれかを読み出すことによって実行されます。

デバイスが選択解除される (デュアル チップ イネーブル デバイスでは  $CE_1$  が HIGH に、 $CE_2$  が LOW にされる) か、または制御信号 ( $OE$ 、 $BLE$ 、 $BHE$ ) がデアサートされるとき、すべての  $I/O$  ( $I/O_{15}$  ~  $I/O_0$ ) は高インピーダンス状態になります。

これらのデバイスは、独自の「Byte Power down」機能を備えています。この機能により、両方のバイト イネーブル (BHE と BLE) が無効にされている場合、デバイスはチップ イネーブルの状態に関係なく、シームレスにスタンバイ モードに切り替わり、消費電力を節約します。

CY62157G と CY62157GE のデバイスは鉛フリー 48 ポール VFBGA、44 ピン TSOP II および 48 ピン TSOP I のパッケージで提供されています。[2 ページの論理ブロック ダイヤグラム - CY62157G](#) を参照してください。

48 ピン TSOP I パッケージに実装されたデバイスは、1M×8 ビット デバイスとして機能するように設定できます。[5 ページのピン配置](#) を参照してください。

### 製品ポートフォリオ

| 製品         | 範囲  | $V_{CC}$ の範囲 (V) | 速度 (ns) | 消費電力                             |     |                             |     |

|------------|-----|------------------|---------|----------------------------------|-----|-----------------------------|-----|

|            |     |                  |         | 動作時 $I_{CC}$ (mA)<br>$f=f_{max}$ |     | スタンバイ時 $I_{SB2}$ ( $\mu$ A) |     |

|            |     |                  |         | Typ <sup>[1]</sup>               | Max | Typ <sup>[1]</sup>          | Max |

| CY62157G18 | 産業用 | 1.65V ~ 2.2V     | 55      | 18                               | 22  | 2.0                         | 8   |

| CY62157G30 | 産業用 | 2.2V ~ 3.6V      | 45      | 18                               | 25  | 1.4                         | 6.5 |

注 :

1. Typ 値は単に参考値であり、保証またはテストされていません。Typ 値は、 $V_{CC}=3V$  (2.2V ~ 3.6V の  $V_{CC}$  の範囲)、 $V_{CC}=1.8V$  (1.65V ~ 2.2V の  $V_{CC}$  の範囲)、 $T_A=25^\circ C$  で測定しています。

### 論理ブロック ダイヤグラム – CY62157G

### 論理ブロック ダイヤグラム – CY62157GE

## 目次

|                                 |    |

|---------------------------------|----|

| ピン配置 .....                      | 4  |

| 最大定格 .....                      | 6  |

| 動作範囲 .....                      | 6  |

| DC 電気的特性 .....                  | 6  |

| 静電容量 .....                      | 7  |

| 熱抵抗 .....                       | 7  |

| AC テストの負荷と波形 .....              | 8  |

| データ保持特性 .....                   | 8  |

| データ保持波形 .....                   | 9  |

| スイッチング特性 .....                  | 10 |

| スイッチング波形 .....                  | 11 |

| 真理値表 – CY62157G/CY62157GE ..... | 16 |

| ERR 出力 – CY62157GE .....        | 16 |

|                            |    |

|----------------------------|----|

| 注文情報 .....                 | 17 |

| 注文コードの定義 .....             | 17 |

| パッケージ図 .....               | 18 |

| 略語 .....                   | 21 |

| 本書の表記法 .....               | 21 |

| 測定単位 .....                 | 21 |

| 改訂履歴 .....                 | 22 |

| セールス, ソリューションおよび法律情報 ..... | 23 |

| ワールドワイドな販売と設計サポート .....    | 23 |

| 製品 .....                   | 23 |

| PSoC® ソリューション .....        | 23 |

| サイプレス開発者コミュニティ .....       | 23 |

| テクニカル サポート .....           | 23 |

## ピン配置

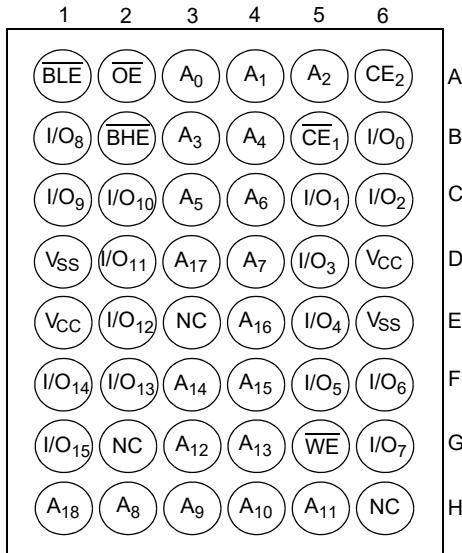

図 1. 48 ポール VFBGA ピン配置 ( 上面図 )<sup>[2]</sup>

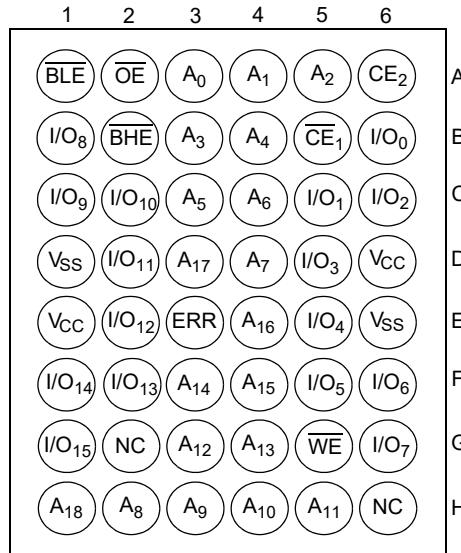

図 2. 48 ポール VFBGA ピン配置 (ERR 付き ( 上面図 ))<sup>[2]</sup>

図 3. 44 ピン TSOP II ピン配置 ( 上面図 )<sup>[2]</sup>

|                  |    |    |                   |

|------------------|----|----|-------------------|

| A <sub>4</sub>   | 1  | 44 | A <sub>5</sub>    |

| A <sub>3</sub>   | 2  | 43 | A <sub>6</sub>    |

| A <sub>2</sub>   | 3  | 42 | A <sub>7</sub>    |

| A <sub>1</sub>   | 4  | 41 | OE                |

| A <sub>0</sub>   | 5  | 40 | BHE               |

| CE               | 6  | 39 | BLE               |

| I/O <sub>0</sub> | 7  | 38 | I/O <sub>15</sub> |

| I/O <sub>1</sub> | 8  | 37 | I/O <sub>14</sub> |

| I/O <sub>2</sub> | 9  | 36 | I/O <sub>13</sub> |

| I/O <sub>3</sub> | 10 | 35 | I/O <sub>12</sub> |

| V <sub>CC</sub>  | 11 | 34 | V <sub>SS</sub>   |

| V <sub>SS</sub>  | 12 | 33 | V <sub>CC</sub>   |

| I/O <sub>4</sub> | 13 | 32 | I/O <sub>11</sub> |

| I/O <sub>5</sub> | 14 | 31 | I/O <sub>10</sub> |

| I/O <sub>6</sub> | 15 | 30 | I/O <sub>9</sub>  |

| I/O <sub>7</sub> | 16 | 29 | I/O <sub>8</sub>  |

| WE               | 17 | 28 | A <sub>8</sub>    |

| A <sub>18</sub>  | 18 | 27 | A <sub>9</sub>    |

| A <sub>17</sub>  | 19 | 26 | A <sub>10</sub>   |

| A <sub>16</sub>  | 20 | 25 | A <sub>11</sub>   |

| A <sub>15</sub>  | 21 | 24 | A <sub>12</sub>   |

| A <sub>14</sub>  | 22 | 23 | A <sub>13</sub>   |

注 :

- NC ピンは内部でダイに接続されておらず、より容量の高いデバイスでのアドレス拡張用に使用されます。ピン配置についてはそれぞれのデータシートを参照してください。

## ピン配置( 続き )

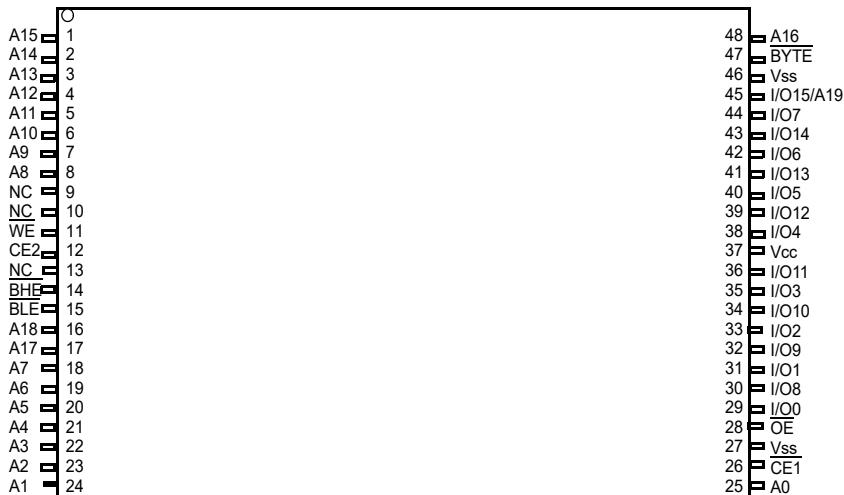

図 4.48 ピン TSOP I ピン配置(上面図)<sup>[3, 4]</sup>

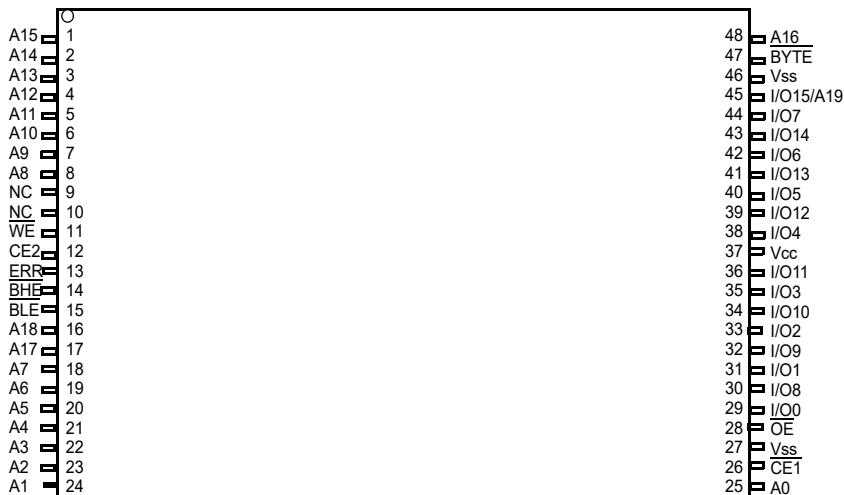

図 5.48 ピン TSOP I ピン配置(上面図)<sup>(ERR付き)</sup><sup>[3, 4]</sup>

### 注:

3. NC ピンは内部でダイに接続されておらず、より容量の高いデバイスでのアドレス拡張用に使用されます。ピン配置についてはそれぞれのデータシートを参照してください。

4. デバイスを 512K×16 SRAM として使用するためには、48 ピン TSOP I パッケージ内の BYTE ピンを V<sub>CC</sub> に接続します。48 ピン TSOP I パッケージは、V<sub>SS</sub> に BYTE 信号を接続することにより 1M×8 SRAM としても使用できます。1M×8 構成の SRAM においては、ピン 45 は余分なアドレスライン A19 であり、一方 BHE、BLE および I/O<sub>8</sub> ~ I/O<sub>14</sub> ピンは未使用であり、開放のままにできます。

## 最大定格

|                                                       |                               |

|-------------------------------------------------------|-------------------------------|

| 最大定格を超えるとデバイスの寿命が短くなる可能性があります。ユーザー ガイドラインはテストされていません。 |                               |

| 保存温度                                                  | -65°C ~ +150°C                |

| 通電時の周囲温度                                              | -55°C ~ +125°C                |

| グランド電位に対する電源電圧                                        | -0.2V ~ V <sub>CC</sub> +0.3V |

| High-Z 状態の DC 出力<br>に印加される電圧 [5]                      | -0.2V ~ V <sub>CC</sub> +0.3V |

| DC 入力電圧 [5]                                           | -0.2V ~ V <sub>CC</sub> +0.3V |

| 出力 (LOW) への出力電流                                       | 20mA                          |

## DC 電気的特性

-40°C ~ 85°C の動作範囲において

| パラメーター                          | 説明                                                   | テスト条件                                                                                                                                                                                                                                                 | 45 / 55ns         |         |                      | 単位 |    |

|---------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------|----------------------|----|----|

|                                 |                                                      |                                                                                                                                                                                                                                                       | Min               | Typ [6] | Max                  |    |    |

| V <sub>OH</sub>                 | 出力 HIGH 電圧                                           | 1.65V ~ 2.2V V <sub>CC</sub> =Min、I <sub>OH</sub> =-0.1mA                                                                                                                                                                                             | 1.4               | -       | -                    | V  |    |

|                                 |                                                      | 2.2V ~ 2.7V V <sub>CC</sub> =Min、I <sub>OH</sub> =-0.1mA                                                                                                                                                                                              | 2                 | -       | -                    |    |    |

|                                 |                                                      | 2.7V ~ 3.6V V <sub>CC</sub> =Min、I <sub>OH</sub> =-1.0mA                                                                                                                                                                                              | 2.4               | -       | -                    |    |    |

| V <sub>OL</sub>                 | 出力 LOW 電圧                                            | 1.65V ~ 2.2V V <sub>CC</sub> =Min、I <sub>OL</sub> =0.1mA                                                                                                                                                                                              | -                 | -       | 0.2                  | V  |    |

|                                 |                                                      | 2.2V ~ 2.7V V <sub>CC</sub> = Min、I <sub>OL</sub> = 0.1mA                                                                                                                                                                                             | -                 | -       | 0.4                  |    |    |

|                                 |                                                      | 2.7V ~ 3.6V V <sub>CC</sub> = Min、I <sub>OL</sub> = 2.1mA                                                                                                                                                                                             | -                 | -       | 0.4                  |    |    |

| V <sub>IH</sub>                 | 入力 HIGH 電圧                                           | 1.65V ~ 2.2V -                                                                                                                                                                                                                                        | 1.4               | -       | V <sub>CC</sub> +0.2 | V  |    |

|                                 |                                                      | 2.2V ~ 2.7V -                                                                                                                                                                                                                                         | 1.8               | -       | V <sub>CC</sub> +0.3 |    |    |

|                                 |                                                      | 2.7V ~ 3.6V -                                                                                                                                                                                                                                         | 2                 | -       | V <sub>CC</sub> +0.3 |    |    |

| V <sub>IL</sub>                 | 入力 LOW 電圧 [6]                                        | 1.65V ~ 2.2V -                                                                                                                                                                                                                                        | -0.2              | -       | 0.4                  | V  |    |

|                                 |                                                      | 2.2V ~ 2.7V -                                                                                                                                                                                                                                         | -0.3              | -       | 0.6                  |    |    |

|                                 |                                                      | 2.7V ~ 3.6V -                                                                                                                                                                                                                                         | -0.3              | -       | 0.8                  |    |    |

| I <sub>IX</sub>                 | 入力リード電流                                              | GND≤V <sub>IN</sub> ≤V <sub>CC</sub>                                                                                                                                                                                                                  | -1                | -       | +1                   | μA |    |

| I <sub>OZ</sub>                 | 出力リード電流                                              | GND≤V <sub>OUT</sub> ≤V <sub>CC</sub> 、出力無効                                                                                                                                                                                                           | -1                | -       | +1                   |    |    |

| I <sub>CC</sub>                 | V <sub>CC</sub> の動作時供給電流                             | V <sub>CC</sub> =Max、I <sub>OUT</sub> =0mA、CMOS レベル                                                                                                                                                                                                   | f=22.22MHz (45ns) | -       | 18                   | 25 | mA |

|                                 |                                                      |                                                                                                                                                                                                                                                       | f=18.18MHz (55ns) | -       | 18                   | 22 |    |

|                                 |                                                      |                                                                                                                                                                                                                                                       | f=1MHz            | -       | 6                    | 7  |    |

| I <sub>SB1</sub> <sup>[7]</sup> | 自動パワーダウン モード時電流、CMOS 入力、V <sub>CC</sub> =2.2 ~ 3.6V  | CE <sub>1</sub> ≥V <sub>CC</sub> -0.2V または CE <sub>2</sub> ≤0.2V、BHE と BLE≥V <sub>CC</sub> -0.2V、V <sub>IN</sub> ≥V <sub>CC</sub> -0.2V、V <sub>IN</sub> ≤0.2V、f=f <sub>max</sub> ( アドレスとデータのみ )、f=0 (OE および WE)、V <sub>CC</sub> =V <sub>CC(max)</sub> | -                 | 1.4     | 6.5                  | μA |    |

|                                 | 自動パワーダウン モード時電流、CMOS 入力、V <sub>CC</sub> =1.65 ~ 2.2V |                                                                                                                                                                                                                                                       | -                 | 2.0     | 8.0                  |    |    |

注 :

5. 20ns 未満のパルス幅の場合、V<sub>IL(min)</sub>=-2.0V、V<sub>IH(max)</sub>=V<sub>CC</sub>+2V。

6. Typ 値は単に参考値であり、保証またはテストされていません。Typ 値は、V<sub>CC</sub>=3V (2.2V ~ 3.6V の V<sub>CC</sub> の範囲)、V<sub>CC</sub>=1.8V (1.65V ~ 2.2V の V<sub>CC</sub> の範囲)、T<sub>A</sub>=25°C で測定しています。

7. I<sub>SB1</sub> / I<sub>SB2</sub> / I<sub>CCDR</sub> の仕様を満たすために、チップ イネーブル (CE<sub>1</sub> および CE<sub>2</sub>) は CMOS レベルに接続する必要があります。他の入力は開放のままにできます。

8. 25°C、40°C、70°C、および一般的に 85°C で制限される I<sub>SB2</sub> は、設計保証されており、実際には 100% テストされていません。

## DC 電気的特性( 続き )

-40°C ~ 85°C の動作範囲において

| パラメーター                   | 説明                                               | テスト条件                                                                                                                                                                                          | 45 / 55ns           |         |     | 単位      |

|--------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|-----|---------|

|                          |                                                  |                                                                                                                                                                                                | Min                 | Typ [6] | Max |         |

| $I_{SB2}$ <sup>[7]</sup> | 自動パワーダウン モード時電流、CMOS 入力、 $V_{CC}=2.2 \sim 3.6V$  | $\overline{CE}_1 \geq V_{CC}-0.2V$ または $CE_2 \leq 0.2V$ 、<br>$BHE$ と $\overline{BLE} \geq V_{CC}-0.2V$ 、<br>$V_{IN} \geq V_{CC}-0.2V$ または $V_{IN} \leq 0.2V$ 、<br>$f=0$ 、 $V_{CC}=V_{CC(max)}$ | 25°C <sup>[8]</sup> | —       | 1.4 | 2.8     |

|                          |                                                  | 40°C <sup>[8]</sup>                                                                                                                                                                            | —                   | —       | 3.5 |         |

|                          |                                                  | 70°C <sup>[8]</sup>                                                                                                                                                                            | —                   | —       | 5.5 |         |

|                          |                                                  | 85°C                                                                                                                                                                                           | —                   | —       | 6.5 |         |

|                          | 自動パワーダウン モード時電流、CMOS 入力、 $V_{CC}=1.65 \sim 2.2V$ | $\overline{CE}_1 \geq V_{CC}-0.2V$ または $CE_2 \leq 0.2V$ 、<br>$BHE$ と $\overline{BLE} \geq V_{CC}-0.2V$ 、<br>$V_{IN} \geq V_{CC}-0.2V$ または $V_{IN} \leq 0.2V$ 、<br>$f=0$ 、 $V_{CC}=V_{CC(max)}$ | —                   | 2.0     | 8.0 | $\mu A$ |

注 :

5. 20ns 未満のパルス幅の場合、 $V_{IL(min)}=-2.0V$ 、 $V_{IH(max)}=V_{CC}+2V$ 。

6. Typ 値は単に参考値であり、保証またはテストされていません。Typ 値は、 $V_{CC}=3V$  (2.2V ~ 3.6V の  $V_{CC}$  の範囲)、 $V_{CC}=1.8V$  (1.65V ~ 2.2V の  $V_{CC}$  の範囲)、 $T_A=25^\circ C$  で測定しています。

7.  $I_{SB1} / I_{SB2} / I_{CCDR}$  の仕様を満たすために、チップ イネーブル ( $\overline{CE}_1$  および  $CE_2$ ) は CMOS レベルに接続する必要があります。他の入力は開放のままにできます。

8. 25°C、40°C、70°C、および一般的に 85°C で制限される  $I_{SB2}$  は、設計保証されており、実際には 100% テストされていません。

## 静電容量

| パラメーター <sup>[9]</sup> | 説明     | テスト条件                                              | Max | 単位   |

|-----------------------|--------|----------------------------------------------------|-----|------|

| $C_{IN}$              | 入力静電容量 | $T_A=25^\circ C$ 、 $f=1MHz$ 、 $V_{CC}=V_{CC(typ)}$ | 10  | $pF$ |

| $C_{OUT}$             | 出力静電容量 |                                                    | 10  |      |

## 熱抵抗

| パラメーター <sup>[9]</sup> | 説明                | テスト条件                             | 48 ピン TSOP I | 48 ポール VFBGA | 44 ピン TSOP II | 単位           |

|-----------------------|-------------------|-----------------------------------|--------------|--------------|---------------|--------------|

| $\Theta_{JA}$         | 熱抵抗<br>(接合部から周囲)  | 無風状態、3×4.5 インチの 4 層プリント回路基板にはんだ付け | 60.07        | 36.92        | 65.91         | $^\circ C/W$ |

| $\Theta_{JC}$         | 熱抵抗<br>(接合部からケース) |                                   | 9.73         | 13.55        | 13.96         |              |

注 :

9. 開発時、およびこれらのパラメーターに影響を与える可能性がある設計／プロセス変更後にテストされます。

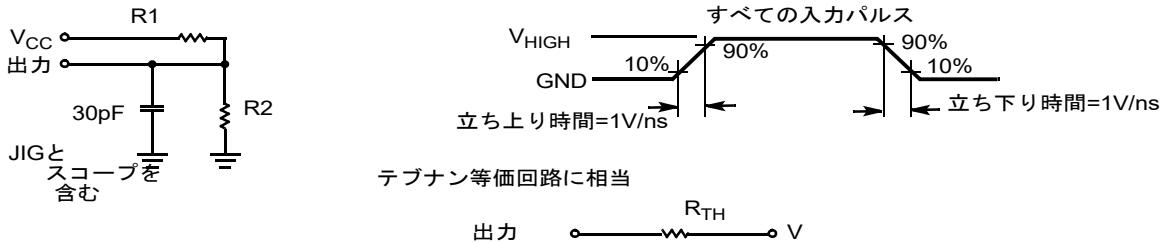

## AC テストの負荷と波形

図 6. AC テストの負荷と波形

| パラメーター   | 1.8V  | 2.5V  | 3.0V | 単位       |

|----------|-------|-------|------|----------|

| R1       | 13500 | 16667 | 1103 | $\Omega$ |

| R2       | 10800 | 15385 | 1554 |          |

| $R_{TH}$ | 6000  | 8000  | 645  |          |

| $V_{TH}$ | 0.8   | 1.20  | 1.75 | V        |

## データ保持特性

動作範囲において

| パラメーター                                                | 説明                           | 条件                                                                                                                                                                                                                                           | Min                       | Typ <sup>[15]</sup> | Max | 単位      |

|-------------------------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------|-----|---------|

| $V_{DR}$                                              | データ保持用の $V_{CC}$             |                                                                                                                                                                                                                                              | 1                         | -                   | -   | V       |

| $I_{CCDR}^{[11, 12]}$<br>データ保持電流<br>(3.3V Typ デバイス向け) |                              | $\overline{CE}_1 \geq V_{CC} - 0.2V$ または $\overline{CE}_2 \leq 0.2V$ 、<br>$\overline{BHE} \geq V_{CC} - 0.2V$ または $\overline{BLE} \geq V_{CC} - 0.2V$ 、<br>$V_{IN} \geq V_{CC} - 0.2V$ または $V_{IN} \leq 0.2V$                                | $V_{CC} = 1.2V$           | -                   | 4.0 | 9.0     |

|                                                       |                              | $\overline{CE}_1 \geq V_{CC} - 0.2V$ または $\overline{CE}_2 \leq 0.2V$ 、<br>$\overline{BHE} \geq V_{CC} - 0.2V$ または $\overline{BLE} \geq V_{CC} - 0.2V$ 、<br>$V_{IN} \geq V_{CC} - 0.2V$ または $V_{IN} \leq 0.2V$                                | $V_{CC} = 1.5V$           | -                   | 3.2 | 8.0     |

|                                                       |                              | $\overline{CE}_1 \geq V_{CC} - 0.2V$ または $\overline{CE}_2 \leq 0.2V$ 、<br>$\overline{BHE} \geq V_{CC} - 0.2V$ または $\overline{BLE} \geq V_{CC} - 0.2V$ 、<br>$V_{IN} \geq V_{CC} - 0.2V$ または $V_{IN} \leq 0.2V$                                | $2.2V < V_{CC} \leq 3.6V$ | -                   | 1.4 | 6.5     |

| $I_{CCDR}^{[11, 12]}$                                 | データ保持電流<br>(1.8V Typ デバイス向け) | $1.2V < V_{CC} \leq 2.2V$ 、<br>$\overline{CE}_1 \geq V_{CC} - 0.2V$ または $\overline{CE}_2 \leq 0.2V$ 、<br>$\overline{BHE} \geq V_{CC} - 0.2V$ または $\overline{BLE} \geq V_{CC} - 0.2V$ 、<br>$V_{IN} \geq V_{CC} - 0.2V$ または $V_{IN} \leq 0.2V$ | -                         | 5.0                 | 9.0 | $\mu A$ |

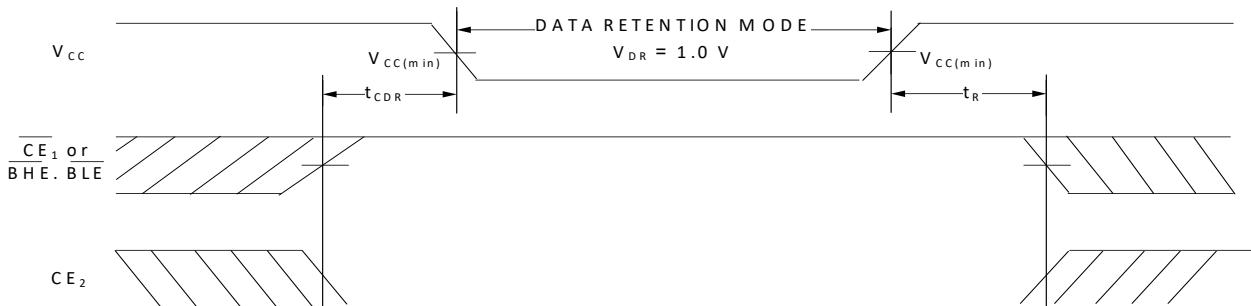

| $t_{CDR}^{[13]}$                                      | チップ選択解除からデータ保持までの時間          | -                                                                                                                                                                                                                                            | 0                         | -                   | -   | -       |

| $t_R^{[14]}$                                          | 動作回復時間                       | -                                                                                                                                                                                                                                            | 45 / 55                   | -                   | -   | ns      |

注 :

10. Typ 値は単に参考値であり、保証またはテストされていません。Typ 値は、 $V_{CC}=3V$  (2.2V ~ 3.6V の  $V_{CC}$  の範囲)、 $T_A=25^\circ C$  で測定しています。

11.  $I_{SB1}$  /  $I_{SB2}$  /  $I_{CCDR}$  の仕様を満たすために、チップイネーブル ( $\overline{CE}_1$  および  $\overline{CE}_2$ ) は CMOS レベルに接続する必要があります。他の入力は開放のままにできます。

12.  $I_{CCDR}$  は、デバイスが最初に  $V_{CC(min)}$  まで電源投入され、その後  $V_{DR}$  に下げられた後でのみ保証されています。

13. 開発時、およびこれらのパラメーターに影響を与える可能性がある設計／プロセス変更後にテストされます。

14. 完全なデバイス動作には、 $V_{DR}$  から  $V_{CC(min)}$  までのリニア  $V_{CC}$  ランプ  $\geq 100\mu s$  か、または  $V_{CC(min)}$  の安定時間  $\geq 100\mu s$  であることが必要です。

## データ保持波形

図 7. データ保持波形<sup>[15]</sup>

注:

15.  $\overline{BHE} \cdot \overline{BLE}$  は  $\overline{BHE}$  と  $\overline{BLE}$  の論理積です。チップを選択解除するために、チップイネーブル信号を無効にするか、または  $\overline{BHE}$  と  $\overline{BLE}$  の両方を無効にします。

## スイッチング特性

| パラメーター <sup>[16]</sup>              | 説明                                                                          | 45ns |     | 55ns |     | 単位 |

|-------------------------------------|-----------------------------------------------------------------------------|------|-----|------|-----|----|

|                                     |                                                                             | Min  | Max | Min  | Max |    |

| <b>読み出しサイクル</b>                     |                                                                             |      |     |      |     |    |

| $t_{RC}$                            | 読み出しサイクル時間                                                                  | 45   | —   | 55   | —   | ns |

| $t_{AA}$                            | アドレスからデータ有効までの時間／アドレス LOW から ERR 有効までの時間                                    | —    | 45  | —    | 55  |    |

| $t_{OHA}$                           | アドレス変更からのデータホールド時間                                                          | 10   | —   | 10   | —   |    |

| $t_{ACE}$                           | $\overline{CE}_1$ LOW および $CE_2$ HIGH からデータ有効までの時間／ $CE$ LOW から ERR 有効までの時間 | —    | 45  | —    | 55  |    |

| $t_{DOE}$                           | $\overline{OE}$ LOW からデータ有効までの時間／ $\overline{OE}$ LOW から ERR 有効までの時間        | —    | 22  | —    | 25  |    |

| $t_{LZOE}$                          | $\overline{OE}$ LOW から Low-Z までの時間 <sup>[17]</sup>                          | 5    | —   | 5    | —   |    |

| $t_{HZOE}$                          | $\overline{OE}$ HIGH から High-Z までの時間 <sup>[17, 18]</sup>                    | —    | 18  | —    | 18  |    |

| $t_{LZCE}$                          | $\overline{CE}_1$ LOW および $CE_2$ HIGH から Low-Z までの時間 <sup>[17]</sup>        | 10   | —   | 10   | —   |    |

| $t_{HZCE}$                          | $\overline{CE}_1$ HIGH および $CE_2$ LOW から High-Z までの時間 <sup>[17, 18]</sup>   | —    | 18  | —    | 18  |    |

| $t_{PU}$                            | $\overline{CE}_1$ LOW および $CE_2$ HIGH から電源投入までの時間                           | 0    | —   | 0    | —   |    |

| $t_{PD}$                            | $\overline{CE}_1$ HIGH および $CE_2$ LOW から電源切断までの時間                           | —    | 45  | —    | 55  |    |

| $t_{DBE}$                           | BLE / BHE LOW からデータ有効までの時間                                                  | —    | 45  | —    | 55  |    |

| $t_{LZBE}$                          | BLE / BHE LOW から Low-Z までの時間 <sup>[17]</sup>                                | 5    | —   | 5    | —   |    |

| $t_{HZBE}$                          | BLE / BHE HIGH から High-Z までの時間 <sup>[17, 18]</sup>                          | —    | 18  | —    | 18  |    |

| <b>書き込みサイクル</b> <sup>[19, 20]</sup> |                                                                             |      |     |      |     |    |

| $t_{WC}$                            | 書き込みサイクル時間                                                                  | 45   | —   | 55   | —   | ns |

| $t_{SCE}$                           | $\overline{CE}_1$ LOW および $CE_2$ HIGH から書き込み終了までの時間                         | 35   | —   | 40   | —   |    |

| $t_{AW}$                            | アドレスセットアップから書き込み終了までの時間                                                     | 35   | —   | 40   | —   |    |

| $t_{HA}$                            | 書き込み終了からのアドレスホールド時間                                                         | 0    | —   | 0    | —   |    |

| $t_{SA}$                            | アドレスセットアップから書き込み開始までの時間                                                     | 0    | —   | 0    | —   |    |

| $t_{PWE}$                           | $\overline{WE}$ パルス幅                                                        | 35   | —   | 40   | —   |    |

| $t_{BW}$                            | BLE / BHE LOW から書き込み終了までの時間                                                 | 35   | —   | 40   | —   |    |

| $t_{SD}$                            | データセットアップから書き込み終了までの時間                                                      | 25   | —   | 25   | —   |    |

| $t_{HD}$                            | 書き込み終了からのデータホールド時間                                                          | 0    | —   | 0    | —   |    |

| $t_{HZWE}$                          | $\overline{WE}$ LOW から High-Z までの時間 <sup>[17, 18]</sup>                     | —    | 18  | —    | 20  |    |

| $t_{LZWE}$                          | $\overline{WE}$ HIGH から Low-Z までの時間 <sup>[17]</sup>                         | 10   | —   | 10   | —   |    |

注：

16. テスト条件は、信号遷移時間（立ち上り／立ち下り）が 3ns 以下、タイミング参照レベルが  $V_{CC} \geq 3V$  の場合）および  $V_{CC}/2$  ( $V_{CC} < 3V$  の場合）、入力パルスレベルが 0V から 3V まで ( $V_{CC} \geq 3V$  の場合) および 0V から  $V_{CC}$  まで ( $V_{CC} < 3V$  の場合) であることを前提としています。特に指定しない限り、読み出しサイクルのためのテスト条件は「AC テストの負荷と波形」に示されている出力負荷を使います。

17. いかなる温度と電圧条件でも、いかなるデバイスでも、 $t_{HZCE}$  は  $t_{LZCE}$  より短く、 $t_{HZBE}$  は  $t_{LZBE}$  より短く、 $t_{HZOE}$  は  $t_{LZOE}$  より短く、 $t_{HZWE}$  は  $t_{LZWE}$  より短いです。

18.  $t_{HZOE}$ 、 $t_{HZCE}$ 、 $t_{HZBE}$  および  $t_{HZWE}$  の遷移は、出力が高インピーダンス状態に入ると測定されます。

19. メモリの内部書き込み時間は  $\overline{WE}=V_{IL}$ 、 $\overline{CE}_1=V_{IL}$ 、 $\overline{BHE}$  または  $\overline{BLE}$  または両方とも  $=V_{IL}$  および  $CE_2=V_{IH}$  の条件が同時に発生するときに定義されます。書き込みを開始するために、すべての信号はアクティブでなければなりません。これらの信号のいずれかが非アクティブになると書き込みが終了します。データ入力のセットアップとホールドのタイミングは、書き込みを終了させる信号のエッジを参照しなければなりません。

20. 書き込みサイクル 1 ( $\overline{WE}$  制御、 $\overline{OE}$  LOW) 用の最小の書き込みサイクルパルス幅は、 $t_{HZWE}$  と  $t_{SD}$  の和です。

## スイッチング波形

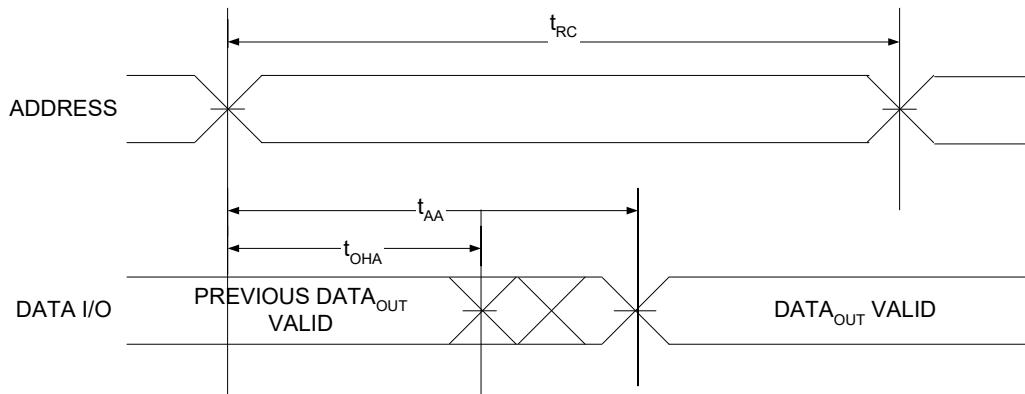

図 8. CY62157G の読み出しサイクル 1 (アドレス遷移制御) [21、22]

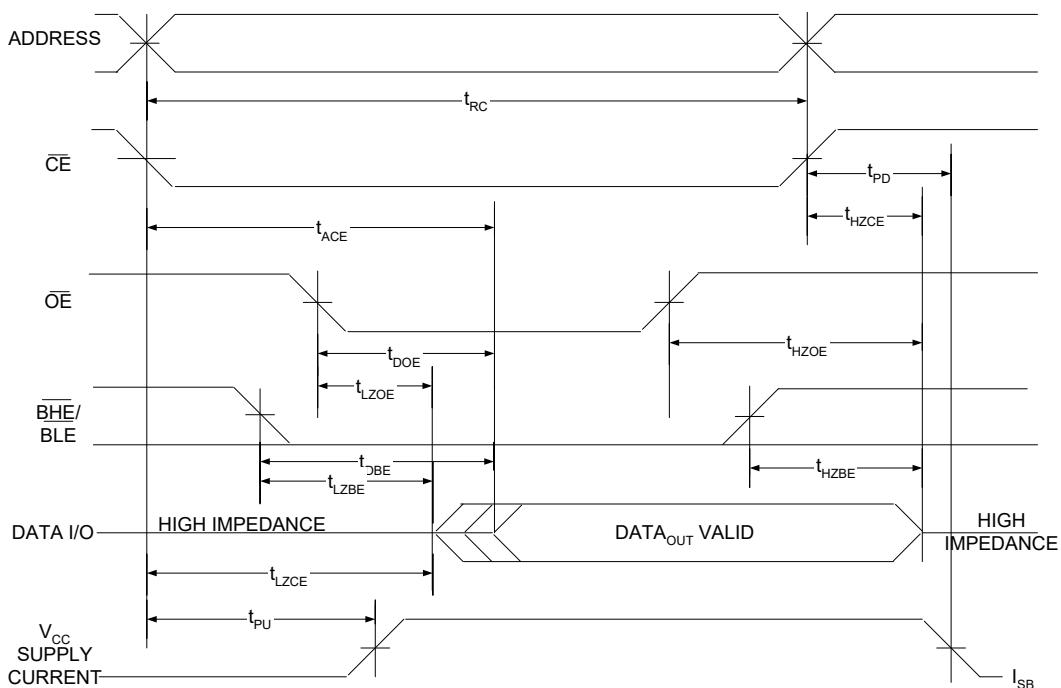

図 9. 読み出しサイクル 2 ( $\overline{OE}$  制御) [22、23、24]

注:

21. デバイスは継続して選択されています。 $\overline{OE} = V_{IL}$ 、 $\overline{CE} = V_{IL}$ 、 $\overline{BHE}$  または  $\overline{BLE}$  または両方とも =  $V_{IL}$ 。

22. 読み出しサイクルの間、 $\overline{WE}$  は HIGH です。

23. すべてのデュアル チップ イネーブル デバイスでは、 $\overline{CE}$  は  $\overline{CE}_1$  と  $CE_2$  の論理結合です。 $\overline{CE}_1$  が LOW で  $CE_2$  が HIGH の場合、 $\overline{CE}$  は LOW です。 $\overline{CE}_1$  が HIGH または  $CE_2$  が LOW の場合、 $\overline{CE}$  は HIGH です。

24. アドレスは  $\overline{CE}$  の LOW 遷移前、または遷移と同時に有効です。

## スイッチング波形 ( 続き )

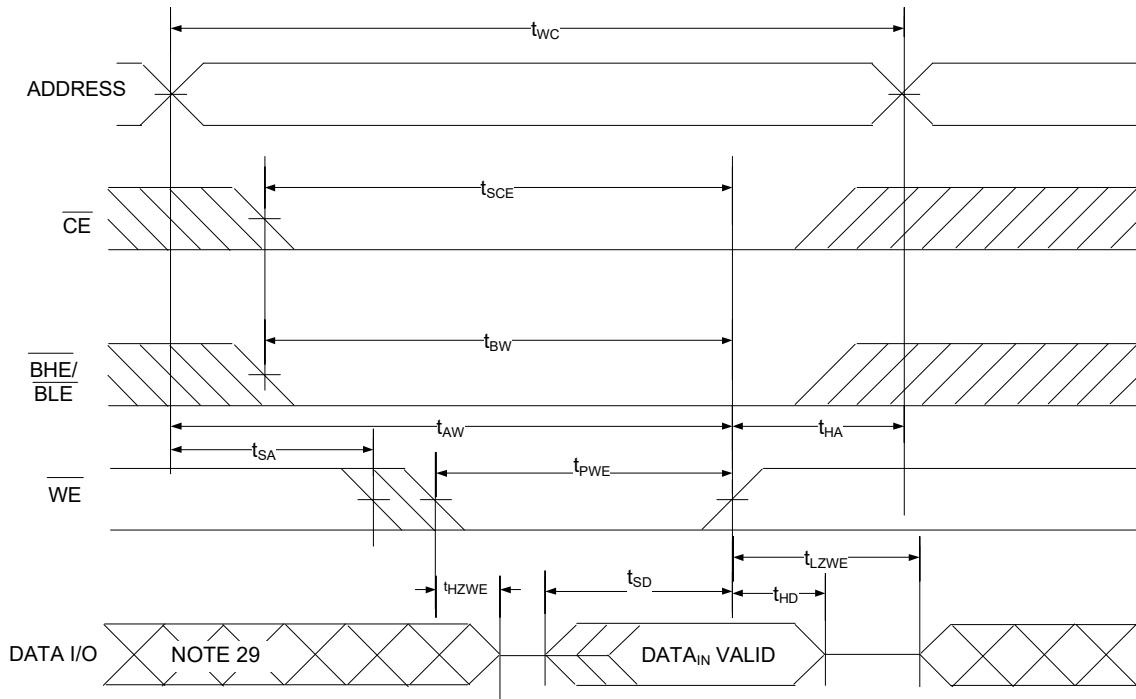

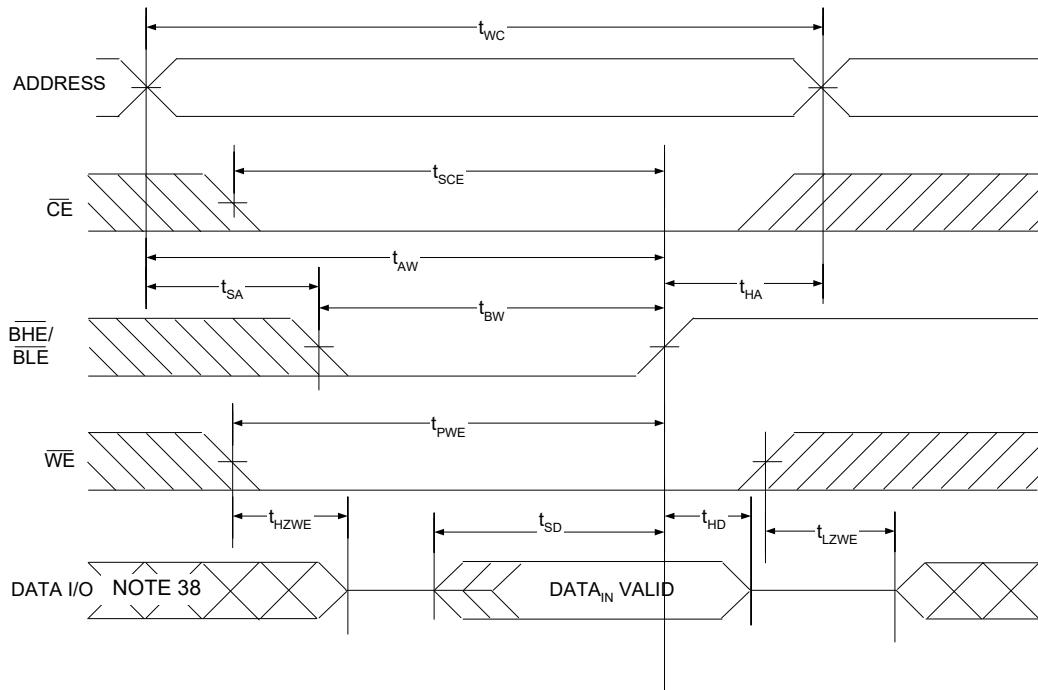

図 10. 書き込みサイクル 1 ( $\overline{WE}$  制御、 $\overline{OE}$  LOW) [25, 26, 27, 28]

### 注:

25. すべてのデュアル チップ イネーブル デバイスでは、 $\overline{CE}$  は  $\overline{CE}_1$  と  $CE_2$  の論理結合です。 $\overline{CE}_1$  が LOW で  $CE_2$  が HIGH の場合、 $\overline{CE}$  は LOW です。 $\overline{CE}_1$  が HIGH または  $CE_2$  が LOW の場合、 $\overline{CE}$  は HIGH です。

26. メモリの内部書き込み時間は  $\overline{WE}=V_{IL}$ 、 $\overline{CE}_1=V_{IL}$ 、 $\overline{BHE}$  または  $\overline{BLE}$  または両方とも  $=V_{IL}$  および  $CE_2=V_{IH}$  の条件が同時に発生するときに定義されます。書き込みを開始するために、すべての信号はアクティブでなければなりません。これらの信号のいずれかが非アクティブになると書き込みが終了します。データ入力のセットアップとホールドのタイミングは、書き込みを終了させる信号のエッジを参照しなければなりません。

27.  $\overline{CE}=V_{IH}$ 、または  $\overline{OE}=V_{IH}$ 、または  $\overline{BHE}$  および／または  $\overline{BLE}=V_{IH}$  の場合、データ I/O は高インピーダンス状態にあります。

28. 書き込みサイクル 1 ( $\overline{WE}$  制御、 $\overline{OE}$  LOW) 用の最小の書き込みサイクルパルス幅は、 $t_{HZWE}$  と  $t_{SD}$  の和です。

29. この期間中、I/O は出力状態にあります。入力信号を印加しないでください。

## スイッチング波形( 続き )

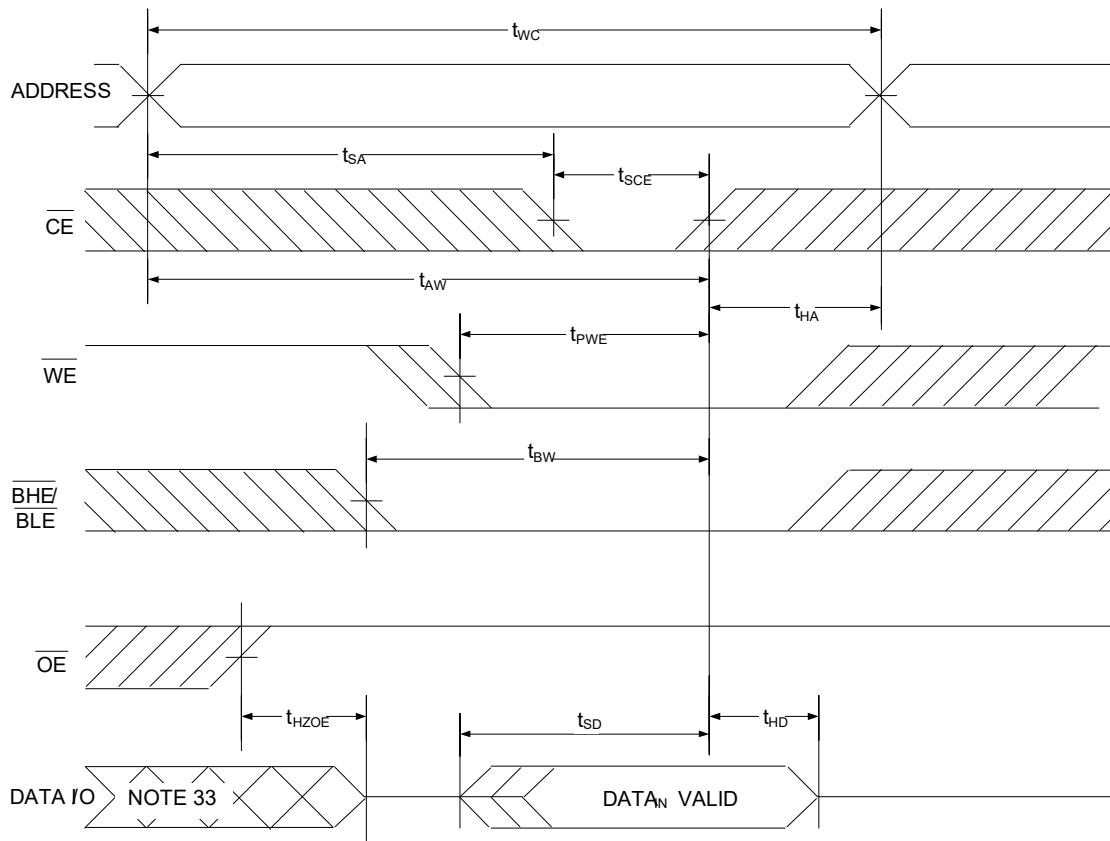

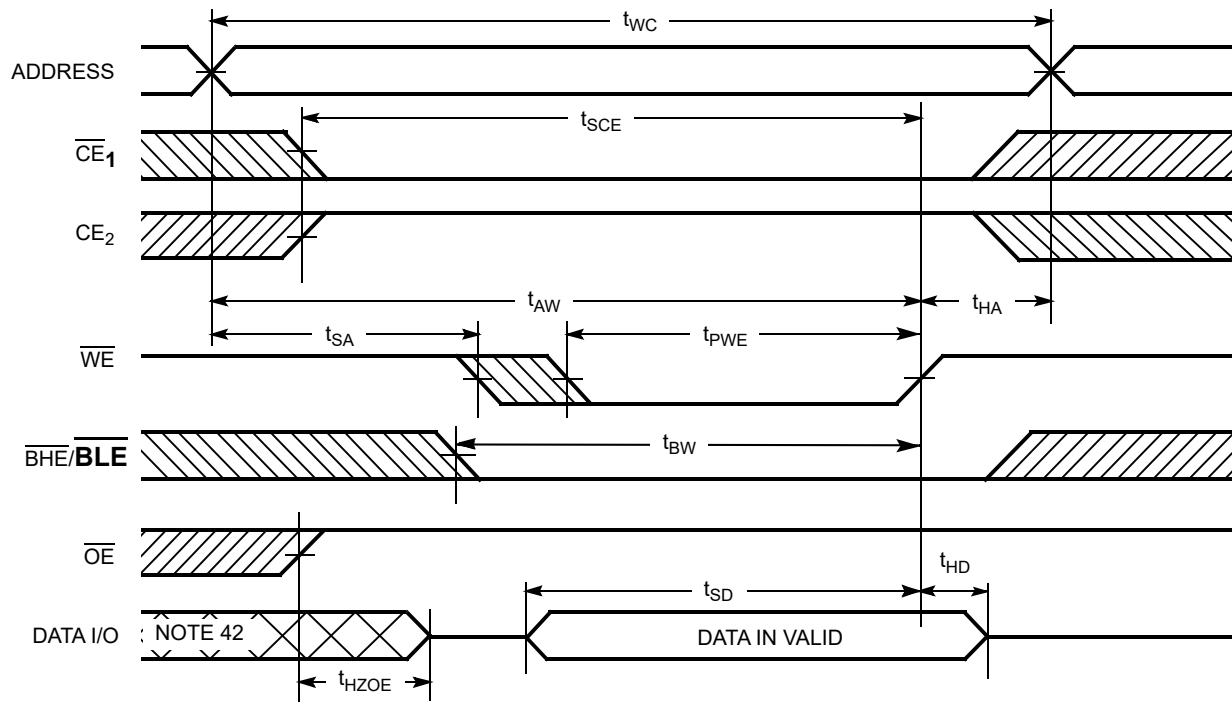

図 11. 書き込みサイクル 2 ( $\overline{CE}$  制御) [30、31、32]

注:

30. すべてのデュアルチップイネーブルデバイスでは、 $\overline{CE}$ は $\overline{CE}_1$ と $CE_2$ の論理結合です。 $\overline{CE}_1$ がLOWで $CE_2$ がHIGHの場合、 $\overline{CE}$ はLOWです。 $\overline{CE}_1$ がHIGHまたは $CE_2$ がLOWの場合、 $\overline{CE}$ はHIGHです。

31. メモリの内部書き込み時間は $\overline{WE}=V_{IL}$ 、 $\overline{CE}_1=V_{IL}$ 、 $\overline{BHE}$ または $\overline{BLE}$ または両方とも $=V_{IL}$ および $CE_2=V_{IH}$ の条件が同時に発生するときに定義されます。書き込みを開始するために、すべての信号はアクティブでなければなりません。これらの信号のいずれかが非アクティブになると書き込みが終了します。データ入力のセットアップとホールドのタイミングは、書き込みを終了させる信号のエッジを参照しなければなりません。

32.  $CE=V_{IH}$ 、または $OE=V_{IH}$ 、または $BHE$ および/または $BLE=V_{IH}$ の場合、データI/Oは高インピーダンス状態にあります。

33. この期間中、I/Oは出力状態にあります。入力信号を印加しないでください。

## スイッチング波形(続き)

図 12. 書き込みサイクル 3 ( $\overline{BHE}$  /  $\overline{BLE}$  制御、 $\overline{OE}$  LOW) [34, 35, 36, 37]

### 注:

34. すべてのデュアル チップ イネーブル デバイスでは、 $\overline{CE}$  は  $\overline{CE}_1$  と  $CE_2$  の論理結合です。 $\overline{CE}_1$  が LOW で  $CE_2$  が HIGH の場合、 $\overline{CE}$  は LOW です。 $\overline{CE}_1$  が HIGH または  $CE_2$  が LOW の場合、 $\overline{CE}$  は HIGH です。

35. メモリの内部書き込み時間は  $\overline{WE}=V_{IL}$ 、 $\overline{CE}_1=V_{IL}$ 、 $\overline{BHE}$  または  $BLE$  または両方とも  $=V_{IL}$  および  $CE_2=V_{IH}$  の条件が同時に発生するときに定義されます。書き込みを開始するために、すべての信号はアクティブでなければなりません。これらの信号のいずれかが非アクティブになると書き込みが終了します。データ入力のセットアップとホールドのタイミングは、書き込みを終了させる信号のエッジを参照しなければなりません。

36.  $\overline{CE}=V_{IH}$ 、または  $\overline{OE}=V_{IH}$ 、または  $BHE$  および／または  $\overline{BLE}=V_{IH}$  の場合、データ I/O は高インピーダンス状態にあります。

37. 書き込みサイクル 3 ( $BHE$  /  $BLE$  制御、 $\overline{OE}$  LOW) 用の最小の書き込みサイクルパルス幅は、 $t_{HZWE}$  と  $t_{SD}$  の和です。

38. この期間中、I/O は出力状態にあります。入力信号を印加しないでください。

## スイッチング波形(続き)

図 13. 書き込みサイクル 4 ( $\overline{WE}$  制御) [39、40、41]

注:

39. メモリの内部書き込み時間は  $\overline{WE}$  と  $\overline{CE}_1=V_{IL}$ ,  $\overline{BHE}$  または  $\overline{BLE}$  または両方とも  $=V_{IL}$  および  $CE_2=V_{IH}$  の条件が同時に発生するときに定義されます。書き込みを開始するために、すべての信号はアクティブでなければなりません。これらの信号のいずれかが非アクティブになると書き込みが終了します。データ入力のセットアップとホールドのタイミングは、書き込みを終了させる信号のエッジを参照しなければなりません。

40.  $\overline{OE}=V_{IH}$  の場合、データ I/O は高インピーダンス状態にあります。

41.  $\overline{WE} = V_{IL}$  と同時に  $\overline{CE}_1$  が HIGH になり、 $CE_2$  が LOW になる場合、出力は高インピーダンス状態のままです。

42. この期間中、I/O は出力状態にあります。入力信号を印加しないでください。

**真理値表 – CY62157G/CY62157GE**

| <b>BYTE</b> [43]  | <b>CE<sub>1</sub></b> | <b>CE<sub>2</sub></b> | <b>WE</b> | <b>OE</b> | <b>BHE</b> | <b>BLE</b> | <b>入力／出力</b>                                                                                  | <b>モード</b>  | <b>消費電流</b>              | <b>コンフィギュレーション</b> |

|-------------------|-----------------------|-----------------------|-----------|-----------|------------|------------|-----------------------------------------------------------------------------------------------|-------------|--------------------------|--------------------|

| X <sup>[44]</sup> | H                     | X <sup>[44]</sup>     | X         | X         | X          | X          | High-Z                                                                                        | 選択解除／パワーダウン | スタンバイ (I <sub>SB</sub> ) | 1M×8 / 512K×16     |

| X                 | X <sup>[44]</sup>     | L                     | X         | X         | X          | X          | High-Z                                                                                        | 選択解除／パワーダウン | スタンバイ (I <sub>SB</sub> ) | 1M×8 / 512K×16     |

| X                 | X <sup>[44]</sup>     | X <sup>[44]</sup>     | X         | X         | H          | H          | High-Z                                                                                        | 選択解除／パワーダウン | スタンバイ (I <sub>SB</sub> ) | 512K×16            |

| H                 | L                     | H                     | H         | L         | L          | L          | データ出力 (I/O <sub>0</sub> ~ I/O <sub>15</sub> )                                                 | 読み出し        | アクティブ (I <sub>CC</sub> ) | 512K×16            |

| H                 | L                     | H                     | H         | L         | H          | L          | データ出力 (I/O <sub>0</sub> ~ I/O <sub>7</sub> ) ; High-Z (I/O <sub>8</sub> ~ I/O <sub>15</sub> ) | 読み出し        | アクティブ (I <sub>CC</sub> ) | 512K×16            |

| H                 | L                     | H                     | H         | L         | L          | H          | High-Z (I/O <sub>0</sub> ~ I/O <sub>7</sub> ) , データ出力 (I/O <sub>8</sub> ~ I/O <sub>15</sub> ) | 読み出し        | アクティブ (I <sub>CC</sub> ) | 512K×16            |

| H                 | L                     | H                     | H         | H         | L          | H          | High-Z                                                                                        | 出力無効        | アクティブ (I <sub>CC</sub> ) | 512K×16            |

| H                 | L                     | H                     | H         | H         | H          | L          | High-Z                                                                                        | 出力無効        | アクティブ (I <sub>CC</sub> ) | 512K×16            |

| H                 | L                     | H                     | H         | H         | L          | L          | High-Z                                                                                        | 出力無効        | アクティブ (I <sub>CC</sub> ) | 512K×16            |

| H                 | L                     | H                     | L         | X         | L          | L          | データ入力 (I/O <sub>0</sub> ~ I/O <sub>15</sub> )                                                 | 書き込み        | アクティブ (I <sub>CC</sub> ) | 512K×16            |

| H                 | L                     | H                     | L         | X         | H          | L          | データ入力 (I/O <sub>0</sub> ~ I/O <sub>7</sub> ) ; High-Z (I/O <sub>8</sub> ~ I/O <sub>15</sub> ) | 書き込み        | アクティブ (I <sub>CC</sub> ) | 512K×16            |

| H                 | L                     | H                     | L         | X         | L          | H          | High-Z (I/O <sub>0</sub> ~ I/O <sub>7</sub> ) ; データ入力 (I/O <sub>8</sub> ~ I/O <sub>15</sub> ) | 書き込み        | アクティブ (I <sub>CC</sub> ) | 512K×16            |

| L                 | L                     | H                     | H         | L         | X          | X          | データ出力 (I/O <sub>0</sub> ~ I/O <sub>7</sub> )                                                  | 読み出し        | アクティブ (I <sub>CC</sub> ) | 1M × 8             |

| L                 | L                     | H                     | H         | H         | X          | X          | High-Z                                                                                        | 出力無効        | アクティブ (I <sub>CC</sub> ) | 1M×8               |

| L                 | L                     | H                     | L         | X         | X          | X          | データ入力 (I/O <sub>0</sub> ~ I/O <sub>7</sub> )                                                  | 書き込み        | アクティブ (I <sub>CC</sub> ) | 1M×8               |

**ERR 出力 – CY62157GE**

| <b>出力</b> [45] | <b>モード</b>                         |

|----------------|------------------------------------|

| 0              | 読み出し動作 - 保存データにはシングルビット エラーはありません。 |

| 1              | 読み出し動作 - シングルビット エラーが検出され、訂正されました。 |

| High-Z         | デバイス選択解除／出力無効／書き込み動作               |

注 :

43. このピンは 48 ピン TSOP I パッケージでのみ利用できます。デバイスを 512K×16 オプションに設定するために、**BYTE** を V<sub>CC</sub> に接続します。

48 ピン TSOP I パッケージは、V<sub>SS</sub> に **BYTE** 信号を接続することにより 1M×8 SRAM としても使用できます。

44. チップ イネーブルの「X」(ドント ケア) 状態は、論理状態 (HIGH または LOW) を意味します。これらのピンでの中間電圧レベルは許可されていません。

45. ERR は出力ピンです。このピンを使用しない場合、開放にしてください。

## 注文情報

| 速度<br>(ns) | 注文コード              | パッケージ図   | パッケージ タイプ                                          | 動作範囲 |  |

|------------|--------------------|----------|----------------------------------------------------|------|--|

| 45         | CY62157G30-45BVXI  | 51-85150 | 48 ボール VFBGA (6×8×1mm) (鉛フリー)、<br>パッケージ コード : BZ48 | 産業用  |  |

|            | CY62157G30-45BVXIT |          |                                                    |      |  |

|            | CY62157GE30-45BVXI |          |                                                    |      |  |

|            | CY62157G30-45ZSXI  | 51-85087 | 44 ピン TSOP II (鉛フリー)                               |      |  |

|            | CY62157G30-45ZXI   | 51-85183 | 48 ピン TSOP I (12×18.4×1.0mm) (鉛フリー)                |      |  |

|            | CY62157GE30-45ZXI  |          |                                                    |      |  |

| 55         | CY62157G18-55BVXI  | 51-85150 | 48 ボール VFBGA (6×8×1mm) (鉛フリー)、<br>パッケージ コード : BZ48 |      |  |

|            | CY62157G18-55BVXIT |          |                                                    |      |  |

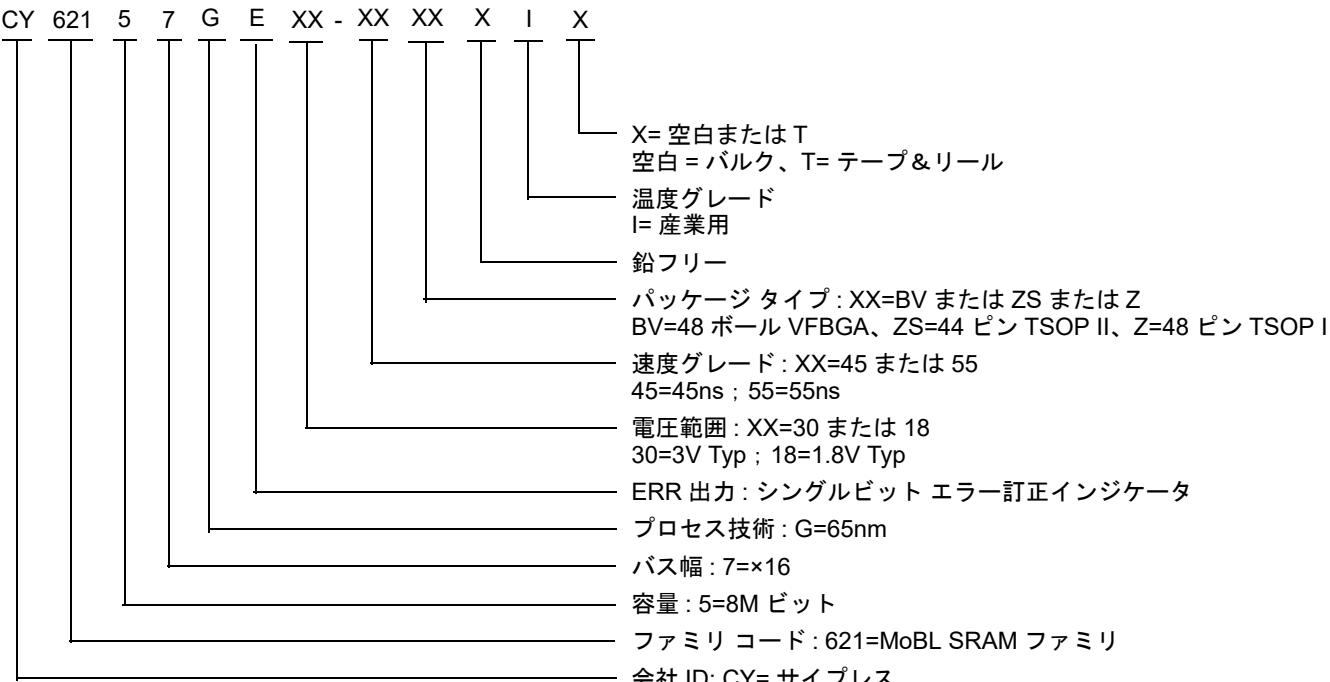

## 注文コードの定義

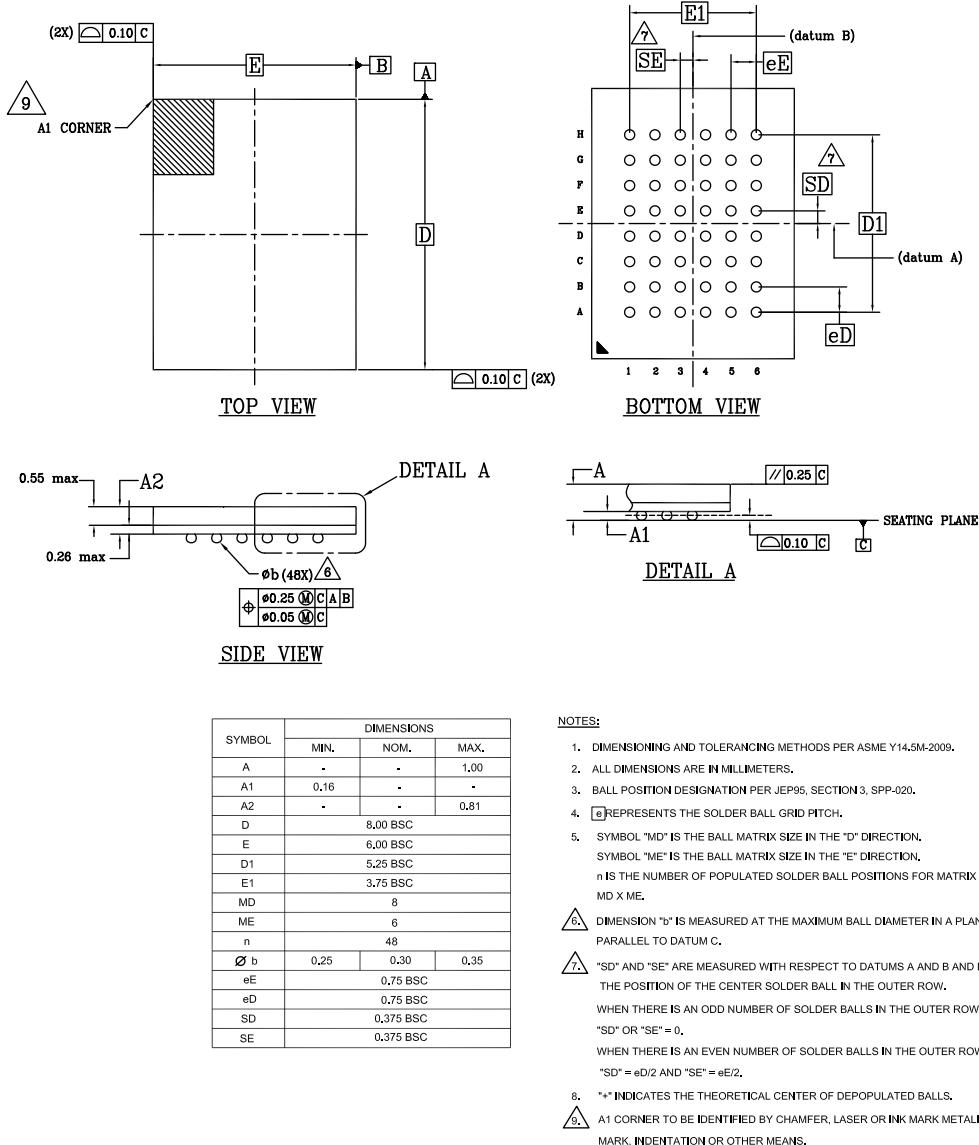

## パッケージ図

図 14. 48 ポール VFBGA (6 × 8 × 1.0 mm) パッケージ外形図、51-85150

51-85150 \*I

## パッケージ図(続き)

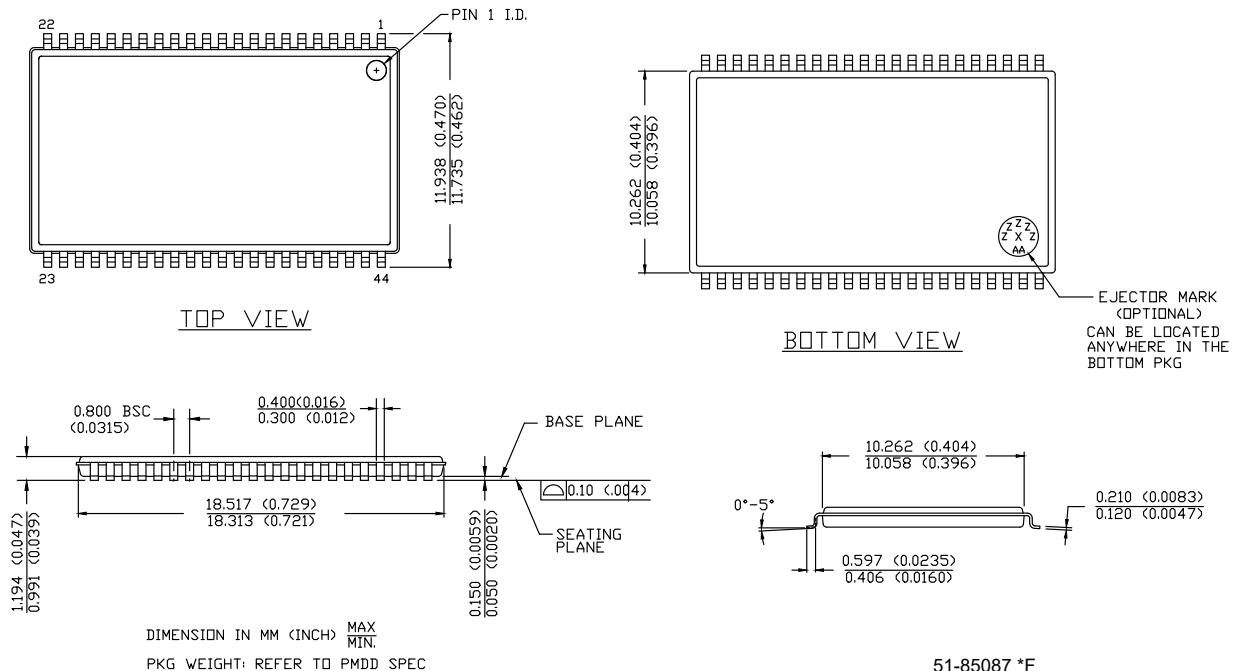

図 15. 44 ピン TSOP II (18.4 × 10.2 × 1.194 mm) パッケージ外形図、51-85087

## パッケージ図(続き)

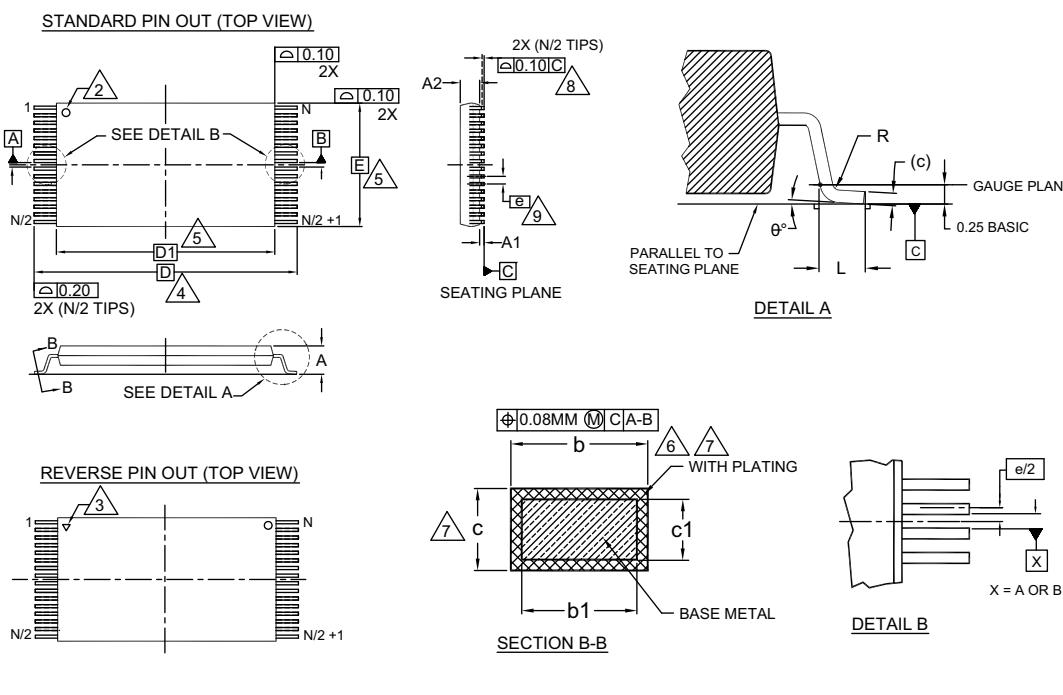

図 16.48 ピン TSOP I (18.4 × 12 × 1.2 mm) パッケージ外形図、51-85183

| SYMBOL   | DIMENSIONS  |      |      |

|----------|-------------|------|------|

|          | MIN.        | NOM. | MAX. |

| A        | —           | —    | 1.20 |

| A1       | 0.05        | —    | 0.15 |

| A2       | 0.95        | 1.00 | 1.05 |

| b1       | 0.17        | 0.20 | 0.23 |

| b        | 0.17        | 0.22 | 0.27 |

| c1       | 0.10        | —    | 0.16 |

| c        | 0.10        | —    | 0.21 |

| D        | 20.00 BASIC |      |      |

| D1       | 18.40 BASIC |      |      |

| E        | 12.00 BASIC |      |      |

| e        | 0.50 BASIC  |      |      |

| L        | 0.50        | 0.60 | 0.70 |

| $\theta$ | 0°          | —    | 8    |

| R        | 0.08        | —    | 0.20 |

| N        | 48          |      |      |

### NOTES:

- ① DIMENSIONS ARE IN MILLIMETERS (mm).

- ② PIN 1 IDENTIFIER FOR STANDARD PIN OUT (DIE UP).

- ③ PIN 1 IDENTIFIER FOR REVERSE PIN OUT (DIE DOWN): INK OR LASER MARK.

- ④ TO BE DETERMINED AT THE SEATING PLANE [-C-]. THE SEATING PLANE IS DEFINED AS THE PLANE OF CONTACT THAT IS MADE WHEN THE PACKAGE LEADS ARE ALLOWED TO REST FREELY ON A FLAT HORIZONTAL SURFACE.

- ⑤ DIMENSIONS D1 AND E DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION ON E IS 0.15mm PER SIDE AND ON D1 IS 0.25mm PER SIDE.

- ⑥ DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL IN EXCESS OF b DIMENSION AT MAX. MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND AN ADJACENT LEAD TO BE 0.07mm .

- ⑦ THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10mm AND 0.25mm FROM THE LEAD TIP.

- ⑧ LEAD COPLANARITY SHALL BE WITHIN 0.10mm AS MEASURED FROM THE SEATING PLANE.

- ⑨ DIMENSION "e" IS MEASURED AT THE CENTERLINE OF THE LEADS.

- 10. JEDEC SPECIFICATION NO. REF: MO-142(D)DD.

51-85183 \*F

## 略語

表 1. 本書で使用する略語

| 略語    | 説明                                                         |

|-------|------------------------------------------------------------|

| BHE   | byte high enable ( 上位バイトイネーブル )                            |

| BLE   | byte low enable ( 下位バイトイネーブル )                             |

| CE    | chip enable ( チップイネーブル )                                   |

| CMOS  | complementary metal oxide semiconductor<br>( 相補型金属酸化膜半導体 ) |

| ECC   | error-correcting code ( エラー訂正コード )                         |

| I/O   | 入力／出力                                                      |

| OE    | output enable ( 出力イネーブル )                                  |

| SRAM  | static random access memory<br>( スタティックランダムアクセスメモリ )       |

| TTL   | transistor-transistor logic<br>( トランジスタ - トランジスタロジック )     |

| VFBGA | very fine-pitch ball grid array<br>( 超ファインピッチボールグリッドアレイ )  |

| WE    | write enable ( 書き込みイネーブル )                                 |

## 本書の表記法

### 測定単位

表 2. 測定単位

| 記号  | 測定単位     |

|-----|----------|

| °C  | 摂氏温度     |

| MHz | メガヘルツ    |

| µA  | マイクロアンペア |

| µs  | マイクロ秒    |

| mA  | ミリアンペア   |

| mm  | ミリメートル   |

| ns  | ナノ秒      |

| Ω   | オーム      |

| %   | パーセント    |

| pF  | ピコファラド   |

| V   | ボルト      |

| W   | ワット      |

## 改訂履歴

文書名 : CY62157G / CY62157GE MoBL、エラー訂正コード (ECC) 内蔵の 8M ビット (512K×16 ビット) スタティック RAM

文書番号 : 002-29784

| 版  | ECN 番号  | 発行日        | 変更内容                                           |

|----|---------|------------|------------------------------------------------|

| ** | 6855749 | 06/04/2020 | これは英語版 002-27323 Rev. *C を翻訳した日本語版 Rev. ** です。 |

## セールス、ソリューションおよび法律情報

### ワールドワイドな販売と設計サポート

サイプレスは、事業所、ソリューションセンター、メーカー代理店、および販売代理店の世界的なネットワークを保持しています。お客様の最寄りのオフィスについては、[サイプレスのロケーションページ](#)をご覧ください。

#### 製品

Arm® Cortex® Microcontrollers

車載用

クロック & バッファ

インターフェース

IoT (モノのインターネット)

メモリ

マイクロコントローラ

PSoC

電源用 IC

タッチ センシング

USB コントローラー

ワイヤレス

[cypress.com/arm](http://cypress.com/arm)

[cypress.com/automotive](http://cypress.com/automotive)

[cypress.com/clocks](http://cypress.com/clocks)

[cypress.com/interface](http://cypress.com/interface)

[cypress.com/iot](http://cypress.com/iot)

[cypress.com/memory](http://cypress.com/memory)

[cypress.com/mcu](http://cypress.com/mcu)

[cypress.com/psoc](http://cypress.com/psoc)

[cypress.com/pmic](http://cypress.com/pmic)

[cypress.com/touch](http://cypress.com/touch)

[cypress.com/usb](http://cypress.com/usb)

[cypress.com/wireless](http://cypress.com/wireless)

#### PSoC® ソリューション

[PSoC 1](#) | [PSoC 3](#) | [PSoC 4](#) | [PSoC 5LP](#) | [PSoC 6 MCU](#)

#### サイプレス開発者コミュニティ

[コミュニティ](#) | [サンプルコード](#) | [Projects](#) | [ビデオ](#) | [ブログ](#) | [トレーニング](#) | [Components](#)

#### テクニカル サポート

[cypress.com/support](http://cypress.com/support)

© Cypress Semiconductor Corporation, 2019-2020. 本書面は、Cypress Semiconductor Corporation 及び Spansion LLC を含むその子会社（以下「Cypress」という。）に帰属する財産である。本書面（本書面に含まれ又は言及されているあらゆるソフトウェア若しくはファームウェア（以下「本ソフトウェア」という。）を含む）は、アメリカ合衆国及び世界の他の国における知的財産法及び条約に基づき Cypress が所有する。Cypress はこれらの法令及び条約に基づく全ての権利を留保し、本段落で特に記載されているものを除き、その特許権、著作権、商標権又はその他の知的財産権のライセンスを一切許諾しない。本ソフトウェアにライセンス契約書が伴っておらず、かつ Cypress との間で別途本ソフトウェアの使用方法を定める書面による合意がない場合、Cypress は、(1) 本ソフトウェアの著作権に基づき、(a) ソースコード形式で提供されている本ソフトウェアについて、Cypress ハードウェア製品と共に用いるためにのみ、かつ組織内部でのみ、本ソフトウェアの修正及び複製を行うこと、並びに (b) Cypress のハードウェア製品ユニットに用いるためにのみ、(直接又は再販売者及び販売代理店を介して間接のいずれか) 本ソフトウェアをバイナリーコード形式で外部エンドユーザーに配布すること、並びに (2) 本ソフトウェア (Cypress により提供され、修正がなされていないもの) が抵触する Cypress の特許権のクレームに基づき、Cypress ハードウェア製品と共に用いるためにのみ、本ソフトウェアの作成、利用、配布及び輸入を行うことについての非独占的で譲渡不能な一身専属的ライセンス（サプライセンスの権利を除く）を付与する。本ソフトウェアのその他の使用、複製、修正、変換又はコンパイルを禁止する。

**適用される法律により許される範囲内で、Cypress は、本書面又はいかなる本ソフトウェア若しくはこれに伴うハードウェアに関するても、明示又は默示をとわず、いかなる保証（商品性及び特定の目的への適合性の默示を含むがこれらに限られない）も行わない。**いかなるコンピューティングデバイスも絶対に安全ということはない。従って、Cypress のハードウェアまたはソフトウェア製品に講じられたセキュリティ対策にもかかわらず、Cypress は、Cypress 製品への権限のないアクセスまたは使用といったセキュリティ違反から生じる一切の責任を負わない。加えて、本書面に記載された製品には、エラッタと呼ばれる設計上の欠陥またはエラーが含まれている可能性があり、公表された仕様とは異なる動作をする場合がある。適用される法律により許される範囲内で、Cypress は、別途通知することなく、本書面を変更する権利を留保する。Cypress は、本書面に記載のある、いかなる製品若しくは回路の適用又は使用から生じる一切の責任を負わない。本書面で提供されたあらゆるサンプルデザイン情報又はプログラムコードを含む）は、参照目的のためにのみ提供されたものである。この情報で構成するあらゆるアプリケーション及びその結果としてのあらゆる製品の機能性及び安全性を適切に設計、プログラム、かつテストすることは、本書面のユーザーの責任において行われるものとする。Cypress 製品は、兵器、兵器システム、原子力施設、生命維持装置若しくは生命維持システム、蘇生用の設備及び外科的移植を含むその他の医療機器若しくは医療システム、汚染管理若しくは有害物質管理の運用のために設計され若しくは意図されたシステムの重要な構成部分としての使用、又は装置若しくはシステムの不具合が人身傷害、死亡若しくは物的損害を生じさせるようなその他の使用（以下「本目的外使用」という。）のためには設計、意図又は承認されていない。重要な構成部分とは、それの不具合が装置若しくはシステムの不具合を生じさせるか又はその安全性若しくは実効性に影響すると合理的に予想できるような装置若しくはシステムのあらゆる構成部分をいう。Cypress 製品のあらゆる本目的外使用から生じ、若しくは本目的外使用に関連するいかなる請求、損害又はその他の責任についても、Cypress はその全部又は一部をとわず一切の責任を負わず、かつ Cypress はそれら一切から本書により免除される。Cypress は Cypress 製品の本目的外使用から生じ又は本目的外使用に関連するあらゆる請求、費用、損害及びその他の責任（人身傷害又は死亡に基づく請求を含む）から免責補償される。

Cypress, Cypress のロゴ、Spansion, Spansion のロゴ及びこれらの組み合わせ、WICED, PSoC, CapSense, EZ-USB, F-RAM, 及び Traveo は、米国及びその他の国における Cypress の商標又は登録商標である。Cypress のより完全な商標のリストは、[cypress.com](http://cypress.com) を参照すること。その他の名称及びブランドは、それぞれの権利者の財産として権利主張がなされている可能性がある。