## 特征

- 宽电源范围：2.3V 至 5.5V

- 可编程增益：1V/V 至 128V/V

- 可编程数据速率：高达 2kSPS

- 单周期数据稳定

- 20SPS 时 50Hz 和 60Hz 谐波抑制

- 4 个单端输入或 2 组差分输入

- 可编程匹配电流源：50 $\mu$ A 至 1.5mA

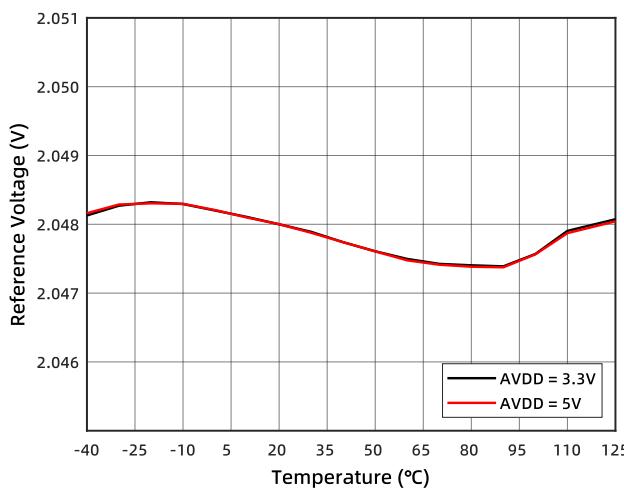

- 内置 2.048V 基准：温漂典型值为 5ppm/ $^{\circ}$ C

- 兼容 SPI 接口模式 1

- 低电流消耗：典型值为 210 $\mu$ A (占空比模式)

- TSSOP16 5mm x 4.4mm 封装

## 应用

- 工业控制及自动化

- 工业现场仪表

- 智能温度、压力变送器

- 温度传感器测量

- 2 线/3 线/4 线 RTD 测量

- 热电偶测量

- PLC/DCS 模拟量采集

- 科学仪器仪表

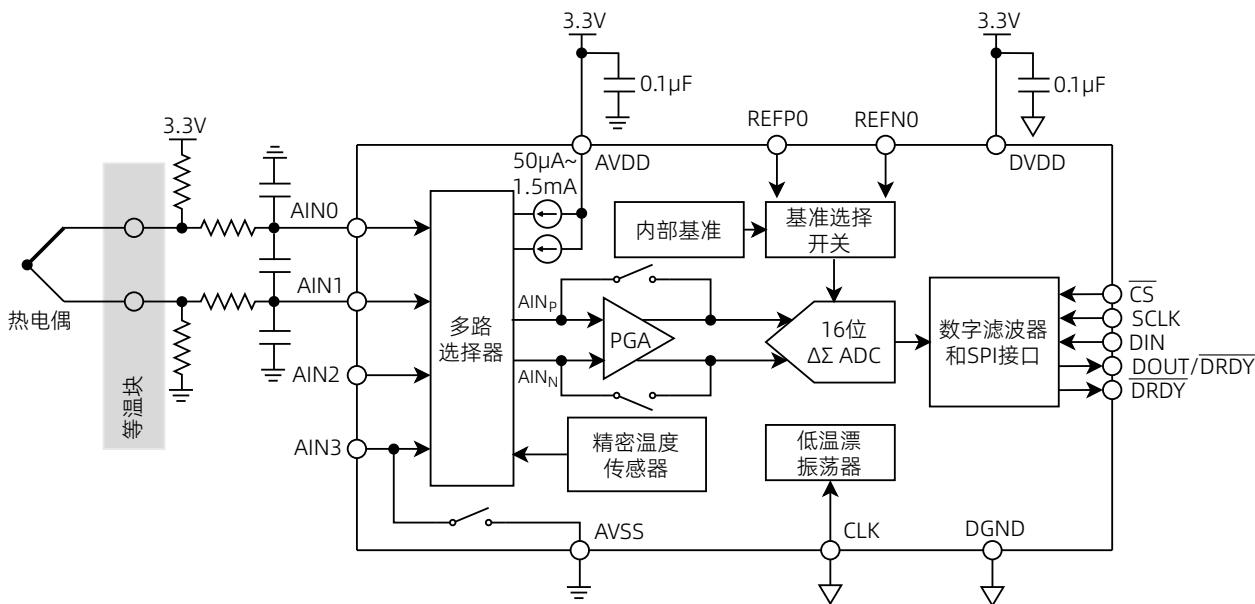

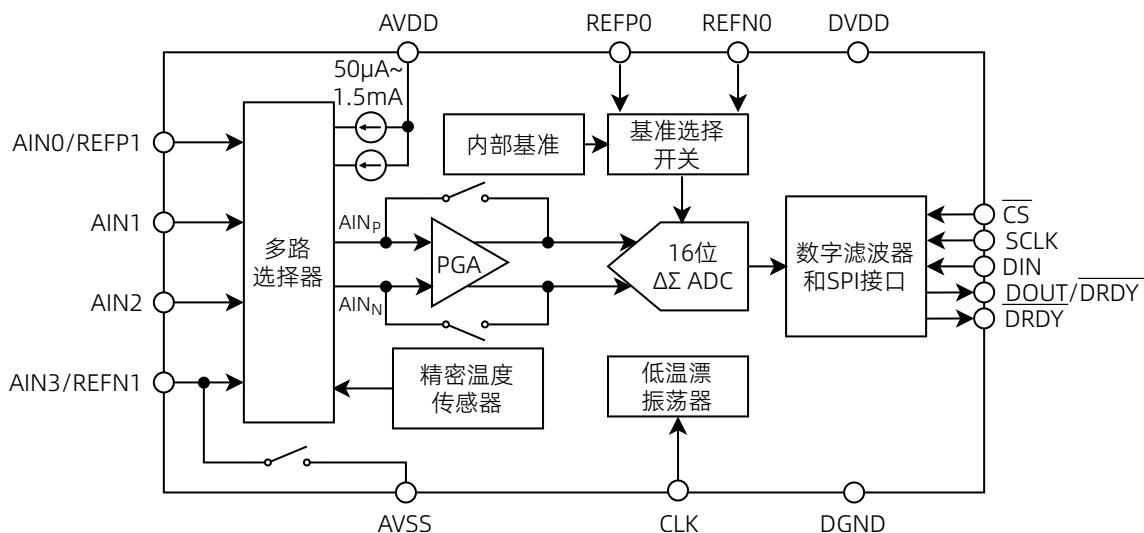

## 架构框图

## 概述

CM1110 是一款精密、低功耗、兼容 SPI 接口、16 位  $\Delta\Sigma$  ADC，其内部集成了一个低噪声可编程增益放大器 (PGA)、两个可编程输出电流源 (IDAC)、一个电压基准、一个振荡器、一个低侧开关和一个精密温度传感器。这些特性使得 CM1110 适用于测量微弱信号，例如电阻式温度检测器 (RTD)、热电偶、热敏电阻和桥式传感器。

CM1110 能够以高达 2kSPS 的速率进行数据转换，并且能够在单周期内稳定。输入多路选择器 (MUX) 可以提供 4 个单端输入或 2 组差分输入。针对工业应用，当采样率为 20SPS 时，数字滤波器能够实现 50Hz 和 60Hz 同步抑制。启用 PGA 时，支持伪差分输入或全差分输入；禁用 PGA 后，仍提供高输入阻抗和高达 4V/V 的增益，以及能实现单端测量。

CM1110 采用 TSSOP16 型封装，其工作温度范围最大为 -40 $^{\circ}$ C 至 125 $^{\circ}$ C。

# 目录

|            |    |                            |    |

|------------|----|----------------------------|----|

| 封页         | 1  | 占空比模式                      | 29 |

| 特征         | 1  | Turbo 模式                   | 29 |

| 应用         | 1  | 断电模式                       | 29 |

| 概述         | 1  | 系统自检                       | 29 |

| 架构框图       | 1  | 传感器检测                      | 29 |

| 文档历史       | 3  | 系统监测                       | 29 |

| 管脚配置和功能    | 4  | 失调检测                       | 30 |

| 管脚配置       | 4  | 数字接口                       | 31 |

| 管脚功能       | 4  | 串行接口                       | 31 |

| 绝对最大额定值    | 5  | 片选 ( $\overline{CS}$ )     | 31 |

| 电气规格       | 6  | 串行时钟 (SCLK)                | 31 |

| 时序规格       | 9  | 数据就绪 ( $\overline{DRDY}$ ) | 31 |

| SPI 时序要求   | 9  | 数据输入 (DIN)                 | 31 |

| SPI 开关特性   | 9  | 数据输出和数据就绪 (DOUT/DRDY)      | 31 |

| 典型特征       | 11 | SPI 超时                     | 31 |

| 工作原理       | 17 | 数据格式                       | 31 |

| 多路选择器      | 17 | 命令                         | 31 |

| 基准电压       | 18 | RESET (0000 011x)          | 32 |

| 时钟源        | 18 | START/SYNC (0000 100x)     | 32 |

| 激励电流源      | 18 | POWERDOWN (0000 001x)      | 32 |

| 低侧电源开关     | 19 | RDATA (0001 xxxx)          | 32 |

| 调制器        | 19 | RREG (0010 rrnn)           | 32 |

| 数字滤波器      | 19 | WREG (0100 rrnn)           | 32 |

| 低噪声 PGA    | 21 | 读取数据                       | 32 |

| PGA 共模电压要求 | 22 | 发送命令                       | 34 |

| 旁路 PGA     | 23 | 连接多个芯片                     | 34 |

| 输出数据速率     | 23 | 寄存器                        | 35 |

| 噪声性能       | 25 | CONFIG                     | 35 |

| 温度传感器      | 28 | CONFIG0 (地址=00h)           | 35 |

| 功能与模式      | 29 | CONFIG1 (地址=01h)           | 36 |

| 上电和复位      | 29 | CONFIG2 (地址=02h)           | 37 |

| 转换模式       | 29 | CONFIG3 (地址=03h)           | 38 |

| 单次转换模式     | 29 | 封装及订购信息                    | 39 |

| 连续转换模式     | 29 | 封装形式                       | 39 |

| 工作模式       | 29 | 产品外形图                      | 39 |

| 普通模式       | 29 | 订购信息                       | 40 |

## 文档历史

下表列举了本文档自产品发布后的所有更新。

| 文档版本 | 修订日期       | 内容描述                                                                                                                                                                                      |

|------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V0.0 | 2024-03-19 | 预发布。                                                                                                                                                                                      |

| V0.1 | 2024-06-11 | 内容更新如下： <ul style="list-style-type: none"><li>根据实验室数据更新<a href="#">电气规格表</a>。</li><li>新增章节<a href="#">典型特征</a>、<a href="#">工作原理</a>、<a href="#">功能与模式</a>、<a href="#">数字接口</a>。</li></ul> |

| V0.5 | 2025-06-16 | 内容更新如下： <ul style="list-style-type: none"><li>根据实验室数据更新<a href="#">噪声性能</a>章节。</li><li>根据实验室数据更新<a href="#">典型特征</a>。</li></ul>                                                           |

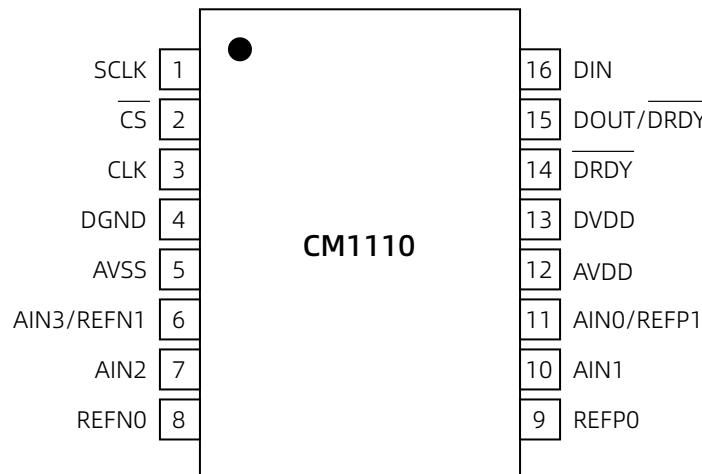

# 管脚配置和功能

## 管脚配置

以下为 CM1110 TSSOP16 封装管脚示意图：

## 管脚功能

表 1 管脚功能描述

| 编号 | 名称         | 类型  | 说明                                               |

|----|------------|-----|--------------------------------------------------|

| 1  | SCLK       | DI  | 串行时钟输入。                                          |

| 2  | CS         | DI  | 片选；低电平有效。如果不使用该管脚，则与 DGND 相连。                    |

| 3  | CLK        | DI  | 外部时钟源管脚。如果不使用该管脚，则与 DGND 相连。                     |

| 4  | DGND       | GND | 数字地。                                             |

| 5  | AVSS       | PWR | 负模拟电源。                                           |

| 6  | AIN3/REFN1 | AI  | 模拟输入 3，基准负端输入 1。该管脚和 AVSS 间连接内部低侧电源开关。           |

| 7  | AIN2       | AI  | 模拟输入 2。                                          |

| 8  | REFNO      | AI  | 基准负端输入 0。                                        |

| 9  | REFPO      | AI  | 基准正端输入 0。                                        |

| 10 | AIN1       | AI  | 模拟输入 1。                                          |

| 11 | AIN0/REFP1 | AI  | 模拟输入 0，基准正端输入 1。                                 |

| 12 | AVDD       | PWR | 正模拟电源。                                           |

| 13 | DVDD       | PWR | 数字电源。                                            |

| 14 | DRDY       | DO  | 数据准备就绪，低电平有效。如果不使用该管脚，则保持断开状态，或通过弱上拉电阻与 DVDD 相连。 |

| 15 | DOUT/DRDY  | DO  | 与数据就绪相结合的串行数据输出；低电平有效。                           |

| 16 | DIN        | DI  | 串行数据输入。                                          |

## 绝对最大额定值

| 参数                | 最小值                 | 最大值        | 单位 |

|-------------------|---------------------|------------|----|

| <b>温度</b>         |                     |            |    |

| 工作温度              | -40                 | 125        | °C |

| 存储温度              | -60                 | 150        | °C |

| 结温                |                     | 150        | °C |

| 回流焊               | 铅锡焊接温度 (10 秒到 30 秒) | 240        | °C |

|                   | 无铅焊接温度              | 260        | °C |

| <b>耐压</b>         |                     |            |    |

| AVDD 至 AVSS       | -0.3                | 7          | V  |

| DVDD 至 DGND       | -0.3                | 7          | V  |

| AVSS 至 DGND       | -2.8                | 0.3        | V  |

| 模拟输入电压            | AVSS - 0.3          | AVDD + 0.3 | V  |

| 数字输入电压            | DGND - 0.3          | DVDD + 0.3 | V  |

| <b>限流</b>         |                     |            |    |

| 输入电流 <sup>1</sup> | -10                 | 10         | mA |

| <b>ESD</b>        |                     |            |    |

| HBM               | 3000                |            | V  |

| CDM               | 2000                |            | V  |

注 1：只针对除电源管脚外任意管脚。另外，瞬态电流达到 100mA 不会引起芯片闩锁。

## 电气规格

默认测试条件: AVDD = 3.3V、AVSS = 0V、DVDD = 3.3V、PGA 启用、DR = 20SPS、外部 VREF = 2.5V、TA = -40°C~125°C。

| 参数                | 测试条件                          | 最小值                          | 典型值         | 最大值 | 单位                 |

|-------------------|-------------------------------|------------------------------|-------------|-----|--------------------|

| <b>直流精度</b>       |                               |                              |             |     |                    |

| 分辨率               | 无失码                           | 16                           |             |     | Bits               |

| 输出数据速率            | 普通模式                          | 20、50、100、200、333、666、1000   |             |     | SPS                |

|                   | 占空比模式                         | 5、12.5、25、50、83.25、166.5、250 |             |     | SPS                |

|                   | Turbo 模式                      | 40、100、200、400、666、1333、2000 |             |     | SPS                |

| INL               | 增益 = 1 至 128, VCM = 0.5 AVDD  |                              | ±6          | ±20 | ppm <sub>FSR</sub> |

| 输入失调电压            | PGA 禁用, 增益 = 1 至 4, 差分输入      |                              | ±4          |     | μV                 |

|                   | 增益 = 1 至 128, 差分输入            |                              | ±4          |     | μV                 |

| 失调电压温漂            | PGA 禁用, 增益 = 1 至 4            |                              | 0.25        |     | μV/°C              |

|                   | 增益 = 1 至 128, TA = -40°C~85°C |                              | 0.06        |     | μV/°C              |

|                   | 增益 = 1 至 128                  |                              | 0.25        |     | μV/°C              |

| 增益误差              | PGA 禁用, 增益 = 1 至 4            |                              | ±0.015      |     | %                  |

|                   | 增益 = 1 至 128, TA = 25°C       |                              | ±0.015      |     | %                  |

| 增益误差温漂            | PGA 禁用, 增益 = 1 至 4            |                              | 2           |     | ppm/°C             |

|                   | 增益 = 1 至 128                  |                              | 4           |     | ppm/°C             |

| 初始精度              | 内部基准, TA = 25°C               |                              | 2.048       |     | V                  |

| 内部电压基准温漂          |                               | 5                            | 25          |     | ppm/°C             |

| VREF              | AVDD - AVSS = 2.3V~3.0V       | 0.9                          | 1.2         |     | V                  |

| VREFP             |                               |                              | VREFN + 1.2 |     | V                  |

| VREFN             |                               | AVSS                         | AVSS + 0.5  |     | V                  |

| VREF <sup>1</sup> | AVDD - AVSS = 3.0V~5.5V       | 0.9                          | 2.048       | 2.5 | V                  |

| VREFP             |                               |                              | AVSS + 2.5  |     | V                  |

| VREFN             |                               | AVSS                         | AVSS + 1.5  |     | V                  |

| VIN               | VREF ≤ 2.048V                 | -VREF/GAIN                   | VREF/GAIN   |     | V                  |

|                   | VREF > 2.048V                 | -2.048/GAIN                  | 2.048/GAIN  |     | V                  |

| 基准输入电流            | REFP0 = VREF, REFN0 = AVSS    |                              | ±10         |     | nA                 |

| 内部振荡器精度           | 普通模式                          |                              | ±1          |     | %                  |

| 激励电流源输出电流设置       |                               | 10、50、100、250、500、1000、1500  |             |     | μA                 |

| 激励电流源顺从电压         | 所有电流设置                        |                              | AVDD - 0.9  |     | V                  |

| 激励电流源精度           | 所有电流设置, 每个 IDAC               |                              | ±0.5        |     | %                  |

| 激励电流源电流匹配         | IDAC 之间                       |                              | ±0.3        |     | %                  |

| 激励电流源温漂           | 每个 IDAC                       |                              | 36          |     | ppm/°C             |

| 参数              | 测试条件                                            | 最小值      | 典型值      | 最大值  | 单位     |

|-----------------|-------------------------------------------------|----------|----------|------|--------|

| 激励电流源温漂匹配       | IDAC 之间                                         |          | 7        |      | ppm/°C |

| 温度传感器转换分辨率      |                                                 |          | 16       |      | Bits   |

| 温度传感器温度分辨率      |                                                 |          | 0.021    |      | °C     |

| 温度传感器精度         | TA = 0°C~75°C                                   |          | ±0.25    |      | °C     |

|                 | TA = -40°C~125°C                                |          | ±1       |      | °C     |

| 低侧电源开关的导通电阻     |                                                 |          | 5.3      |      | Ω      |

| 流经低侧电源开关的电流     |                                                 |          | 30       |      | mA     |

| <b>动态性能</b>     |                                                 |          |          |      |        |

| 工频抑制比           | 50Hz ±3%, DR = 20SPS, 外部时钟, 50/60位 = 10         |          | 107      |      | dB     |

|                 | 60Hz ±3%, DR = 20SPS, 外部时钟, 50/60位 = 11         |          | 113      |      | dB     |

|                 | 50Hz 或 60Hz ±3%, DR = 20SPS, 外部时钟, 50/60 位 = 01 | 80       |          |      | dB     |

| CMRR            | 直流条件下的增益 = 1                                    | 95       | 112      |      | dB     |

|                 | f <sub>CM</sub> = 50Hz, DR = 2kSPS              |          | 95       |      | dB     |

|                 | f <sub>CM</sub> = 60Hz, DR = 2kSPS              |          | 97       |      | dB     |

| PSRR            | 直流条件下的 AVDD, VCM = 0.5 AVDD, 增益 = 1             |          | 100      |      | dB     |

|                 | 直流条件下的 DVDD, VCM = 0.5 AVDD, 增益 = 1             |          | 115      |      | dB     |

| <b>模拟输入</b>     |                                                 |          |          |      |        |

| 绝对输入电流          |                                                 |          | ±10      |      | nA     |

| 差分输入电流          |                                                 |          | ±10      |      | nA     |

| <b>数字输入/输出</b>  |                                                 |          |          |      |        |

| V <sub>IH</sub> |                                                 | 0.7 DVDD | DVDD     |      | V      |

| V <sub>IL</sub> |                                                 | DGND     | 0.3 DVDD |      | V      |

| V <sub>OH</sub> | I <sub>OH</sub> = 3mA                           | 0.8 DVDD |          |      | V      |

| V <sub>OL</sub> | I <sub>OL</sub> = 3mA                           |          | 0.2 DVDD |      | V      |

| I <sub>IH</sub> | V <sub>IH</sub> = 5.5V                          | -10      | 10       |      | μA     |

| I <sub>IL</sub> | V <sub>IL</sub> = DGND                          | -10      | 10       |      | μA     |

| <b>电源</b>       |                                                 |          |          |      |        |

| 单极性模拟电源         | AVDD 至 AVSS                                     | 2.3      | 5.5      |      | V      |

| 双极性模拟电源         | AVDD 至 DGND                                     | 2.3      | 2.5      | 2.75 | V      |

|                 | AVSS 至 DGND                                     | -2.75    | -2.5     | -2.3 | V      |

| 参数     | 测试条件                     | 最小值 | 典型值 | 最大值 | 单位 |

|--------|--------------------------|-----|-----|-----|----|

| 数字电源   | DVDD 至 DGND              | 2.3 | 5.5 |     | V  |

| 数字电源电流 | 普通模式                     | 0.1 |     |     | μA |

|        | 占空比模式                    | 0.1 |     |     | μA |

|        | Turbo 模式                 | 0.2 |     |     | μA |

|        | 断电模式                     | 0.1 |     |     | μA |

| 模拟电源电流 | 普通模式, PGA 禁用             | 473 |     |     | μA |

|        | 普通模式, 增益 = 1、2、4         | 590 |     |     | μA |

|        | 普通模式, 增益 = 8             | 636 |     |     | μA |

|        | 普通模式, 增益 = 16            | 723 |     |     | μA |

|        | 普通模式, 增益 = 32、64、128     | 896 |     |     | μA |

|        | 占空比模式, PGA 禁用            | 225 |     |     | μA |

|        | 占空比模式, 增益 = 1、2、4        | 260 |     |     | μA |

|        | 占空比模式, 增益 = 8            | 229 |     |     | μA |

|        | 占空比模式, 增益 = 16           | 305 |     |     | μA |

|        | 占空比模式, 增益 = 32、64、128    | 360 |     |     | μA |

|        | Turbo 模式, PGA 禁用         | 473 |     |     | μA |

|        | Turbo 模式, 增益 = 1、2、4     | 590 |     |     | μA |

|        | Turbo 模式, 增益 = 8         | 636 |     |     | μA |

|        | Turbo 模式, 增益 = 16        | 723 |     |     | μA |

|        | Turbo 模式, 增益 = 32、64、128 | 896 |     |     | μA |

|        | 断电模式                     | 0.3 |     |     | μA |

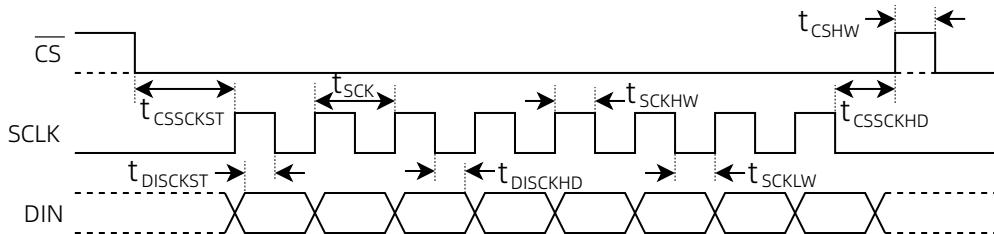

## 时序规格

### SPI 时序要求

默认测试条件: DVDD = 2.3V 至 5.5V、TA = -40°C~125°C。

| 参数            | 描述                                     | 最小值 | 典型值 | 最大值 | 单位 |

|---------------|----------------------------------------|-----|-----|-----|----|

| $t_{CSSCKST}$ | $\overline{CS}$ 的下降沿到第一个 SCLK 上升沿的建立时间 | 50  |     |     | ns |

| $t_{CSSCKHD}$ | $\overline{CS}$ 上升沿到最后一个 SCLK 下降沿的保持时间 | 25  |     |     | ns |

| $t_{CSHW}$    | $\overline{CS}$ 高电平脉冲宽度                | 50  |     |     | ns |

| $t_{SCK}$     | SCLK 时钟周期                              | 150 |     |     | ns |

| $t_{SCKHW}$   | SCLK 高电平脉冲宽度                           | 60  |     |     | ns |

| $t_{SCKLW}$   | SCLK 低电平脉冲宽度                           | 60  |     |     | ns |

| $t_{DISCKST}$ | DIN 有效到 SCLK 下降沿之前的时间: 数据建立时间          | 50  |     |     | ns |

| $t_{DISCKHD}$ | DIN 有效到 SCLK 下降沿之后的时间: 数据保持时间          | 25  |     |     | ns |

| SPI 超时        | 普通模式, 占空比模式                            | 50  | 55  | 60  | ms |

|               | Turbo 模式                               | 50  | 55  | 60  | ms |

注: 图中所示为单字节通信, 实际通信可能涉及多个字节。

图 1 串行接口时序要求

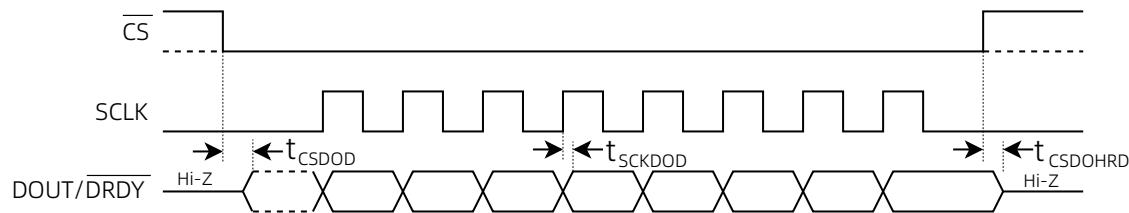

### SPI 开关特性

默认测试条件: DVDD = 2.3V 至 5.5V、TA = -40°C~125°C。

| 参数            | 描述                                 | 最小值 | 典型值 | 最大值 | 单位 |

|---------------|------------------------------------|-----|-----|-----|----|

| $t_{CSDD}$    | $\overline{CS}$ 下降沿到 DOUT 被驱动的延迟时间 |     |     | 50  | ns |

| $t_{SCKDOD}$  | SCLK 上升沿到新的有效 DOUT 延迟时间            | 8   |     | 42  | ns |

| $t_{CSDOHRD}$ | $\overline{CS}$ 上升沿到 DOUT 为高阻的延迟时间 |     |     | 50  | ns |

注：图中所示为单字节通信，实际通信可能涉及多个字节。

图 2 串行接口开关特性

## 典型特征

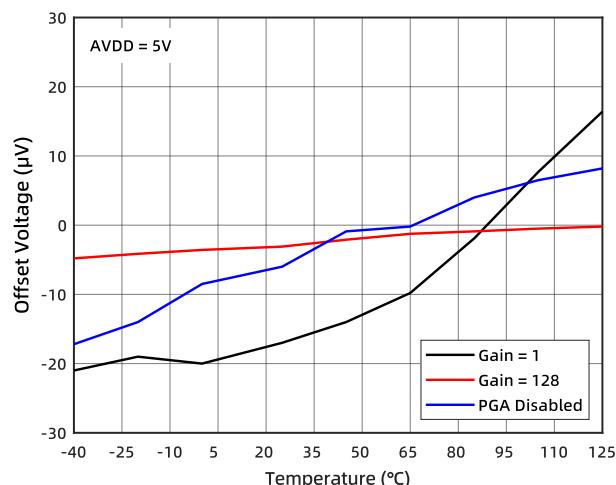

图 3 失调电压的温度特性

图 4 失调电压的温度特性

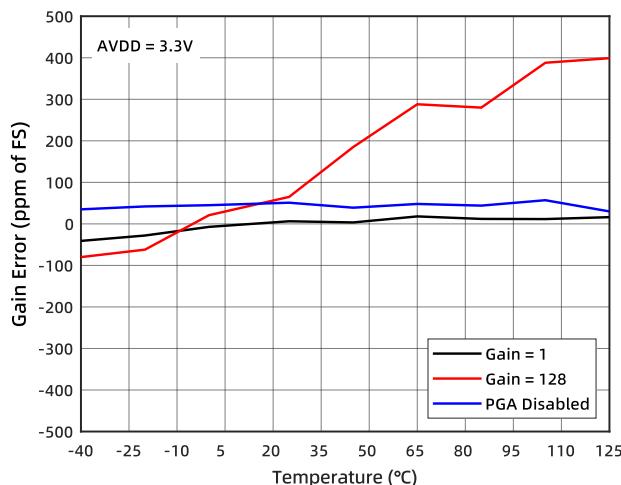

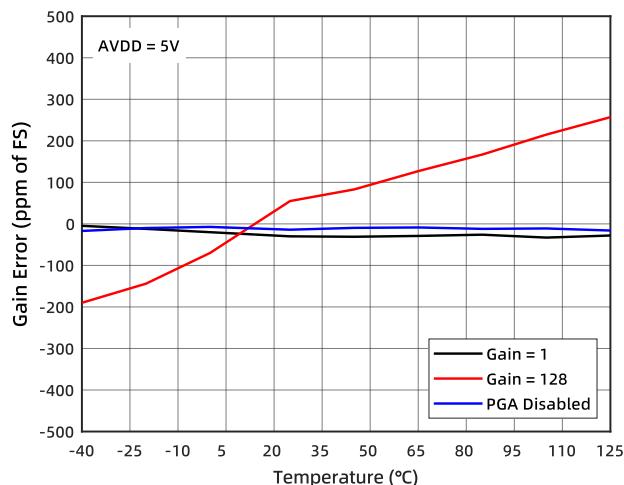

图 5 增益误差的温度特性

图 6 增益误差的温度特性

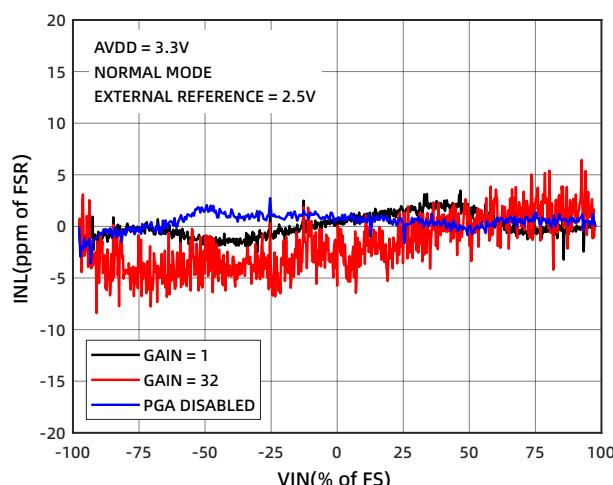

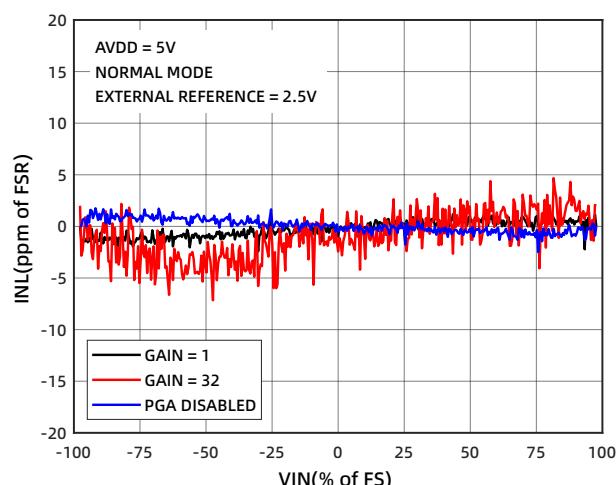

图 7 INL 随差分输入信号的变化

图 8 INL 随差分输入信号的变化

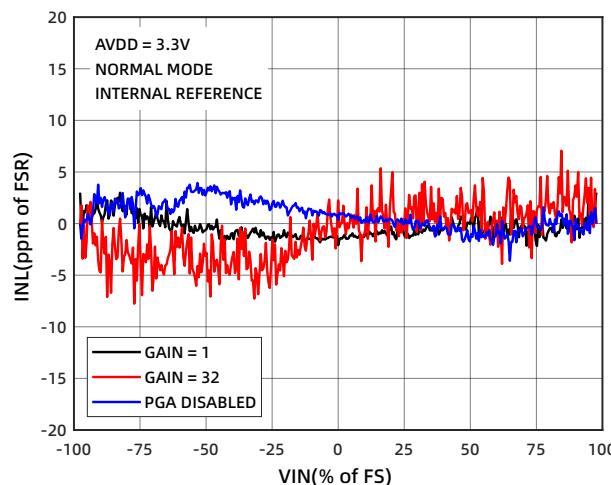

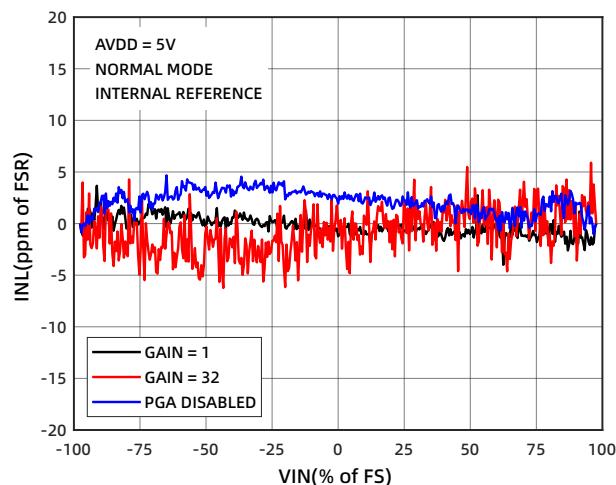

图 9 INL 随差分输入信号的变化

图 10 INL 随差分输入信号的变化

图 11 内部基准电压的温度特性

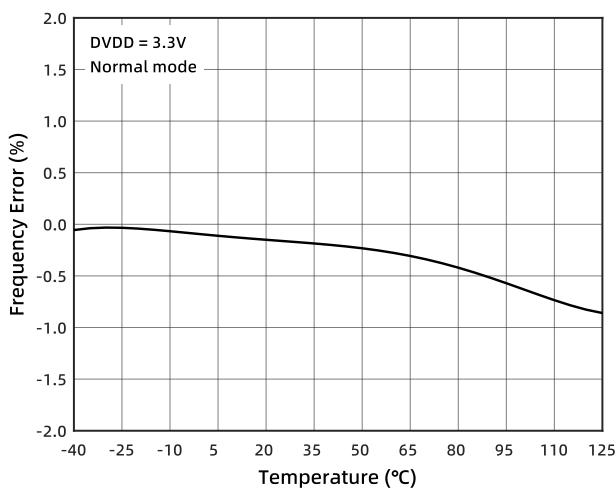

图 12 内部振荡器精度的温度特性

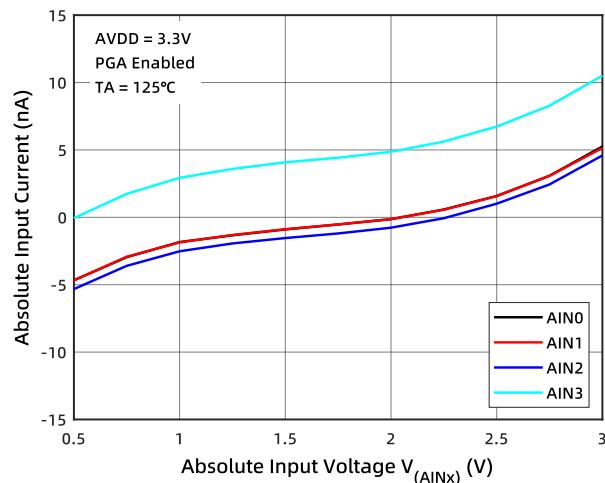

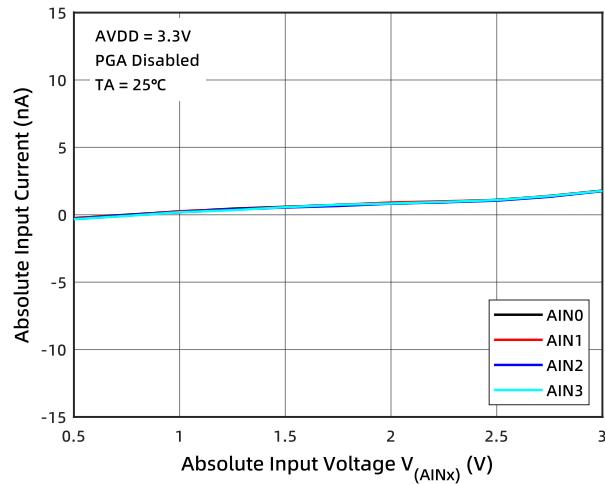

图 13 绝对输入电流随绝对输入电压的变化

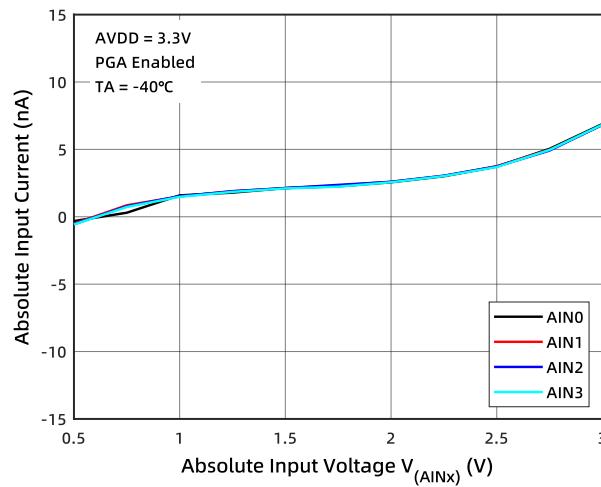

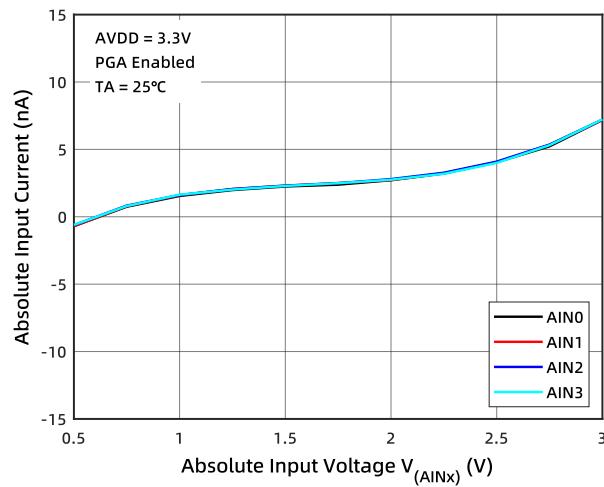

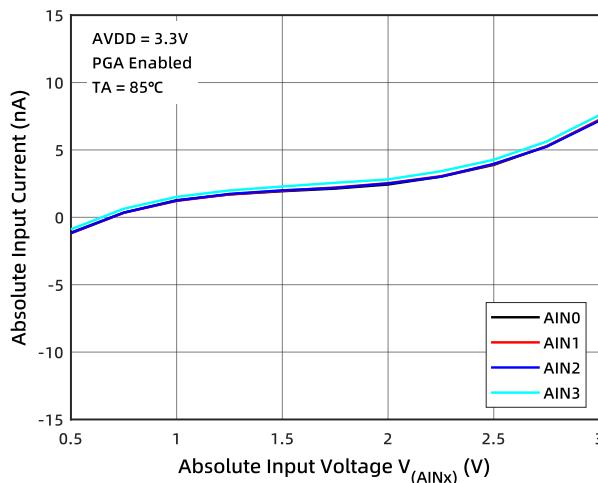

图 14 绝对输入电流随绝对输入电压的变化

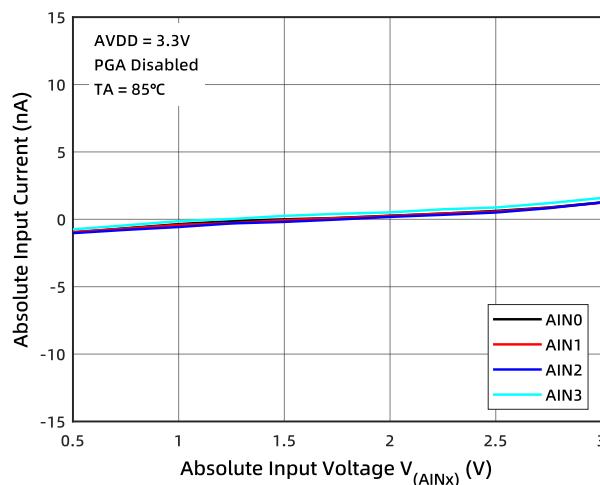

图 15 绝对输入电流随绝对输入电压的变化

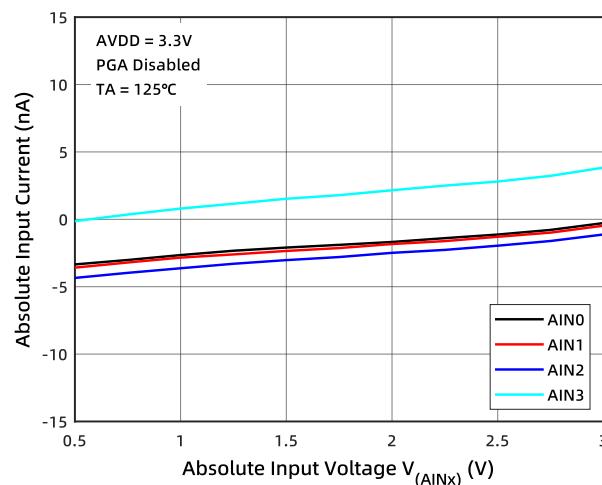

图 16 绝对输入电流随绝对输入电压的变化

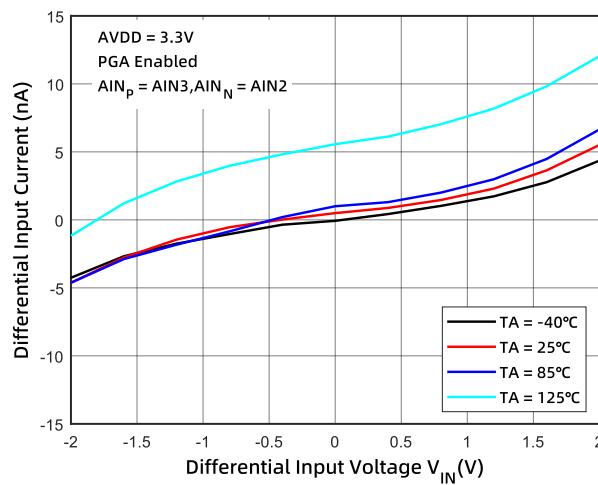

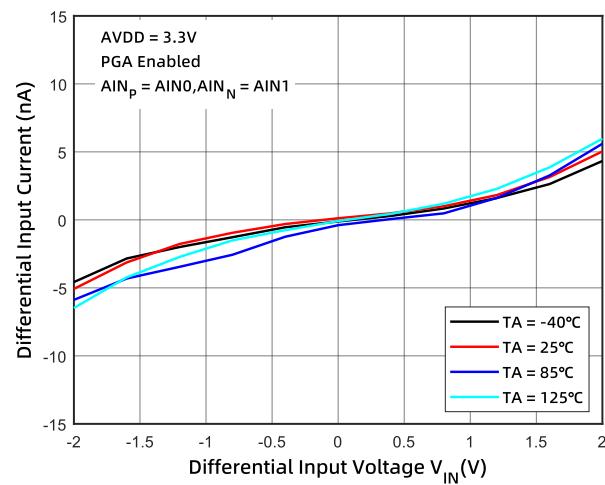

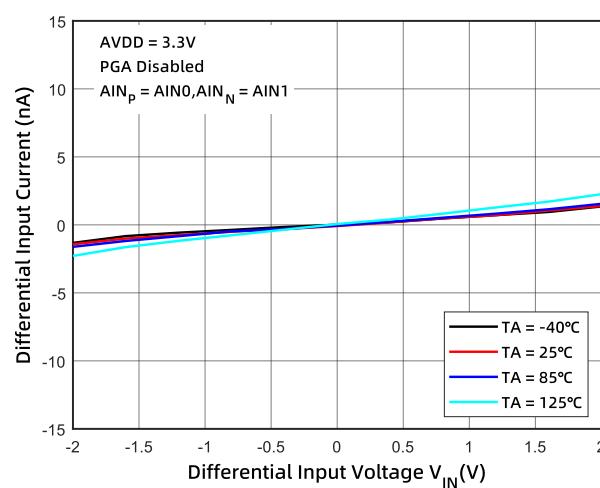

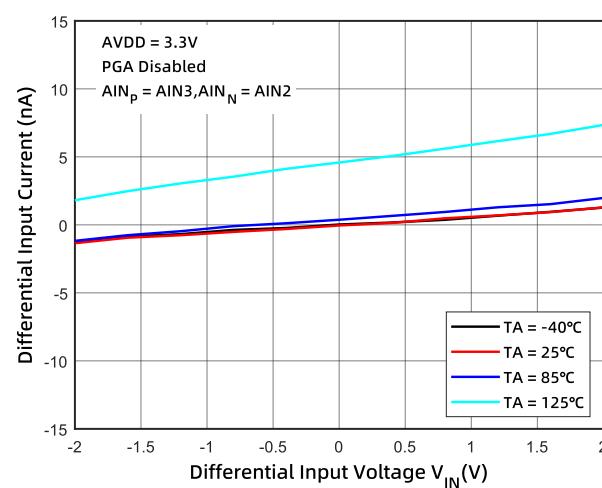

图 17 差分输入电流随差分输入电压的变化

图 18 差分输入电流随差分输入电压的变化

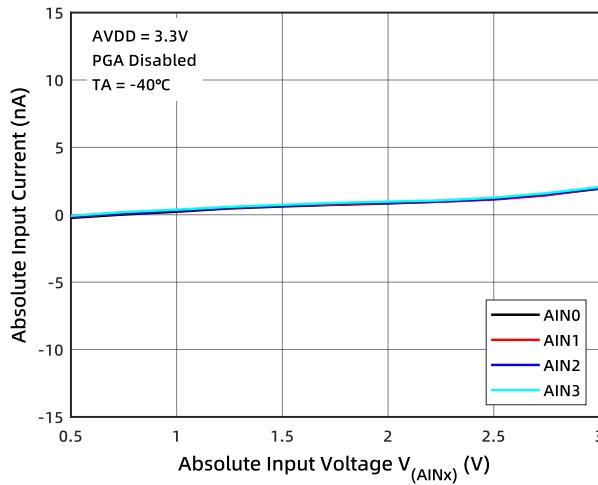

图 19 绝对输入电流随绝对输入电压的变化

图 20 绝对输入电流随绝对输入电压的变化

图 21 绝对输入电流随绝对输入电压的变化

图 22 绝对输入电流随绝对输入电压的变化

图 23 差分输入电流随差分输入电压的变化

图 24 差分输入电流随差分输入电压的变化

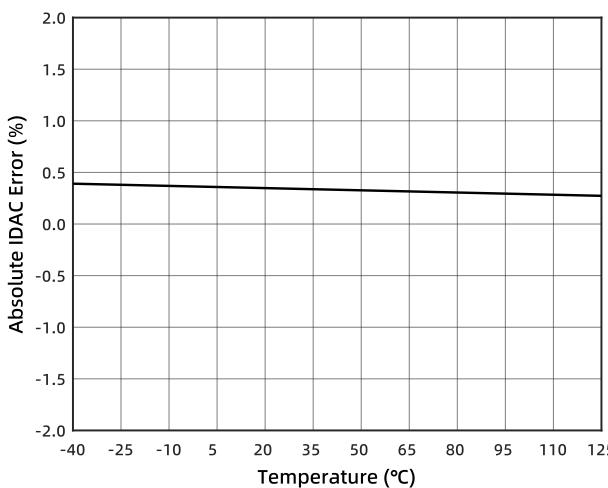

图 25 IDAC 精度的温度特性

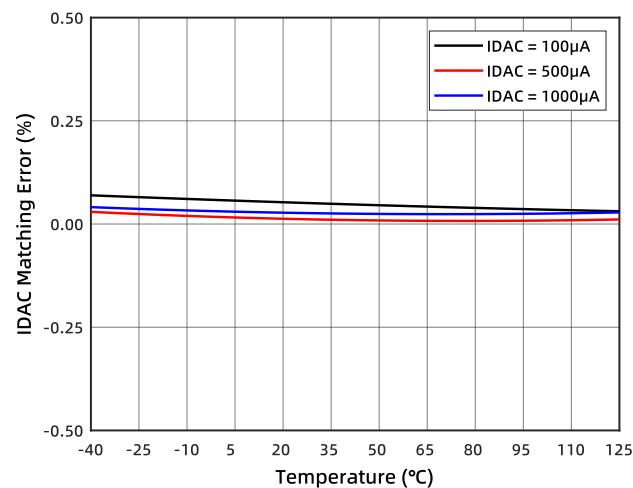

图 26 IDAC 匹配的温度特性

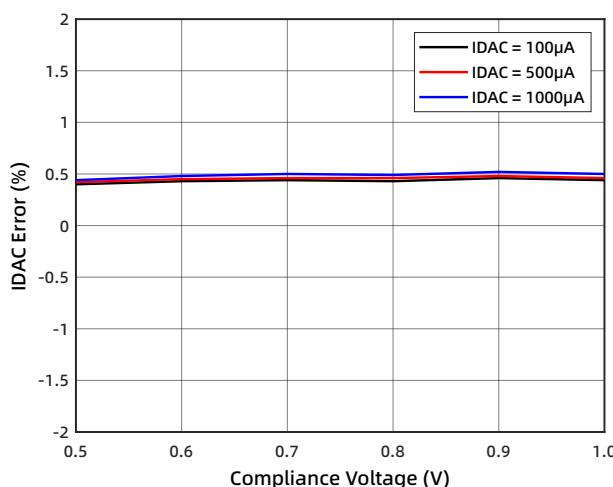

图 27 IDAC 精度随服从电压的变化

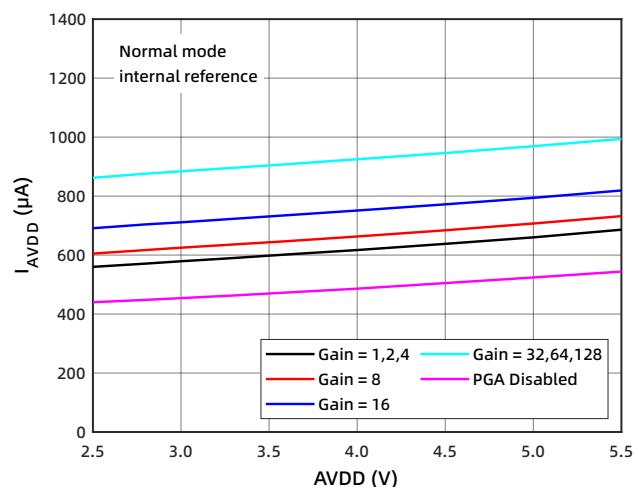

图 28 I\_AVDD 随 AVDD 的变化

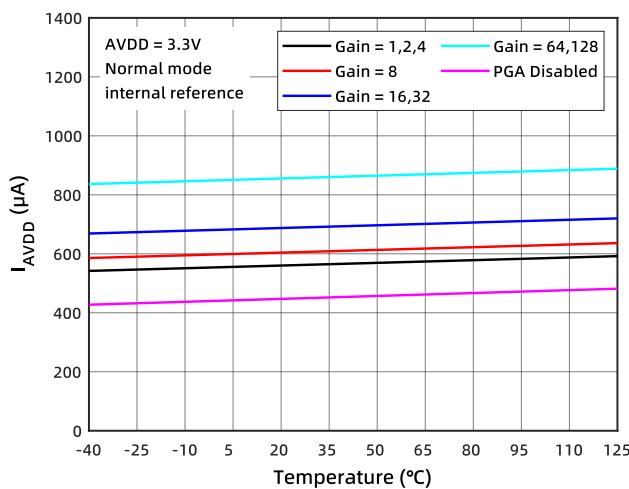

图 29 I\_AVDD 的温度特性

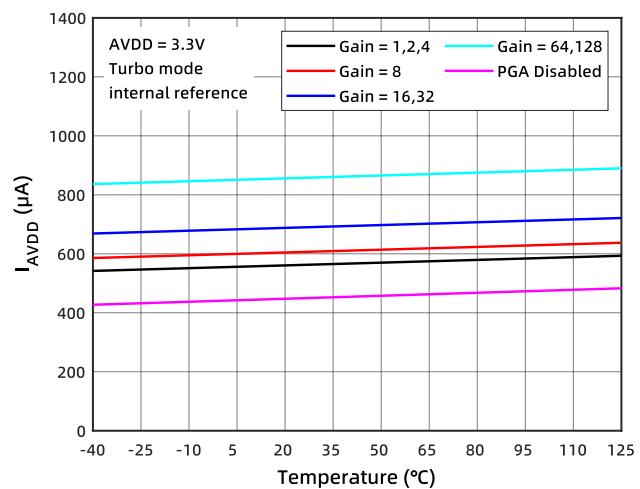

图 30 I\_AVDD 的温度特性

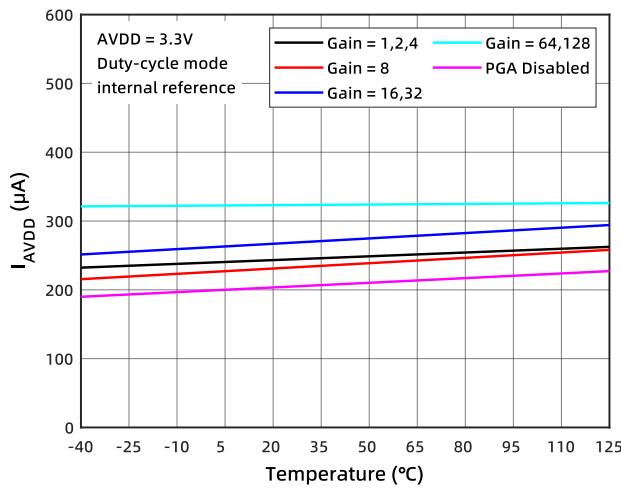

图 31 I\_AVDD 的温度特性

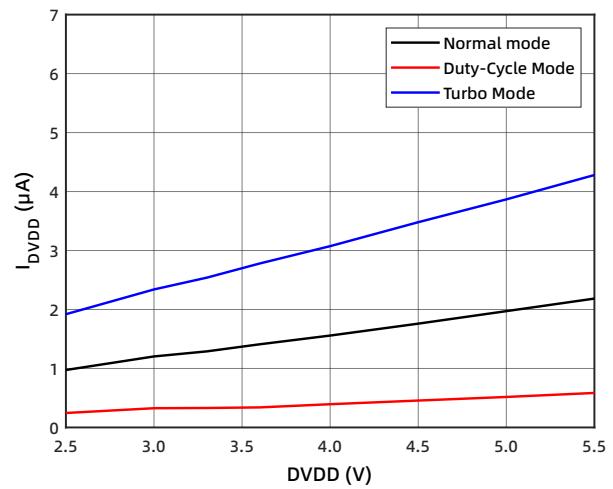

图 32 I\_DVDD 随 DVDD 的变化

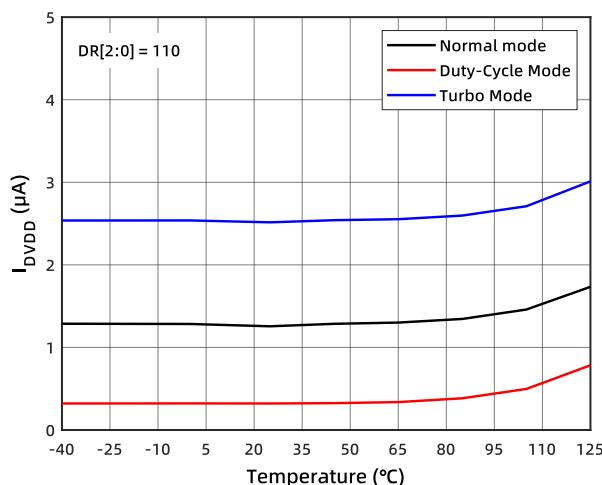

图 33  $I_{DVDD}$  的温度特性

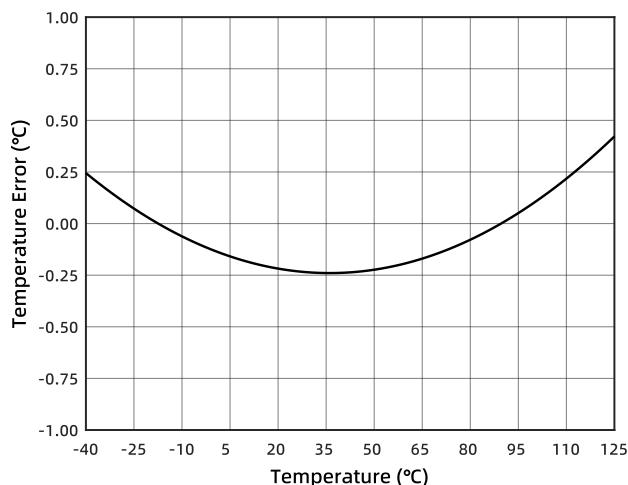

图 34 内部温度传感器精度的温度特性

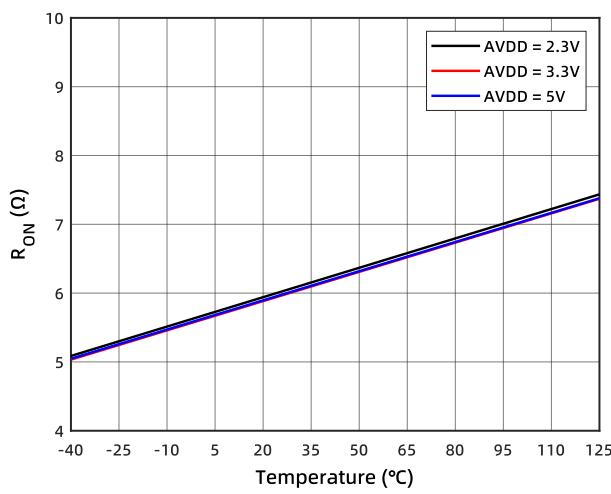

图 35 低侧电源开关  $R_{ON}$  的温度特性

## 工作原理

CM1110 是一款小型、低功耗、16 位  $\Delta\Sigma$  ADC，集成了多种功能，能够降低系统成本并减少小型传感器信号测量应用中的组件数量。

除了  $\Delta\Sigma$  ADC 内核以及单周期稳定数字滤波器外，该芯片还具备低噪声高输入阻抗可编程 PGA、内部电压基准和时钟振荡器。同时，该芯片还集成了一个精确度较高的精密温度传感器以及两个匹配的可编程电流源 (IDAC)。内部低侧电源开关简化了低功耗桥式传感器的设计。该芯片可通过一个兼容 SPI 模式 1 的接口实现 4 个寄存器的配置和 6 条命令的控制。图 36 所示为芯片功能框图。

CM1110 可测量差分信号  $V_{IN}$  ( $AIN_p$  和  $AIN_N$  之间的电压差)。转换器内核由一个差分开关电容  $\Delta\Sigma$  调制器和数字滤波器组成。数字滤波器接收调制器输出的高速码流，输出与输入电压成正比的码字。

CM1110 提供两种转换模式：单次转换模式和连续转换模式。在单次转换模式下，该芯片根据要求对输入信号执行单次转换，然后将转换值存入内部数据缓冲区。接着，该芯片进入低功耗状态。对于仅需定期转换或在两次转换之间长时间处于空闲状态的系统，采用单次转换模式可显著节省功耗。连续转换模式下，该芯片前一次转换结束后立即开始新的一次转换。数据可以随时读取，无需担心数据损坏。读到的数据表示最近一次的转换结果。

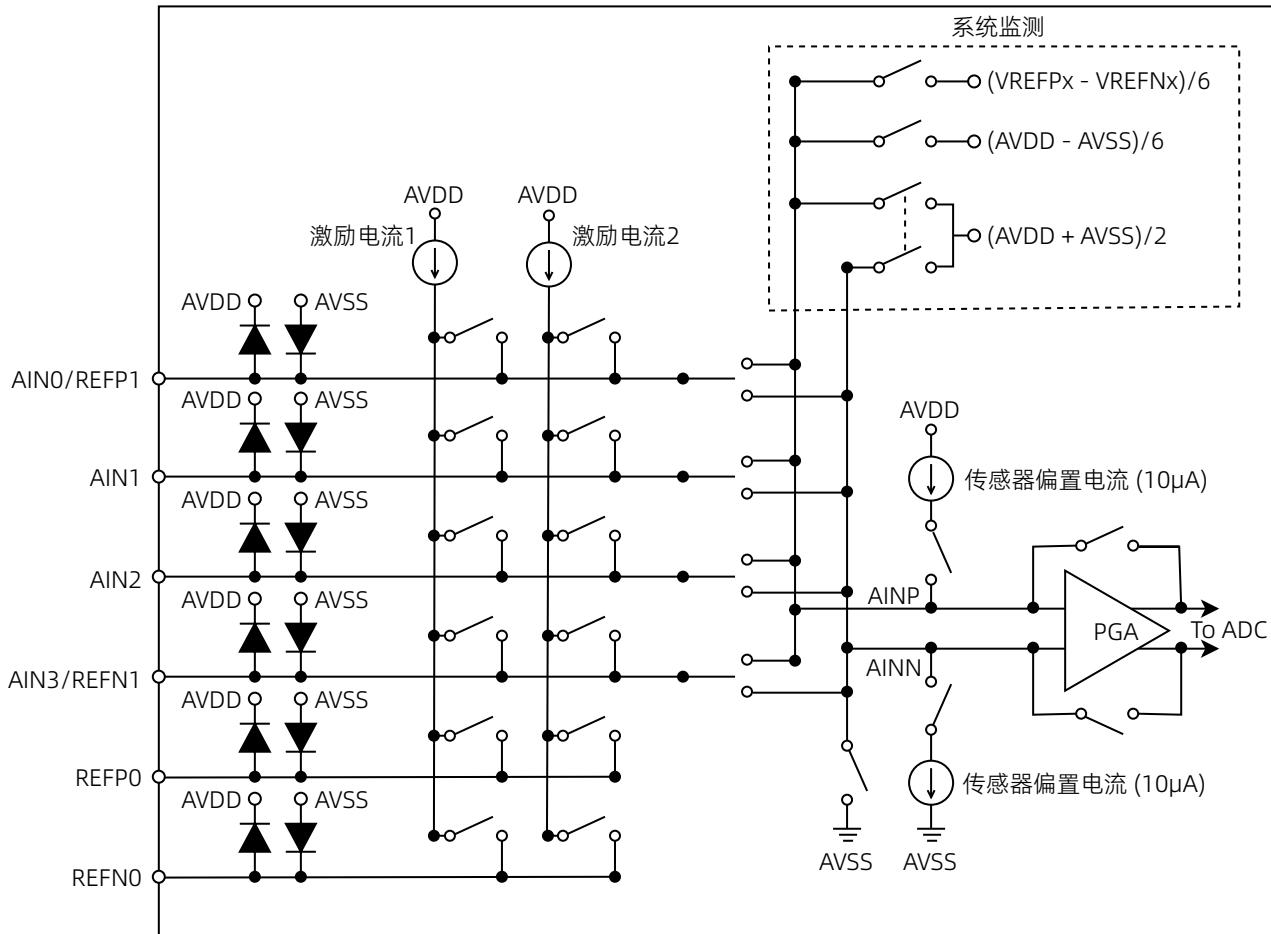

## 多路选择器

CM1110 具有一个非常灵活的输入多路选择器，如图 37 所示。可以测量四路单端信号、两路差分信号、或两路单端信号与一路差分信号组合。该多路选择器通过寄存器  $MUX[3:0]$  进行配置。测量单端信号时，负模拟输入 ( $AIN_N$ ) 通过多路选择器在芯片内部与  $AVSS$  相连。可以选择模拟电源 ( $AVDD - AVSS$ )/6 或外部基准电压 ( $VREFPx - VREFNx$ )/6 作为 ADC 的输入，以实现对系统工作状态的监控。该多路选择器还可将两个可编程电流源引至任意模拟输入 ( $AINx$ ) 或任意基准管脚 (REFPO、REFNO)。

与  $AVDD$  和  $AVSS$  相连的静电放电 (ESD) 二极管可保护输入。为了防止 ESD 二极管导通，所有输入的绝对电压必须处于公式[1] 给定的范围内：

$$AVSS - 0.3V < V_{AINx} < AVDD + 0.3V \quad [1]$$

如果输入管脚电压可能超出上述限制条件，则需要使用外部肖特基钳位二极管或串联电阻将输入电流限制为安全值（请参见绝对最大额定值表）。对该芯片中未使用的输入管脚进行过驱动可能影响正在进行的转换。在这种情况下，建议使用外部肖特基二极管针对信号进行钳位。

图 36 功能框图

图 37 模拟输入多路选择器

## 基准电压

CM1110 集成了 2.048V 低漂移基准电压。对于需要不同基准电压或比例测量方法的应用，该芯片可提供两对差分基准输入 (REFPO/REFNO 和 REFPO1/REFN1)。

基准源通过寄存器 VREF[1:0] 进行配置选择。默认选择内部基准。上电后、退出断电模式或由外部基准源切换至内部基准后，内部基准电压在 25μs 内可完全稳定。

差分基准输入支持自由选择共模基准电压。REFPO 和 REFNO 为专用基准输入管脚，而 REFPO1 和 REFN1 分别与输入 AIN0 和 AIN3 共享输入管脚。所有基准输入均在芯片内部进行缓冲，以提高输入阻抗。因此，使用外部基准时，通常无需额外使用基准缓冲器。在比例测量应用中，基准输入管脚不会成为外部电路的负载。请注意，由于启用基准缓冲器，因此当使用外部基准时，模拟电源电流增大。

大部分情况下，转换结果的精度和基准源电压的稳定性相关。电压基准的噪声和电压漂移都将直接影响转换结果。

## 时钟源

CM1110 系统时钟可由内部低漂移振荡器或 CLK 输入的外部时钟源提供。芯片上电或者复位时，如果 CLK 为低电平将启动内部振荡器作为系统时钟。当 CLK 管脚上检测到两个上升沿后，内部振荡器禁用并切换到外部时钟。CM1110 切换至外部时钟后，仅可通过重新上电或发送 RESET 命令切换回内部振荡器。

## 激励电流源

CM1110 为 RTD 应用提供两个匹配的 IDAC。通过配置寄存器 IDAC[2:0] 可编程输出电流 10μA、50μA、100μA、250μA、500μA、1000μA 或 1500μA。每个电流源均可连接到任意模拟输入管脚 (AINx) 或者基准输入管脚 (REFPO 和 REFNO) 进行输出，并且两个电流源可以连接到同一管脚并联输出电流。请注意，在使用时，电流输出管脚上的电压不能太大 (限制在 AVDD - 0.9V 以内)，否则无法满足 IDAC 精度要求。对于三线 RTD 应用，匹配的电流源可用于抵消传感器引线电阻引起的误差。

IDAC[2:0] 设置完成后，IDAC 在不超过 200μs 内即可启动。如果寄存器 CONFIG2 和 CONFIG3 不是在同一个 WREG 命令中配置，建议先通过 IDAC[2:0] 配置相应电流值，然后再通过 I1MUX[2:0] 和 I2MUX[2:0] 配置各电流源的路径。

在单次转换模式下，如果将 IDAC[2:0] 配置为 000 以外的值，电流源会在非转换时始终保持激活状态。直到接收到 POWERDOWN 命令后，电流源关闭。

请注意，IDAC 启用后 (即 BIT IDAC[2:0] 置为 000 以外的值)，模拟电源电流将会增大。即使 IDAC 未引至任何管脚 (I1MUX[2:0] = I2MUX[2:0] = 000)，IDAC 电路也需要偏置电流进行工作。如果将 I1MUX[2:0] 或 I2MUX[2:0] 置为 000 以外的值，通过相应管脚输出的电流都来自于芯片的模拟电源。

## 低侧电源开关

CM1110 还集成了一个在模拟输入 AIN3/REFN1 和 AVSS 之间低阻值的开关。在桥式传感器应用中，该电源开关可使桥式电路在无需采样转换时掉电，以此降低系统功耗。如果寄存器 PSW 配置为 1，该开关将在发出 START/SYNC 命令后自动闭合，并且在发出 POWERDOWN 命令后断开。需要注意的是，单次转换模式下，开关将始终保持闭合状态。如果寄存器 PSW 配置为 0，开关断开，这也是默认配置状态。

## 调制器

CM1110 中的  $\Delta\Sigma$  调制器用于将模拟输入电压转换为经脉冲调制(PCM)的数据流。调制器以时钟频率  $f_{MOD} = f_{CLK} / 16$  运行，而  $f_{CLK}$  可由内部振荡器或外部时钟源提供。使用内部振荡器或 4.096MHz 外部时钟时，各工作模式下的调制器频率  $f_{MOD}$  为 256kHz。

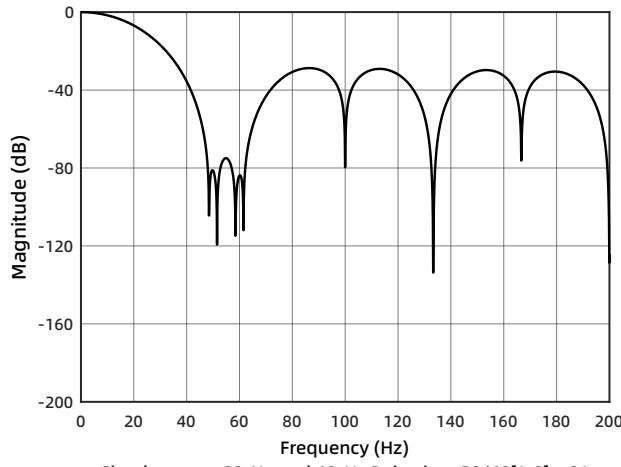

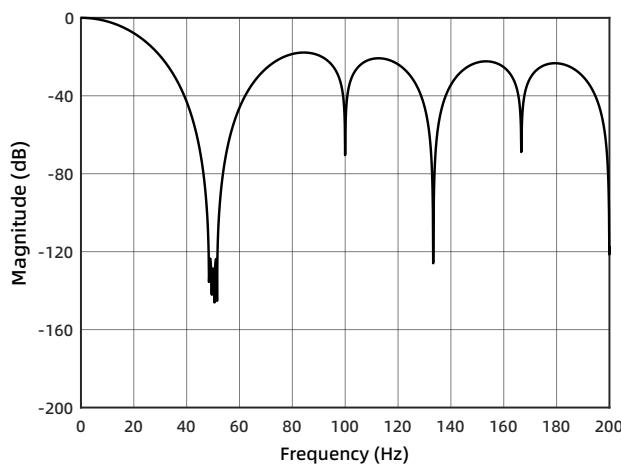

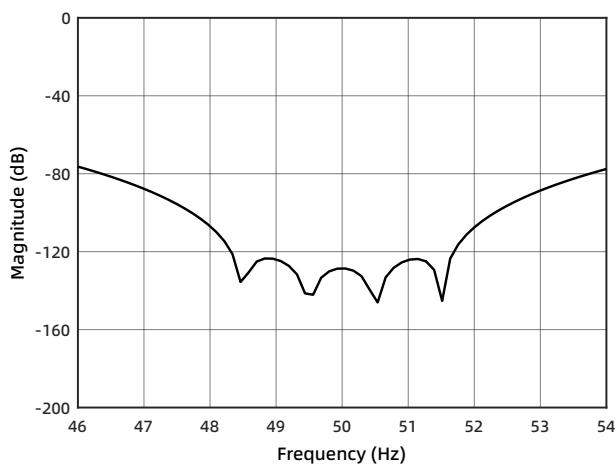

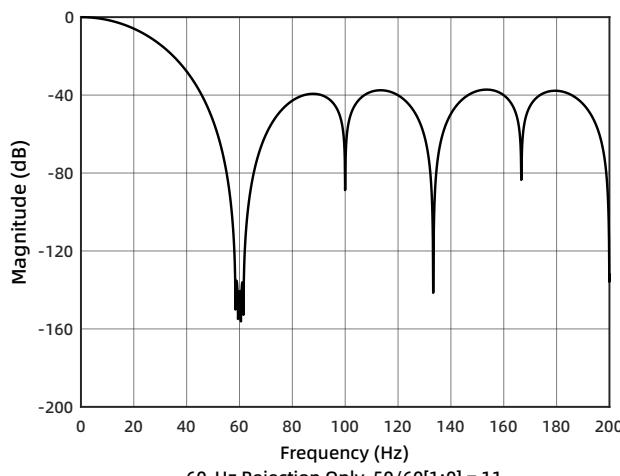

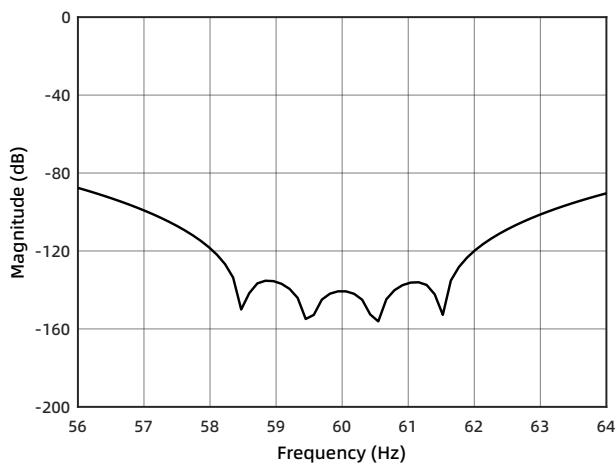

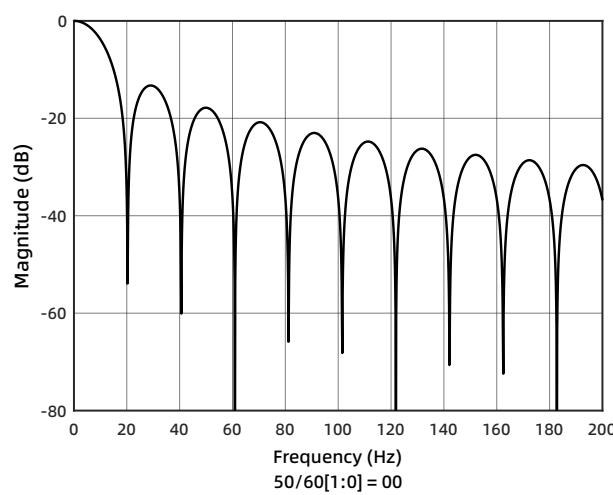

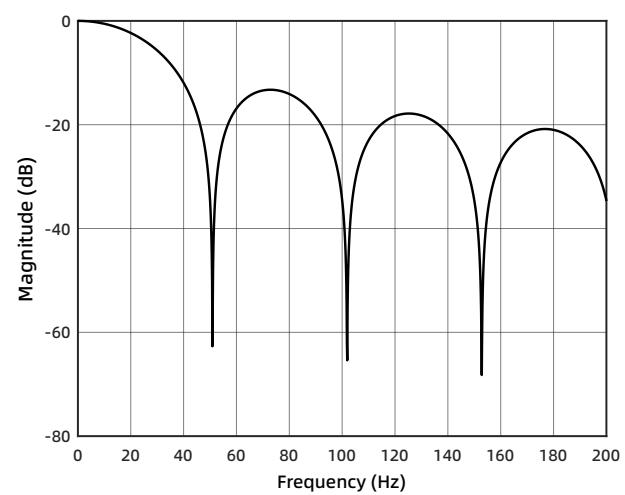

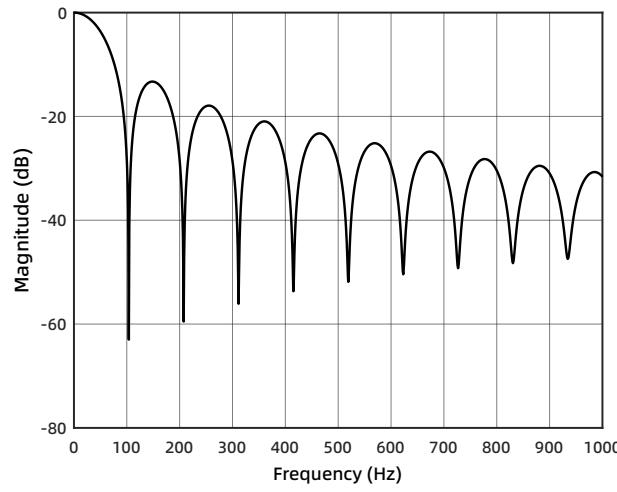

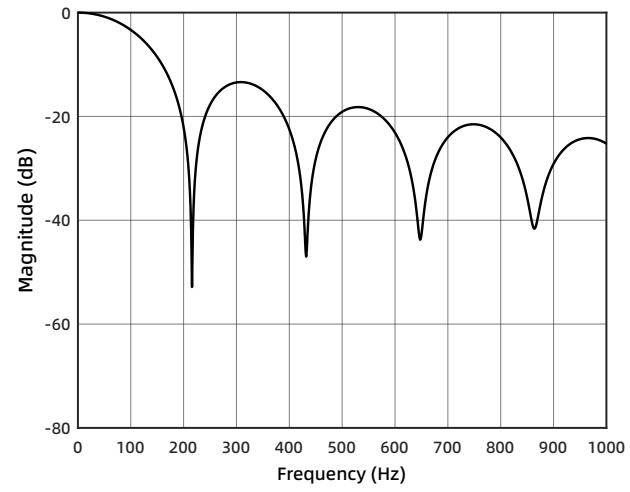

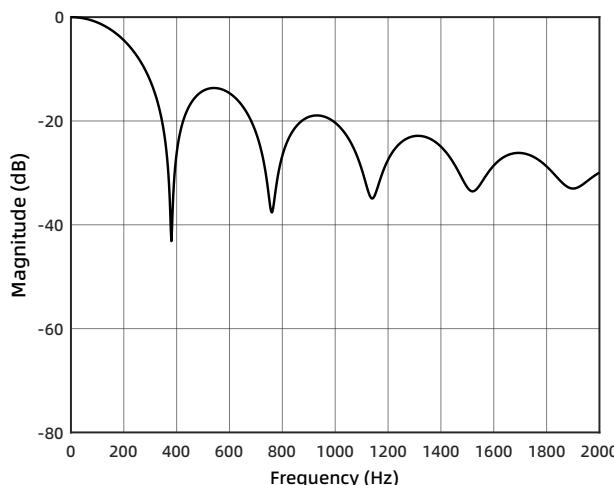

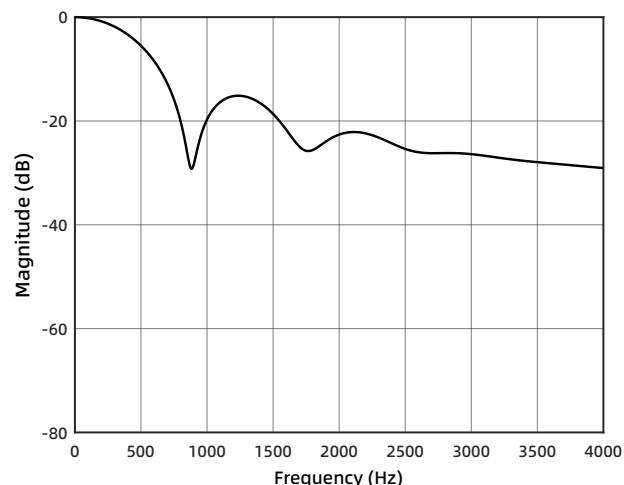

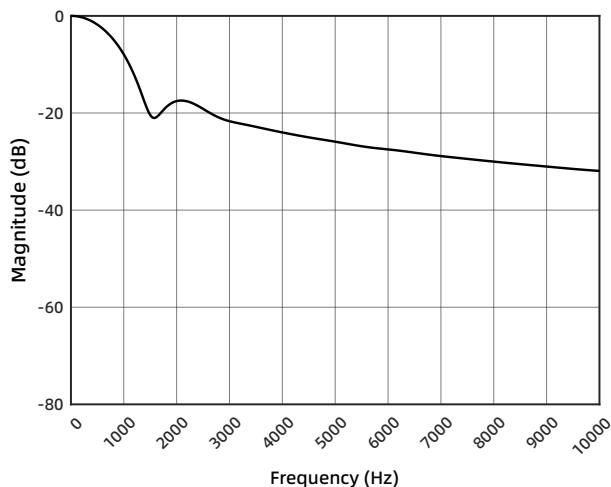

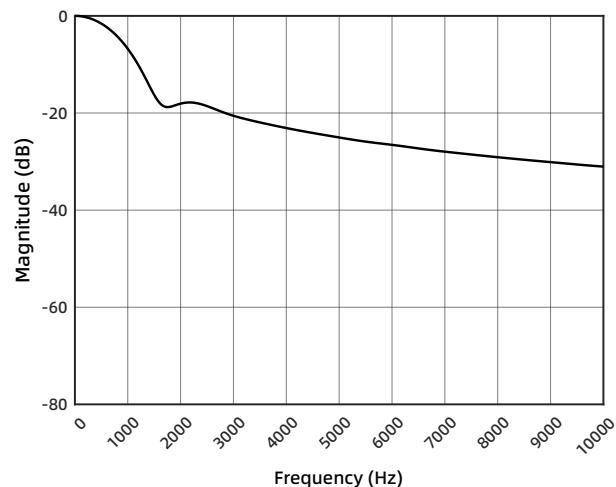

图 38 滤波器响应 (DR = 20SPS)

## 数字滤波器

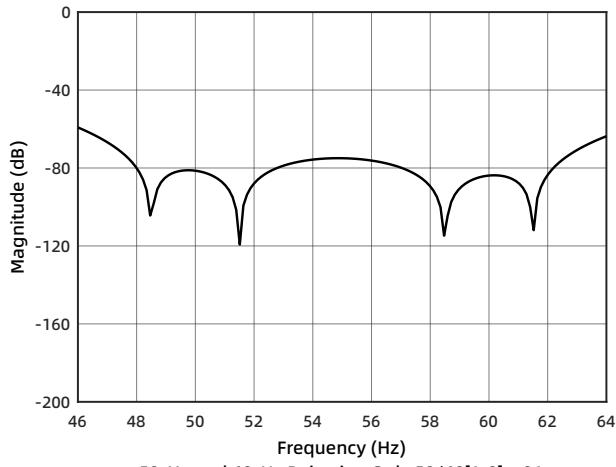

CM1110 采用一个线性相位有限冲激响应(FIR)数字滤波器，能够针对调制器传输的数字数据流进行滤波和抽取。该数字滤波器根据不同数据速率自动调节，在单一周期内可始终达到稳定状态。当数据速率为 5SPS 和 20SPS 时，通过配置寄存器 50/60[1:0]，可实现滤波器对 50Hz 和 60Hz 的工频抑制。图 38 至图 51 所示为使用内部振荡器或 4.096MHz 外部时钟时，不同输出数据速率对应的数字滤波器频率响应。

滤波器陷波频率和输出数据速率根据时钟频率确定。例如，当使用 4.096MHz 时钟时，于 20Hz 频率处产生陷波，如果使用 2.048MHz 时钟时，产生陷波的频率为 10Hz。请注意，内部振荡器随温度变化，如电气规格表所述。数据速率或转换时间随之发生变化，因此滤波器陷波也按相同比例发生变化。如需更为精确的在特定频率下产生滤波器陷波，则考虑使用外部精密时钟源。

图 39 滤波器响应详细视图 (DR = 20SPS)

图 40 滤波器响应 (DR = 20SPS)

图 41 滤波器响应详细视图 (DR = 20SPS)

图 42 滤波器响应 (DR = 20SPS)

图 43 滤波器响应详细视图 (DR = 20SPS)

图 44 滤波器响应 (DR = 20SPS)

图 45 滤波器响应 (DR = 50SPS)

图 46 滤波器响应 (DR = 100SPS)

图 47 滤波器响应 (DR = 200SPS)

图 48 滤波器响应 (DR = 333SPS)

图 49 滤波器响应 (DR = 666SPS)

图 50 滤波器响应 (DR = 1kSPS)

图 51 滤波器响应 (DR = 2kSPS)

## 低噪声 PGA

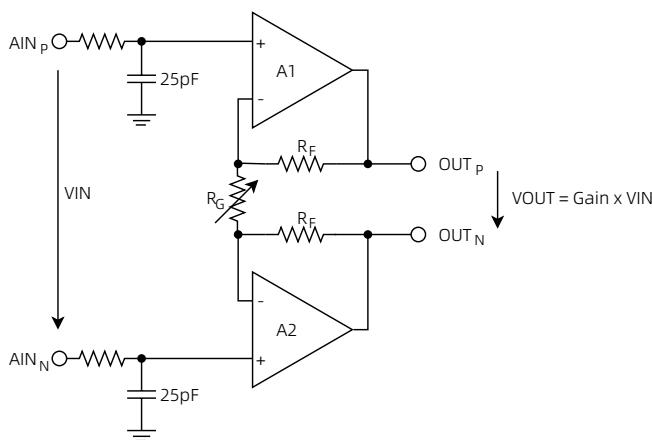

CM1110 具有一个低噪声、低漂移、高输入阻抗的 PGA。通过配置寄存器 GAIN[2:0]，PGA 增益可设置为 1、2、4、8、16、32、64 或 128。图 52 所示为 PGA 的简化框图。PGA 由两个斩波稳定放大器 (A1 和 A2) 及设置 PGA 增益的电阻反馈网络组成。PGA 输入配有一个电磁干扰 (EMI) 滤波器。

图 52 简化的 PGA 示意图

VIN 表示差分输入电压  $VIN = VAINP - VAINN$ 。PGA 增益可通过公式[2]进行计算：

$$\text{增益} = 1 + 2R_F/R_G \quad [2]$$

增益可通过芯片内部的可调电阻 RG 进行更改。PGA 的差分满量程输入电压范围 (FSR) 由增益和所用基准电压定义，如公式[3]所示：

$$FSR = \pm VREF/GAIN \quad [3]$$

表 2 所示为使用 2.048V 内部基准电压时的满量程范围。

表 2 PGA 满量程范围

| 增益设置 | FSR          |

|------|--------------|

| 1    | $\pm 2.048V$ |

| 2    | $\pm 1.024V$ |

| 4    | $\pm 0.512V$ |

| 8    | $\pm 0.256V$ |

| 16   | $\pm 0.128V$ |

| 32   | $\pm 0.064V$ |

| 64   | $\pm 0.032V$ |

| 128  | $\pm 0.016V$ |

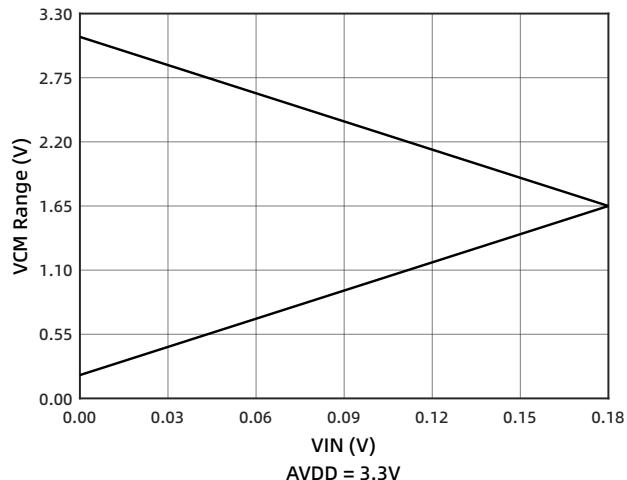

## PGA 共模电压要求

为了始终处于 PGA 的线性工作范围内，输入信号必须满足本节介绍的特定要求。

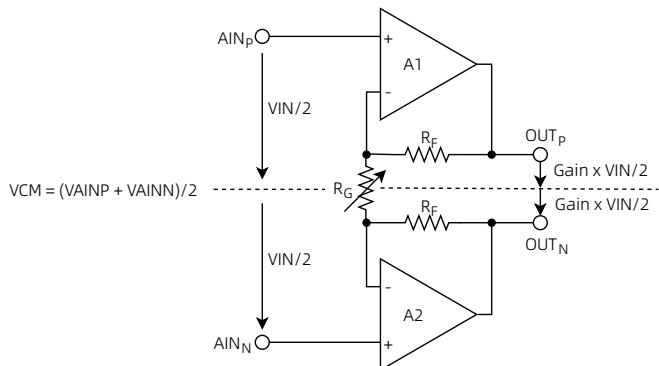

图 52 中两个放大器 (A1 和 A2) 的输出摆幅距离电源 (AVSS 和 AVDD) 不得低于 200mV。如果输出  $OUT_P$  和  $OUT_N$  驱动至距离电源轨电压 200mV 范围内，放大器将达到饱和并因此进入非线性状态。为防止出现此类非线性工作条件，输出电压必须满足公式[4]的要求：

$$AVSS + 0.2V \leq VOUTN, VOUTP \leq AVDD - 0.2V \quad [4]$$

可将公式[4]的要求换算为针对 PGA 输入 ( $AIN_P$  和  $AIN_N$ ) 的要求，这样无需直接访问 PGA 输出。PGA 采用对称设计，因此可假设 PGA 的输出共模电压与输入信号共模电压相等，如图 53 所示。

图 53 PGA 共模电压

共模电压通过公式[5]进行计算：

$$VCM = (VAINP + VAINN)/2 = (VOUTP + VOUTN)/2 \quad [5]$$

PGA 输入 ( $AIN_P$  和  $AIN_N$ ) 电压可表示为公式[6]和公式[7]：

$$VAINP = VCM + VIN/2 \quad [6]$$

$$VAINN = VCM - VIN/2 \quad [7]$$

此后，输出电压 ( $VOUTP$  和  $VOUTN$ ) 可根据公式[8]和公式[9]进行计算：

$$VOUTP = VCM + GAIN \times VIN/2 \quad [8]$$

$$VOUTN = VCM - GAIN \times VIN/2 \quad [9]$$

现可将放大器 A1 和 A2 的输出电压要求 (公式[4]) 通过公式[8]和公式[9]换算为针对输入共模电压范围的要求，具体内容在公式[10]和公式[11]中给出：

$$VCM(MIN) \geq AVSS + 0.2V + GAIN \times VIN(MAX)/2 \quad [10]$$

$$VCM(MAX) \leq AVDD - 0.2V - GAIN \times VIN(MAX)/2 \quad [11]$$

为计算最小和最大共模电压限值，必须使用应用中出现的最高差分输入电压 ( $VIN(MAX)$ )。 $VIN(MAX)$  可小于可能出现的最大 FSR 值。

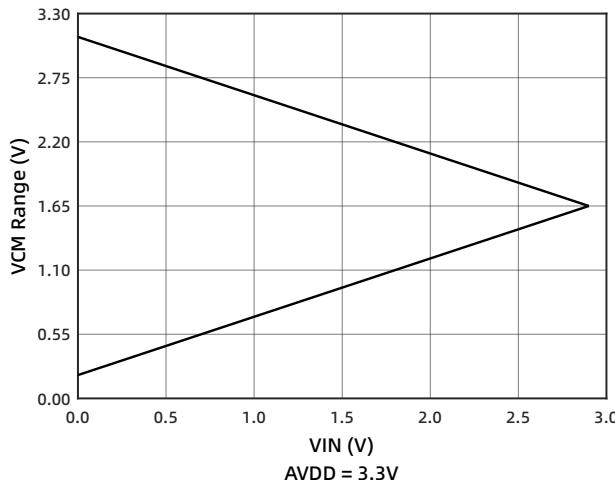

图 55 和图 56 以图像形式表示当  $AVDD = 3.3V$  和  $AVSS = 0V$ ，增益分别为 1 和 16 时的共模电压限值。

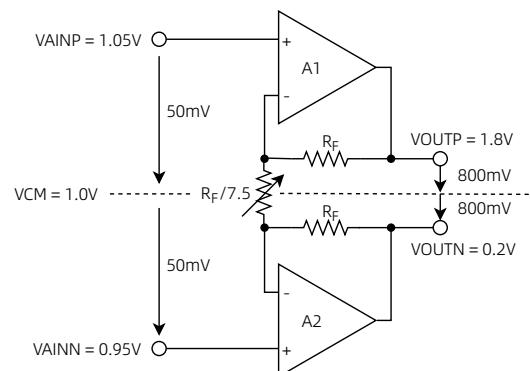

下文中的讨论介绍如何将公式[10]至公式[11]应用于假设性应用。本示例的设置条件为  $AVDD = 3.3V$ 、 $AVSS = 0V$ 、增益 = 16，同时采用外部基准电压  $VREF = 2.5V$ 。可施加的最高差分输入电压  $VIN = VAINP - VAINN$  随之限制为满量程范围  $FSR = \pm 2.5V/16 = \pm 0.156V$ 。因此，公式[10]至公式[11]可得出允许的  $VCM$  范围  $1.45V \leq VCM \leq 1.85V$ 。

例如，如果与该示例输入相连的传感器信号未采用完整满量程范围，而是限制为  $VIN(MAX) = \pm 0.1V$ ，则缩小的输入信号幅值会将  $VCM$  限制范围扩展至  $1.0V \leq VCM \leq 2.3V$ 。

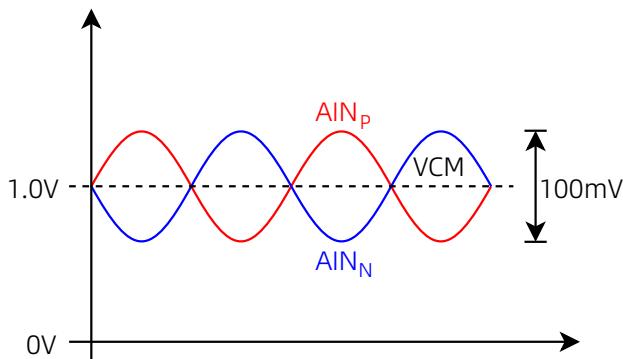

对于全差分传感器信号，每路输入 ( $AIN_P$ 、 $AIN_N$ ) 可在共模电压  $(VAINP + VAINN)/2$  (其限值必须保持在 1.0V 至 2.3V 范围内) 的  $\pm 50mV$  范围内摆动。对称型惠斯通电桥的输出即为一种全差分信号示例。图 54 所示为输入信号的共模电压处于下限的情况。在这种情况下， $VOUTN$  为 0.2V。进一步减小共模电压  $VCM$  或增大差分输入电压  $VIN$  均会导致  $VOUTN$  低于 0.2V 并导致放大器 A2 达到饱和状态。

图 54 VCM 处于下限的示例

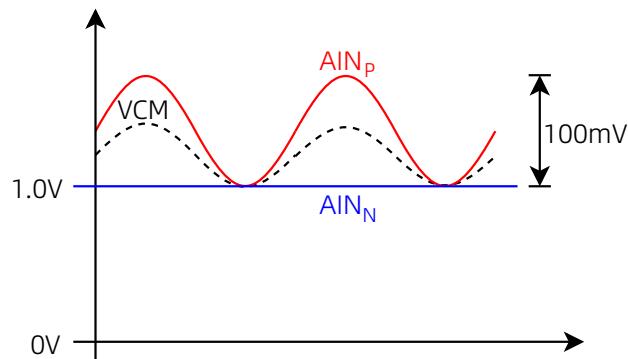

相反，RTD 的信号具有伪差分特性 (如果按 RTD 测量部分所示的方式实施)，其中负输入电压恒定不变 (但不等于 0V)，只有正输入电压发生变化。如果必须测量伪差分信号，本示例中的负输入必须在 0.95V 至 2.25V 的电压范围内偏置。正输入最高可在超出负输入  $VIN(MAX) = 100mV$  进行摆动。请注意，在这种

情况下, 共模电压与正输入电压同时发生变化。即, 当输入信号在  $0V \leq VIN \leq VIN(MAX)$  的范围内摆动时, 共模电压的摆动范围为  $VAINN \leq VCM \leq VAINN + VIN(MAX)/2$ 。满足最大输入电压  $VIN(MAX)$  的共模电压要求有助于在整个信号范围内满足要求。

图 55 共模电压限值 (增益 = 1)

图 56 共模电压限值 (增益 = 16)

图 57 全差分输入信号

图 58 伪差分输入信号

## 旁路 PGA

通过配置寄存器 BIT PGA\_BYPASS 为 1 禁用并旁路 PGA, 在增益为 1、2 和 4 的情况下可使用此配置。禁用 PGA 会降低整体功耗, 同时消除[公式\[10\]](#)至[公式\[11\]](#)针对共模输入电压范围 VCM 的限制。在 PGA 禁用的情况下, 可用的绝对输入电压和共模输入电压范围为( $AVSS - 0.1V \leq VAINx, VCM \leq AVDD + 0.1V$ )。

为测量以  $AVSS$  ( $AIN_P = VIN, AIN_N = AVSS$ ) 为负参考输入的单端信号, PGA 必须旁路。通过在外部将任一模拟输入与  $AVSS$  相连或通过多路选择器 (MUX[3:0]置为 1000 至 1011) 内部连接  $AVSS$ , 可将芯片配置为单端测量。如果以  $AINN = AVSS$  的设置配置内部多路选择器 (MUX[3:0] = 1000 至 1011), 则无论 PGA\_BYPASS 是否置 1 以及增益是否限制为 1、2 或 4, 均将自动旁路并禁用 PGA。对于将增益设置为大于 4 的情况, 该芯片会将增益限制为 4。

PGA 禁用后, 该芯片使用经缓冲的开关电容级实现增益值 1、2 和 4。开关电容级前的内部缓冲器可确保最大限度降低因电容充

放电而产生的输入负载效应。有关 PGA 禁用情况下的绝对输入电流 (流入或流出各路输入的电流) 以及差分输入电流 (正负输入间的绝对电流差值) 典型值, 请参见[图 19](#)至[图 24](#)。

对于输出阻抗较高的信号源, 仍需进行外部缓冲。请注意, 有源缓冲器会在引入噪声的同时引入偏移和增益误差。高精度应用需要密切关注上述因素。

## 输出数据速率

[表 3](#) 所示为各数据速率下的实际转换时间。表格内的值基于  $t_{CLK}$  周期计算所得, 所用外部时钟的频率  $f_{CLK} = 4.096MHz$ 。如果所用外部时钟的频率不等于 4.096MHz, 数据速率将按比例调节。

在连续转换模式下, 数据速率对应的时间为一个  $\overline{DRDY}$  下降沿至下一  $\overline{DRDY}$  下降沿。首次转换始于 START/SYNC 命令最后一个 SCLK 下降沿后的  $210 \cdot t_{CLK}$  (普通模式、占空比模式) 或  $114 \cdot t_{CLK}$  (Turbo 模式)。

在单次转换模式下，数据速率对应的时间为 START/SYNC 命令的最后一个 SCLK 下降沿至  $\overline{\text{DRDY}}$  下降沿，经四舍五入变为下一个  $t_{\text{CLK}}$ 。在单次转换模式下，如果使用内部振荡器，则必须额外增加长达  $50\mu\text{s}$  振荡器唤醒时间。内部振荡器在 START/SYNC 命令的首个 SCLK 上升沿开始上电。如果使用的 SCLK 频率高于  $160\text{kHz}$ （普通模式，占空比模式）或  $320\text{kHz}$ （Turbo 模式），振荡器在 START/SYNC 命令结束后可能不会完全上电。该芯片等待内部振荡器完全上电，然后开始转换。

占空比模式与普通模式下的单次转换时间相同。有关占空比工作模式的更多详细信息，请参见[占空比模式](#)部分。

请注意，即使  $20\text{SPS}$  设置对应的转换时间不等于  $1/20\text{Hz} = 50\text{ms}$ ，该差异也不会影响  $50\text{Hz}$  或  $60\text{Hz}$  抑制。要实现  $50\text{Hz}$  和  $60\text{Hz}$  抑制（如[电气规格](#)表所述），外部时钟频率必须为  $4.096\text{MHz}$ 。使用内部振荡器时，转换时间和滤波器陷波的变化量等于[电气规格](#)表指定的振荡器精度变量。

表 3 转换时间

| 标称数据速率(SPS)     | -3dB 带宽(Hz) | 实际转换时间( $t_{\text{CLK}}$ ) |        |

|-----------------|-------------|----------------------------|--------|

|                 |             | 连续转换模式                     | 单次转换模式 |

| <b>普通模式</b>     |             |                            |        |

| 20              | 13.1        | 204800                     | 204960 |

| 50              | 21.5        | 81920                      | 82080  |

| 100             | 41.3        | 40960                      | 41120  |

| 200             | 84.6        | 20480                      | 20640  |

| 333             | 155         | 12304                      | 12448  |

| 666             | 285         | 6160                       | 6304   |

| 1000            | 495         | 4096                       | 4256   |

| <b>占空比模式</b>    |             |                            |        |

| 5               | 13.1        | 819200                     | 不适用    |

| 12.5            | 21.5        | 327680                     | 不适用    |

| 25              | 41.3        | 163840                     | 不适用    |

| 50              | 84.6        | 81920                      | 不适用    |

| 83.25           | 155         | 49216                      | 不适用    |

| 166.5           | 285         | 24640                      | 不适用    |

| 250             | 495         | 16384                      | 不适用    |

| <b>Turbo 模式</b> |             |                            |        |

| 40              | 26.2        | 102400                     | 102560 |

| 100             | 39.6        | 40960                      | 41120  |

| 200             | 84.6        | 20480                      | 20640  |

| 400             | 165         | 10240                      | 10400  |

| 666             | 311.9       | 6152                       | 6304   |

| 1333            | 656         | 3080                       | 3232   |

| 2000            | 990         | 2048                       | 2208   |

## 噪声性能

$\Delta\Sigma$  ADC 基于过采样原则，其输入信号在高频下（调制器频率）进行采样，随后在数字域中进行滤波和抽取，从而在相应输出数据速率下生成转换结果。调制器频率与输出数据速率的比值称为过采样率 (OSR)。通过增加 OSR 降低输出数据速率，ADC 的噪声性能可以被优化。即当输出数据速率下降时，获取一个转换结果需要对内部调制器的更多样本求取平均值，因此输入参考噪声下降。增大增益同样能够降低输入参考噪声，适用于测量低幅度信号的应用。

表 4 至表 11 总结了芯片的噪声性能。这些数据代表  $TA = 25^\circ\text{C}$  并使用 2.048V 内部基准电压时的典型噪声性能。显示的数据为在约 0.75 秒的时间内针对单一芯片读数求取平均值的结果，此类数据的测定条件为输入在芯片内部短接在一起。表 4、表 6、表 8 和表 10 列出了不同条件下输入参考噪声（单位为

$\mu\text{VRms}$ ）。请注意，峰峰值噪声以  $\mu\text{Vpp}$  为单位在括号中显示。表 5、表 7、表 9 和表 11 列出了根据  $\mu\text{VRms}$  值计算得出的相应数据有效位数 (ENOB)。该计算过程通过公式[12]完成。请注意，使用公式[13]并根据噪声峰峰值计算得出的无噪声位在括号中显示。

要在使用除 2.048V 外的其他基准电压时计算 ENOB 数和无噪声位，请使用公式[12]至公式[14]：

$$\text{ENOB} = \ln(\text{满量程范围}/\text{VRms 噪声})/\ln(2) \quad [12]$$

$$\text{无噪声位} = \ln(\text{满量程范围}/\text{Vpp 噪声})/\ln(2) \quad [13]$$

$$\text{满量程范围} = 2\text{VREF}/\text{GAIN} \quad [14]$$

表 4 PGA 启用时的均方根和峰峰值噪声  $\mu\text{VRms}$  ( $\mu\text{Vpp}$ )。条件：AVDD = 3.3V, AVSS = 0V, 普通模式, 内部基准电压 = 2.048V

| 数据速率<br>(SPS) | 增益 (PGA 启用)  |               |               |              |              |             |             |             |

|---------------|--------------|---------------|---------------|--------------|--------------|-------------|-------------|-------------|

|               | 1            | 2             | 4             | 8            | 16           | 32          | 64          | 128         |

| 20            | 62.5 (62.5)  | 31.25 (31.25) | 15.63 (15.63) | 7.81 (7.81)  | 3.91 (3.91)  | 1.95 (1.95) | 0.98 (0.98) | 0.49 (0.49) |

| 50            | 62.5 (62.5)  | 31.25 (31.25) | 15.63 (15.63) | 7.81 (7.81)  | 3.91 (3.91)  | 1.95 (1.95) | 0.98 (0.98) | 0.49 (0.49) |

| 100           | 62.5 (62.5)  | 31.25 (31.25) | 15.63 (15.63) | 7.81 (7.81)  | 3.91 (3.91)  | 1.95 (1.95) | 0.98 (0.98) | 0.49 (1.46) |

| 200           | 62.5 (125)   | 31.25 (62.5)  | 15.63 (31.25) | 7.81 (7.81)  | 3.91 (3.91)  | 1.95 (1.95) | 0.98 (2.93) | 0.49 (1.46) |

| 333           | 62.5 (125)   | 31.25 (62.5)  | 15.63 (31.25) | 7.81 (15.63) | 3.91 (7.81)  | 1.95 (3.91) | 0.98 (2.93) | 0.49 (2.44) |

| 666           | 62.5 (187.5) | 31.25 (93.75) | 15.63 (31.25) | 7.81 (23.44) | 3.91 (11.72) | 1.95 (5.86) | 0.98 (3.91) | 0.64 (4.39) |

| 1000          | 62.5 (187.5) | 31.25 (93.75) | 15.63 (62.5)  | 7.81 (31.25) | 3.91 (19.53) | 1.95 (7.81) | 0.98 (6.84) | 0.86 (5.86) |

表 5 PGA 启用时的有效分辨率和无噪声分辨率。条件：AVDD = 3.3V, AVSS = 0V, 普通模式, 内部基准电压 = 2.048V

| 数据速率<br>(SPS) | 增益 (PGA 启用) |            |         |            |            |            |            |               |

|---------------|-------------|------------|---------|------------|------------|------------|------------|---------------|

|               | 1           | 2          | 4       | 8          | 16         | 32         | 64         | 128           |

| 20            | 16 (16)     | 16 (16)    | 16 (16) | 16 (16)    | 16 (16)    | 16 (16)    | 16 (16)    | 16 (16)       |

| 50            | 16 (16)     | 16 (16)    | 16 (16) | 16 (16)    | 16 (16)    | 16 (16)    | 16 (16)    | 16 (16)       |

| 100           | 16 (16)     | 16 (16)    | 16 (16) | 16 (16)    | 16 (16)    | 16 (16)    | 16 (16)    | 16 (14.42)    |

| 200           | 16 (15)     | 16 (15)    | 16 (15) | 16 (15)    | 16 (15)    | 16 (16)    | 16 (14.42) | 16 (14.42)    |

| 333           | 16 (15)     | 16 (15)    | 16 (15) | 16 (15)    | 16 (15)    | 16 (15)    | 16 (14.42) | 16 (13.68)    |

| 666           | 16 (14.42)  | 16 (14.42) | 16 (15) | 16 (14.42) | 16 (14.42) | 16 (14.42) | 16 (14)    | 15.61 (12.83) |

| 数据速率<br>(SPS) | 增益 (PGA 启用) |            |         |         |            |         |            |               |

|---------------|-------------|------------|---------|---------|------------|---------|------------|---------------|

|               | 1           | 2          | 4       | 8       | 16         | 32      | 64         | 128           |

| 1000          | 16 (14.42)  | 16 (14.42) | 16 (14) | 16 (14) | 16 (13.68) | 16 (14) | 16 (13.19) | 15.19 (12.42) |

表 6 PGA 禁用时的均方根和峰峰值噪声  $\mu\text{Vrms}$  ( $\mu\text{Vpp}$ )。条件: AVDD = 3.3V, AVSS = 0V, 普通模式, 内部基准电压 = 2.048V

| 数据速率 (SPS) | 增益 (PGA 禁用)  |               |               |

|------------|--------------|---------------|---------------|

|            | 1            | 2             | 4             |

| 20         | 62.5 (62.5)  | 31.25 (31.25) | 15.63 (15.63) |

| 50         | 62.5 (62.5)  | 31.25 (31.25) | 15.63 (15.63) |

| 100        | 62.5 (62.5)  | 31.25 (31.25) | 15.63 (15.63) |

| 200        | 62.5 (62.5)  | 31.25 (62.5)  | 15.63 (31.25) |

| 333        | 62.5 (125)   | 31.25 (62.5)  | 15.63 (31.25) |

| 666        | 62.5 (187.5) | 31.25 (93.75) | 15.63 (46.88) |

| 1000       | 62.5 (250)   | 31.25 (93.75) | 15.63 (78.13) |

表 7 PGA 禁用时的有效分辨率和无噪声分辨率。条件: AVDD = 3.3V, AVSS = 0V, 普通模式, 内部基准电压 = 2.048V

| 数据速率 (SPS) | 增益 (PGA 禁用) |            |            |

|------------|-------------|------------|------------|

|            | 1           | 2          | 4          |

| 20         | 16 (16)     | 16 (16)    | 16 (16)    |

| 50         | 16 (16)     | 16 (16)    | 16 (16)    |

| 100        | 16 (16)     | 16 (16)    | 16 (16)    |

| 200        | 16 (16)     | 16 (15)    | 16 (15)    |

| 333        | 16 (15)     | 16 (15)    | 16 (15)    |

| 666        | 16 (14.42)  | 16 (14.42) | 16 (14.42) |

| 1000       | 16 (14)     | 16 (14.42) | 16 (13.68) |

表 8 PGA 启用时的均方根和峰峰值噪声  $\mu\text{Vrms}$  ( $\mu\text{Vpp}$ )。条件: AVDD = 3.3V, AVSS = 0V, Turbo 模式, 内部基准电压 = 2.048V

| 数据速率<br>(SPS) | 增益 (PGA 启用) |               |               |              |              |             |             |             |

|---------------|-------------|---------------|---------------|--------------|--------------|-------------|-------------|-------------|

|               | 1           | 2             | 4             | 8            | 16           | 32          | 64          | 128         |

| 40            | 62.5 (62.5) | 31.25 (31.25) | 15.63 (15.63) | 7.81 (7.81)  | 3.91 (3.91)  | 1.95 (1.95) | 0.98 (0.98) | 0.49 (0.49) |

| 100           | 62.5 (62.5) | 31.25 (31.25) | 15.63 (15.63) | 7.81 (7.81)  | 3.91 (3.91)  | 1.95 (1.95) | 0.98 (0.98) | 0.49 (1.46) |

| 200           | 62.5 (62.5) | 31.25 (62.5)  | 15.63 (31.25) | 7.81 (7.81)  | 3.91 (3.91)  | 1.95 (1.95) | 0.98 (2.93) | 0.49 (1.46) |

| 400           | 62.5 (125)  | 31.25 (62.5)  | 15.63 (31.25) | 7.81 (15.63) | 3.91 (11.72) | 1.95 (5.86) | 0.98 (3.91) | 0.49 (2.44) |

| 数据速率<br>(SPS) | 增益 (PGA 启用)  |                |                |              |              |              |              |             |

|---------------|--------------|----------------|----------------|--------------|--------------|--------------|--------------|-------------|

|               | 1            | 2              | 4              | 8            | 16           | 32           | 64           | 128         |

| 666           | 62.5 (187.5) | 31.25 (93.75)  | 15.63 (31.25)  | 7.81 (15.63) | 3.91 (11.72) | 1.95 (5.86)  | 0.98 (3.91)  | 0.66 (3.91) |

| 1333          | 62.5 (187.5) | 31.25 (93.75)  | 15.63 (62.5)   | 7.81 (31.25) | 3.91 (15.63) | 1.95 (9.77)  | 1.1 (5.86)   | 0.9 (5.86)  |

| 2000          | 62.5 (375)   | 31.25 (218.75) | 16.59 (109.38) | 8.56 (54.69) | 4.49 (27.34) | 2.31 (15.63) | 1.83 (11.72) | 1.15 (8.3)  |

表 9 PGA 启用时的有效分辨率和无噪声分辨率。条件: AVDD = 3.3V, AVSS = 0V, Turbo 模式, 内部基准电压 = 2.048V

| 数据速率<br>(SPS) | 增益 (PGA 启用) |            |               |               |              |            |               |               |

|---------------|-------------|------------|---------------|---------------|--------------|------------|---------------|---------------|

|               | 1           | 2          | 4             | 8             | 16           | 32         | 64            | 128           |

| 40            | 16 (16)     | 16 (16)    | 16 (16)       | 16 (16)       | 16 (16)      | 16 (16)    | 16 (16)       | 16 (16)       |

| 100           | 16 (16)     | 16 (16)    | 16 (16)       | 16 (16)       | 16 (16)      | 16 (16)    | 16 (16)       | 16 (14.42)    |

| 200           | 16 (16)     | 16 (15)    | 16 (15)       | 16 (16)       | 16 (16)      | 16 (16)    | 16 (14.42)    | 16 (14.42)    |

| 400           | 16 (15)     | 16 (15)    | 16 (15)       | 16 (15)       | 16 (14.42)   | 16 (14.42) | 16 (14)       | 16 (13.68)    |

| 666           | 16 (14.42)  | 16 (14.42) | 16 (15)       | 16 (15)       | 16 (14.42)   | 16 (14.42) | 16 (14)       | 15.56 (13)    |

| 1333          | 16 (14.42)  | 16 (14.42) | 16 (14)       | 16 (14)       | 16 (14)      | 16 (13.68) | 15.83 (13.42) | 15.12 (12.42) |

| 2000          | 16 (13.42)  | 16 (13.19) | 15.91 (13.19) | 15.87 (13.19) | 15.8 (13.19) | 15.76 (13) | 15.09 (12.42) | 14.77 (11.91) |

表 10 PGA 禁用时的均方根和峰峰值噪声  $\mu$ Vrms ( $\mu$ Vpp)。条件: AVDD = 3.3V, AVSS = 0V, Turbo 模式, 内部基准电压 = 2.048V

| 数据速率 (SPS) | 增益 (PGA 禁用)  |               |               |

|------------|--------------|---------------|---------------|

|            | 1            | 2             | 4             |

| 40         | 62.5 (62.5)  | 31.25 (31.25) | 15.63 (15.63) |

| 100        | 62.5 (62.5)  | 31.25 (31.25) | 15.63 (15.63) |

| 200        | 62.5 (62.5)  | 31.25 (62.5)  | 15.63 (31.25) |

| 400        | 62.5 (125)   | 31.25 (62.5)  | 15.63 (31.25) |

| 666        | 62.5 (125)   | 31.25 (93.75) | 15.63 (46.88) |

| 1333       | 62.5 (250)   | 31.25 (125)   | 15.63 (93.75) |

| 2000       | 62.5 (312.5) | 32.19 (187.5) | 21.76 (125)   |

表 11 当 PGA 禁用时的有效分辨率和无噪声分辨率。条件: AVDD = 3.3V, AVSS = 0V, Turbo 模式, 内部基准电压 = 2.048V

| 数据速率 (SPS) | 增益 (PGA 禁用) |         |         |

|------------|-------------|---------|---------|

|            | 1           | 2       | 4       |

| 40         | 16 (16)     | 16 (16) | 16 (16) |

| 100        | 16 (16)     | 16 (16) | 16 (16) |

| 数据速率 (SPS) | 增益 (PGA 禁用) |               |            |

|------------|-------------|---------------|------------|

|            | 1           | 2             | 4          |

| 200        | 16 (15)     | 16 (15)       | 16 (15)    |

| 400        | 16 (15)     | 16 (15)       | 16 (15)    |

| 666        | 16 (15)     | 16 (14.42)    | 16 (14.42) |

| 1333       | 16 (14)     | 16 (14)       | 16 (13.42) |

| 2000       | 16 (13.68)  | 15.96 (13.42) | 15.52 (13) |

## 温度传感器

CM1110 内置了一个高精度温度传感器，将配置寄存器中的 TS 位置 1 以使能该传感器。温度传感器输出数据长度为 16 位，测温模式下，直接取 ADC 输出数据的 16 位即可。转换函数如下所示：

$$\text{温度} = 0.021 \times \text{ADC 输出结果 (十进制数值)} - 273^\circ\text{C}$$

## 功能与模式

### 上电和复位

芯片在上电过程中执行复位。复位过程耗时约 5.6ms。上电复位完成后，该芯片以默认寄存器设置执行一次单次转换，然后进入低功耗状态。完成转换后，DRDY管脚由高电平转换为低电平，这个电平跳变可以用于指示 CM1110 上电完成，可进入正常工作状态。

### 转换模式

CM1110 采用单次转换模式和连续转换模式。这两种模式可通过配置寄存器的 CM 位进行选择。

#### 单次转换模式

该模式下，CM1110 仅在发出 START/SYNC 命令后执行单次转换，然后返回低功耗状态，直到进行下次转换。低功耗状态下，除激励电流源之外的所有模拟电路均处于关断状态。此外，针对任一配置寄存器进行写操作均会开启新一次转换（如果写操作发生在转换过程中，那么当前的转换将被终止）。由于该芯片的数字滤波器在单一周期内达到稳定状态，因此每次转换均实现完全稳定（假设模拟输入信号在转换开始前稳定至最终值）。

#### 连续转换模式

该模式下，CM1110 在完成一次转换后，将结果置于输出缓冲器，并立即开启新的一次转换。

为启动连续转换模式，CM 位必须置 1 并且随即发出 START/SYNC 命令。START/SYNC 命令最后一个 SCLK 下降沿之后再延时  $210t_{CLK}$ （普通模式，占空比模式）或  $114t_{CLK}$ （Turbo 模式），进行首次转换。在进行的转换过程中针对任何配置寄存器进行写操作均会重启当前转换过程。建议始终在 CM 位置 1 后立即发送 START/SYNC 命令。

### 工作模式

除了转换模式不同外，该芯片还可采用不同工作模式，同时在各模式之间权衡功耗、噪声性能和输出数据速率。工作模式包括：普通模式、占空比模式、Turbo 模式及断电模式。

#### 普通模式

普通模式为上电后的默认工作模式。在该模式下， $\Delta\Sigma$  ADC 的内部调制器以时钟频率  $f_{MOD} = f_{CLK}/16$  运行，其中系统时钟 ( $f_{CLK}$ ) 由内部振荡器或外部时钟源提供。使用内部振荡器时，调制器频率为 256kHz。在普通模式下，使用内部振荡器时的输出数据速率范围为 20SPS 至 1kSPS。数据速率通过配置寄存器的 BIT DR[2:0]进行选择。如果使用时钟频率不等于 4.096MHz 的外部时钟源，数据速率将进行相应变化。例如，如果使用  $f_{CLK} = 2.048MHz$  的外部时钟，数据速率范围为 10SPS 至 500SPS。

#### 占空比模式

当数据速率降低时，由于获取一个转换结果需要对内部调制器的更多样本求取平均值，因此  $\Delta\Sigma$  ADC 的噪声性能通常有所改善。但是在一些应用场景中，这种低数据速率带来的噪声性能改善是不需要的，反而更关心功耗性能。对于此类应用，可以采用芯片

提供的自动占空比模式，通过在各转换过程之间周期性进入低功耗状态，从而显著降低能耗。CM1110 的运行占空比为 25%，意味着该芯片按照普通模式下的运行方式进行一次转换，但随后自动进入低功耗状态并持续三个连续转换周期。因此，占空比模式下的噪声性能与普通模式下采用四倍数据速率时的噪声性能相当。在占空比模式下，使用内部振荡器时的数据速率范围为 5SPS 至 250SPS。

#### Turbo 模式

对于数据速率（高达 2kSPS）要求较高的应用，该芯片可在 Turbo 模式下运行。Turbo 模式与普通模式转换频率相同，通过将采样倍数减半实现数据率加倍的效果。

#### 断电模式

发出 POWERDOWN 命令后，该芯片在完成当前转换后进入断电模式。在该模式下，所有模拟电路（包括电压基准和两个 IDAC）均断电，低侧电源开关断开，此时电流消耗仅为 400nA。在断电模式下，该芯片的配置寄存器设置保持不变，并可以响应命令，但不执行任何数据转换。

发出 START/SYNC 命令将唤醒该芯片并启动单次转换或连续转换，具体取决于寄存器 CM 的配置。请注意，写入任意配置寄存器也会唤醒该芯片，但无论 CM 如何配置，仅会启动单次转换。

### 系统自检

#### 传感器检测

为了协助检测可能出现的传感器故障，CM1110 内置两个  $10\mu A$  电流源。通过将配置寄存器的相应位 (BCS) 置 1 启用电流源，其中一个电流源连接至当前所选正模拟输入 ( $AIN_P$ ) 释放电流，而另一电流源连接所选负模拟输入 ( $AIN_N$ ) 吸收电流。

如果传感器发生开路，这些电流源将正输入拉至 AVDD，同时将负输入拉至 AVSS，从而得到满量程读数。满量程读数还可以表示传感器过载或缺少基准电压。近似为零的读数可能表示传感器短路。请注意，该偏置电流源的绝对值通常在  $\pm 10\%$  的范围内浮动，并且内部多路选择器开关导通时等效成小的串联电阻，因此即使传感器短路，多路选择器的导通电阻也会导致大于零的转换结果，这使得区分传感器短路和正常读数难度较大，当输入端存在阻容 (RC) 滤波器时尤其如此。

请注意，启用传感器偏置电流源后，功能传感器的 ADC 读数可能受到影响。建议在执行精密测量的过程中禁用该电流源，并且仅在测试传感器故障时启用。

#### 系统监测

CM1110 提供多种模拟电源和外部基准电压监测方法。要监测电压，必须在配置寄存器中针对内部多路选择器 (MUX[3:0]) 进行相应配置。无论在使用监测功能时如何设置配置寄存器，该芯片均会自动旁路 PGA 并将增益设置为 1。请注意，系统监测功能仅提供粗略结果，并非精密测量。

测量模拟电源 (MUX[3:0] = 1101) 时, 得出的转换结果约为  $(AVDD - AVSS)/6$ 。无论寄存器 VREF[1:0] 如何配置, 该芯片均使用 2.048V 内部基准进行测量。

监测外部基准电压源 (MUX[3:0] = 1100) 的其中之一时, 结果约为  $(V_{REFPx} - V_{REFNx})/6$ 。REFPx 和 REFNx 表示寄存器 VREF[1:0] 中配置的基准输入对。该芯片自动使用内部基准进行测量。

## 失调检测

内部多路选择器支持将两路 PGA 输入 ( $AIN_p$  和  $AIN_N$ ) 短接至中间供电电压  $(AVDD + AVSS)/2$ 。这种方式可用于测量并校准芯片失调电压, 具体方法为将短路输入电压读数的结果存储于微控制器中, 进而从后续读数中减去该结果。建议在输入短路的情况下获取多个读数, 进而针对结果求取平均值, 以降低噪声影响。

## 数字接口

### 串行接口

CM1110 的 SPI 兼容串行接口仅支持 SPI 模式 1 (CPOL = 0, CPHA = 1)，适用于读取转换数据、读写芯片配置寄存器以及控制芯片工作状态。该接口由 $\overline{CS}$ 、SCLK、DIN、DOUT/ $\overline{DRDY}$ 和 $\overline{DRDY}$ 组成，专用数据就绪信号 ( $\overline{DRDY}$ ) 可配置为与 DOUT/ $\overline{DRDY}$ 共享。如果串行总线未与其他任何器件共享，则 $\overline{CS}$ 可永久与低电平相连，以便仅需使用信号 SCLK、DIN 和 DOUT/ $\overline{DRDY}$ 与芯片进行通信。

#### 片选 ( $\overline{CS}$ )

片选信号 $\overline{CS}$ 低电平有效，可选择芯片进行 SPI 通信。当多个芯片共享同一总线时，该特性非常有用。在串行通信过程中， $\overline{CS}$ 必须保持低电平。 $\overline{CS}$ 置为高电平后，串行接口随即复位，SCLK 将被忽略，DOUT/ $\overline{DRDY}$ 进入高阻抗状态，DOUT/ $\overline{DRDY}$ 无法指示数据何时就绪，此种情况下可以采用专用的 $\overline{DRDY}$ 管脚进行转换状态监测。如果串行总线未与其他外设共享， $\overline{CS}$ 可连接低电平。

#### 串行时钟 (SCLK)

SCLK 具备施密特触发输入，但依然建议 SCLK 信号尽量保持干净，以防数据在切换时产生毛刺。当串行接口处于空闲状态时，SCLK 保持低电平。

#### 数据就绪 ( $\overline{DRDY}$ )

$\overline{DRDY}$ 用于指示新转换结果准备就绪，低电平有效。 $\overline{DRDY}$ 将在下一 SCLK 上升沿转换回高电平。如果在连续转换模式下没有进行读取操作，则 $\overline{DRDY}$ 保持低电平，但在新的 $\overline{DRDY}$ 下降沿到来前会拉起一个  $2t_{MOD}$  的高电平脉冲，以便对转换结果更新进行指示。 $\overline{DRDY}$ 管脚输出状态不受 $\overline{CS}$ 管脚电平的影响。

#### 数据输入 (DIN)

DIN 用于向芯片输入命令或者寄存器数据，在 SCLK 的下降沿，将 DIN 管脚上的数据进行输入锁存。

#### 数据输出和数据就绪 (DOUT/ $\overline{DRDY}$ )

DOUT/ $\overline{DRDY}$ 用于读取芯片转换结果和寄存器数据，在 SCLK 的上升沿，将数据移位输出到管脚上。DOUT/ $\overline{DRDY}$ 在 $\overline{CS}$ 处于高电平时呈现高阻状态。

此外，通过将配置寄存器的 BIT DRDYM 置为高电平也可将 DOUT/ $\overline{DRDY}$ 管脚配置为数据就绪指示器。在新转换完成时，DOUT/ $\overline{DRDY}$ 与 $\overline{DRDY}$ 一样，同时跳变为低电平，指示新转换数据可用。两信号均可用于检测新数据是否准备就绪。然而，由于 DOUT/ $\overline{DRDY}$ 在 $\overline{CS}$ 处于高电平时禁用，因此当 SPI 总线连接多个芯片时，建议使用专用 $\overline{DRDY}$ 管脚针对转换结束进行监测。

### SPI 超时

CM1110 具备 SPI 超时复位功能，可用于在串行接口传输中断时恢复通信。该功能尤其适用于 $\overline{CS}$ 永久连接低电平且不用于构建通信序列的应用。如果在 55ms 内未发送完整命令，则串行接口复位，下一 SCLK 脉冲将开启新一通信周期。请参见 [调制器](#) 部分，了解有关不同工作模式下调制器频率 ( $f_{MOD} = 1/t_{MOD}$ ) 的详细信

息。对于 RREG 和 WREG 命令，一条完整的命令包括命令字节本身外加读取或写入的寄存器字节。

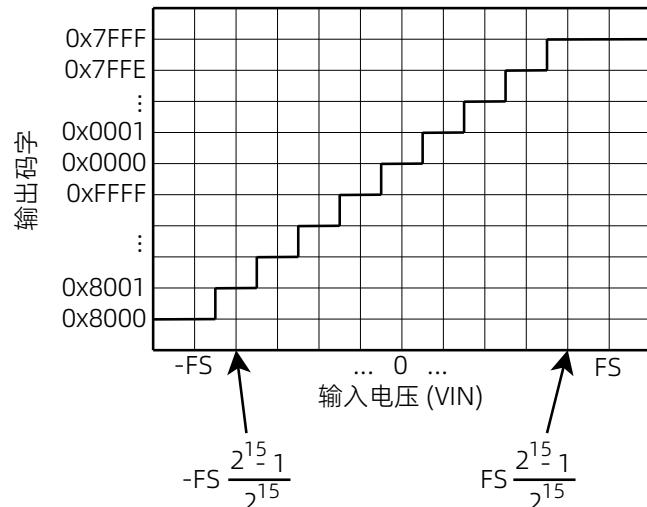

### 数据格式

CM1110 以二进制补码格式提供 16 位数据。最低有效位 (LSB) 的大小通过[公式\[15\]](#)进行计算。

$$1\text{LSB} = (2 \times \text{VREF}/\text{GAIN})/2^{16} = +\text{FS}/2^{15} \quad [15]$$

正满量程输入 [ $\text{VIN} \geq (+\text{FS} - 1 \text{ LSB}) = (\text{VREF}/\text{GAIN} - 1\text{LSB})$ ] 产生输出代码 7FFFh；负满量程输入 ( $\text{VIN} \leq -\text{FS} = -\text{VREF}/\text{GAIN}$ ) 产生输出代码 8000h。

[表 12](#) 总结了不同输入信号的理想输出码字。

表 12 理想输出码字与输入信号间的关系

| 输入信号<br>$\text{VIN} = (\text{VAINP} - \text{VAINN})$ | 理想输出码字 <a href="#">1</a> |

|------------------------------------------------------|--------------------------|

| $\geq \text{FS}(2^{15}-1)/2^{15}$                    | 7FFFh                    |

| $\text{FS}/2^{15}$                                   | 0001h                    |

| 0                                                    | 0000h                    |

| $-\text{FS}/2^{15}$                                  | FFFFh                    |

| $\leq -\text{FS}$                                    | 8000h                    |

注 1：排除噪声、INL、失调和增益误差的影响。

将模拟输入信号映射到输出码字，如[图 59](#) 所示。

图 59 码字转换图

### 命令

CM1110 通过六种不同命令控制其工作状态，如[表 13](#) 所示。其中四种命令为独立指令 (RESET、START/SYNC、POWERDOWN 和 RDATA)。寄存器读 (RREG) 和寄存器写 (WREG) 命令需要附加寄存器信息。

表 13 命令定义

| 命令         | 说明                       | 命令字节 1    |

|------------|--------------------------|-----------|

| RESET      | 复位芯片                     | 0000 011x |

| START/SYNC | 启动或重启转换                  | 0000 100x |

| POWERDOWN  | 进入断电模式                   | 0000 001x |

| RDATA      | 通过命令读取数据                 | 0001 xxxx |

| RREG       | 从配置寄存器 rr 开始读取 nn+1 字节数据 | 0010 rrnn |

| WREG       | 从配置寄存器 rr 开始写入 nn+1 字节数据 | 0100 rrnn |

注 1：操作数：rr = 配置寄存器（00 至 11），nn = 字节数 - 1（00 至 11）以及 x = 无关值。

### RESET (0000 011x)

将芯片复位为默认值。发送 RESET 命令后应至少等待 ( $50\mu s + 32t_{CLK}$ ) 方可继续发送其他命令。

### START/SYNC (0000 100x)

在单次转换模式下，START/SYNC 命令用于启动单次转换，或（在转换的发送过程中）复位数字滤波器，随后重启新一次转换。如果在连续转换模式下发送 START/SYNC 命令，则会复位数字滤波器并重启连续转换。

### POWERDOWN (0000 001x)

POWERDOWN 命令将芯片置于断电模式。该命令关断所有内部模拟组件、断开低侧开关、并关断两个 IDAC，但保持所有寄存器值。如果在转换过程中发出 POWERDOWN 命令，CM1110 将在当前转换完成后进入断电模式。

### RDATA (0001 xxxx)

RDATA 命令将最新转换结果载入输出移位寄存器。当没有监测数据就绪指示信号来进行同步数据读取时，可以通过 RDATA 读取命令结束时 DRDY 管脚上的电平状态，区分发送命令过程中是否产生了新的转换结果。DRDY 如果为低电平，表明产生了新的转换数据，还未被读出。DRDY 如果为高电平，表明没有产生新的转换数据，移位寄存器中已经加载了最新的转换结果。

### RREG (0010 rrnn)

RREG 命令从地址为 rr 的配置寄存器开始，读取 nn+1 个字节的寄存器数据。命令字节之后要持续发送时钟以保证 nn+1 个字节数据的读取，从而完成整个 RREG 命令。例如，从配置寄存器 1 (rr = 01) 开始读取三个字节 (nn = 10) 的命令为 0010 0110。

### WREG (0100 rrnn)

WREG 命令从地址为 rr 的配置寄存器开始，写入 nn+1 个字节的寄存器数据。命令字节之后要持续发送时钟以保证 nn+1 个字节数据的写入，从而完成整个 WREG 命令。例如，从配置寄存器 0 (rr = 00) 开始写入两个字节 (nn = 01) 的命令为 0100 0001。配置寄存器在最后一个 SCLK 下降沿更新。

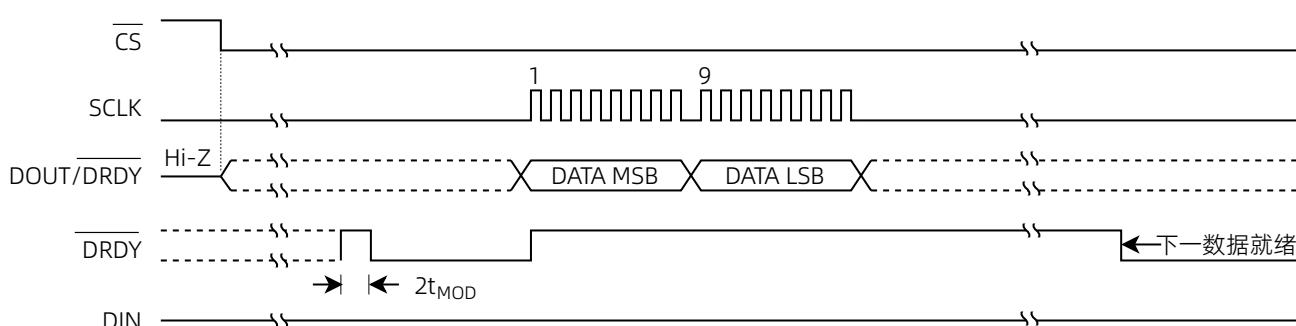

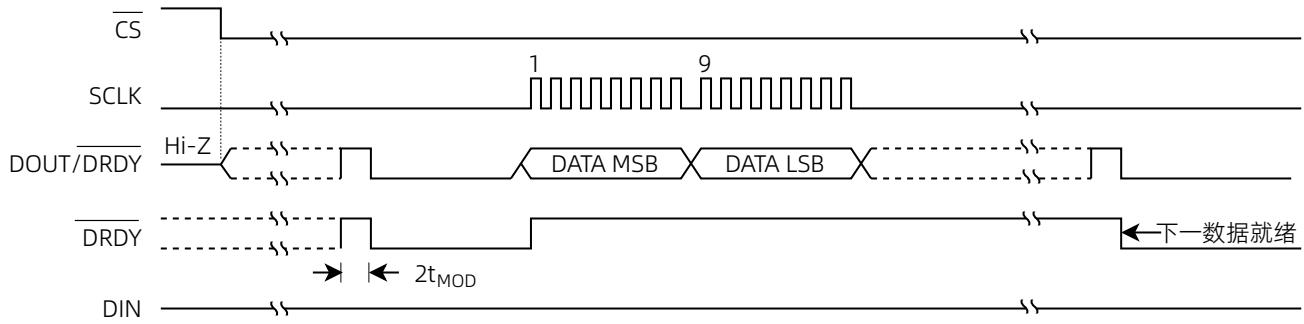

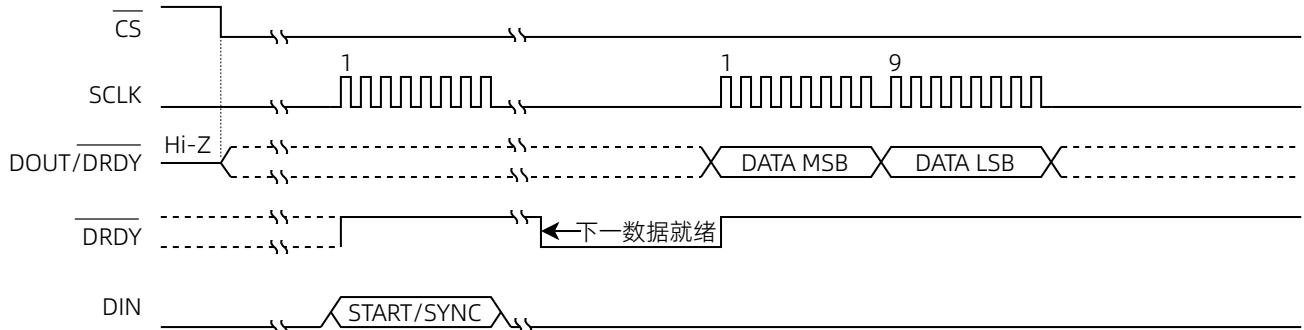

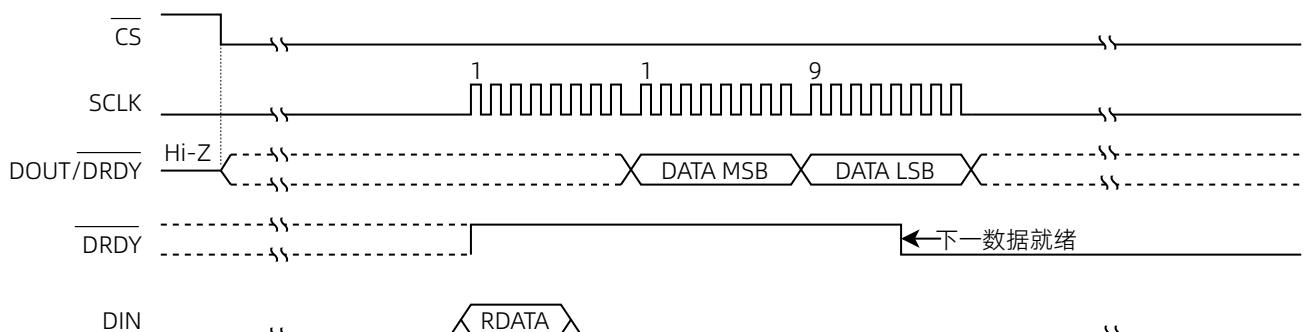

## 读取数据

输出管脚 DRDY 和 DOUT/DRDY（如果将配置寄存器的 BIT DRDYM 置为高电平）将在新数据准备就绪时变为低电平。转换数据写入内部数据缓冲区。该缓冲区中的数据可直接通过 DOUT/DRDY 进行读取（前提是 DRDY 降为低电平），无须担心损坏数据。无需发送 RDATA 命令。数据将在 SCLK 上升沿移出（MSB 首先移出），其中包括两个字节的数据。

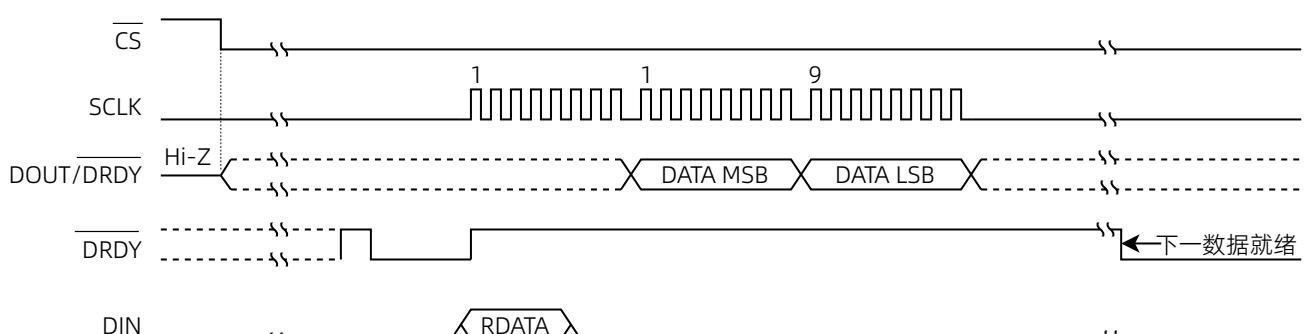

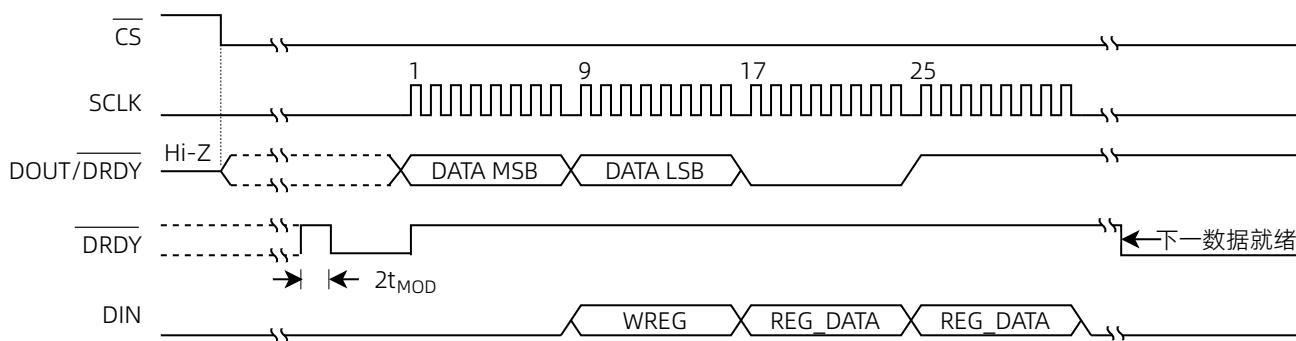

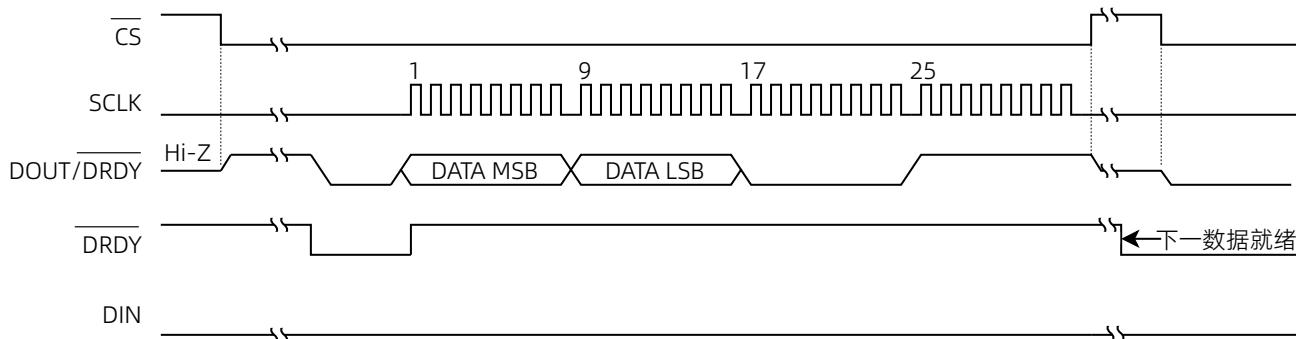

图 60 至图 62 所示为未使用 RDATA 命令时，在连续转换模式和单次转换模式下读取转换数据的时序图。

图 60 连续转换模式 (DRDYM = 0)

图 61 连续转换模式 (DRDY\_M = 1)

图 62 单次转换模式 (DRDY\_M = 0)

还可使用 RDATA 命令随时读取数据，无需与  $\overline{DRDY}$  信号同步。发出 RDATA 命令后，当前存储于数据缓冲区的转换结果在后续 SCLK 上升沿从 DOUT/DRDY 移出。也可使用 RDATA 命令连续读取数据，来替代监测  $\overline{DRDY}$  或 DOUT/DRDY。转换数据移出后，

可以通过轮询  $\overline{DRDY}$  管脚，来确定是否有新转换结果载入。如果在读操作期间完成了新的转换，但读取的是前一次转换数据，则  $\overline{DRDY}$  为低。否则，如果读取的是最新结果，则  $\overline{DRDY}$  为高。图 63 和图 64 所示为这两种情况对应的行为。

图 63 在 RDATA 命令过程中完成新转换时的  $\overline{DRDY}$  状态图 64 在 RDATA 命令过程中读取新转换结果时的  $\overline{DRDY}$  状态

## 发送命令

CM1110 的串行接口可在不使用 RDATA 命令进行读取转换数据时执行全双工操作。全双工操作意味着在读取转换数据的同时可针对命令进行解码。在数据读取操作过程中，可在任意完成 8 位数据读取后位置插入发送命令。如果插入的命令为 RREG 或 RDATA，当前的读取操作终止，转换数据损坏。对于 RREG 和 RDATA 命令，在命令字节后的第一个 SCLK 上升沿将数据输出到 DOUT/DRDY 管脚。为了确保读取数据不被中断，读取时保持 DIN 为低电平。

发送 WREG 命令不会破坏进行中的读操作。图 65 所示为在连续转换模式下读取转换数据时，发送 WREG 命令写入两配置寄存器的示例。命令随时钟移入后（在第 32 个 SCLK 下降沿之后），该芯片复位数字滤波器并开始以新寄存器设置进行转换。

请注意，串行接口在执行 RDATA 或 RREG 命令过程中无法进行解码。在这两个命令全部执行完成后（包括命令字节和相应的读取数据），才能够发出新命令。

图 65 在读取数据的同时发送 WREG 命令的示例

图 66 在读取转换结果后将 DOUT/DRDY 驱动为高电平的示例

## 连接多个芯片

将多个 CM1110 芯片与同一 SPI 总线相连时，通过各自独立的 CS 控制，可以实现 SCLK、DIN 和 DOUT/DRDY 的安全共享。因为 CS 为高电平时会使 DOUT/DRDY 进入高阻态，此时对应芯片只能通过专用的 DRDY 管脚来作为数据就绪指示。

在某些情况下，DRDY 管脚无法连接至微控制器。如微控制器上的通用输入/输出 (GPIO) 通道数不够用。因此，为了评估其中一个芯片何时准备好新的转换数据，微控制器会定期拉低相应芯片的 CS，然后查询 DOUT/DRDY 管脚的状态。如果 DOUT/DRDY 为低电平，说明产生新的转换数据，如果 DOUT/DRDY 为高电平，则无新转换数据产生。该过程要求 DOUT/DRDY 在读取各个转换结果之后以及在 CS 驱动为高电平之前呈高电平。为确保 DOUT/DRDY 驱动为高电平，在每次进行完数据读取操作之后都额外发送 8 个 SCLK (DIN 保持为低电平)，如图 66 所示。

# 寄存器

## CONFIG

CM1110 有 4 个 8 位配置寄存器，这些寄存器可通过串行接口使用 RREG 和 WREG 命令进行访问。配置寄存器可控制芯片的工作方式，并且可随时进行切换，而不会导致数据损坏。上电或复位

后，所有寄存器均设置为默认值 (0)。在断电模式下，所有寄存器的值均可保持。表 14 显示了配置寄存器的具体信息。

表 14 配置寄存器表

| 地址  | 名称      | 默认值 | 描述      |

|-----|---------|-----|---------|

| 00h | CONFIG0 | 00h | 配置寄存器 0 |

| 01h | CONFIG1 | 00h | 配置寄存器 1 |

| 02h | CONFIG2 | 00h | 配置寄存器 2 |

| 03h | CONFIG3 | 00h | 配置寄存器 3 |

### CONFIG0 (地址=00h)

| 位   | 名称        | 访问类型 | 复位 | 描述                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|-----------|------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | MUX[3:0]  | RW   | 0h | <p>输入多路选择器配置。</p> <p>对于 <math>AIN_N = AVSS</math> 的设置，PGA 必须禁用 (<math>PGA\_BYPASS = 1</math>)，并且仅可使用增益 1、2 和 4。</p> <p>0000: <math>AIN_P = AIN_0, AIN_N = AIN_1</math> (默认设置)<br/> 0001: <math>AIN_P = AIN_0, AIN_N = AIN_2</math><br/> 0010: <math>AIN_P = AIN_0, AIN_N = AIN_3</math><br/> 0011: <math>AIN_P = AIN_1, AIN_N = AIN_2</math><br/> 0100: <math>AIN_P = AIN_1, AIN_N = AIN_3</math><br/> 0101: <math>AIN_P = AIN_2, AIN_N = AIN_3</math><br/> 0110: <math>AIN_P = AIN_1, AIN_N = AIN_0</math><br/> 0111: <math>AIN_P = AIN_3, AIN_N = AIN_2</math><br/> 1000: <math>AIN_P = AIN_0, AIN_N = AVSS</math><br/> 1001: <math>AIN_P = AIN_1, AIN_N = AVSS</math><br/> 1010: <math>AIN_P = AIN_2, AIN_N = AVSS</math><br/> 1011: <math>AIN_P = AIN_3, AIN_N = AVSS</math><br/> 1100: <math>(V_{REFPx} - V_{REFNx}) / 6</math> 监视 (旁路 PGA)<br/> 1101: <math>(AVDD - AVSS) / 6</math> 监视 (旁路 PGA)<br/> 1110: <math>AIN_P</math> 和 <math>AIN_N</math> 短接至 <math>(AVDD + AVSS) / 2</math><br/> 1111: 保留 </p> |

| 3:1 | GAIN[2:0] | RW   | 0h | <p>增益配置。</p> <p>在不使用 PGA 的情况下，可使用增益 1、2 和 4。此时，通过开关电容结构获得增益。</p> <p>000: 增益 = 1 (默认设置)<br/> 001: 增益 = 2<br/> 010: 增益 = 4<br/> 011: 增益 = 8<br/> 100: 增益 = 16<br/> 101: 增益 = 32<br/> 110: 增益 = 64<br/> 111: 增益 = 128 </p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 位 | 名称         | 访问类型 | 复位 | 描述                                                                                                                                                                                                |

|---|------------|------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | PGA_BYPASS | RW   | 0h | <p>禁用内部低噪声 PGA。</p> <p>禁用 PGA 会降低整体功耗，并可将共模电压范围(<math>V_{CM}</math>) 扩展为 AVSS - 0.1V 至 AVDD + 0.1V。</p> <p>PGA 禁用功能只在增益设置为 1、2 和 4 时有效，在其他增益下，该位配置无效。</p> <p>0: PGA 启用（默认设置）<br/>1: PGA 禁用并旁路</p> |

## CONFIG1 (地址=01h)

| 位   | 名称        | 访问类型 | 复位 | 描述                                                                                                                                                   |

|-----|-----------|------|----|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | DR[2:0]   | RW   | 0h | <p>数据速率配置。</p> <p>数据速率取决于所选工作模式。<a href="#">表 15</a> 列出了普通模式、占空比模式和 Turbo 模式对应的位设置。</p>                                                              |

| 4:3 | MODE[1:0] | RW   | 0h | <p>工作模式配置。</p> <p>00: 普通模式 (256kHz 调制器时钟, 默认设置)<br/>01: 占空比模式 (内部占空比 1:4)<br/>10: Turbo 模式 (256kHz 调制器时钟)<br/>11: 保留</p>                             |

| 2   | CM        | RW   | 0h | <p>转换模式配置。</p> <p>0: 单次模式（默认设置）<br/>1: 连续转换模式</p>                                                                                                    |

| 1   | TS        | RW   | 0h | <p>温度传感器模式配置。</p> <p>该位用于启用内部温度传感器以及将芯片置于温度传感器模式下。</p> <p>启用温度传感器模式后, CONFIG0 的设置不会产生任何影响, 芯片会使用内部基准进行测量。</p> <p>0: 禁用温度传感器（默认设置）<br/>1: 启用温度传感器</p> |

| 0   | BCS       | RW   | 0h | <p>该位用于控制 10<math>\mu</math>A 传感器偏置电流。</p> <p>传感器偏置电流可用于检测传感器故障（例如，传感器断路和短路）。</p> <p>0: 电流源关断（默认设置）<br/>1: 电流源接通</p>                                 |

表 15 DR 位设置

| 数据率配置 | 普通模式    | 占空比模式    | Turbo 模式 |

|-------|---------|----------|----------|

| 000   | 20SPS   | 5SPS     | 40SPS    |

| 001   | 50SPS   | 12.5SPS  | 100SPS   |

| 010   | 100SPS  | 25SPS    | 200SPS   |

| 011   | 200SPS  | 50SPS    | 400SPS   |

| 100   | 333SPS  | 83.25SPS | 666SPS   |

| 101   | 666SPS  | 166.5SPS | 1333SPS  |

| 110   | 1000SPS | 250SPS   | 2000SPS  |

| 数据率配置 | 普通模式 | 占空比模式 | Turbo 模式 |

|-------|------|-------|----------|

| 111   | 保留   | 保留    | 保留       |

## CONFIG2 (地址=02h)

| 位   | 名称         | 访问类型 | 复位 | 描述                                                                                                                                                                                                                            |

|-----|------------|------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | VREF[1:0]  | RW   | 0h | <p>电压基准选择。<br/>这些位用于选择转换所使用的电压基准源。<br/>00: 选择 2.048V 内部电压基准 (默认设置)<br/>01: 使用专用 REFPO 和 REFNO 输入的外部电压基准<br/>10: 使用 AINO/REFP1 和 AIN3/REFN1 输入的外部电压基准<br/>11: 保留</p>                                                           |

| 5:4 | 50/60[1:0] | RW   | 0h | <p>FIR 滤波器配置。<br/>这些位用于为内部 FIR 滤波器配置滤波器系数。<br/>在普通模式下, 这些位仅与 20SPS 设置结合使用; 在占空比模式下, 这些位仅与 5SPS 设置结合使用。对于所有其他数据速率, 这些位均需设置为 00。<br/>00: 无 50Hz 或 60Hz 抑制 (默认设置)<br/>01: 同时抑制 50Hz 和 60Hz<br/>10: 只抑制 50Hz<br/>11: 只抑制 60Hz</p> |

| 3   | PSW        | RW   | 0h | <p>低侧电源开关配置。<br/>该位用于配置 AIN3/REFN1 和 AVSS 之间连接的低侧开关的行为。<br/>0: 开关始终处于断开状态 (默认设置)<br/>1: 开关会在发送 START/SYNC 命令时自动闭合, 并在发出 POWERDOWN 命令时自动断开。</p>                                                                                |

| 2:0 | IDAC[2:0]  | RW   | 0h | <p>IDAC 电流设置。<br/>这些位用于为 IDAC1 和 IDAC2 激励电流源设置电流。<br/>000: 关断 (默认设置)<br/>001: 10µA<br/>010: 50µA<br/>011: 100µA<br/>100: 250µA<br/>101: 500µA<br/>110: 1000µA<br/>111: 1500µA</p>                                             |

## CONFIG3 (地址=03h)

| 位   | 名称         | 访问类型 | 复位 | 描述                                                                                                                                                                                                                                 |

|-----|------------|------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | I1MUX[2:0] | RW   | 0h | IDAC1 输出通道配置。<br>这些位用于选择 IDAC1 输出的对应通道。<br>000: IDAC1 禁用 (默认设置)<br>001: IDAC1 连接至 AIN0/REFP1<br>010: IDAC1 连接至 AIN1<br>011: IDAC1 连接至 AIN2<br>100: IDAC1 连接至 AIN3/REFN1<br>101: IDAC1 连接至 REFP0<br>110: IDAC1 连接至 REFNO<br>111: 保留 |

| 4:2 | I2MUX[2:0] | RW   | 0h | IDAC2 输出通道配置。<br>这些位用于选择 IDAC2 输出的对应通道。<br>000: IDAC2 禁用 (默认设置)<br>001: IDAC2 连接至 AIN0/REFP1<br>010: IDAC2 连接至 AIN1<br>011: IDAC2 连接至 AIN2<br>100: IDAC2 连接至 AIN3/REFN1<br>101: IDAC2 连接至 REFP0<br>110: IDAC2 连接至 REFNO<br>111: 保留 |

| 1   | DRDYM      | RW   | 0h | DRDY模式。<br>该位用于控制新数据就绪时 DOUT/DRDY管脚的行为。<br>0: 仅用DRDY管脚指示数据何时就绪 (默认设置)。<br>1: 同时通过 DOUT/DRDY和DRDY指示数据就绪。                                                                                                                            |

| 0   | RSV        | RW   | 0h | 保留。<br>始终写为 0。                                                                                                                                                                                                                     |

## 封装及订购信息

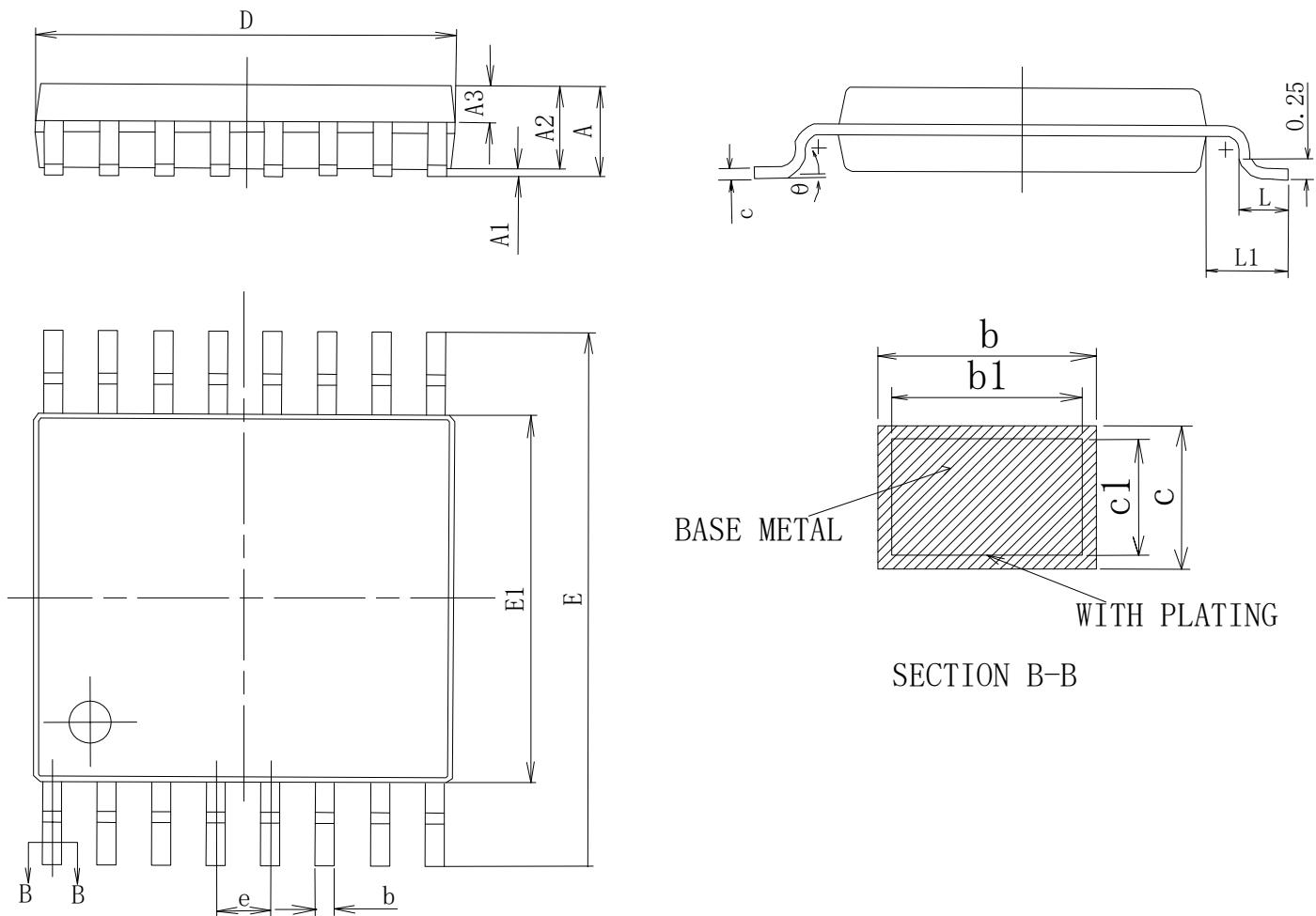

### 封装形式

CM1110 采用 TSSOP16 封装。

### 产品外形图

产品外形图如下图所示。

| 标识 | 尺寸 (毫米)    |      |      |

|----|------------|------|------|

|    | 最小值        | 典型值  | 最大值  |

| A  | -          | -    | 1.20 |

| A1 | 0.05       | 0.10 | 0.15 |

| A2 | 0.90       | 1.00 | 1.05 |

| A3 | 0.39       | 0.44 | 0.49 |

| b  | 0.20       | 0.24 | 0.28 |

| b1 | 0.19       | 0.22 | 0.25 |

| c  | 0.13       | 0.15 | 0.17 |

| c1 | 0.12       | 0.13 | 0.14 |

| D  | 4.90       | 5.00 | 5.10 |

| E  | 6.20       | 6.40 | 6.60 |

| E1 | 4.30       | 4.40 | 4.50 |

| e  | 0.65 (BSC) |      |      |

| L  | 0.45       | 0.60 | 0.75 |

| L1 | 1.00 (BSC) |      |      |

| θ  | 0°         | 4°   | 8°   |

## 订购信息

| 型号           | 温度范围        | 封装      | 包装   | 包装数量 |

|--------------|-------------|---------|------|------|

| CM1110-SOPTA | -40°C~125°C | TSSOP16 | Reel | 1000 |