# MYD-YM90X FPGA 开发指南

|                                          |         |                          |

|------------------------------------------|---------|--------------------------|

| 文件状态:                                    | 文件编号:   | MYIR MYD-YM90X FPGA 开发指南 |

| <input type="checkbox"/> 草稿              | 文件版本:   | V1.0[文档]                 |

| <input checked="" type="checkbox"/> 正式发布 | 作    者: | MSW0102                  |

|                                          | 发布日期:   | 2024-09-02               |

|                                          | 最近更新:   | 2024-12-27               |

# 版本历史

| 版本       | 作者      | 审核者     | 日期         | 备注     |

|----------|---------|---------|------------|--------|

| V1.0[文档] | MSW0102 | MSW0027 | 2024-09-02 | 正式版本发布 |

## 目录

|                             |        |

|-----------------------------|--------|

| 版本历史                        | - 0 -  |

| 第一章 概述                      | - 4 -  |

| 1.1. 文档介绍                   | - 4 -  |

| 1.2. 关于本文档后面章节安排            | - 4 -  |

| 1.3. DR1 系列芯片介绍             | - 5 -  |

| 1.3.1. DR1 系列基础特性           | - 5 -  |

| 1.3.2. DR1 系列封装             | - 5 -  |

| 第二章 MYD-YM90X 使用准备          | - 6 -  |

| 2.1. 硬件准备                   | - 6 -  |

| 2.2. 软件准备                   | - 7 -  |

| 2.2.1. TD 软件下载              | - 8 -  |

| 2.2.2. TD 软件的安装             | - 9 -  |

| 2.2.3. FD 软件的安装             | - 13 - |

| 2.2.4. TD 软件官方 IP 和参考设计     | - 16 - |

| 第三章 硬件平台详细配置                | - 17 - |

| 3.1. TD 工程介绍                | - 17 - |

| 3.1.1. 新建 TD 工程             | - 17 - |

| 3.1.2. 编写 Verilog 代码        | - 18 - |

| 3.1.3. 编译工程                 | - 21 - |

| 3.1.4. 设置管脚约束               | - 22 - |

| 3.1.5. 下载 bit 文件            | - 25 - |

| 第四章 串口输出打印测试                | - 30 - |

| 4.1. UART 工程介绍              | - 30 - |

| 4.1.1. 新建 Hello_world 工程    | - 30 - |

| 4.1.2. 打开 Design Integrator | - 31 - |

| 4.1.3. 新建 Design            | - 31 - |

| 4.1.4. 调用 PS 端 IP           | - 32 - |

|                                   |               |

|-----------------------------------|---------------|

| 4.1.5. 导出 Design .....            | - 36 -        |

| 4.1.6. 新建 FPGA 顶层文件 .....         | - 38 -        |

| 4.1.7. 编译 FPGA 工程 .....           | - 40 -        |

| 4.1.8. 导出 HPF 工程 .....            | - 41 -        |

| 4.1.9. 新建 BSP 工程 .....            | - 42 -        |

| 4.1.10. 生成 BOOT.bin 文件 .....      | - 47 -        |

| 4.1.11. Debug 调试 .....            | - 51 -        |

| <b>第五章 GPIO-EMIO 输出测试 .....</b>   | <b>- 52 -</b> |

| 5.1. GPIO-EMIO 工程介绍 .....         | - 52 -        |

| 5.1.1. 新建 Emio_test 工程 .....      | - 52 -        |

| 5.1.2. 打开 Design Integrator ..... | - 53 -        |

| 5.1.3. 新建 Design .....            | - 53 -        |

| 5.1.4. 调用 PS 端 IP .....           | - 54 -        |

| 5.1.5. 导出 Design .....            | - 59 -        |

| 5.1.6. 新建 FPGA 顶层文件 .....         | - 61 -        |

| 5.1.7. 编译 FPGA 工程 .....           | - 63 -        |

| 5.1.8. 导出 HPF 工程 .....            | - 64 -        |

| 5.1.9. 新建 BSP 工程 .....            | - 65 -        |

| 5.1.10. 生成 BOOT.bin 文件 .....      | - 70 -        |

| 5.1.11. Debug 调试 .....            | - 74 -        |

| <b>第六章 AXI4-Lite 总线使用 .....</b>   | <b>- 75 -</b> |

| 6.1. AXI4-Lite 工程介绍 .....         | - 75 -        |

| 6.1.1. 新建 Axi_gpio 工程 .....       | - 75 -        |

| 6.1.2. 打开 Design Integrator ..... | - 76 -        |

| 6.1.3. 新建 Design .....            | - 76 -        |

| 6.1.4. 调用 PS 端 IP .....           | - 77 -        |

| 6.1.5. 配置 PS 端 IP .....           | - 81 -        |

| 6.1.6. PS 端模块连接 .....             | - 85 -        |

| 6.1.7. PS 端管脚输出配置 .....           | - 89 -        |

| 6.1.8. PS 端工程设计验证 .....           | - 91 -        |

| 6.1.9. PS 端导出 Design .....        | - 91 -        |

|                              |                |

|------------------------------|----------------|

| 6.1.10. 顶层例化 Design .....    | - 93 -         |

| 6.1.11. 设置顶层管脚约束 .....       | - 94 -         |

| 6.1.12. 生成 bit 文件 .....      | - 95 -         |

| 6.1.13. 导出 hpf 文件 .....      | - 96 -         |

| 6.1.14. 新建 BSP 工程 .....      | - 96 -         |

| 6.1.15. 编译 FD 工程 .....       | - 100 -        |

| 6.1.16. FD 工程下载 .....        | - 101 -        |

| <b>第七章 HDMI 输出显示测试 .....</b> | <b>- 104 -</b> |

| 7.1. HDMI 显示工程介绍 .....       | - 104 -        |

| 7.1.1. 新建 HDMI 显示工程 .....    | - 104 -        |

| 7.1.2. 配置 PS 端设备 .....       | - 105 -        |

| 7.1.3. 工程设计检查 .....          | - 109 -        |

| 7.1.4. 导出 PS 端工程 .....       | - 110 -        |

| 7.1.5. 添加 VDMA 模块 .....      | - 111 -        |

| 7.1.6. 编译工程 .....            | - 114 -        |

| 7.1.7. 导出 HPF 文件 .....       | - 114 -        |

| 7.1.8. 打开 FD 软件 .....        | - 115 -        |

| 7.1.9. 生成 BSP 文件 .....       | - 115 -        |

| <b>附录一 联系我们 .....</b>        | <b>- 123 -</b> |

| <b>附录二 售后服务与技术支持 .....</b>   | <b>- 125 -</b> |

# 第一章 概述

## 1.1. 文档介绍

本文档主要是介绍怎么在 MYD-YM90X 硬件平台上实现自己的工程开发。通过学习本文档，希望客户可以达到几个目标：

1. 了解 MYD-YM90X 这个硬件平台。

2. 能够在这个硬件平台上实现自己的目标设计。

3. 了解有关 MYD-YM90X 这个硬件平台的参考资料，客户可以快速的找到，特别是对于安路官方的一些参考文档和参考设计。

在使用 MYD-YM90X 硬件平台的时候，可能用到的资料信息搜集，遇到关键点可以寻求参考资料方向，可以向米尔寻求合作开发。

关于 MYD-YM90X 硬件平台，MYD-YM90X 硬件平台使用的是安路科技 SALDRAGON1 系列器件简称为 DR1,DR1 系列器件延续安路科技 FPPSoC 家族，组合了硬核处理器系统和 FPGA，通过高带宽总线进行二者互联。多核 ARM/RISC-V 处理器系统与安路 FPGA 可编程相结合于一颗芯片中，提供了应用类 ARM/RISC-V 处理器的性能与生态系统，并且具备安路 FPGA 的灵活性，低功耗，可扩展 SoC 平台。ARM/RISC-V CPU 是嵌入式系统的核心，同时系统还包含 On-Chip RAM，内存接口和丰富的外设互联接口，定位复杂嵌入式系统，低功耗和高性能芯片市场。

## 1.2. 关于本文档后面章节安排

第一章概论，简要介绍了本文档撰写目的以及文档的章节结构。

第二章介绍了硬件平台的一些基本参数，如何到官网下载资料和编译软件，并且详细的介绍 TD 和 FD 软件的安装。

第三章介绍 TD 软件的纯 FPGA 工程的新建，管脚约束，工程编译和下载

第四章介绍在 TD 软件里配置 PS 端 ARM 核，并且通过串口打印输出，这个章节主要介绍 FD 软件的使用，以及 PS 端 ARM 的配置方法。

第五章相当于前两个章节的结合，不仅有 PL 端也有 PS 端的配置，相当于一个基础的 PL+PS 结合的工程，主要为后面的 HDMI 复杂类的工程打基础。

第六章介绍 HDMI 输出显示测试，HDMI 显示是 PS+PL 的形式，也包含 HDMI 芯片的 IIC 配置，以及包含其它测试接口和 axi 总线设备。

## 1.3. DR1 系列芯片介绍

### 1.3.1. DR1 系列基础特性

| Device       | LUTs   | DFFs    | ERAM |               | DRAM<br>(Kbits) | DSP | PLL | TS | ADC | MIPI<br>DPHY-RX | MAX user I/O<br>(HR'/MIPI) |

|--------------|--------|---------|------|---------------|-----------------|-----|-----|----|-----|-----------------|----------------------------|

|              |        |         | 20K  | Total (Kbits) |                 |     |     |    |     |                 |                            |

| DR1M90GEG484 | 52,480 | 104,960 | 280  | 5600          | 1340            | 240 | 8   | 1  | 1   | -               | 201 (96) /0                |

| DR1V90GEG484 | 52,480 | 104,960 | 280  | 5600          | 1340            | 240 | 8   | 1  | 1   | -               | 201 (96) /0                |

| DR1M90MEG484 | 52,480 | 104,960 | 280  | 5600          | 1340            | 240 | 8   | 1  | 1   | 2               | 175 (84) /20               |

| DR1V90MEG484 | 52,480 | 104,960 | 280  | 5600          | 1340            | 240 | 8   | 1  | 1   | 2               | 175 (84) /20               |

图 1-1. DR1 系列器件基础特性

DR1 系列芯片，可以看出 MEG484 封装带有两个 miipi 模块，其中 M90 中 M 表示 ARM Cortex-A 处理器，V90 中 V 表示 RISC-V 处理器，90 表示 90K 查找表

### 1.3.2. DR1 系列封装

| Device | Package |           |            | MAX USER I/O    |                 |

|--------|---------|-----------|------------|-----------------|-----------------|

|        | Type    | Size (mm) | Pitch (mm) | PS <sup>1</sup> | PL <sup>2</sup> |

| DR1M90 | GEG484  | 19x19     | 0.8        | 54              | 201             |

|        | MEG484  | 19x19     | 0.8        | 54              | 195             |

| DR1V90 | GEG484  | 19x19     | 0.8        | 54              | 201             |

|        | MEG484  | 19x19     | 0.8        | 54              | 195             |

图 1-2. DR1 系列封装

上图中列举的是 DR1 常用的封装，MYD-YM90X 硬件平台使用的是 GEG484 这个封装，从上图可以看出 484 封装 PCB 尺寸大小是一样的，但端口数 GEG484 和 MEG484 有所不同，GEG484 封装 PL 端口数为 201，MEG484 封装 PL 端口数为 195。

## 第二章 MYD-YM90X 使用准备

## 2.1. 硬件准备

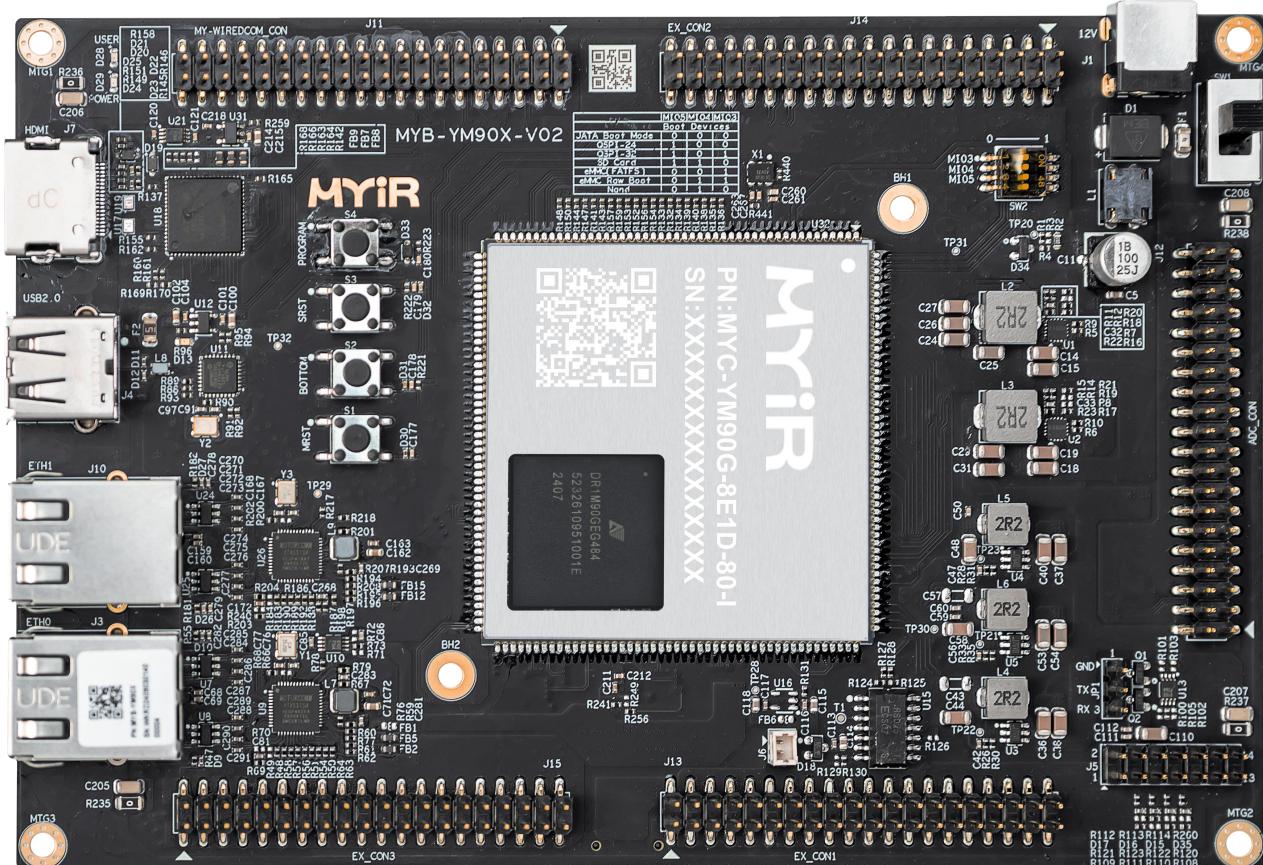

介绍 MYD-YM90X 硬件平台的基本特性，产品预览图 2-1

图 2-1. 硬件平台产品图示

MYD-YM90X 硬件平台采用 SALDRAGON1 系列器件简称为 DR1，DR1 器件，2 万 3 千逻辑门、1GB DDR3 SDRAM、一路 HDMI 输出显示接口、两路以太网接口，一路 USB 接口，以及通过外设扩展的 RS232，RS485，CAN 接口。

表 2-1. FPGA 逻辑资源

| 资源            | DR1           |

|---------------|---------------|

| 逻辑核心          | SALDRAGON1 系列 |

| 可编程逻辑单元(LUT6) | 524800        |

| 触发器           | 104,960       |

| DRAM          | 1340          |

| DSP Slice     | 240           |

| ADC           | 1             |

| FPGA 管脚数量     | 201           |

## 2.2. 软件准备

本节主要介绍安路 TD 工具的安装，本产品使用的是安路 TD\_5.9.1\_DR1\_ES1.1 版本，这里我们以 TD\_5.9.1\_DR1\_ES1.1 版本的安装方法为模板来操作，其它 TD 版本安装方法同样可以参考此版本安装方法进行安装。

因安路之前的 TD 开发工具只包含 FPGA 工程开发，新版本 TD\_5.9.1\_DR1\_ES1.1 既包含普通 FPGA 芯片开发也包含 DR1 系列芯片开发，如果使用的是 DR1 器件，最好下载 TD\_5.9.1\_DR1\_ES1.1 版本或者更高的版本，如果下载之前的的老版本 TD 软件，可能无法兼容 DR1 这个型号的器件，推荐客户使用和我们版本相同的 TD\_5.9.1\_DR1\_ES1.1 版本来使用，使用相同的软件版本，如果工程出现问题，便于我司快速定位出现问题的地方。

FD 工具为 ARM 端的裸机开发工具，主要使用裸机来测试 PS 端的外设接口，比如 UART, IIC, SPI, CAN 接口等，对于 DR1 芯片来说，主要用于 PL 和 PS 交互使用，所以不仅要掌握 TD 工具的使用，同时也要掌握 FD 工具的基础使用方法，这样才能在调试出现问题时，能快速定位是 PL 部分还是 PS 部分出现问题，从而快速解决。

## 2.2.1. TD 软件下载

下载安路 TD 工具需要在安路官方网站上 <https://www.anlogic.com> 注册账号，注册完成后，点击服务支持选择工具与资料下载，如图所示。

图 2-2. 安路官网界面

## 选择软件工具

安路科技软件工具、数据手册、使用指南

首页 > 服务支持 > 工具与资料下载

输入您想了解的文档

按日期排序

热门关键词： DS400 DS300

技术文档

标题

日期

版本

开发板设计

TD\_4.6.8\_CPLD\_Release\_96021\_NL.msi

2024-01-10

v4.6.8

压缩码：[SHA-256] 13075241b16c150377065b28b336c1fe6ca7bb30b51a731591f69a992cafde9d

软件工具

TD\_4.6.8\_CPLD\_Release\_96021\_32bit\_NL.ms

2024-01-10

v4.6.8

图 2-3. 安路官网软件工具界面

选择 TD Windows-->TD\_5.9,可以看到右侧的 TD5.9.1\_DR1 软件，点击后面的下载按钮

图 2-4. TD 下载工具

## 2.2.2. TD 软件的安装

安装之前，请关闭杀毒软件，特别是防护杀毒软件

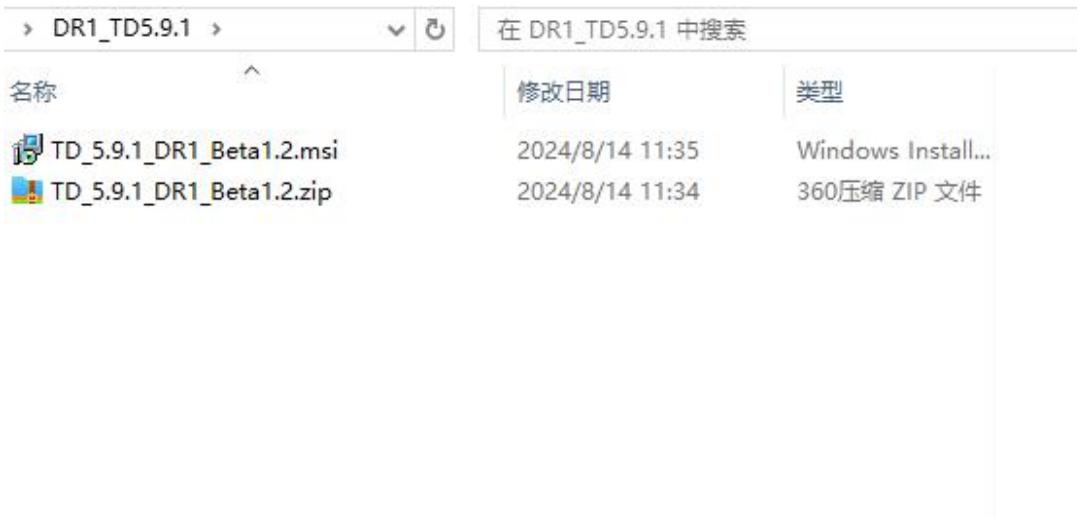

- 打开下载的 TD 安装文件夹，双击 TD\_5.9.1\_DR1\_Beta1.2.msi 安装程序，如图

图 2-5. FD 软件安装文件

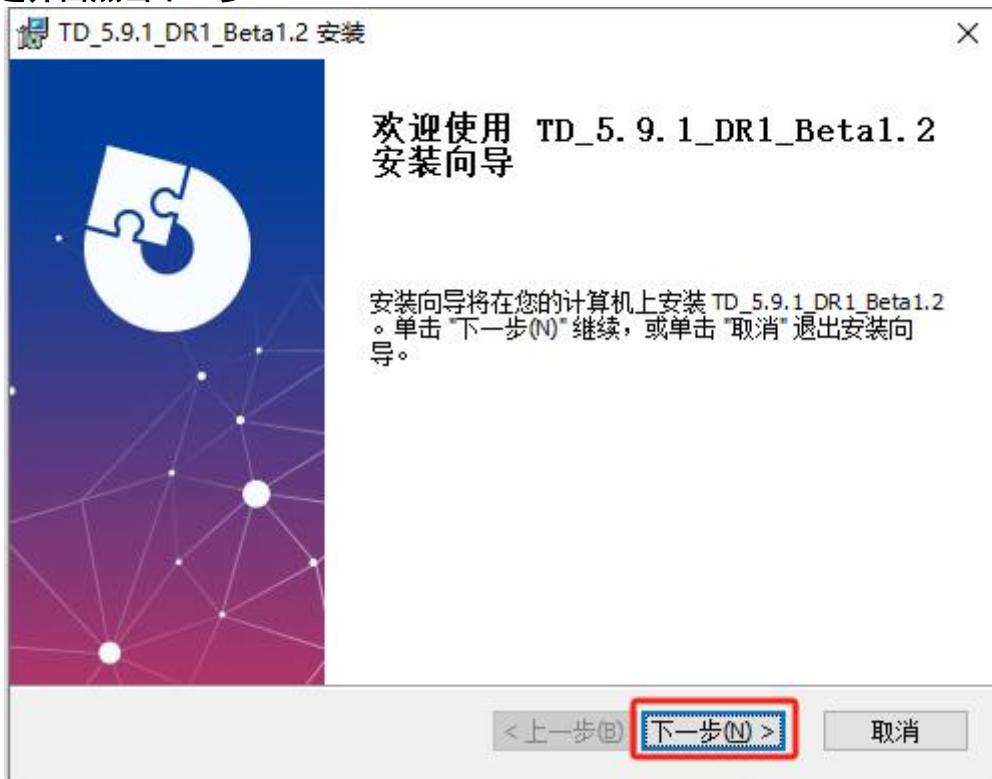

- 在欢迎界面点击下一步

图 2-6. 安装向导界面

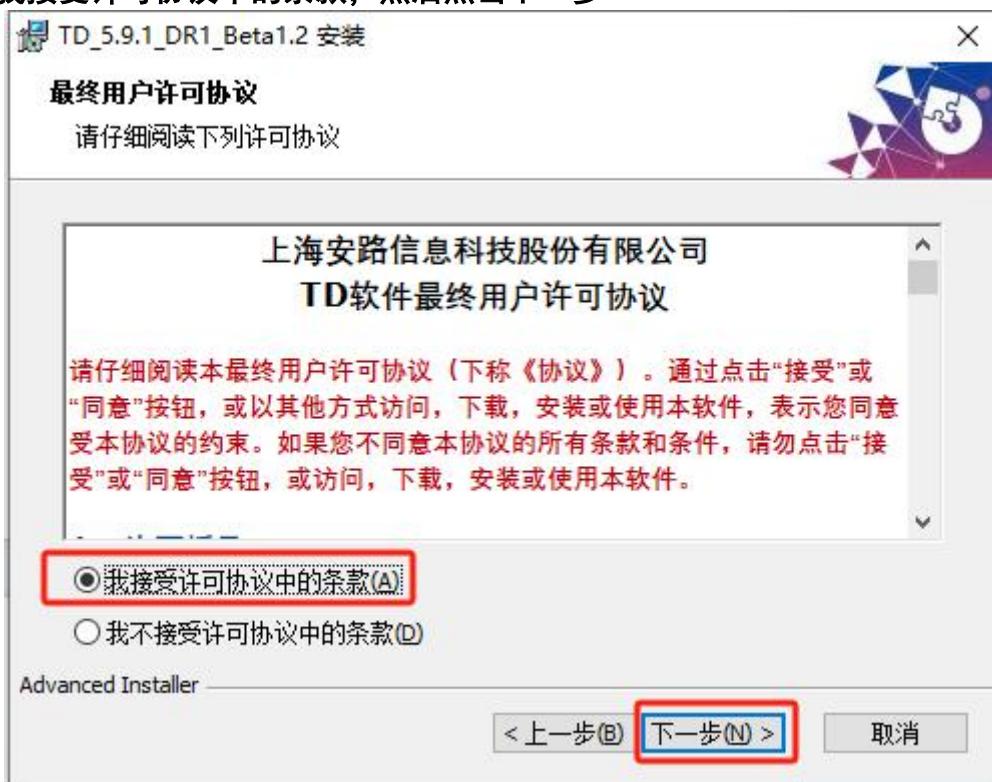

- 选择我接受许可协议中的条款，然后点击下一步

图 2-7. 安装协议

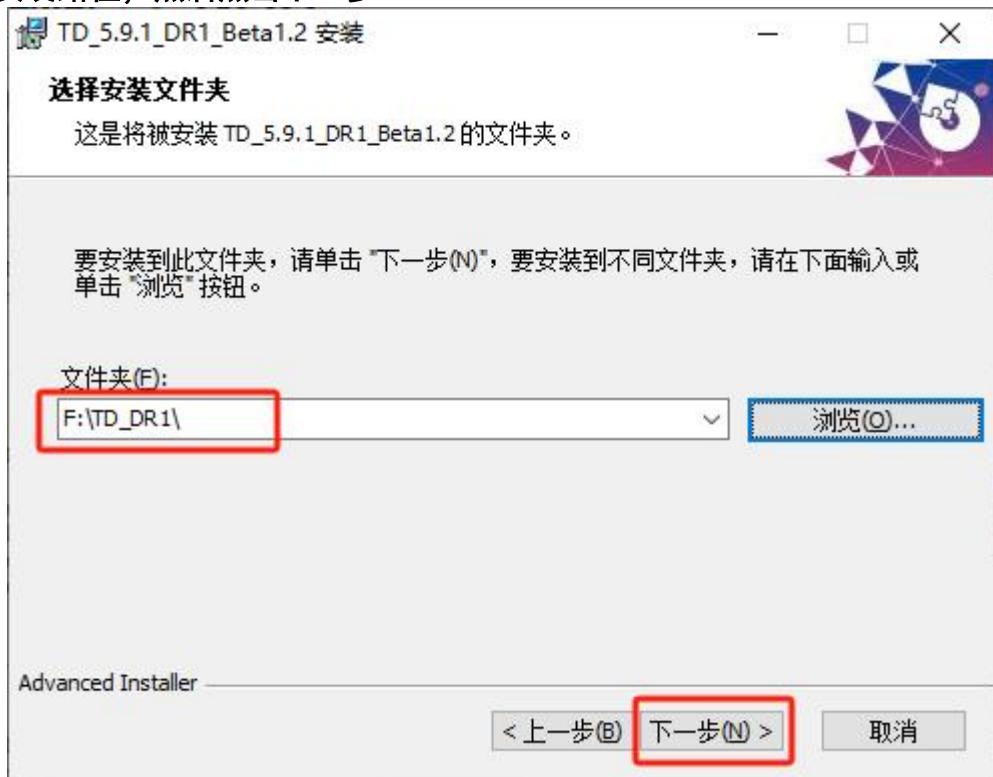

- 选择安装路径，然后点击下一步

图 2-8. 添加安装路径

- 点击安装，开始安装 TD 软件，如图所示

图 2-9. 准备安装

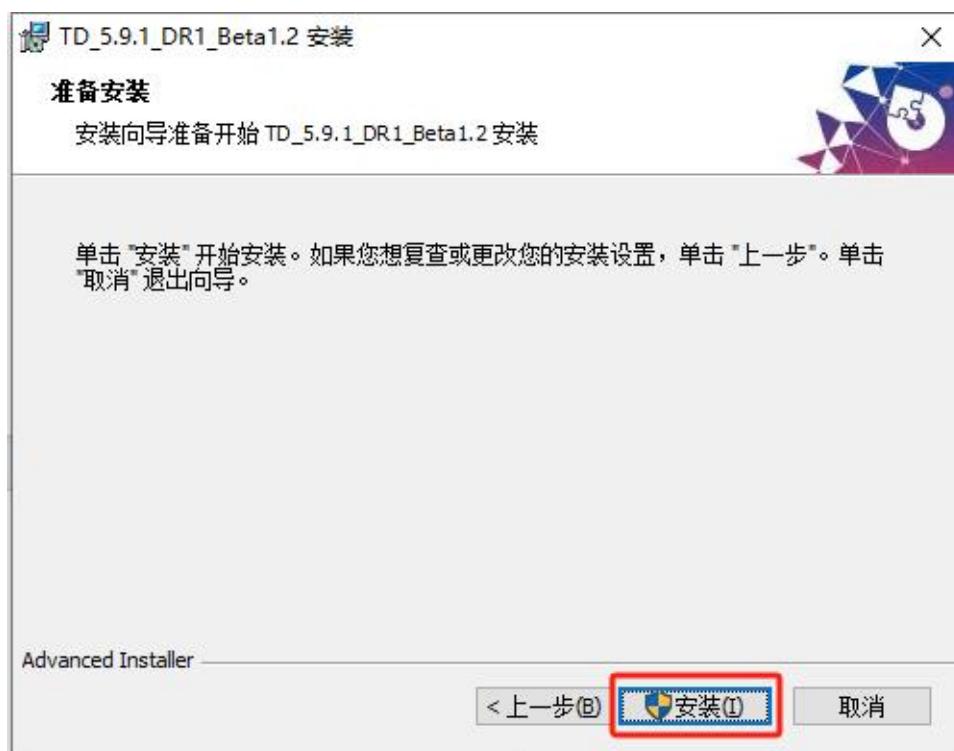

- 自动安装完成后，点击完成，退出安装向导

图 2-10. 安装完成

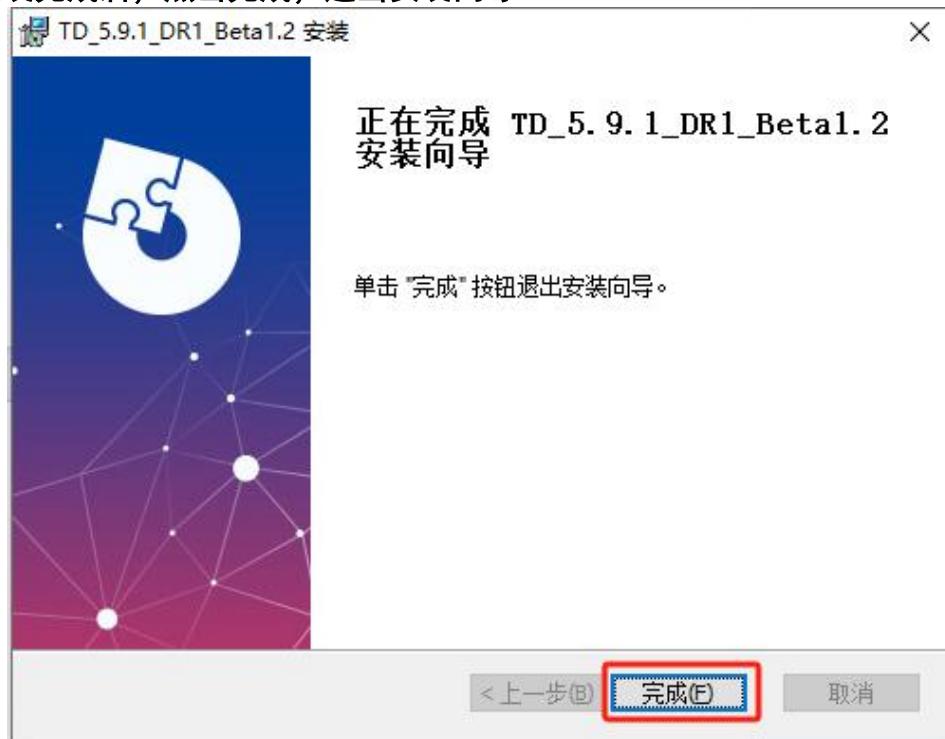

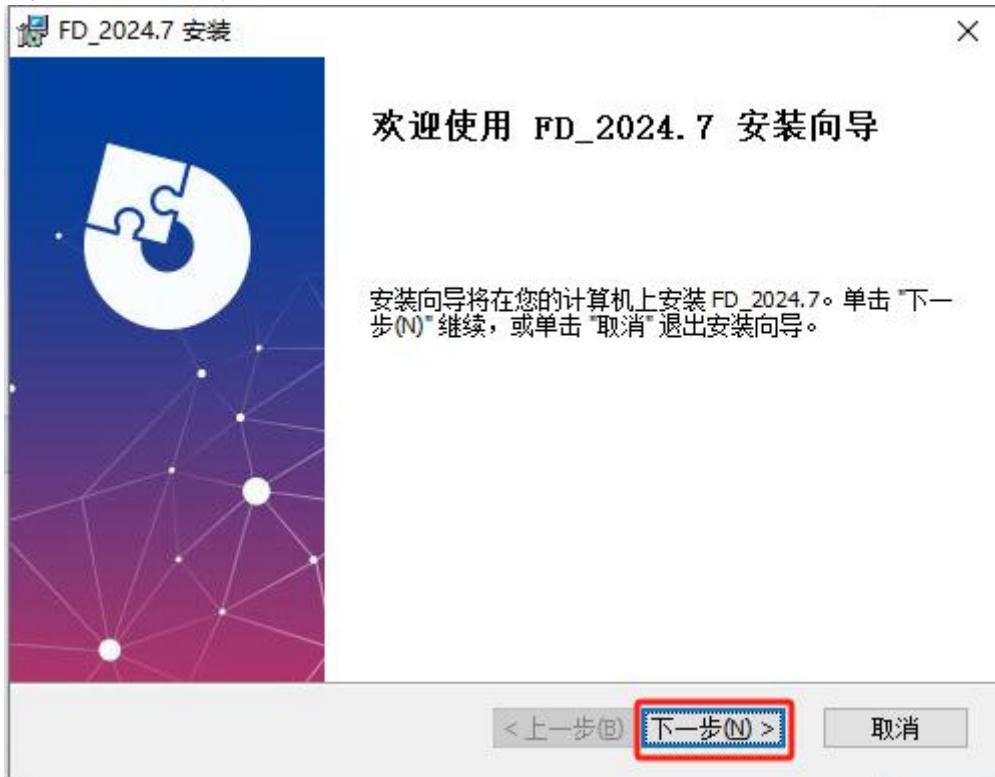

### 2.2.3. FD 软件的安装

安装之前，请关闭杀毒软件，特别是防护杀毒软件

- 打开下载的 FD 安装文件夹，双击 FD\_2024.7.msi 安装程序，如图

图 2-11. FD 软件安装文件

- 在欢迎界面点击下一步

图 2-12. 安装向导界面

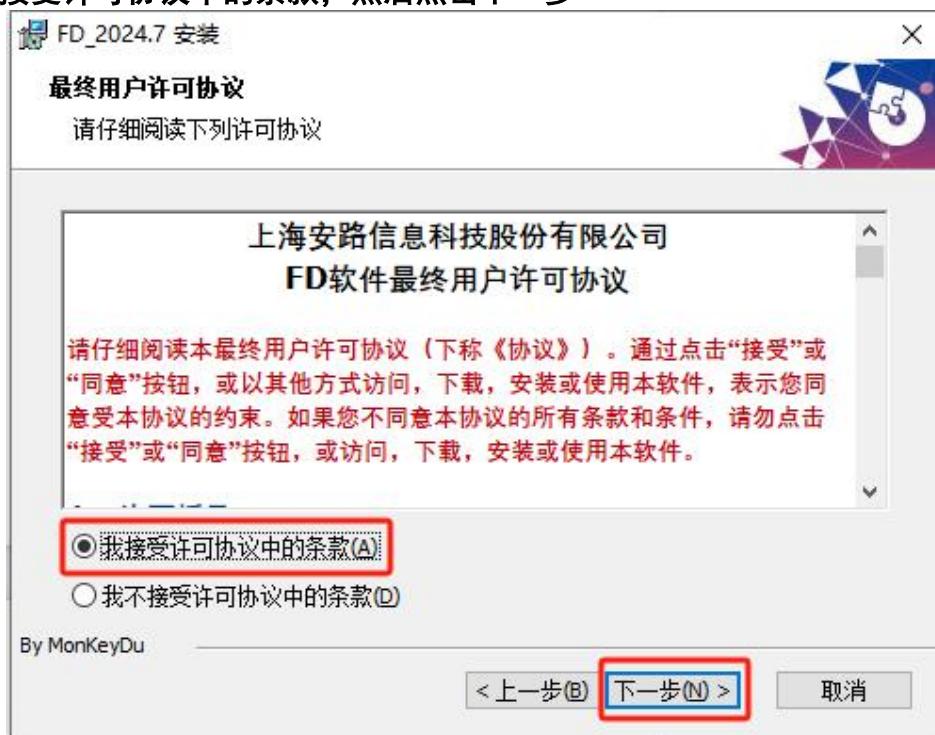

- 选择我接受许可协议中的条款，然后点击下一步

图 2-13. 安装协议

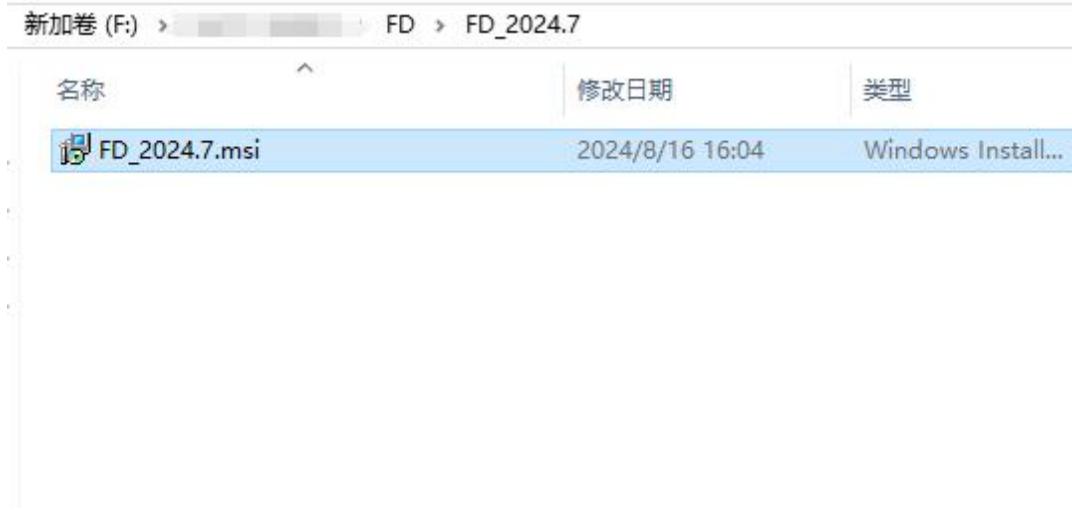

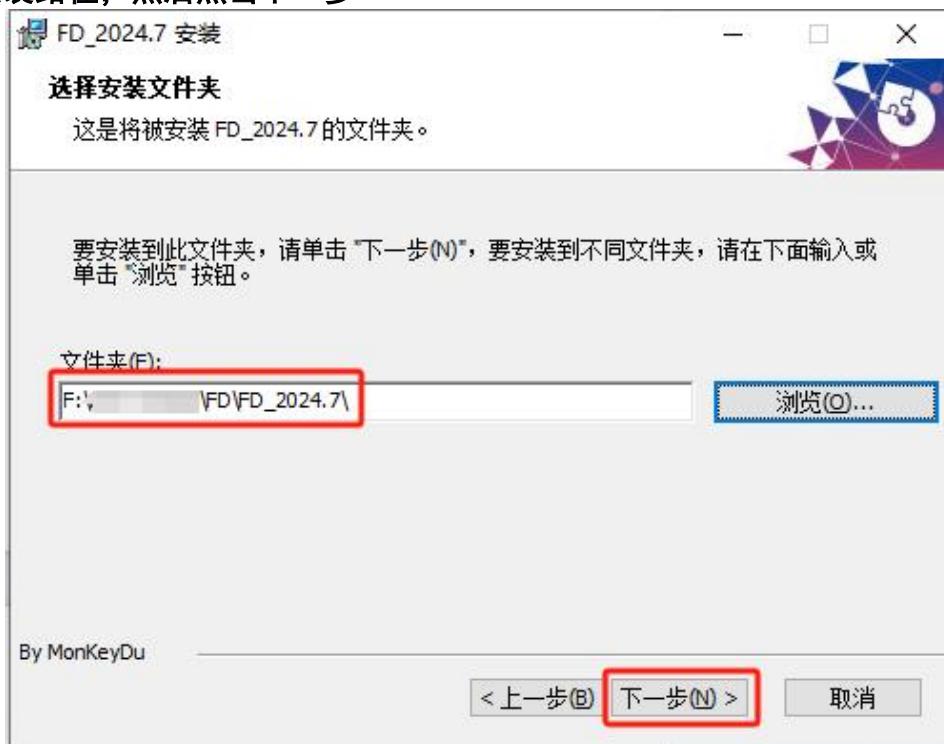

- 选择安装路径，然后点击下一步

图 2-14. 添加安装路径

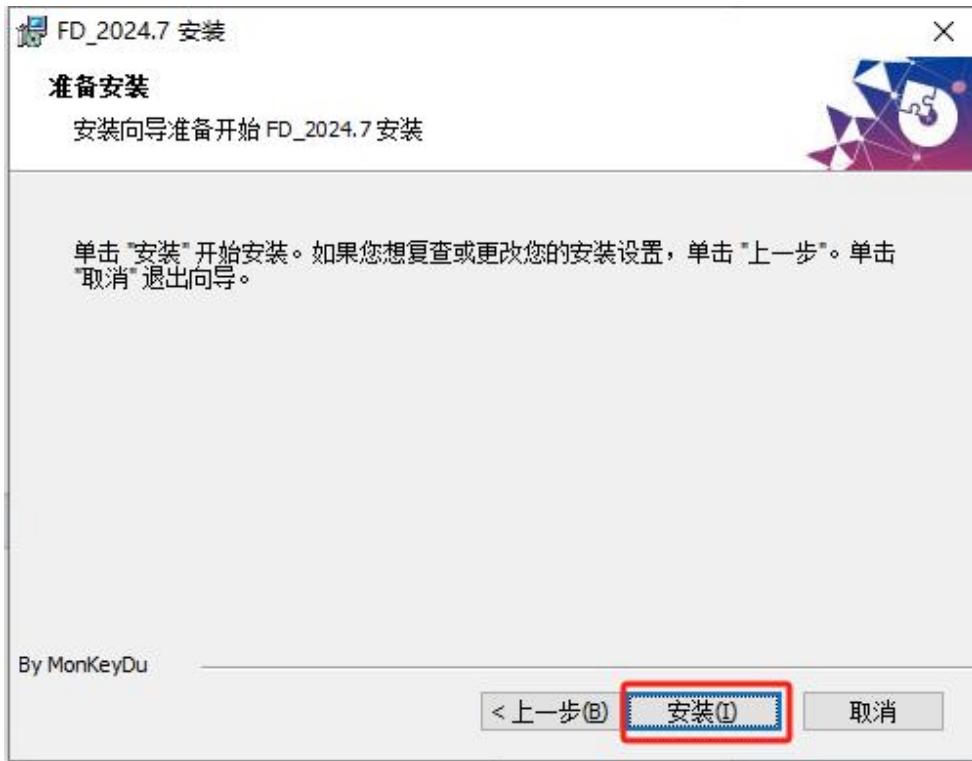

- 点击安装，开始安装 FD 软件，如图所示

图 2-15. 准备安装

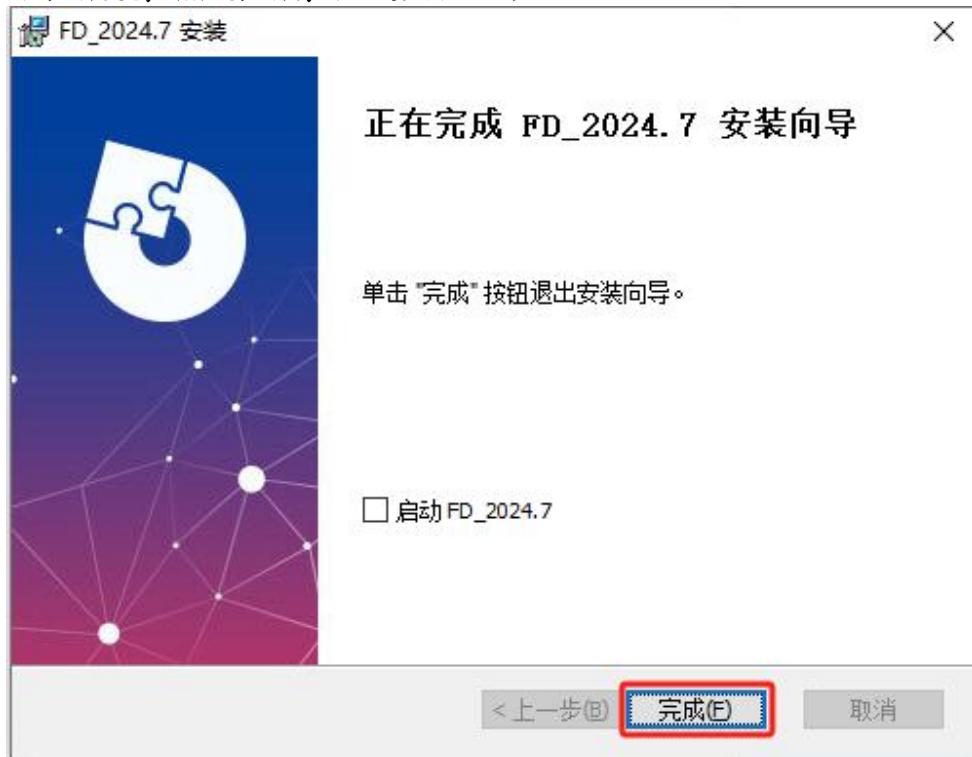

- 自动安装完成后，点击完成，退出安装向导

图 2-16. 安装完成

## 2.2.4. TD 软件官方 IP 和参考设计

在安路官方网站 <https://www.anlogic.com> 上，点击服务支持选择 IP 和参考设计

图 2-17. IP 和参考设计

选择需要的 IP，然后点击后面的下载按键

The screenshot shows the 'IP and Reference Design' page. At the top, there is a search bar and a filter section for date and version. Below that, a table lists several IP and reference designs. The first item in the table is highlighted with a red box around its download button. The table columns include IP Type, Title, Date, Version, Support Series, and Operation.

| IP   | 标题                                 | 日期         | 版本   | 支持系列               | 操作 |

|------|------------------------------------|------------|------|--------------------|----|

| 参考设计 | IPUG012_Soft_FIFO 用户手册.pdf         | 2024-08-02 | v2.0 | EF2\EF3\EG4\SF1    |    |

|      | IPUG179_AXI_DMA_IP 用户手册.pdf        | 2024-08-02 | v1.0 | EG4/EF 系列/PH1A/SF1 |    |

|      | IPUG166_Video_NPU_IP 用户手册          | 2024-06-07 | v1.0 | DR1                |    |

|      | IPUG173.Utility_Reduced_Logic 用户手册 | 2024-06-07 | v1.0 | EG4/EF 系列/PH1A/SF1 |    |

图 2-18. 参考设计手册

# 第三章 硬件平台详细配置

MYD-YM90X 的平台主要是 FPGA 和 ARM 两部分，TD 平台主要是搭建 PL 和 PS 工程，本章节主要讲解如何使用 TD 平台来搭建工程，以及如何配置 PS 端的一些外设接口。

## 3.1. TD 工程介绍

本章节注意讲解如何使用 TD 新建 FPGA 工程，DR1 是一个 FPGA+ARM 类型的架构芯片，本章节着重重新建 FPGA 工程，并对工程进行约束以及将 bit 文件下载到开发板运行。

### 3.1.1. 新建 TD 工程

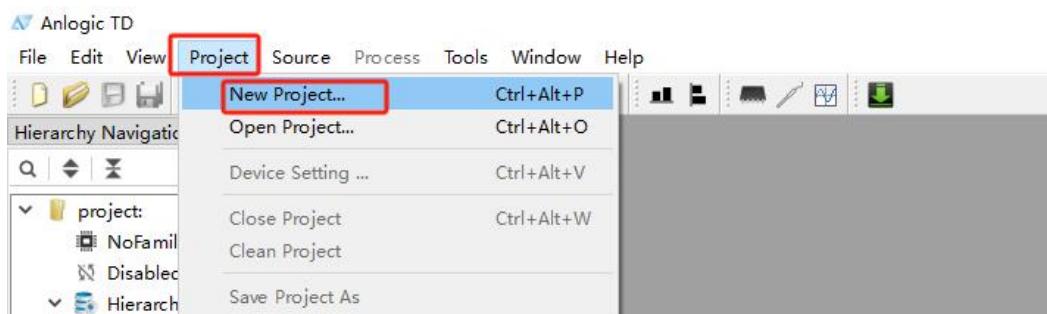

点击 Project-->New Project 新建工程

图 3-1. TD 界面

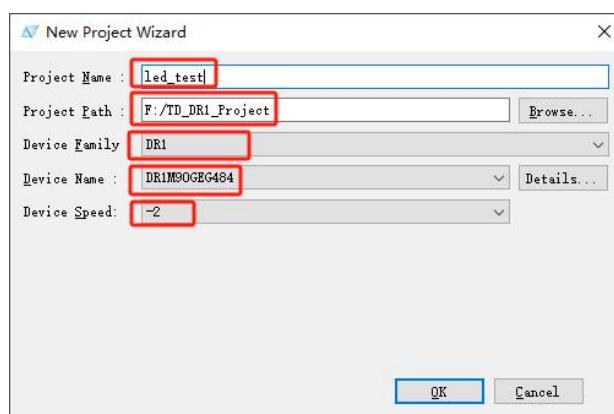

依次分别填写工程名称，工程路径，芯片类型，芯片型号，芯片速度等级，然后点击 OK

图 3-2. 新建工程对话框

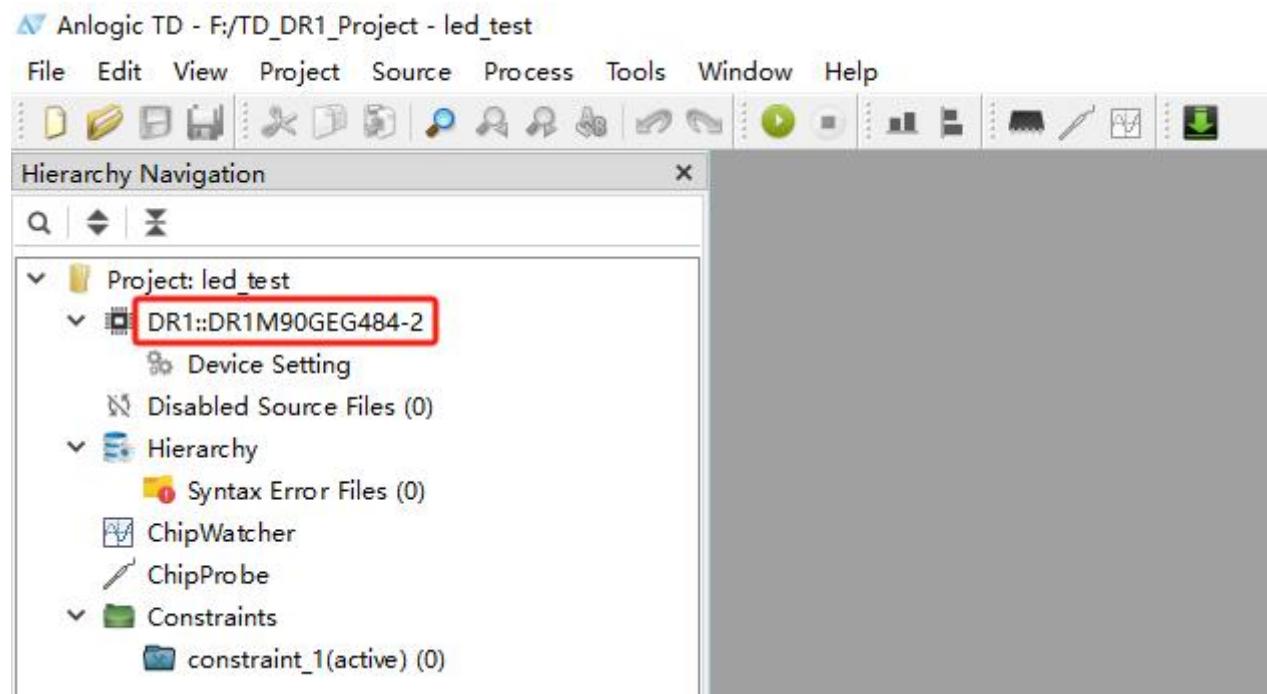

新建的 led\_test 工程，如下图所示

图 3-3. 新建的 led\_test 工程

### 3.1.2. 编写 Verilog 代码

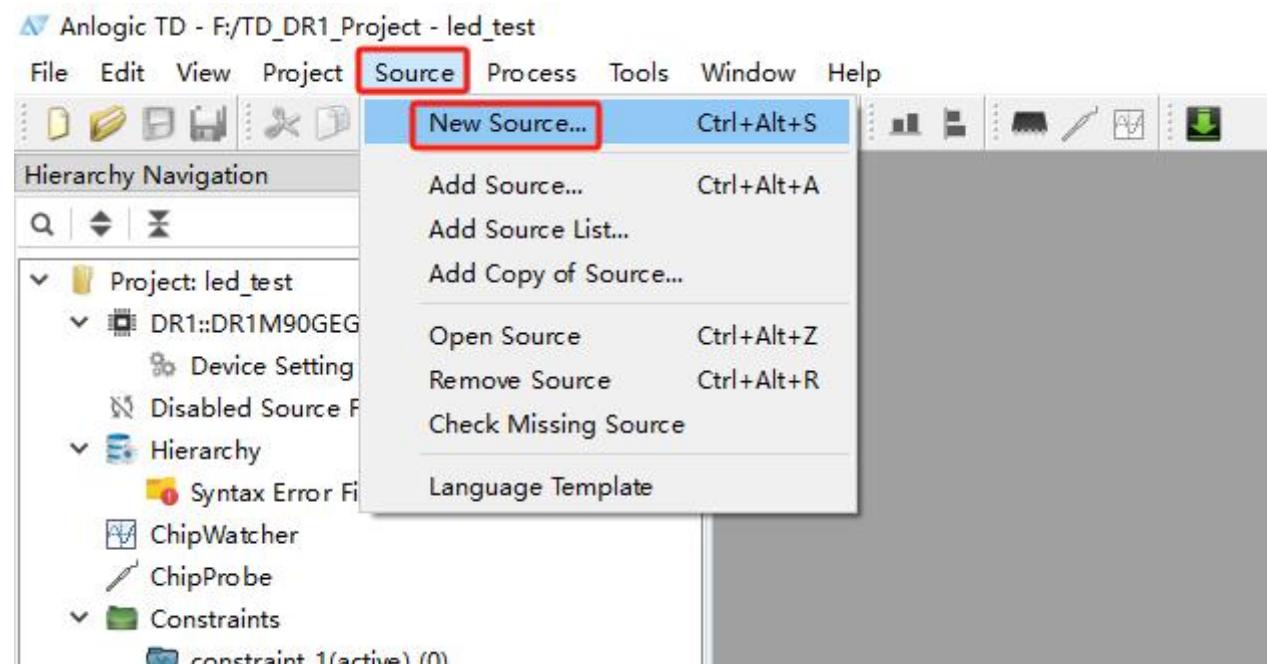

点击 Source-->New Source 新建 verilog 工程文件

图 3-4. 新建 verilog 工程

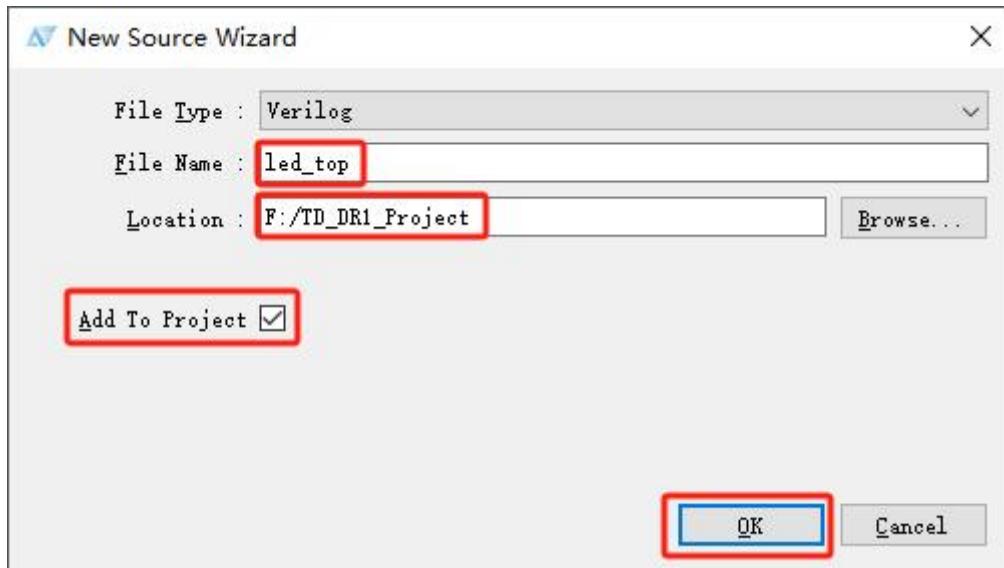

填写 verilog 工程名 led\_top，选择工程存放路径，加入到工程里，然后点击 OK

图 3-5. 新建 verilog 工程文件

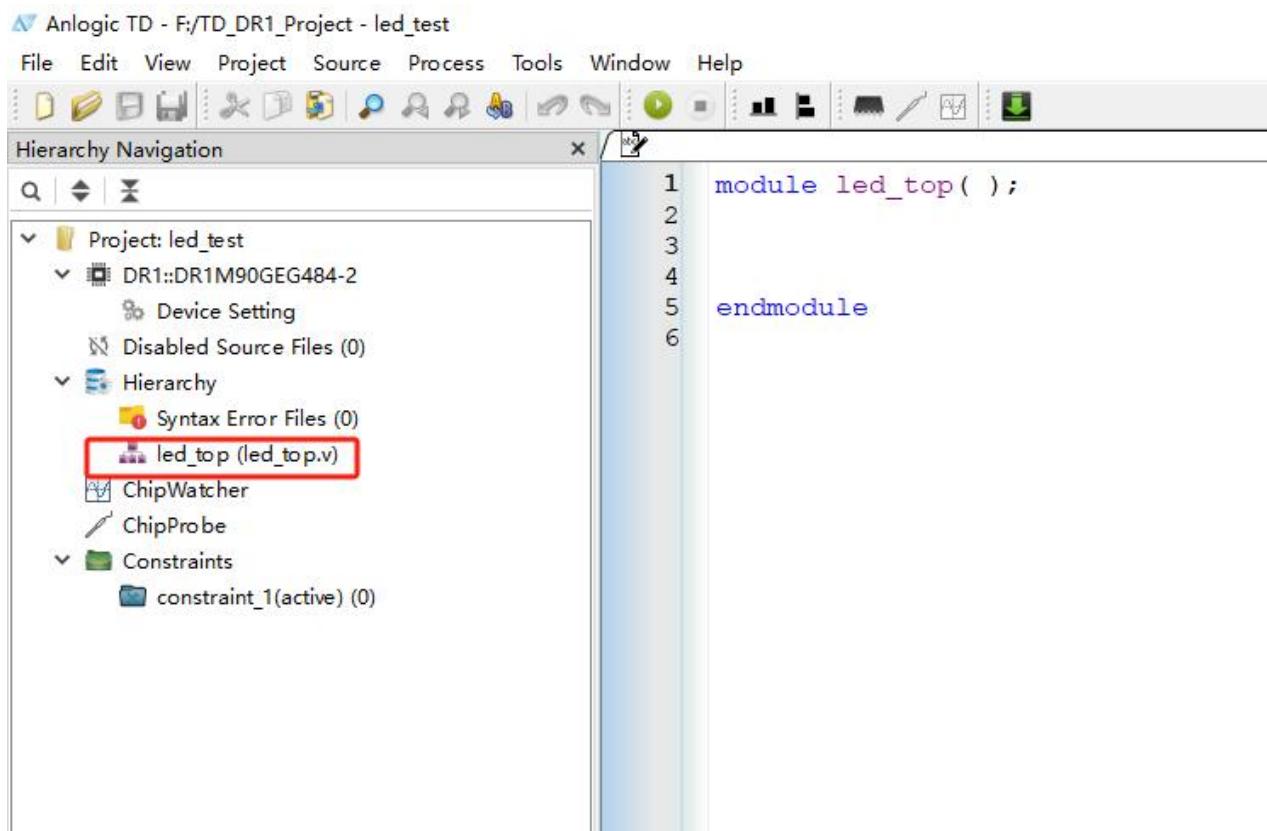

可以看到新建的 led\_top 工程文件

图 3-6. 新建的 led\_top 文件

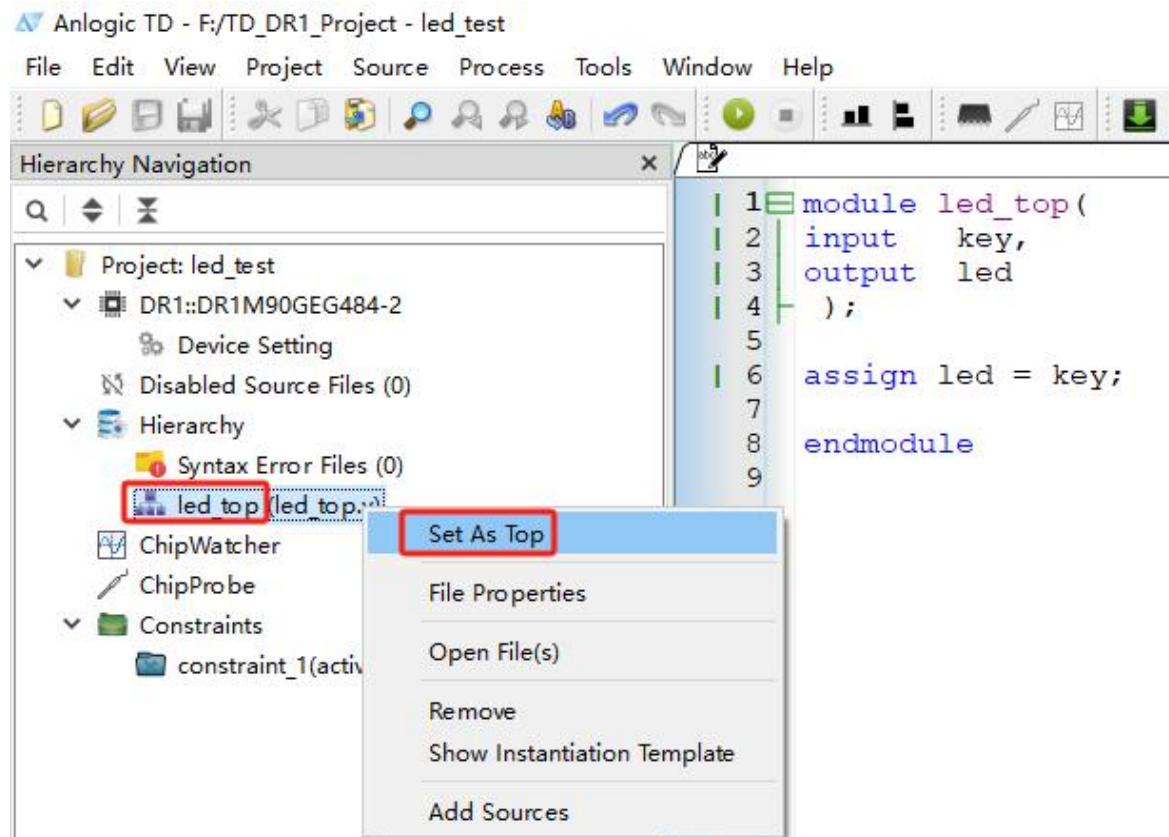

在代码编辑区，编写 led\_top 代码，如下图所示，因 pl 端没有接晶振，所以使用按键控制 led

```

1 module led_top(

2     input  key,

3     output led

4 );

5

6     assign led = key;

7

8 endmodule

9

```

图 3-7. 编写 led\_top 文件

右击 led\_top-->Set As Top 设置顶层文件

图 3-8. 设置顶层文件

### 3.1.3. 编译工程

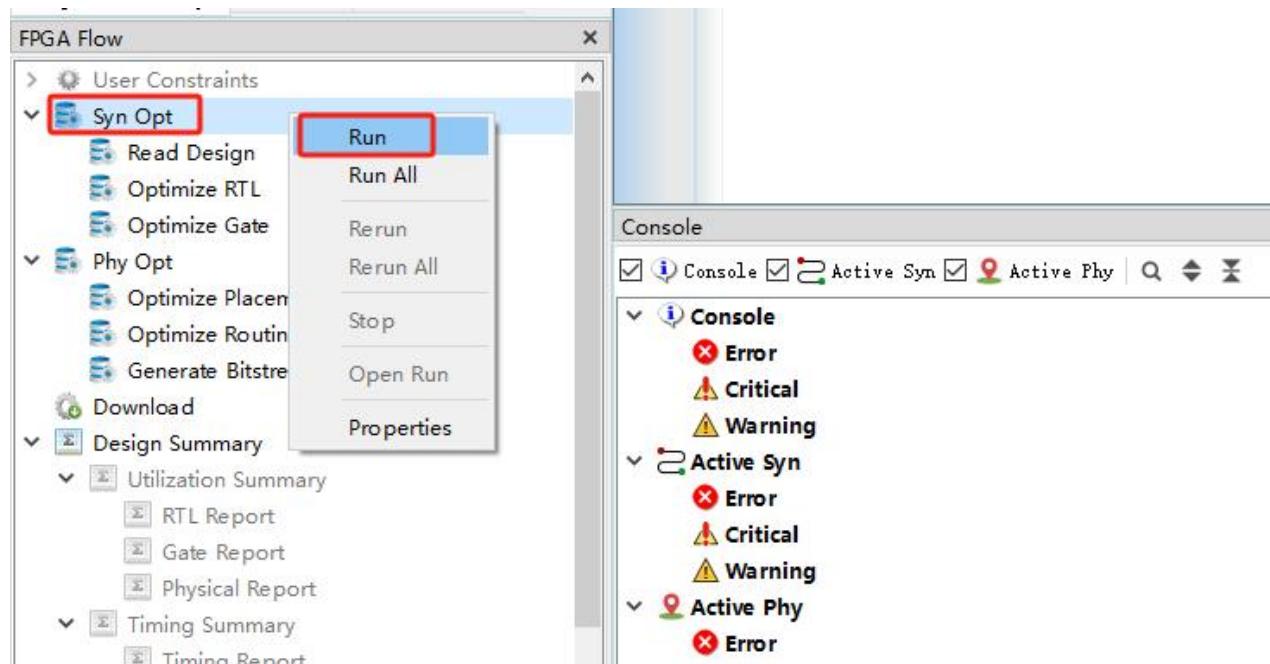

在 FPGA Flow 下的 Syn Opt 右击选择 Run 对工程进行编译

图 3-9. 编译工程

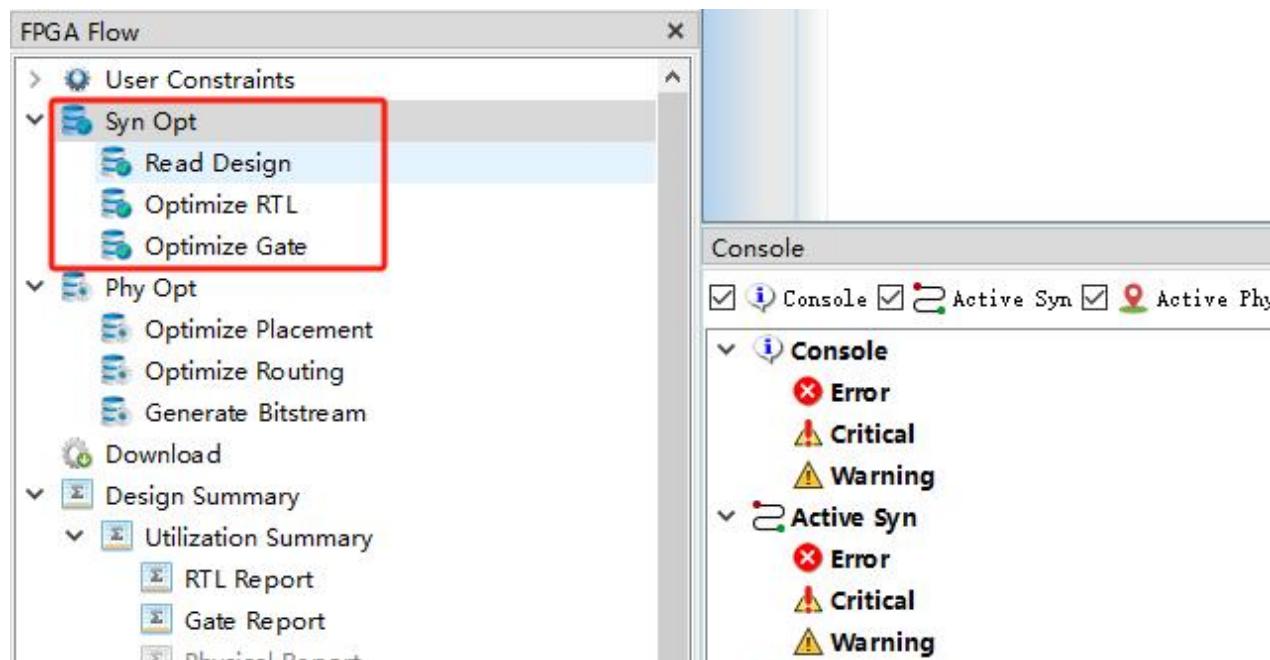

工程编译完成 (注意这部分只是编译 verilog 代码部分, 不包含管脚约束部分)

图 3-10. 工程编译完成

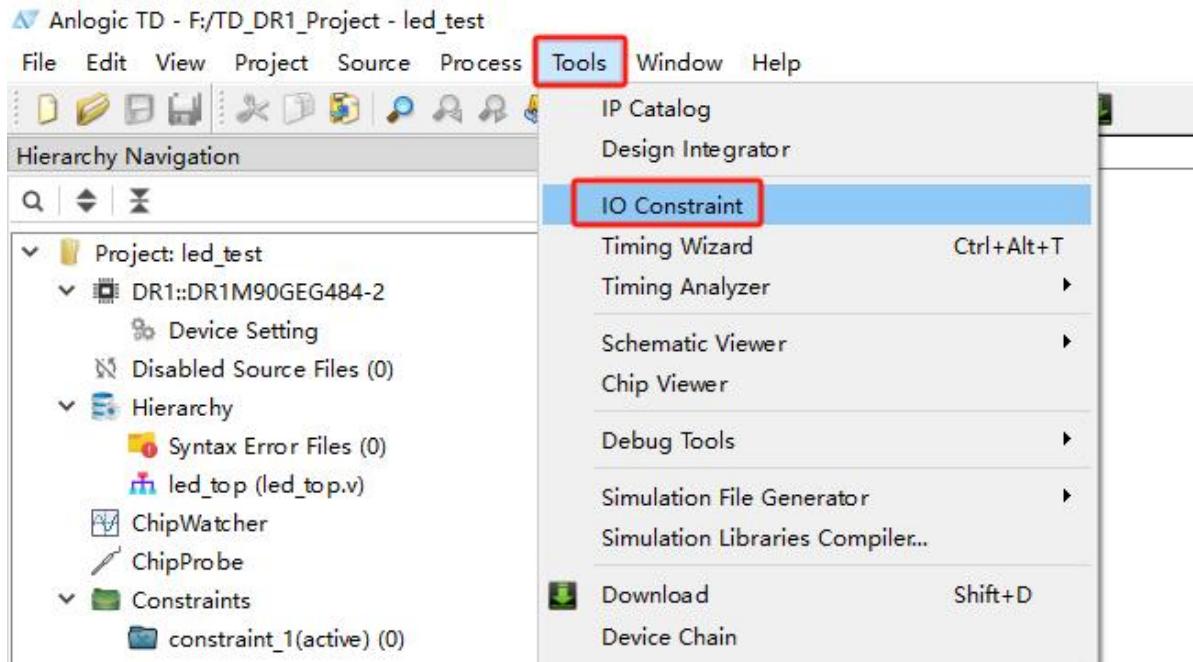

### 3.1.4. 设置管脚约束

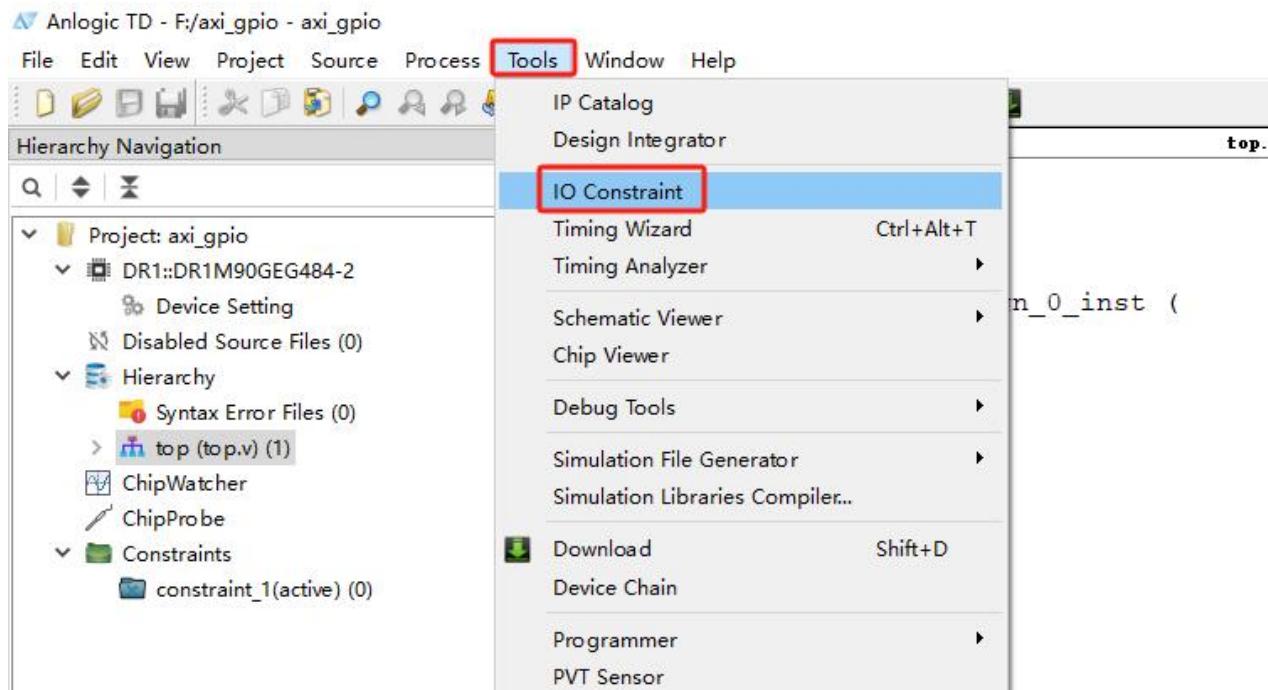

点击 Tools-->IO Constraint 设置管脚约束

图 3-11. 设置管脚约束

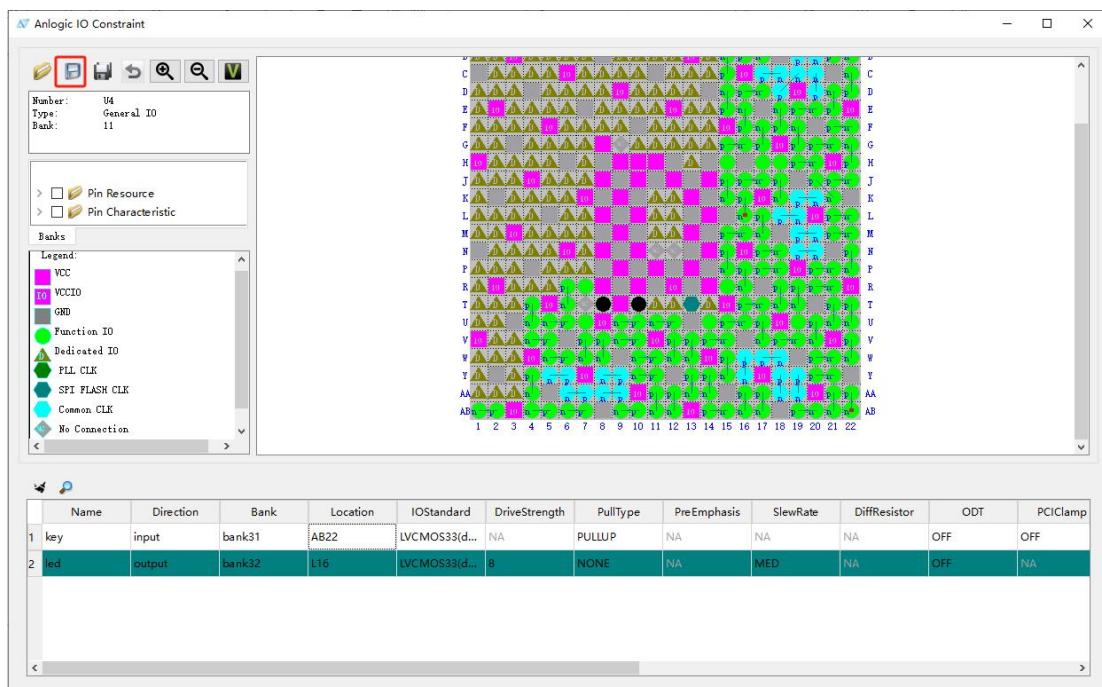

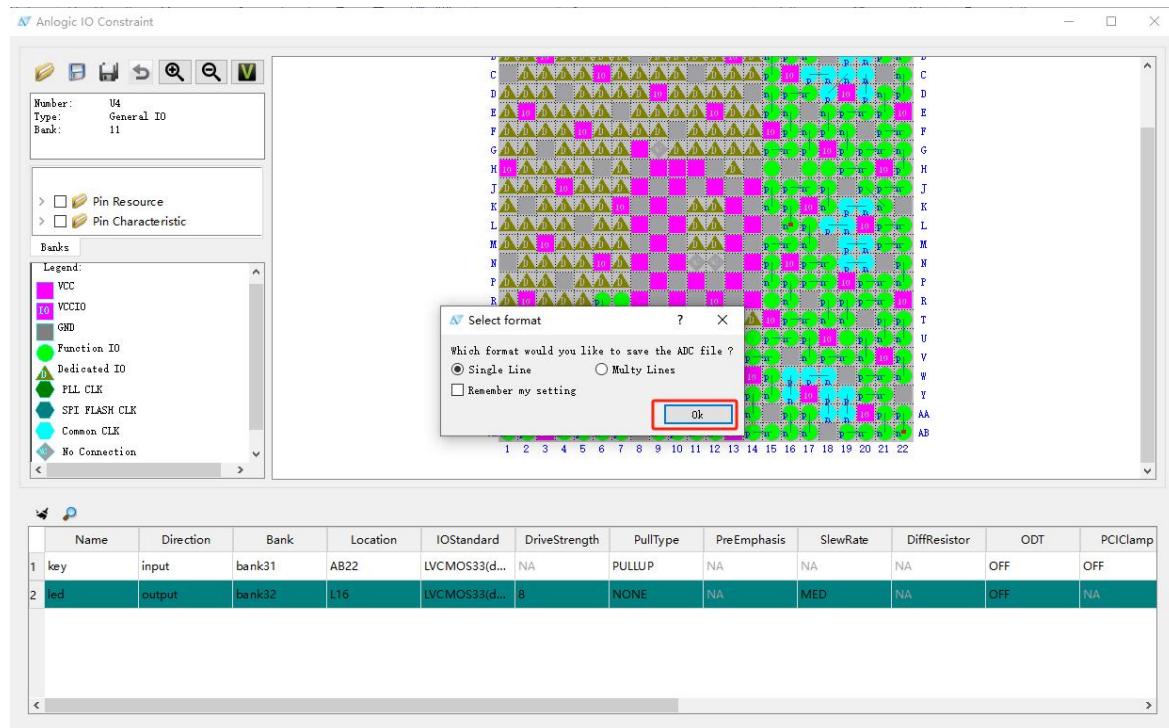

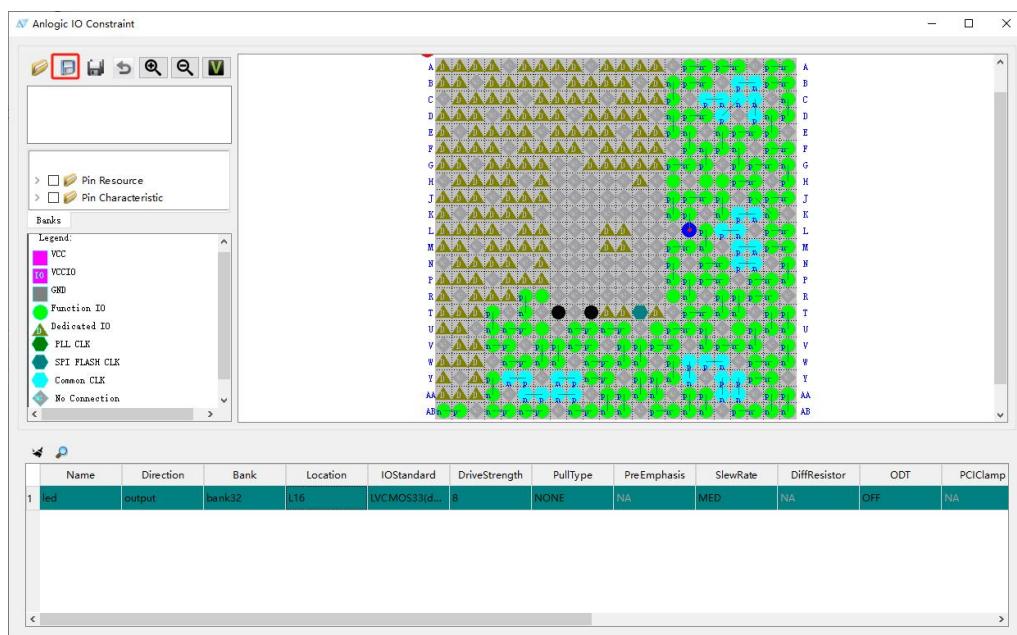

设置开发板的管脚约束和电压，然后点击保存按钮保存管脚约束

图 3-12. 配置管脚

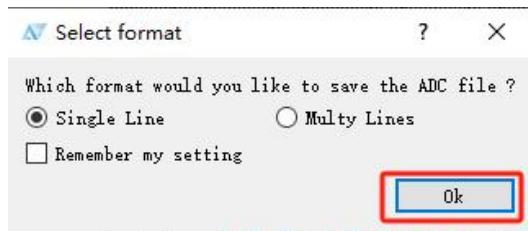

在弹出的对话框点击 OK

图 3-13. 保存约束

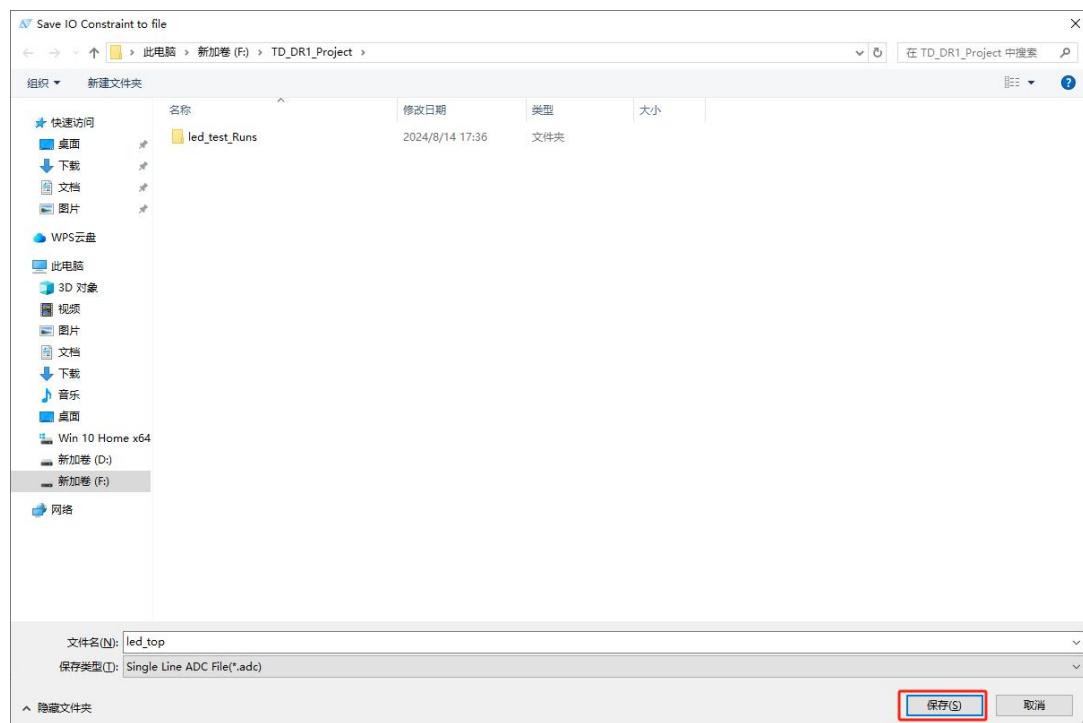

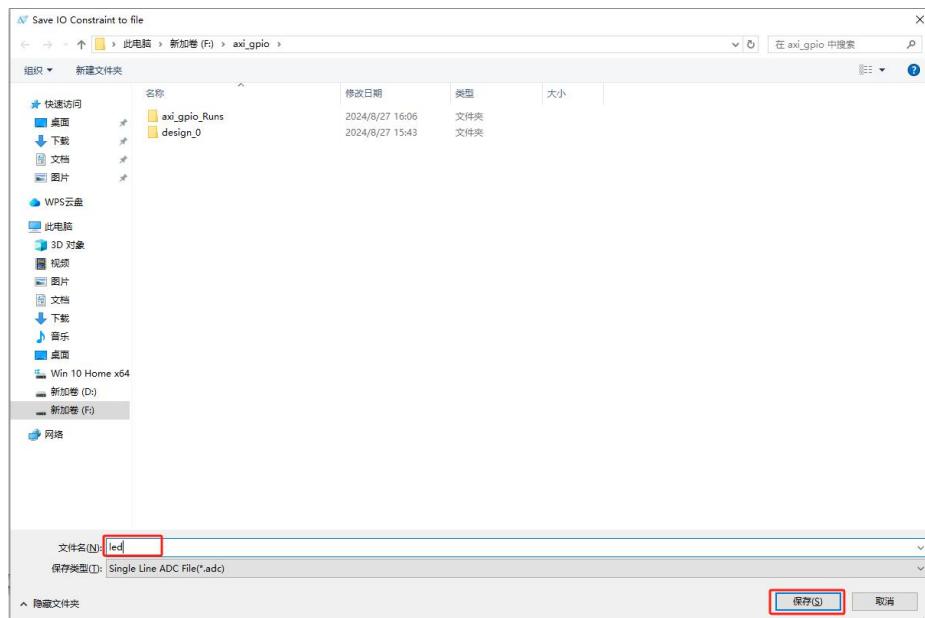

设置保存的约束文件名称，点击保存

图 3-14. 保存约束文件

生成的约束文件，如下图所示

```

set_pin_assignment { key } { LOCATION = AB2

set_pin_assignment { led } { LOCATION = L16

```

图 3-15. 生成约束文件

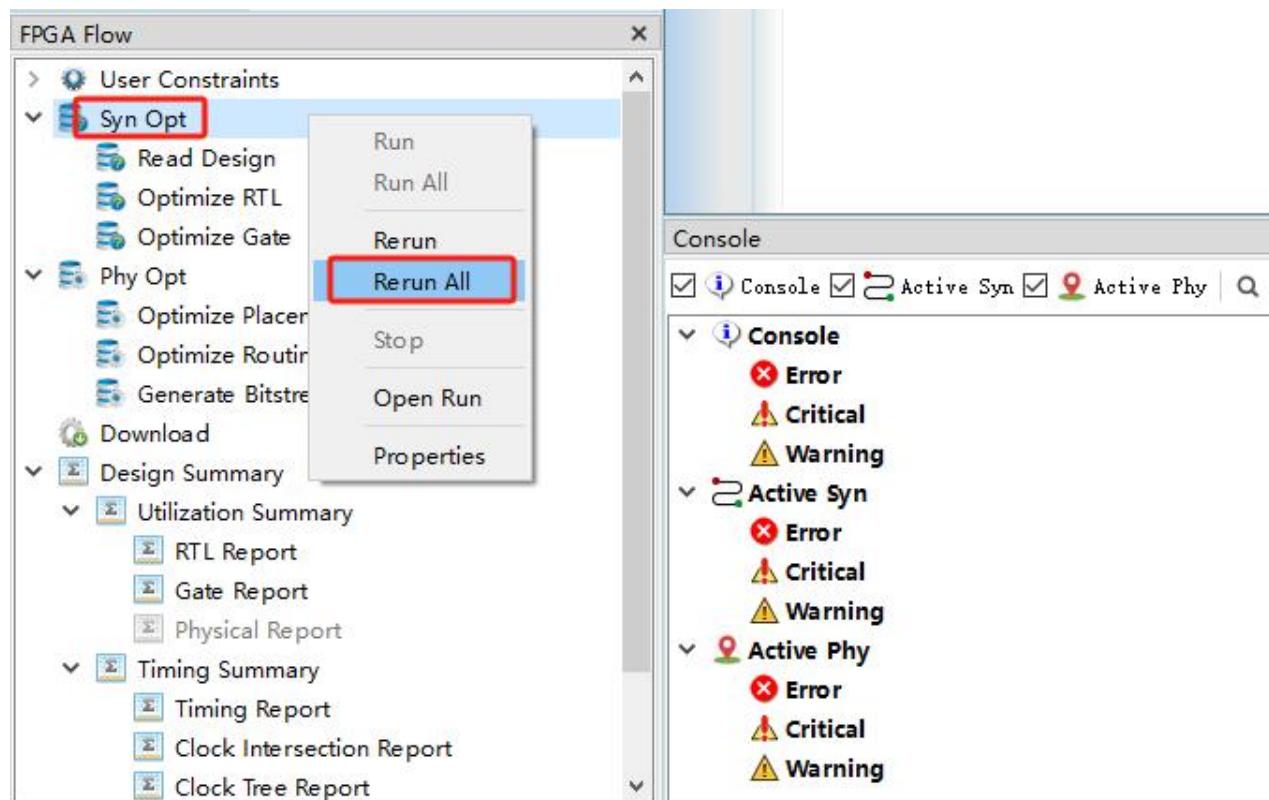

因添加了约束文件，所以整个工程需要重新编译一次，在 Syn Opt 右击选择 Rerun All 编译整个工程

图 3-16. 编译整个工程

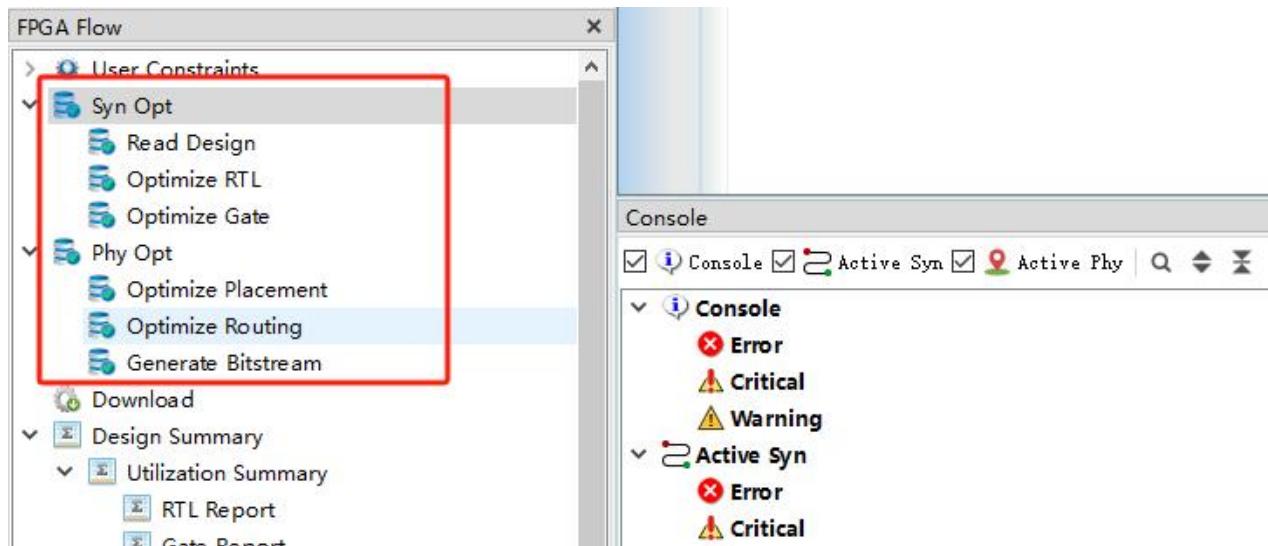

工程编译完成，生成了 bit 文件，如下图所示

图 3-17. 整个工程编译完成

### 3.1.5 下载 bit 文件

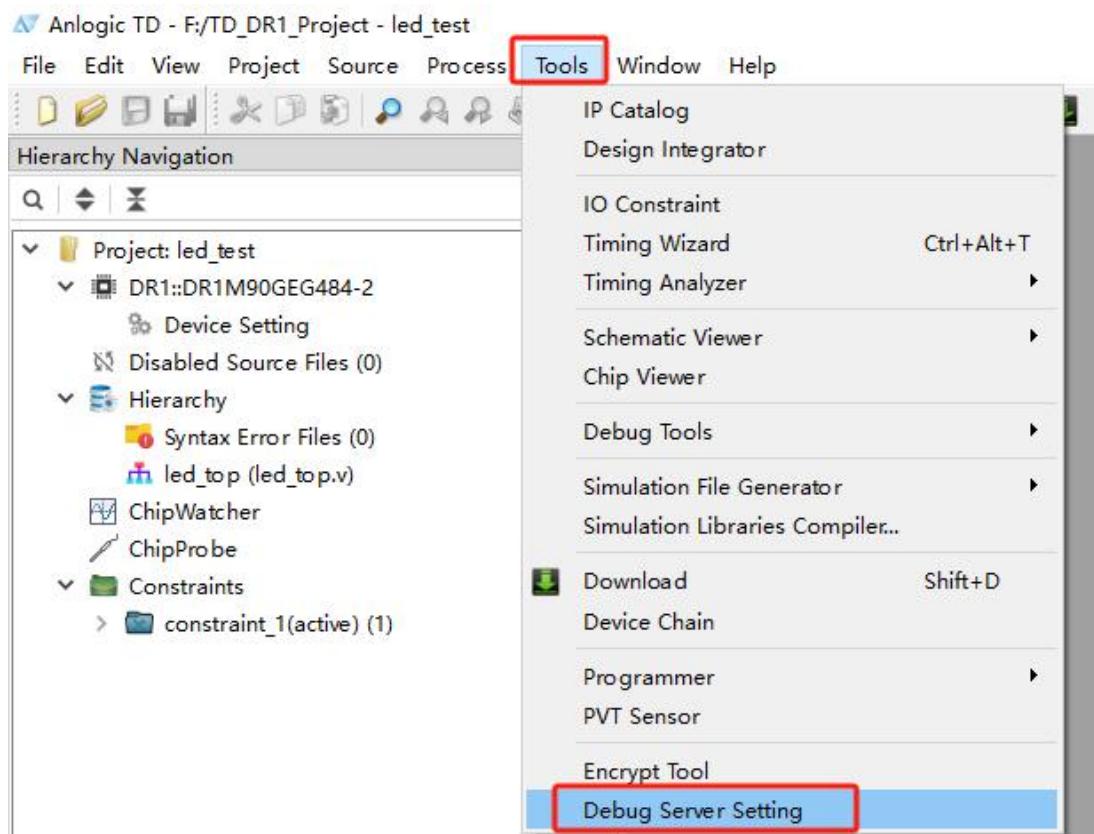

选择 Tools-->Debug Server Setting，设置 jtag 参数

图 3-18. 打开 JTAG 设置对话框

在弹出的对话框，选择 AL-LINK-FT,点击 Refresh 刷新器件，Cable Select 会显示接口，然后点击 Apply

图 3-19. JTAG 接口参数设置

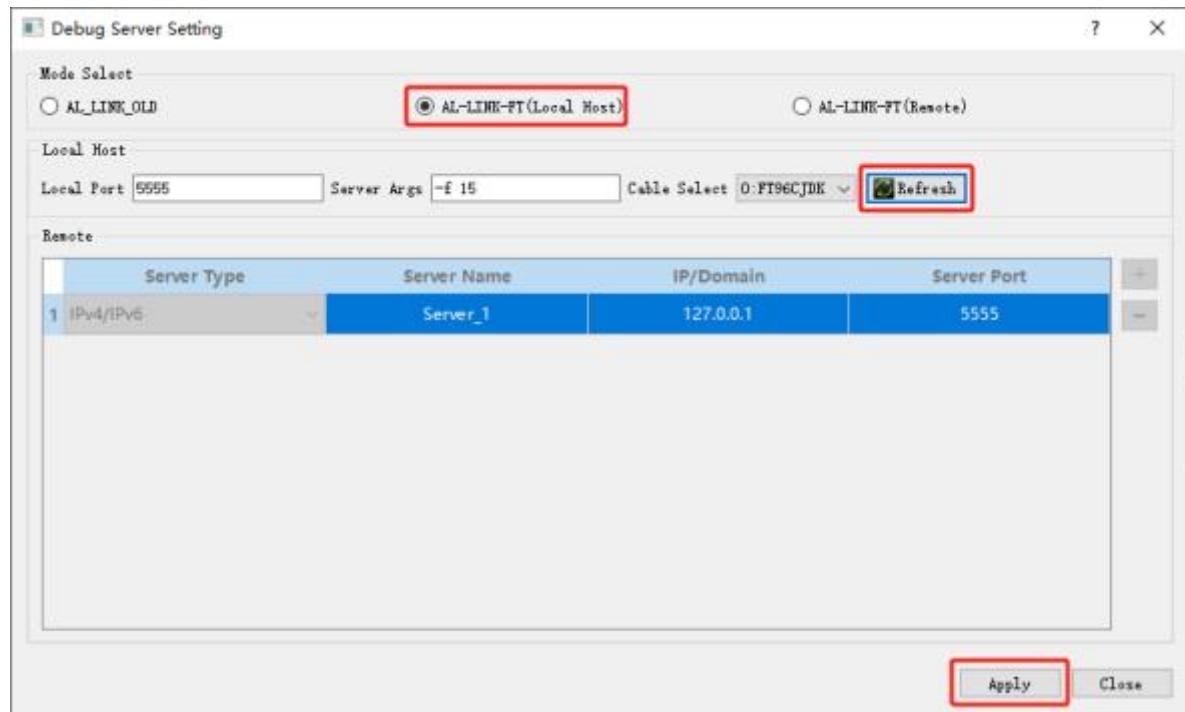

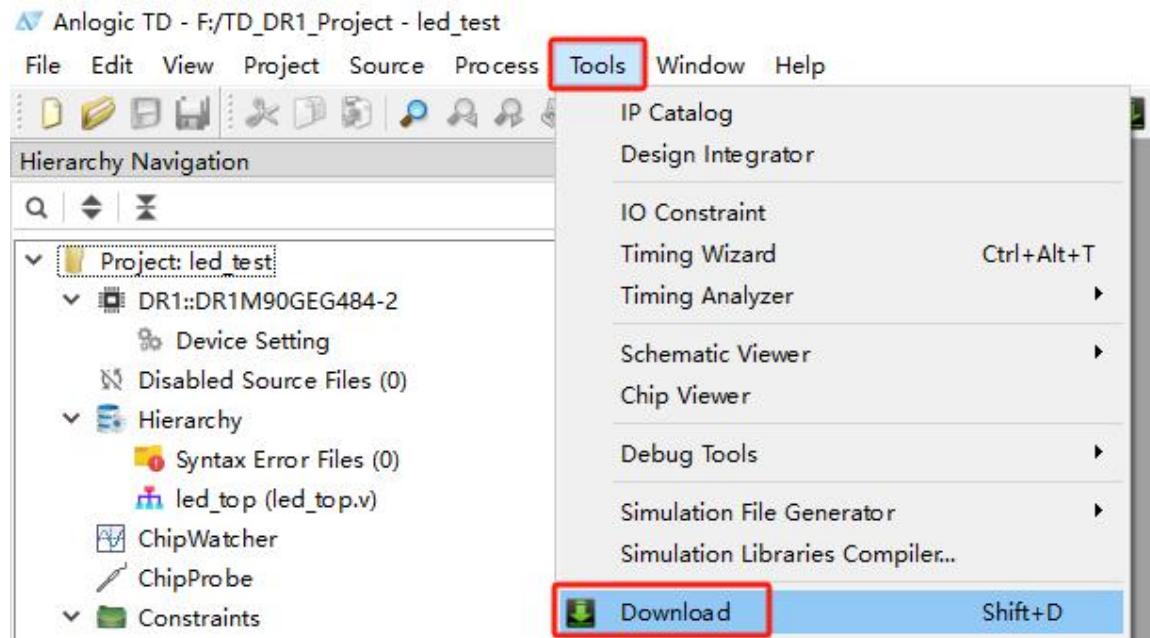

选择 Tools-->Download，打开 JTAG 下载界面

图 3-20. 打开 JTAG 下载对话框

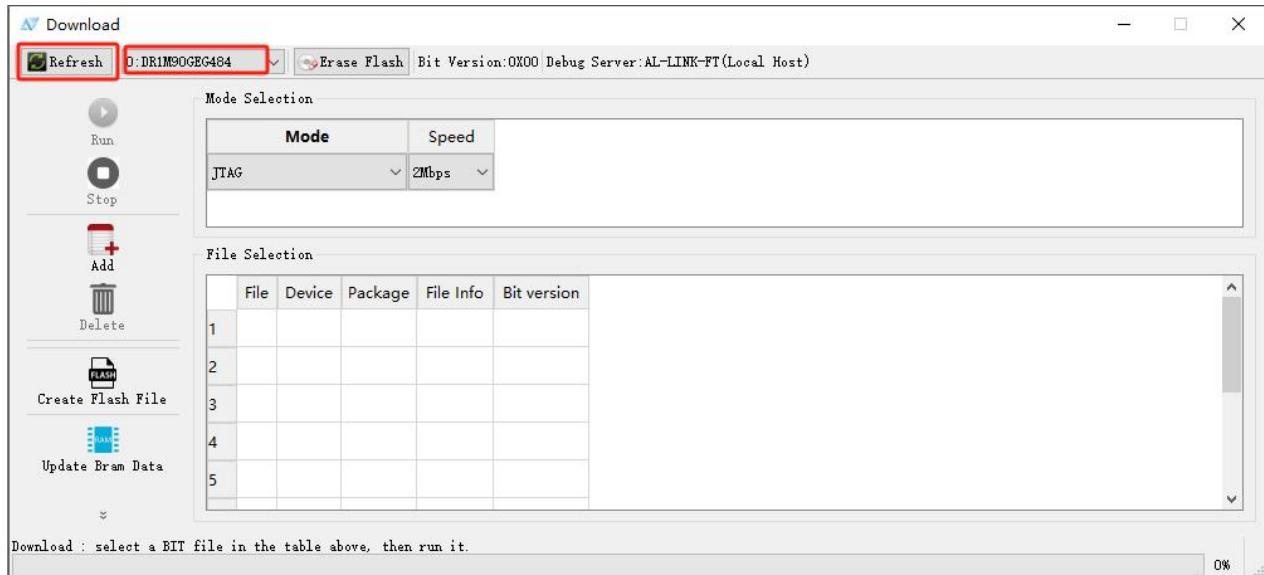

下载前请将开发板上电，点击 Refresh，右侧可以看到识别的开发板型号为 DR1M90GEG484 这个型号，说明 JTAG 已经正常识别

图 3-21. 扫描 JTAG 设备

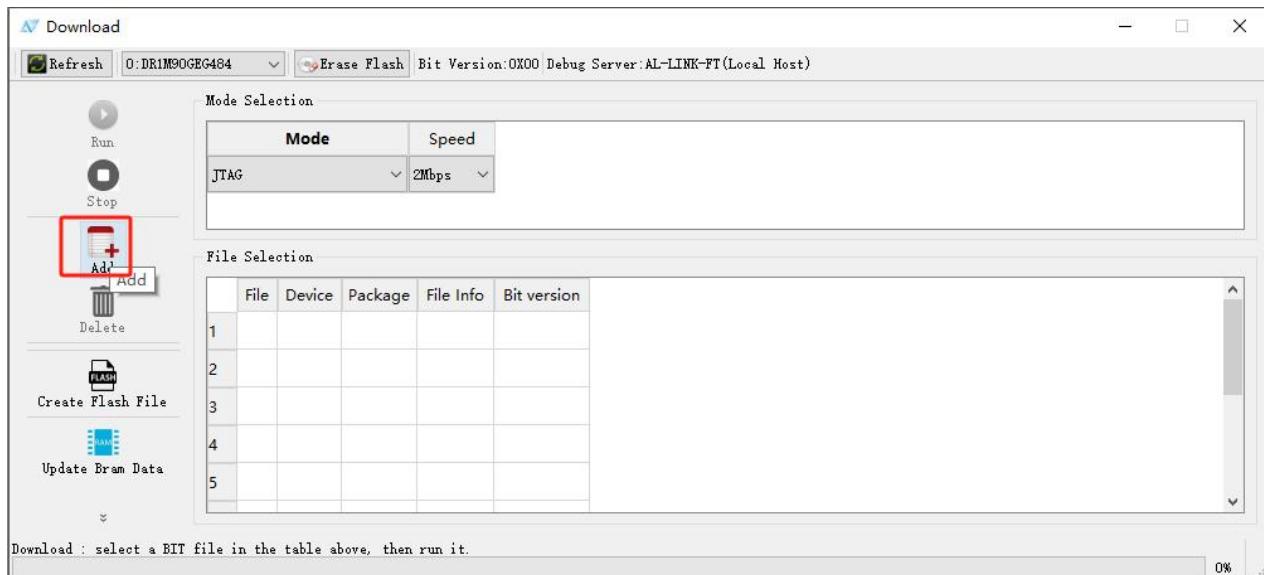

点击 Add 图标，添加 JTAG 下载文件

图 3-22. 添加 JTAG 下载文件

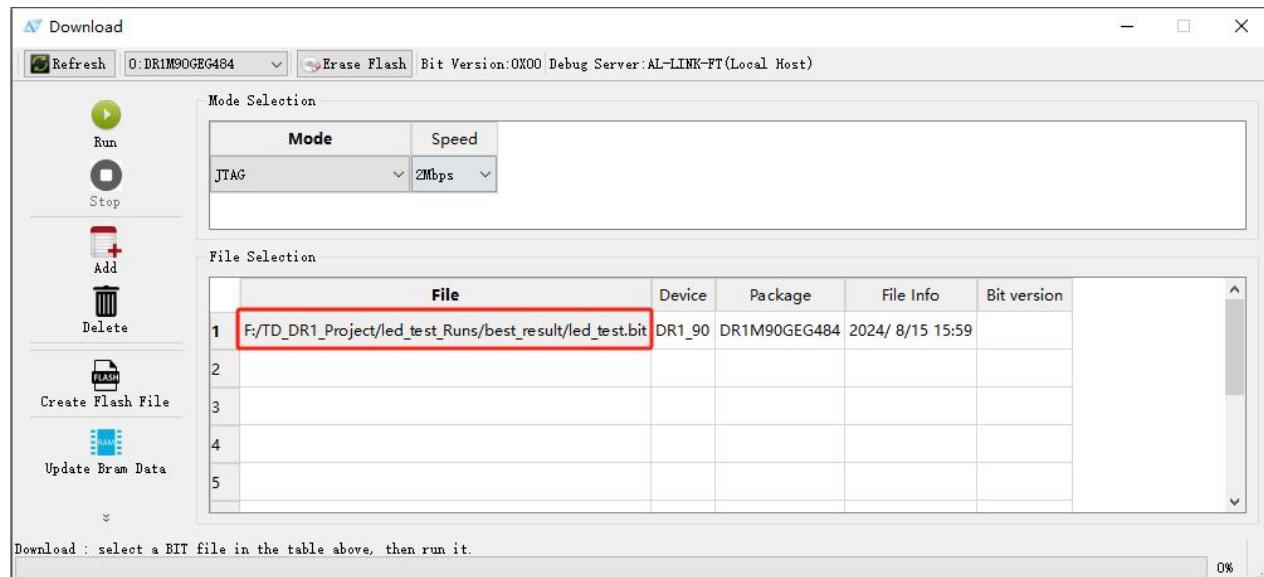

## 添加 bit 文件

图 3-23. 添加 bit 下载文件

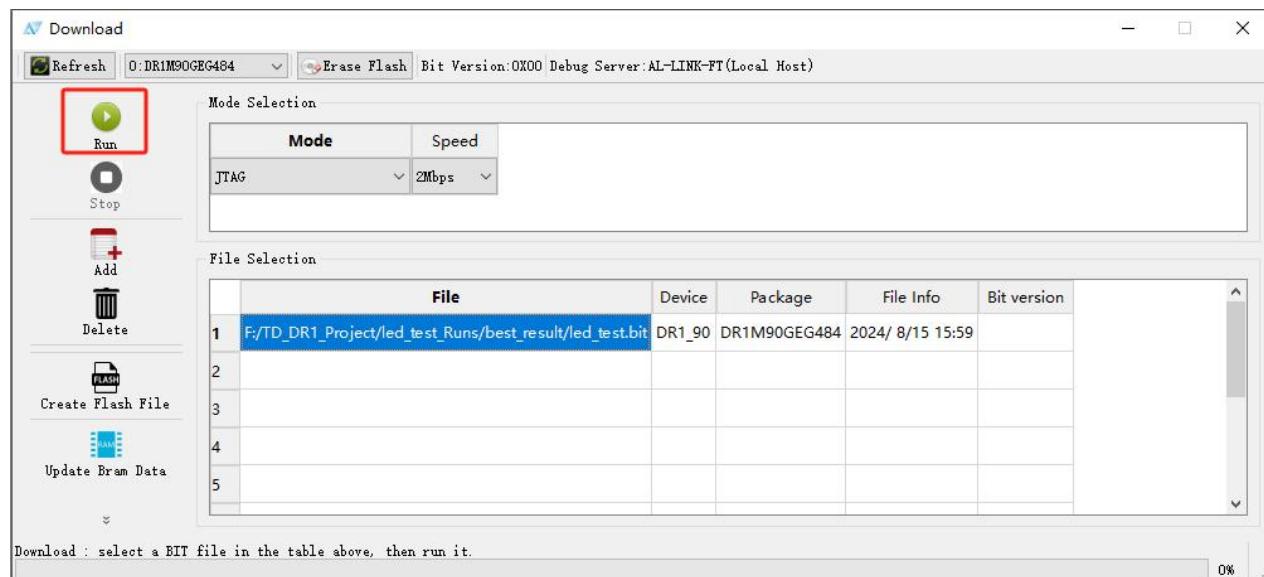

## 点击 Run 开始下载 bit 文件

图 3-24. 开始下载 bit 文件

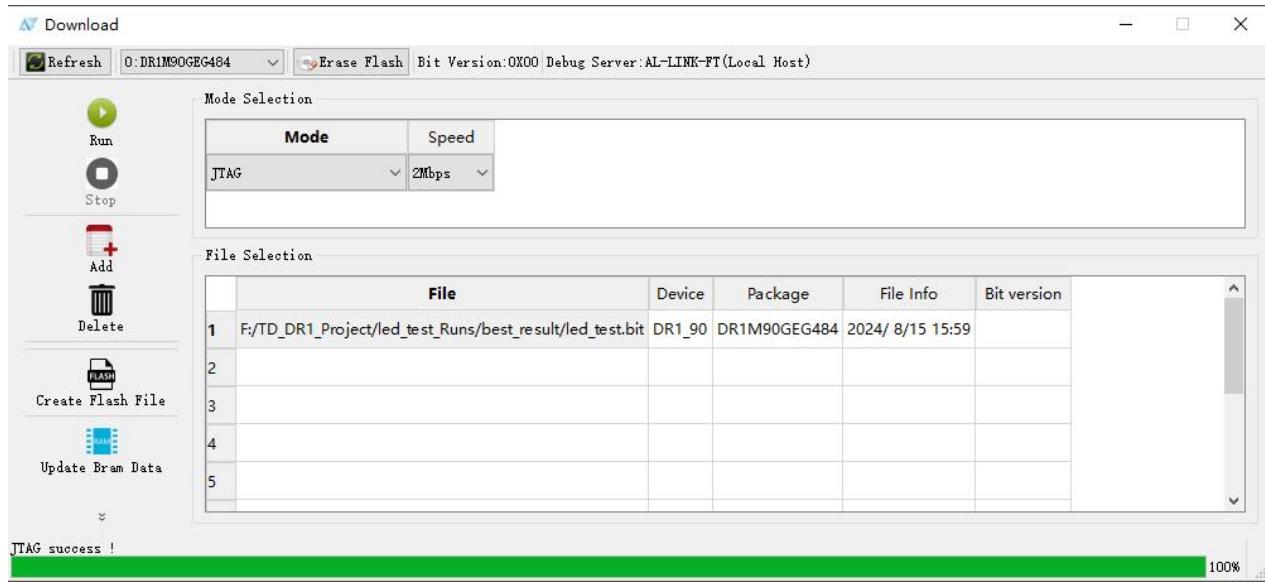

bit 文件下载成功

图 3-25. bit 文件下载成功

# 第四章 串口输出打印测试

MYD-YM90X 的平台主要是 FPGA 和 ARM 两部分组成，上一个章节主要介绍怎么使用 FPGA 部分，这章节着重介绍 ARM 部分，怎么配置 PS 端设备，ARM 端将会用到 FD 软件平台，本章节主要介绍 PS 端接口配置，以及 FD 软件平台的简单使用。

## 4.1. UART 工程介绍

本章节主要使用 PS 端的 UART 进行串口输出打印测试，因不涉及 PL 端管脚，所以不需要添加 PL 约束，需注意如何配置 PS 端的 ARM 核。

### 4.1.1. 新建 Hello\_world 工程

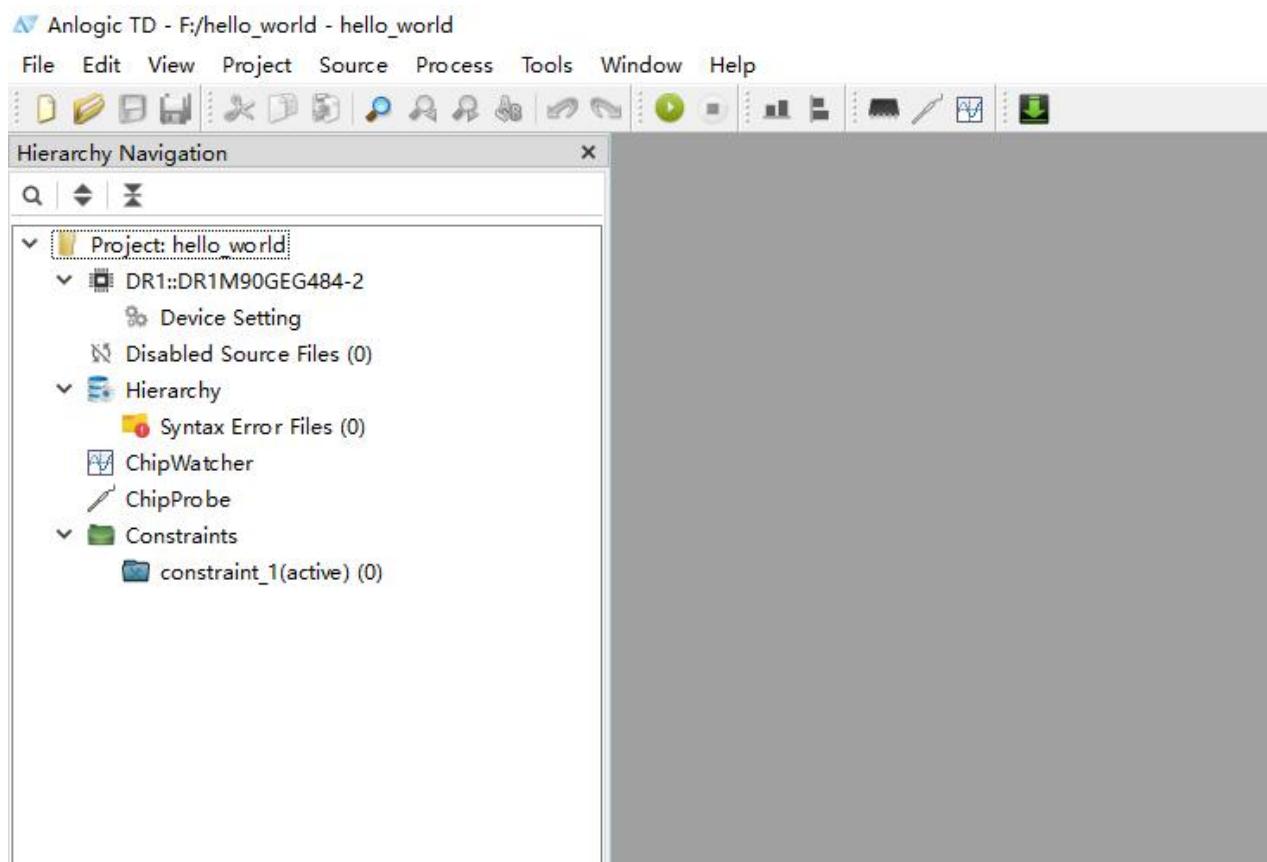

因新建工程部分和前一章节一样，这里不再重复新建 TD 工程步骤，不熟练的可以参考上一章节新建工程的方法。

图 4-1. 新建 TD 工程

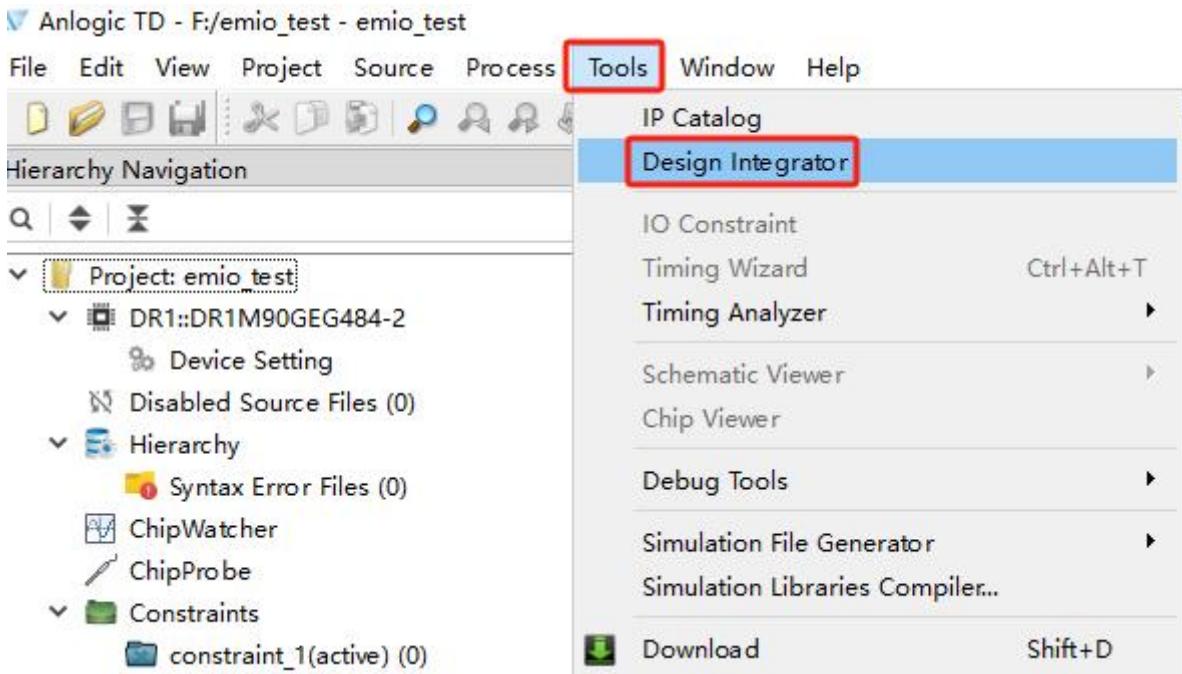

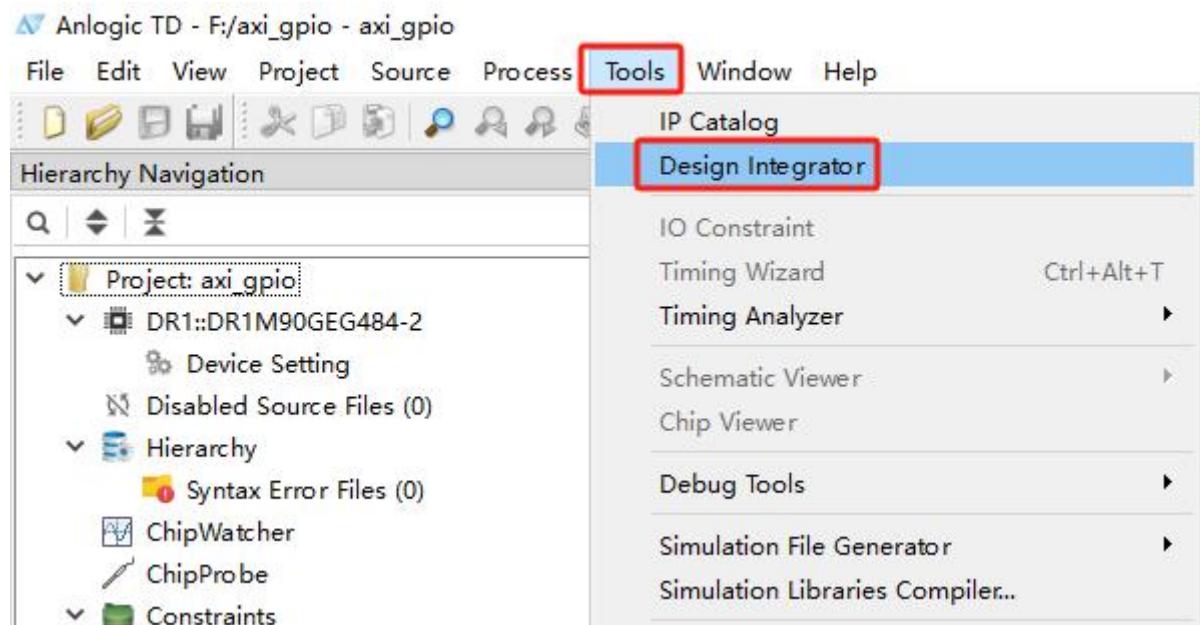

## 4.1.2. 打开 Design Integrator

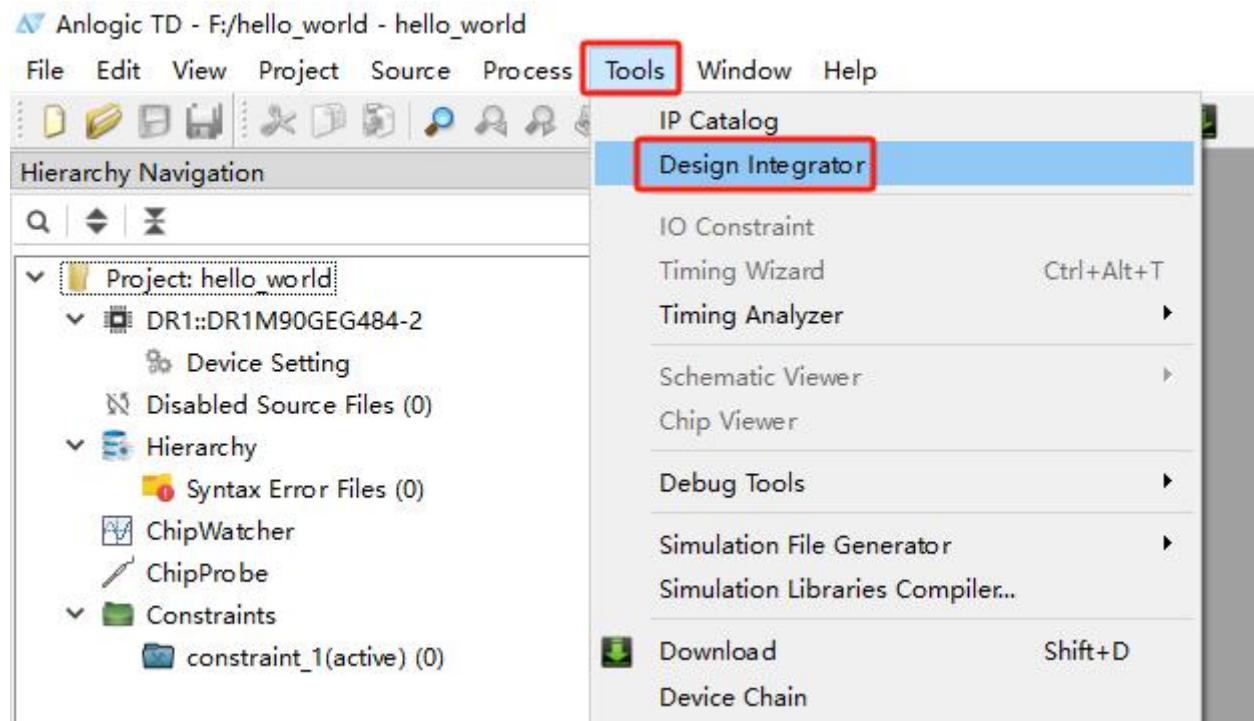

为了方便用户在 TD 中使用 IP，避免手写 IP 端扣间连接的重复操作，开发了 Design Integrator 工具，其主要功能是：根据用户定制的 ip 以及端口，在连线后生成对应 RTL 代码。

选择 Tools-->Design Integrator

图 4-2. 打开 Design Integrator

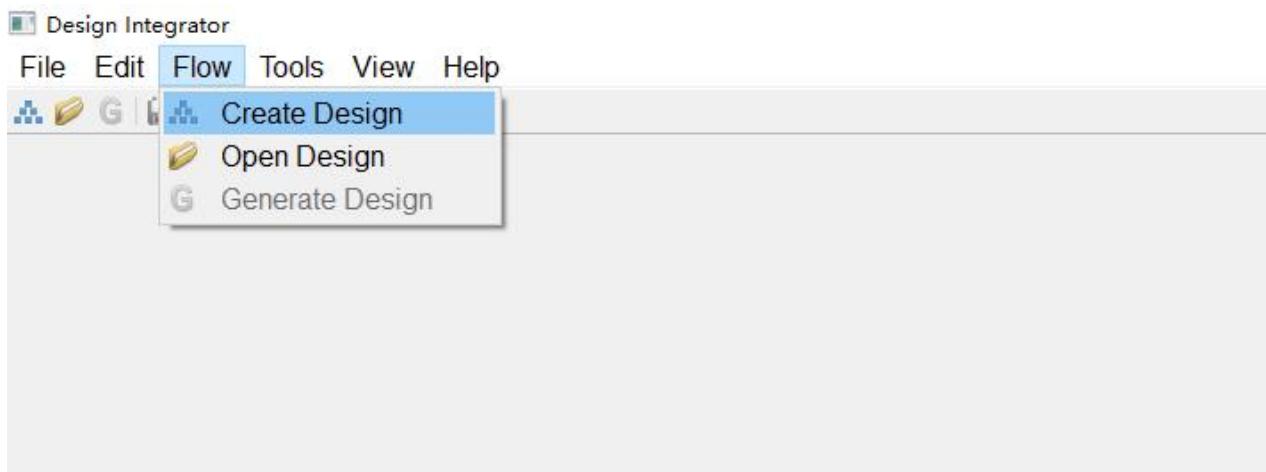

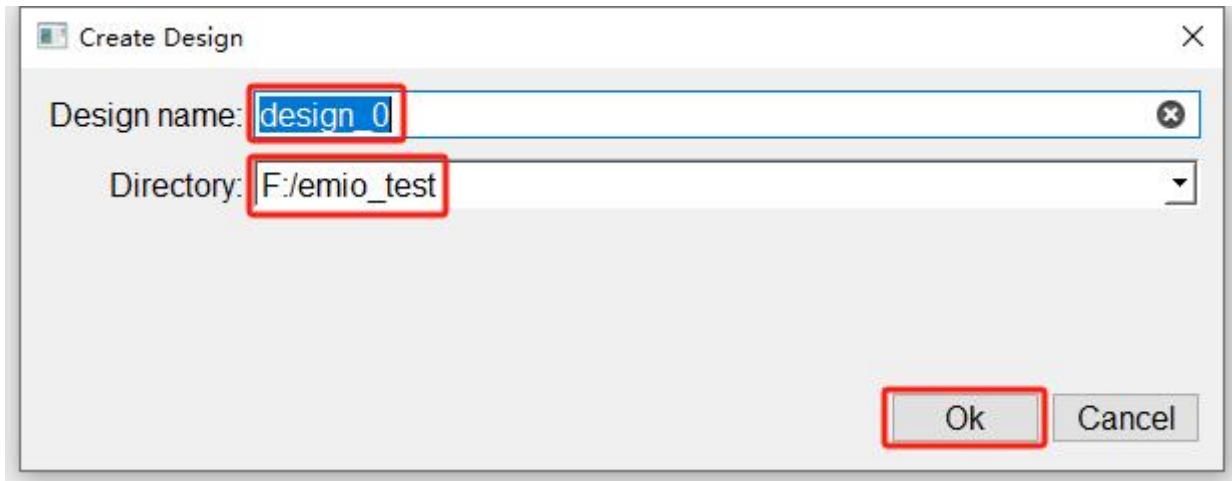

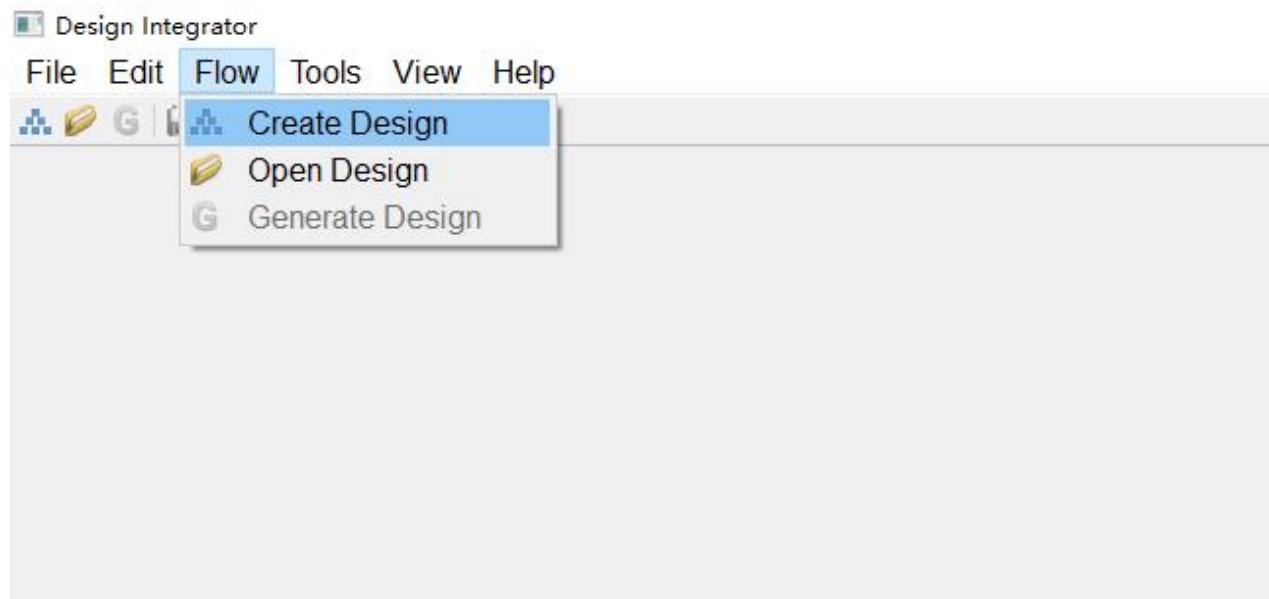

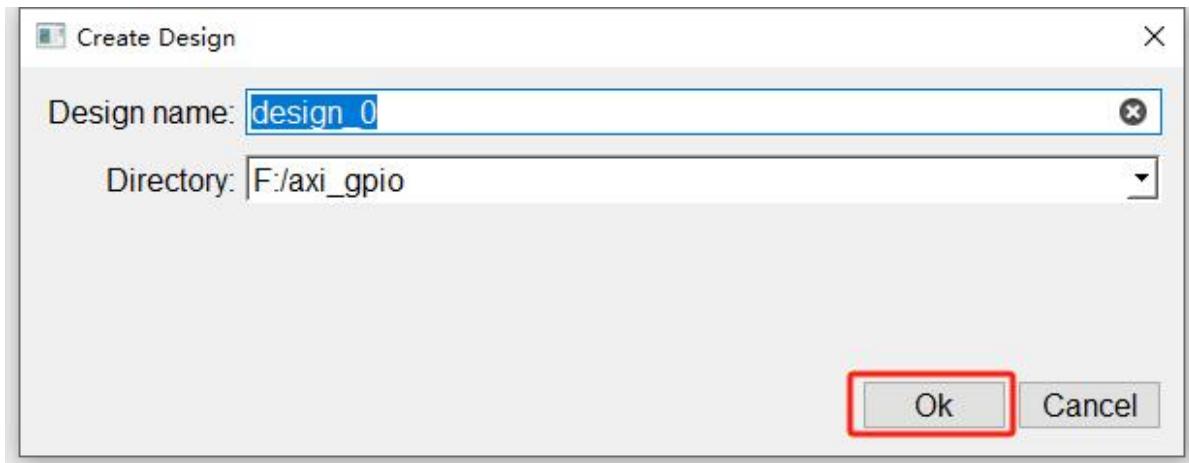

## 4.1.3. 新建 Design

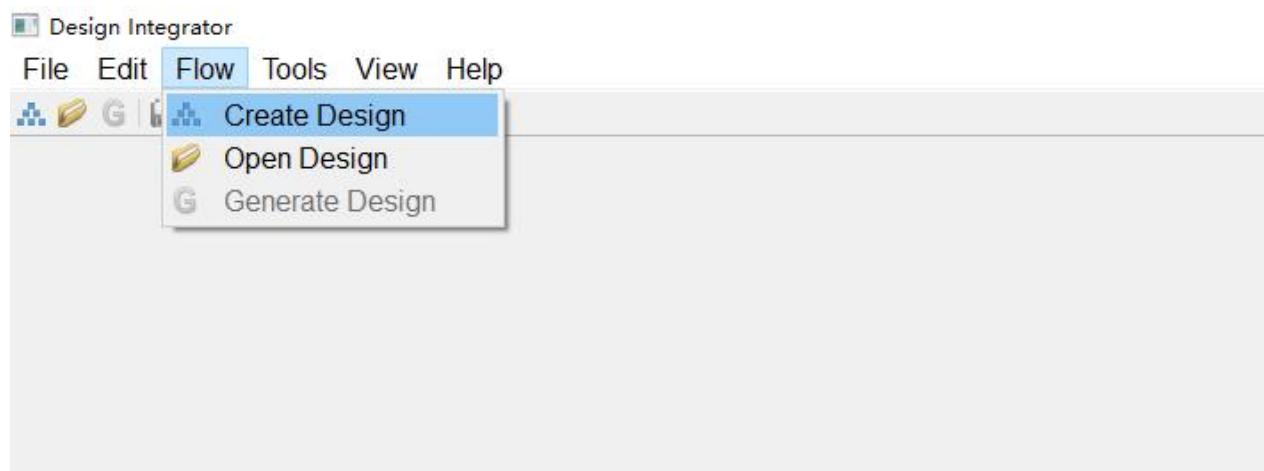

点击 Flow-->Create Design

填写 design 名称和存储路径，然后点击 OK

图 4-3. 新建 design

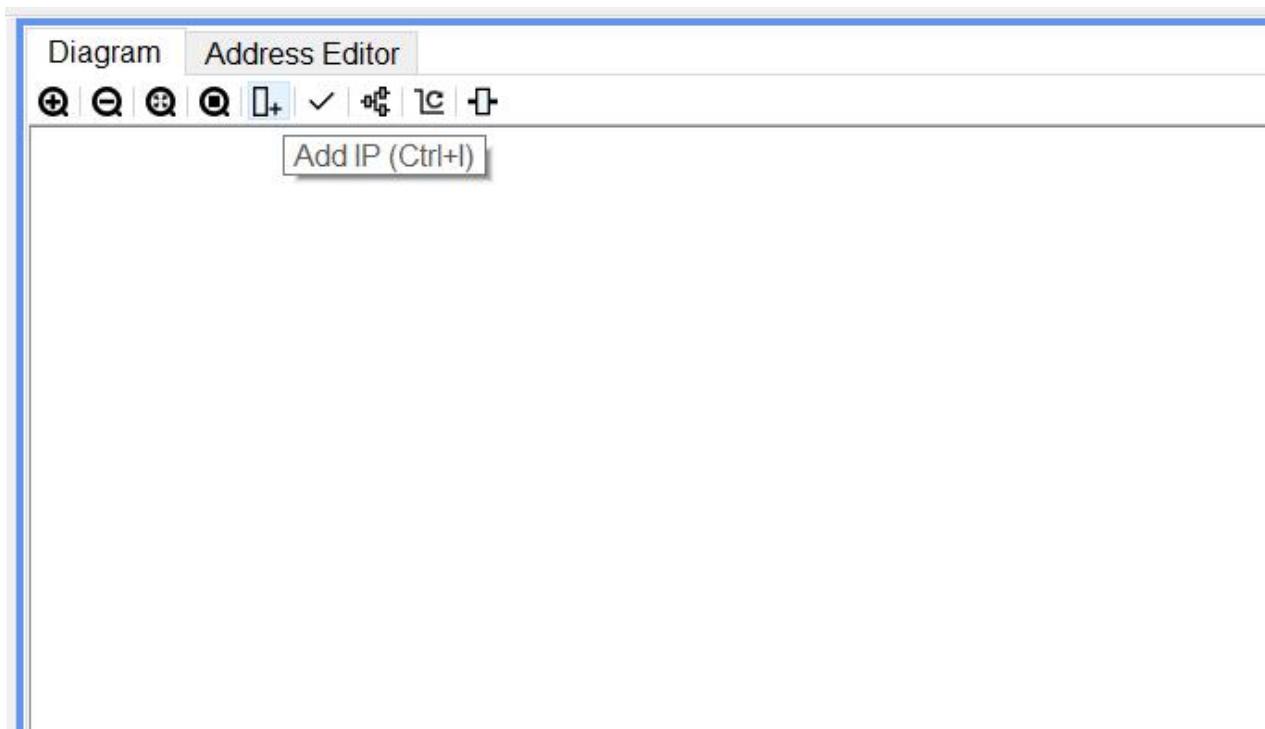

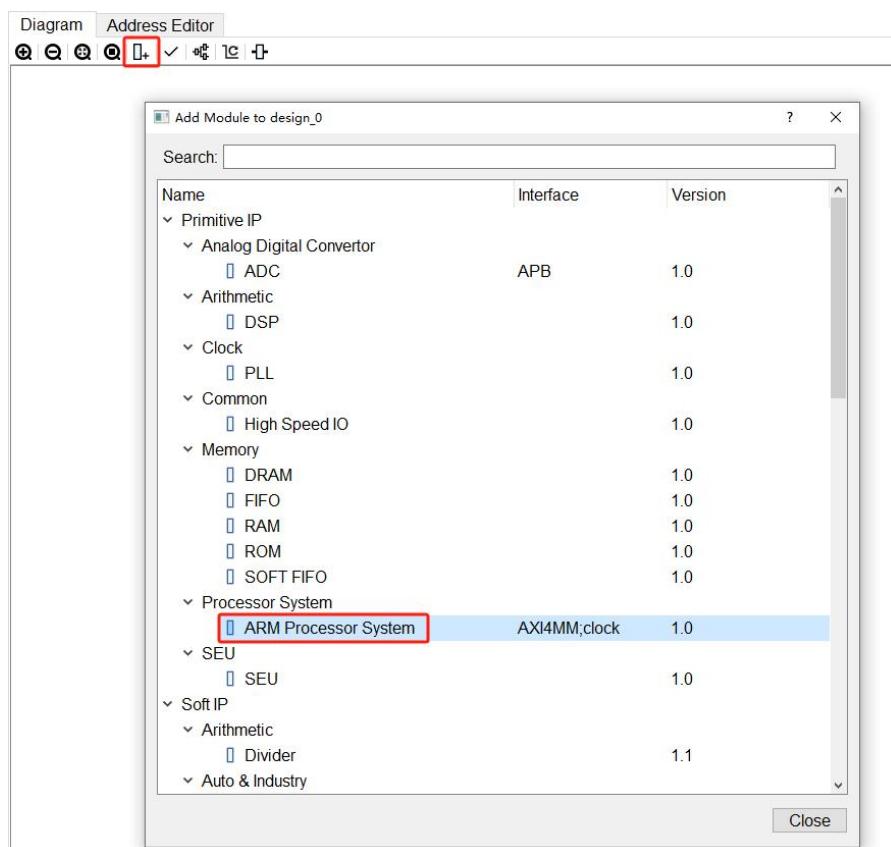

#### 4.1.4. 调用 PS 端 IP

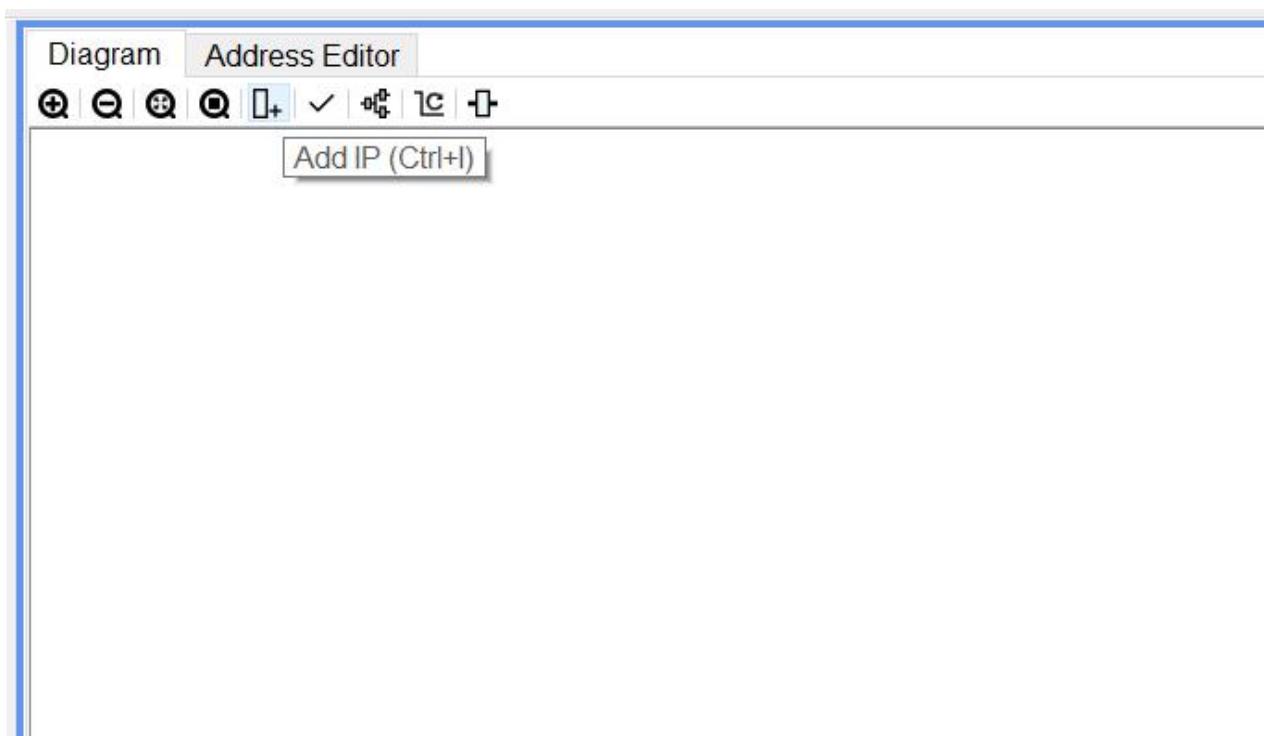

点击 Add IP 添加 PS 端 ip

图 4-4. 添加 ps 端 ip

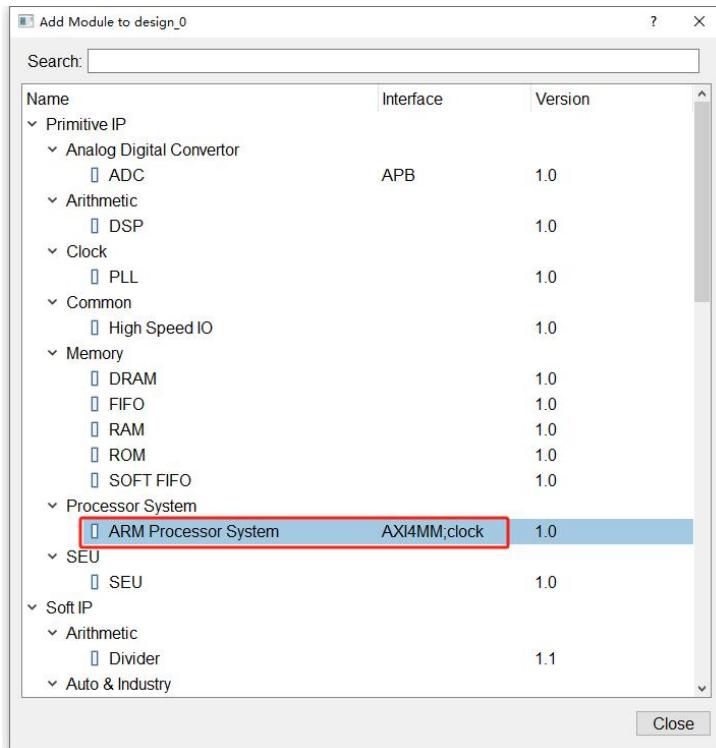

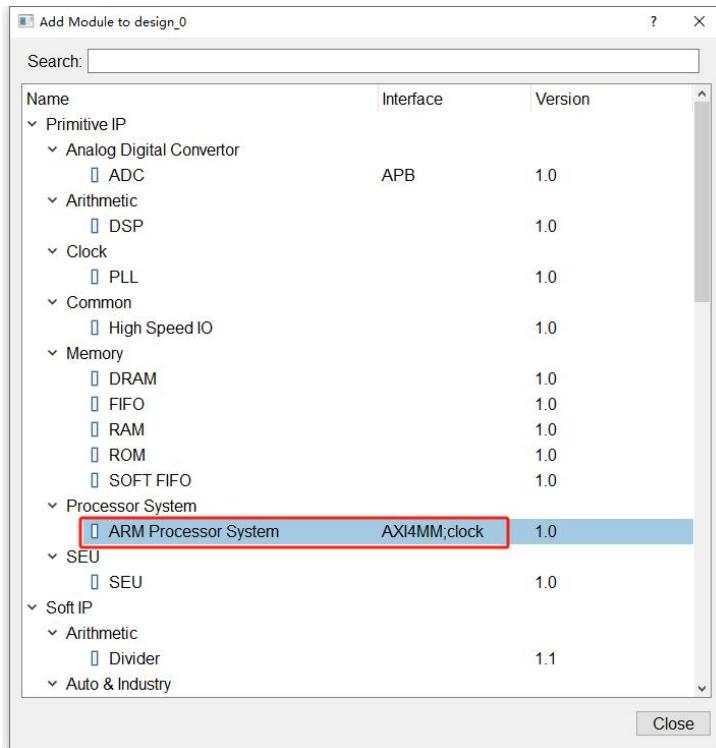

在弹出的对话框中，双击 ARM Processor System 调用 ip 核

图 4-5. 调用 ps 端 ip

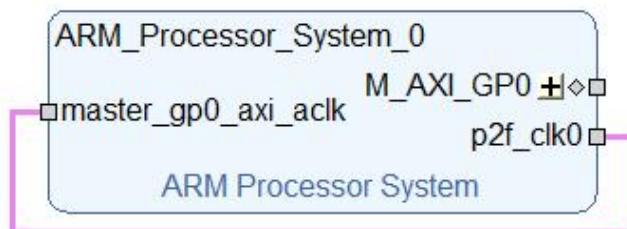

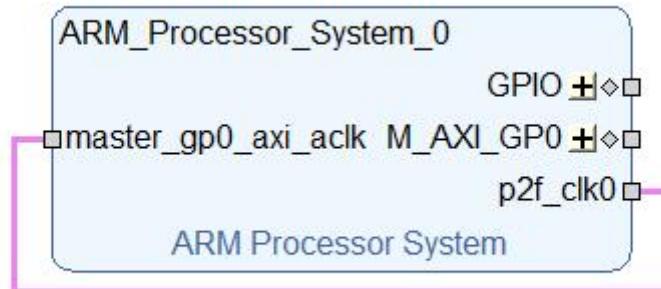

调用的 PS 端 IP

图 4-6. 调用的 ps 端 ip

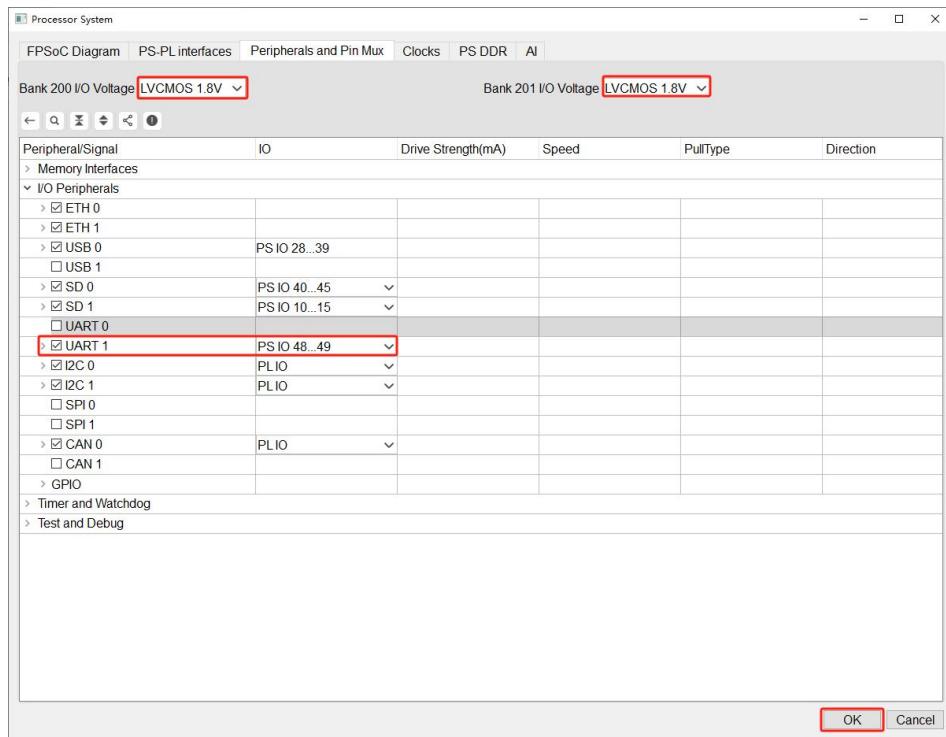

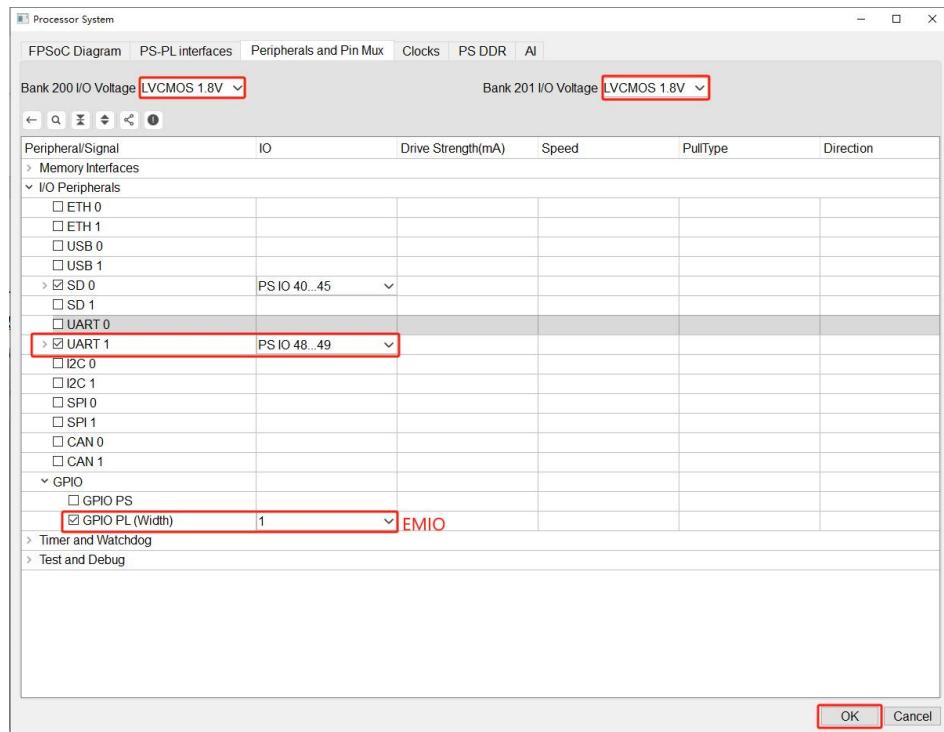

双击 IP 核，设置 PS 端的 uart 管脚为 MIO50~MIO51，Bank 电压都设置为 1.8V,然后点击 OK

图 4-7. 配置 uart 管脚

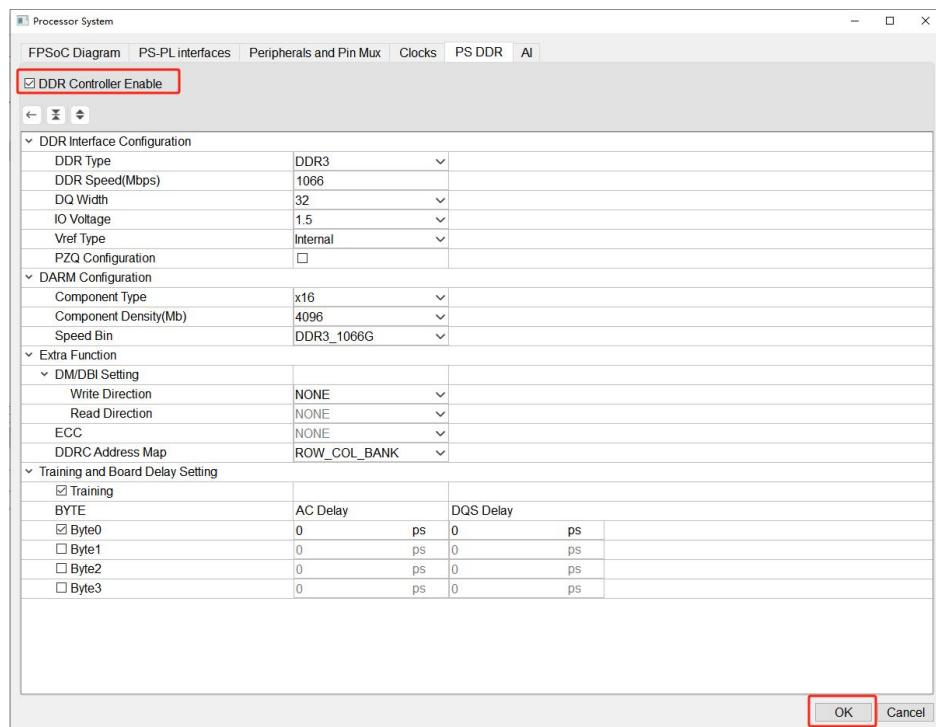

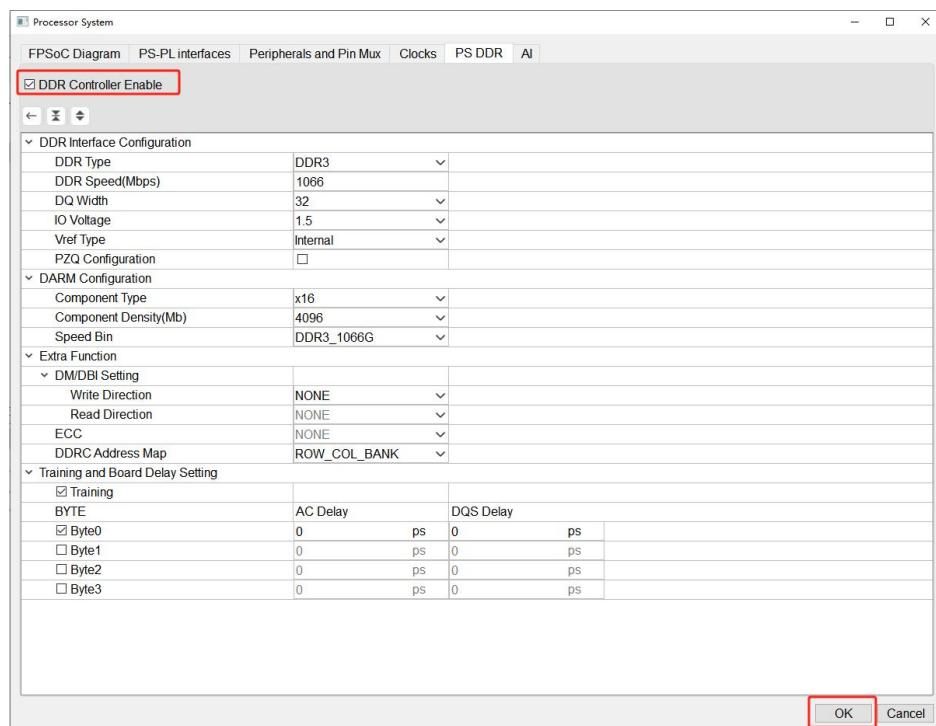

配置 DDR，勾选 DDR 使能和参考，配置完成后点击 OK

图 4-8. 配置 DDR 参数

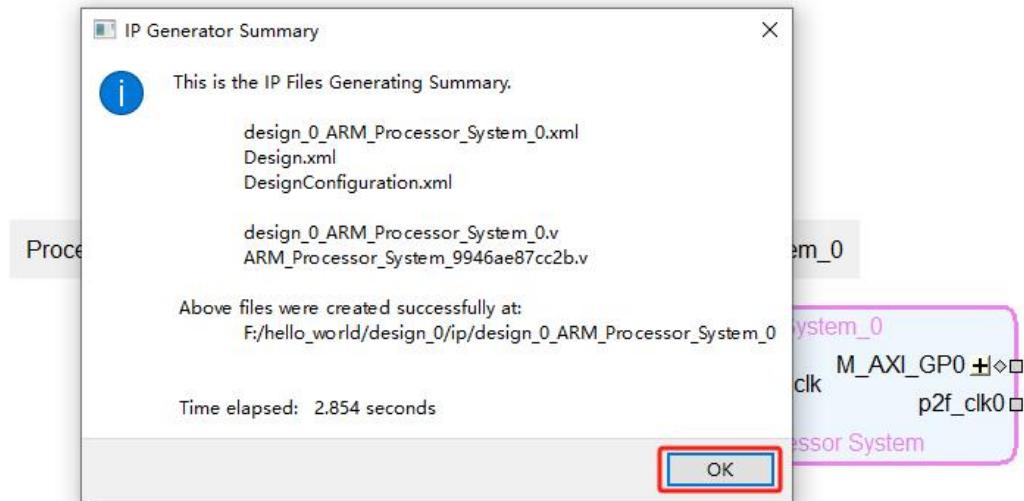

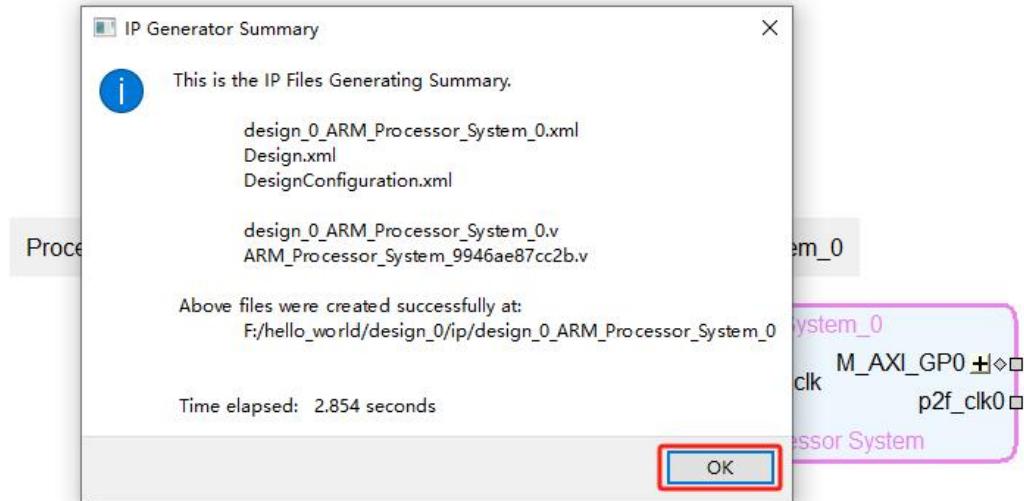

IP 核生成成功，点击 OK 关闭对话框

图 4-9. IP 核生成成功

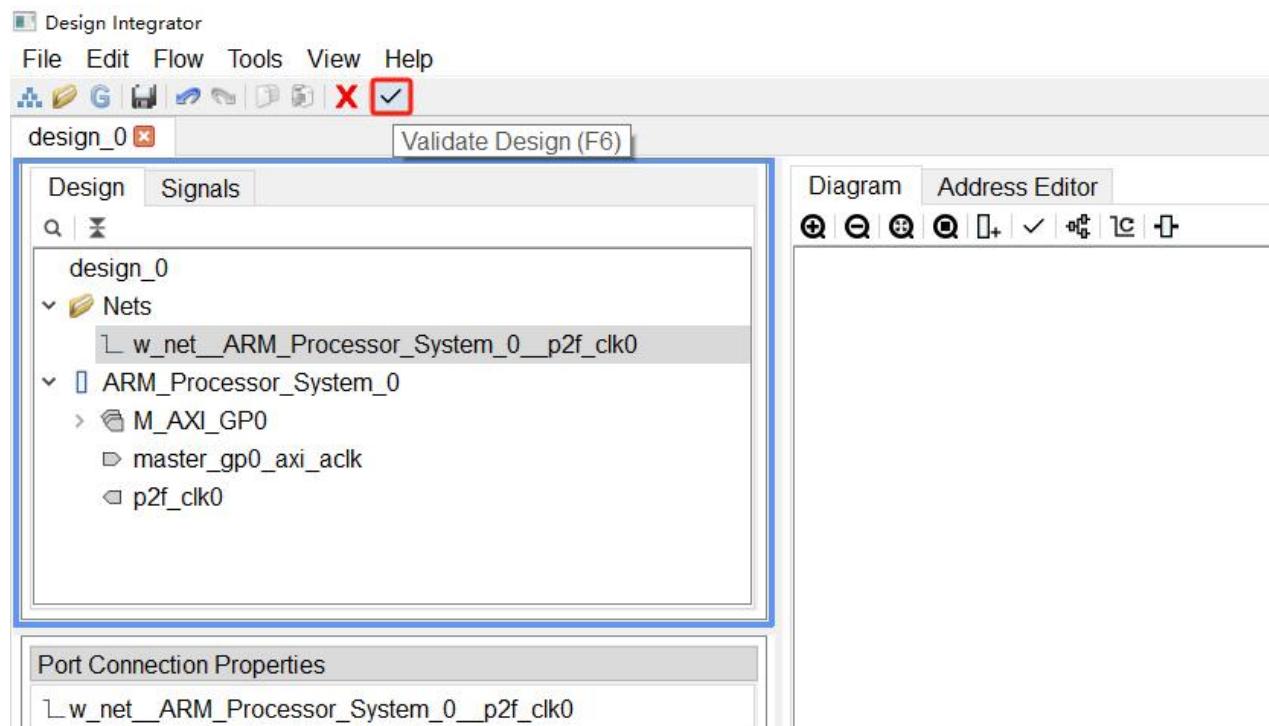

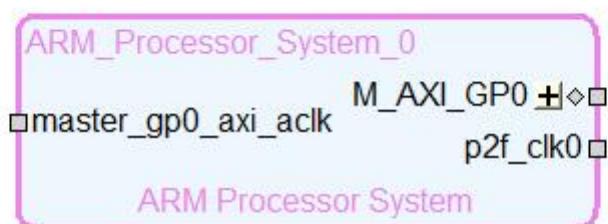

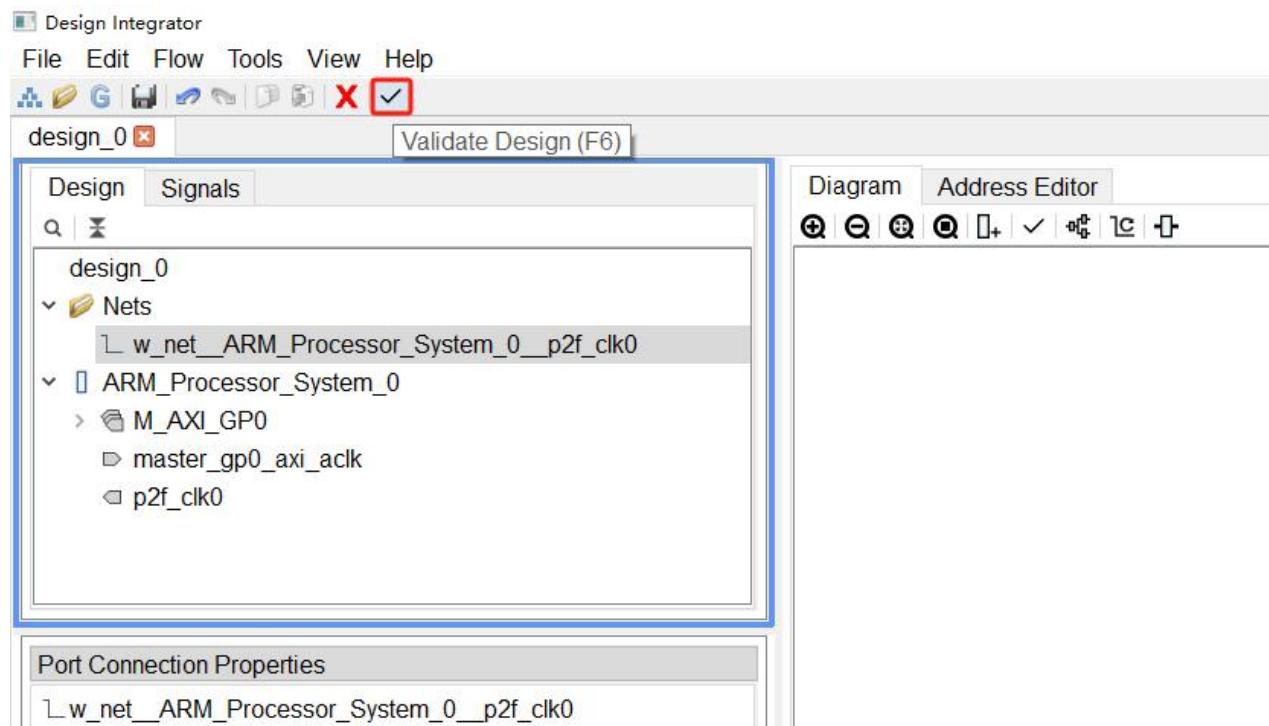

双击 p2f\_clk0 连接 master\_gp0\_axi\_aclk 管脚，因 GP 接口没有使用这里不需要引出

图 4-10 连接 GP 接口时钟管脚

点击 Validate Design 检查是否有设计上的错误

图 4-11 设计验证

#### 4.1.5. 导出 Design

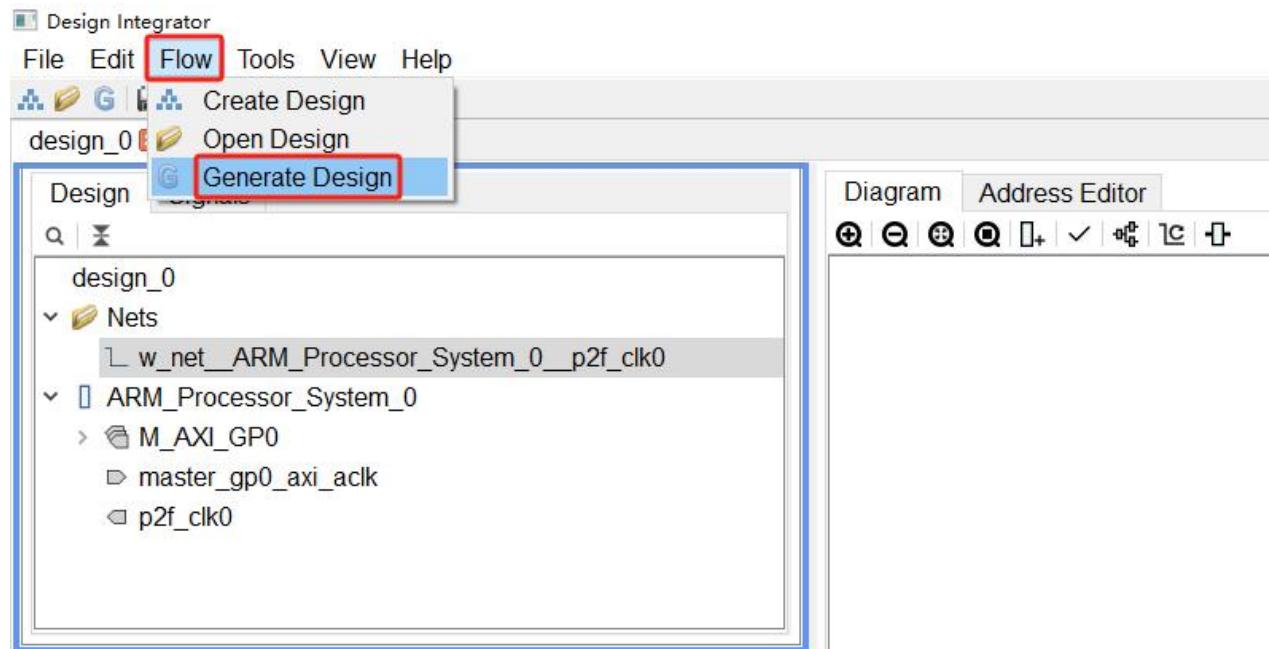

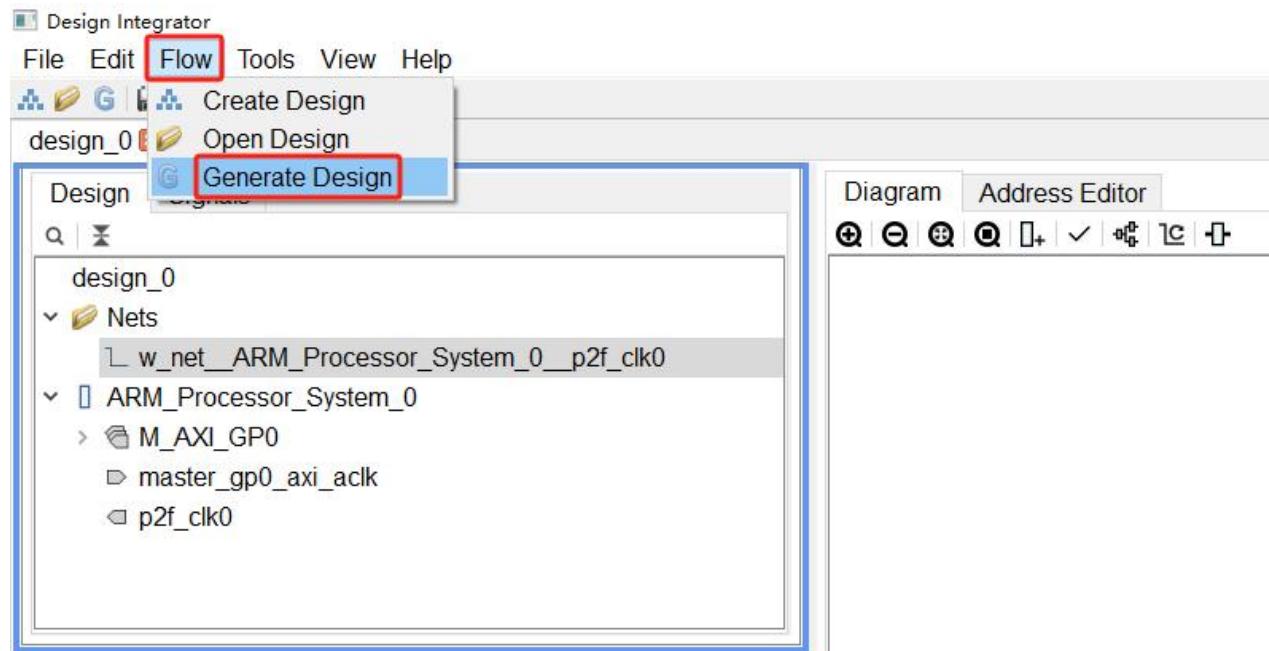

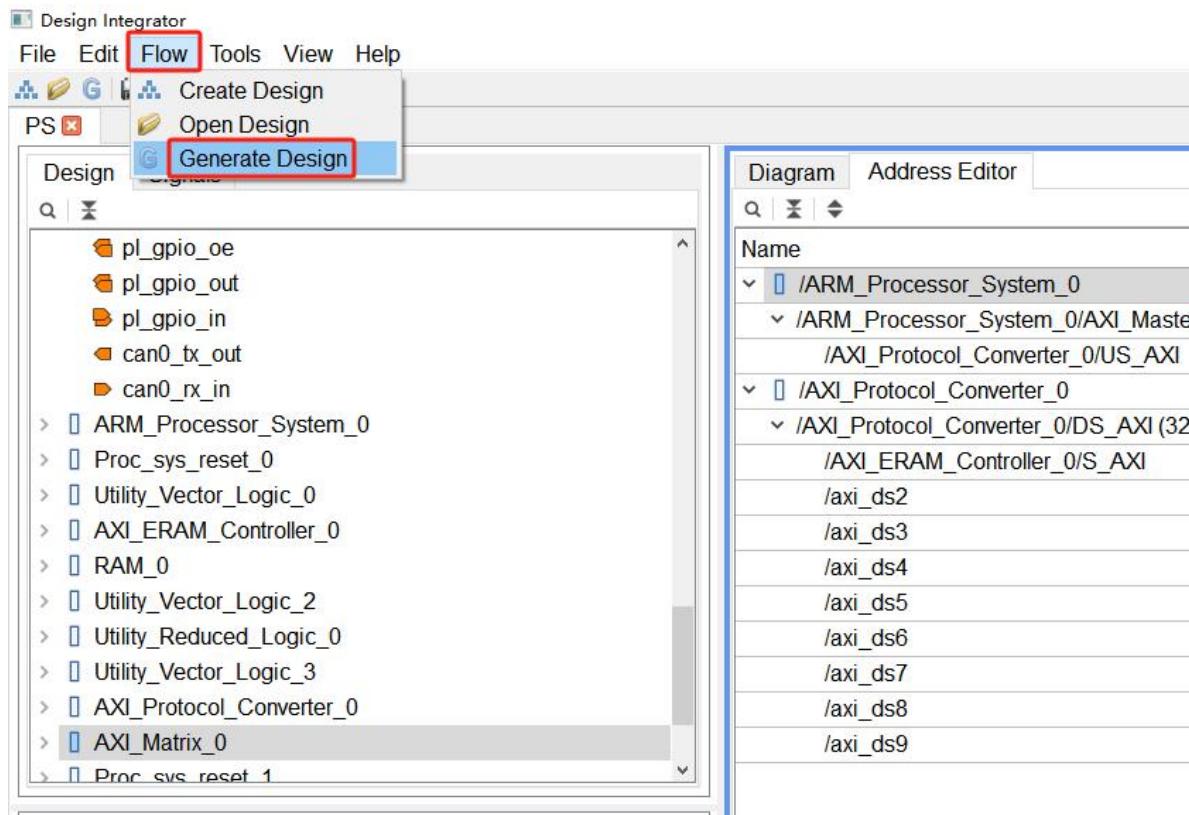

点击 Flow-->Generate Design 导出 design

图 4-12 选择导出 design 菜单

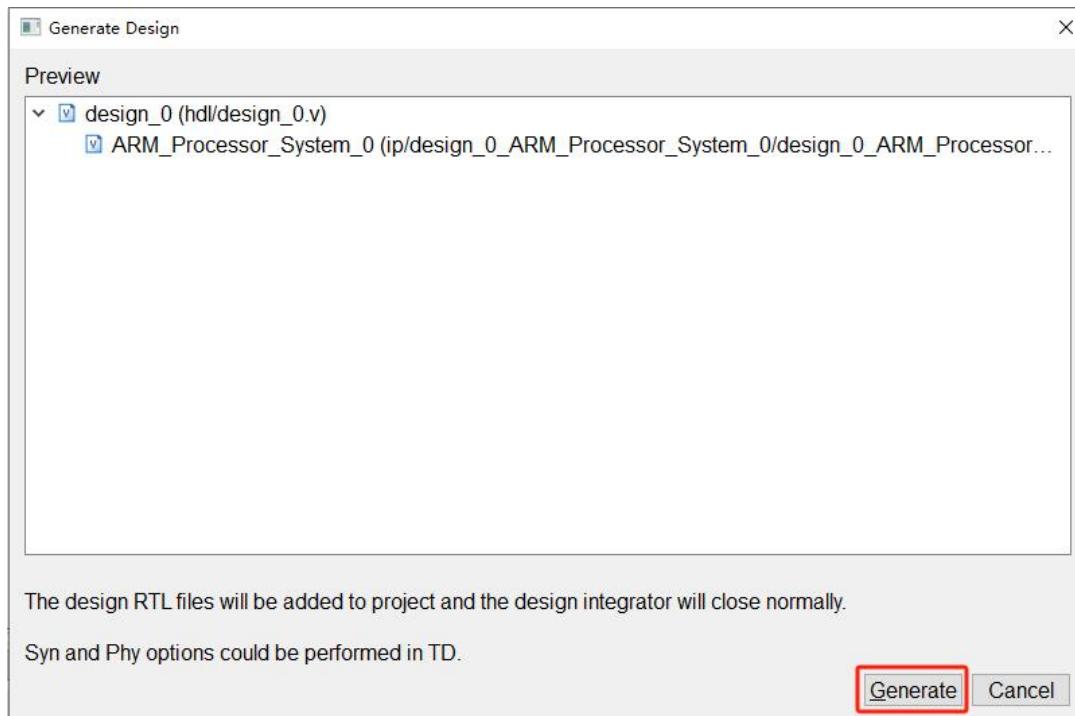

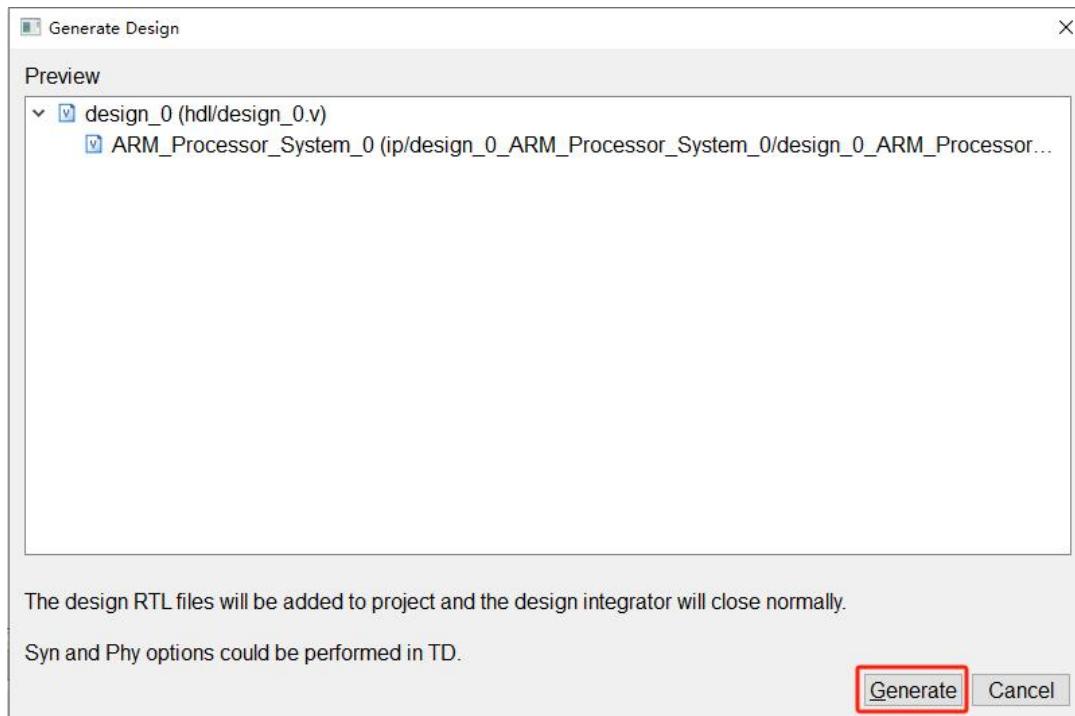

点击 Generate，导出 design 配置

图 4-13 导出 design

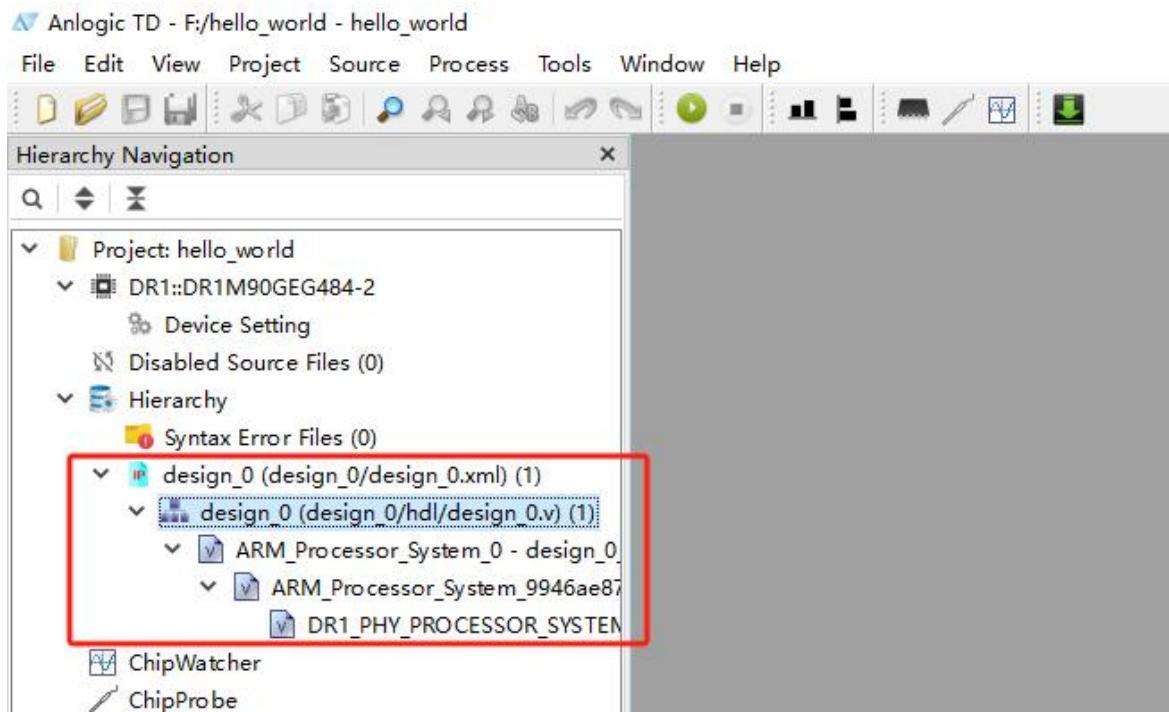

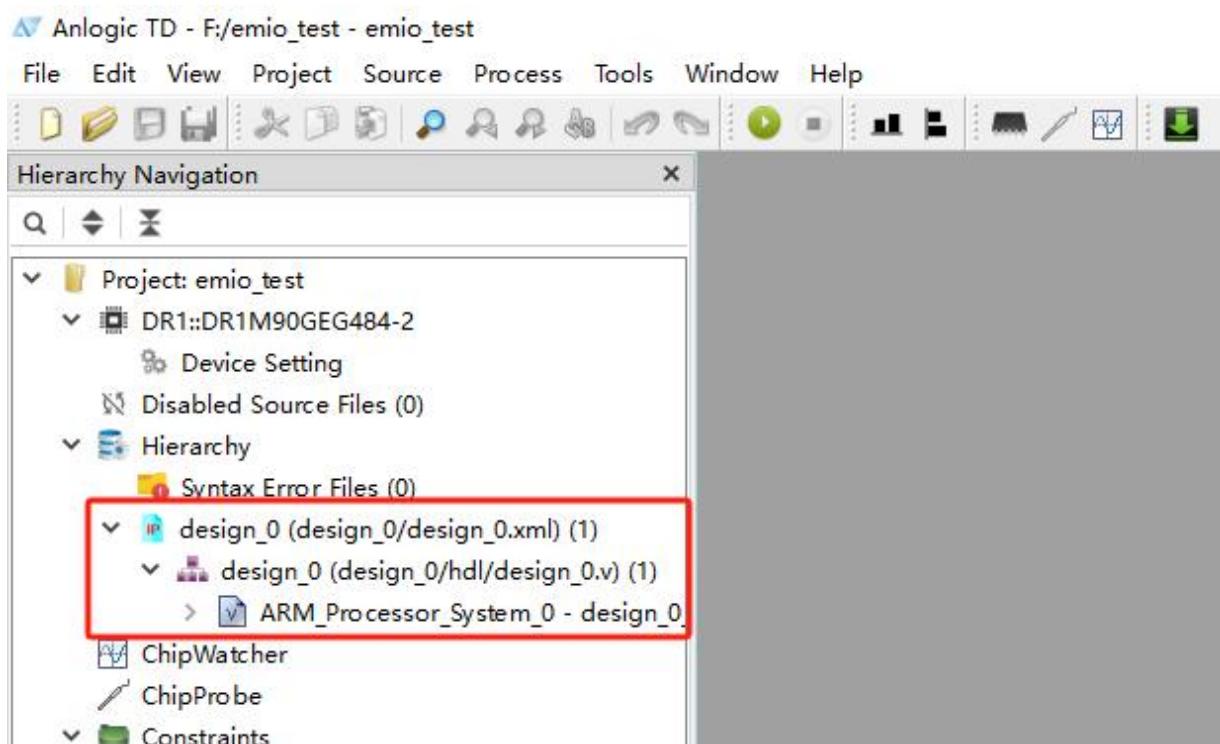

导出的 design 文件树

图 4-14 导出的 design 文件树

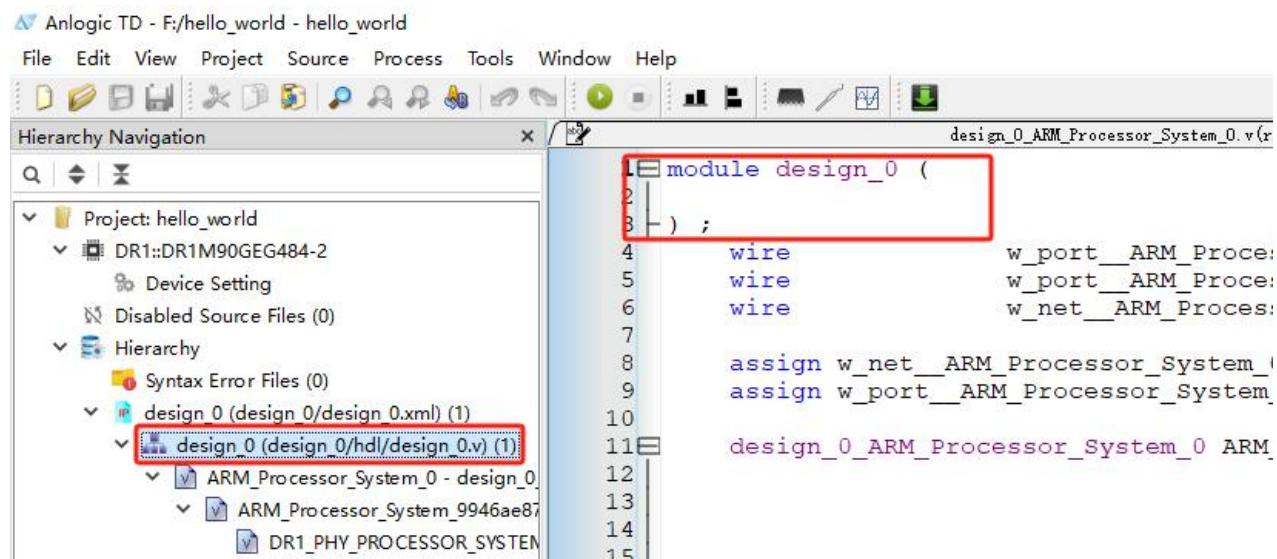

design 生成的顶层文件，如下图所示，因此工程主要使用 PS 端 ip，所以可以看到右边顶层文件没有 FPGA 管脚输出口

```

1 module design_0 (

2   );

3   wire;

4   wire;

5   wire;

6   assign w_net_ARM_Processor_System_0 = w_port_ARM_Processor_System;

7   assign w_port_ARM_Processor_System = w_net_ARM_Processor_System;

8   design_0_ARM_Processor_System_0 ARM;

9

10

11

12

13

14

15

```

图 4-15 生成的 design 模块顶层文件

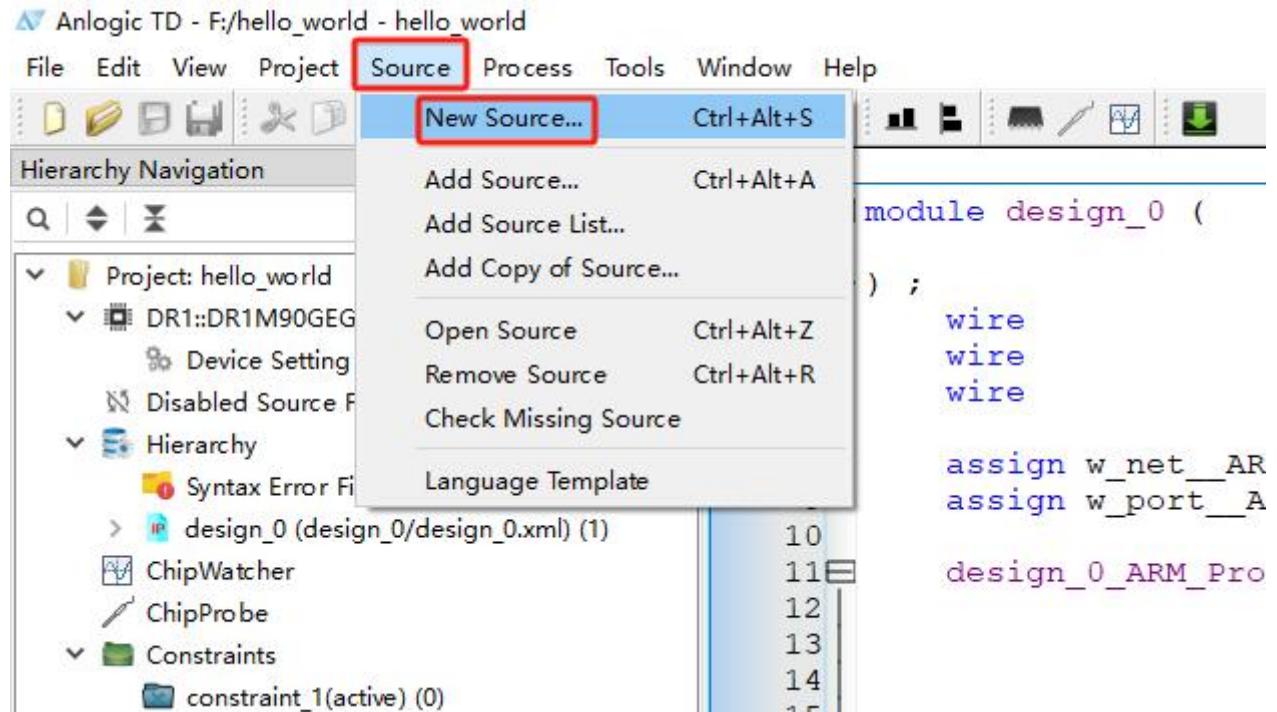

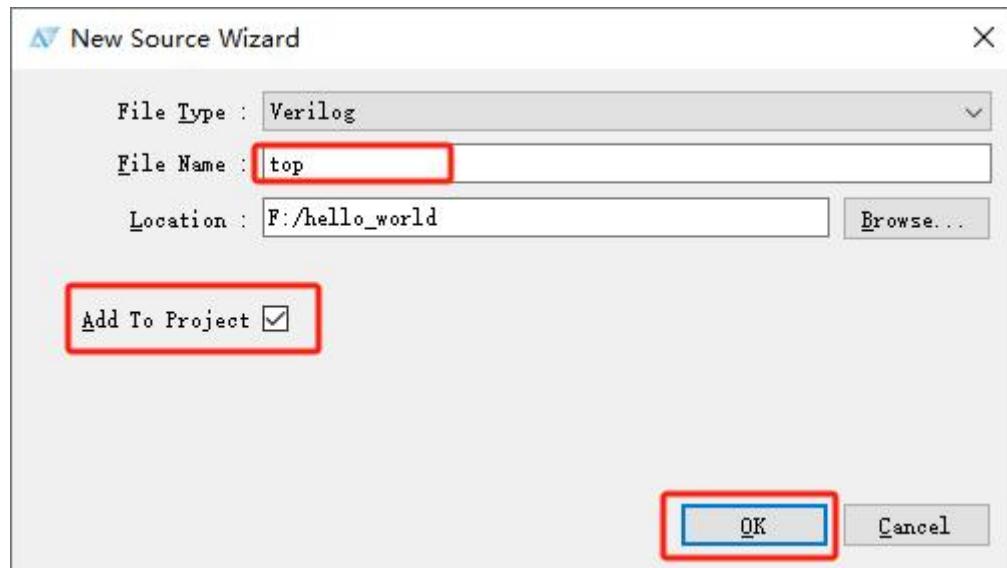

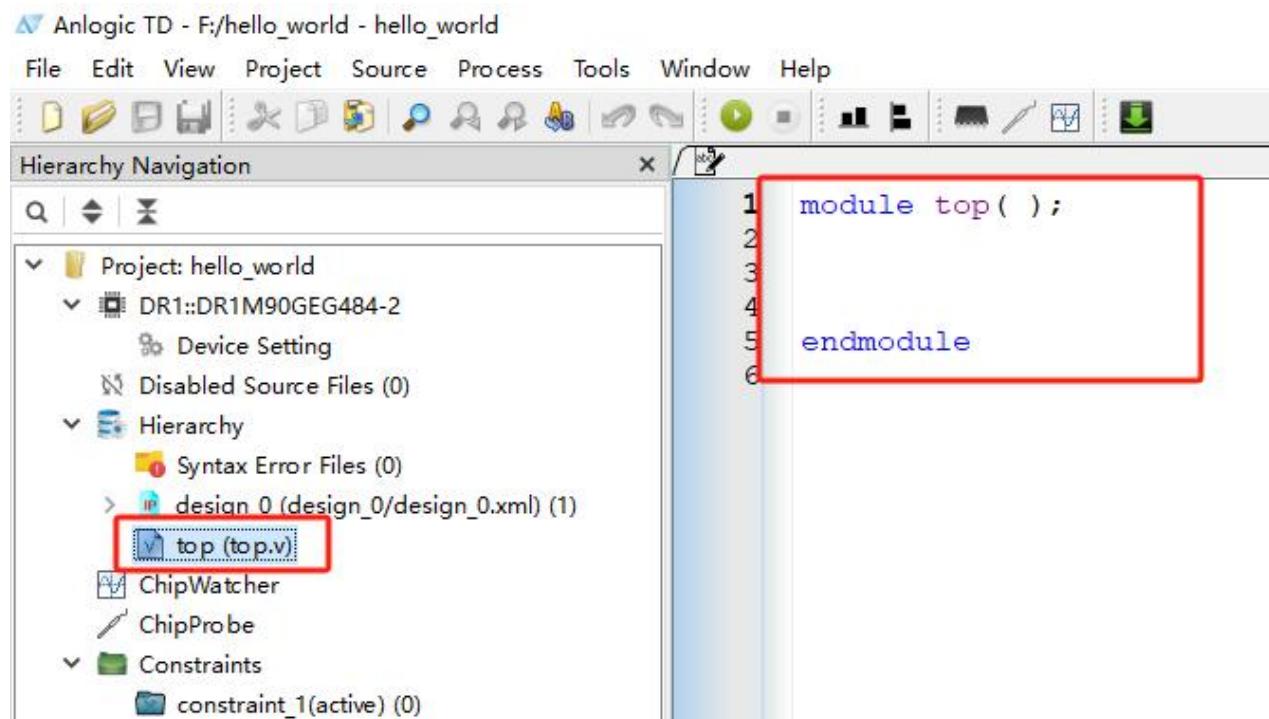

#### 4.1.6. 新建 FPGA 顶层文件

点击 Source-->New Source, 新建 FPGA 文件

图 4-16 新建 FPGA 顶层文件

设置顶层文件名为 top，加入到工程里，然后点击 OK

图 4-17 设置顶层文件

生成的顶层文件 top，如下图所示

图 4-18 生成顶层文件 top

将 design 顶层例化到 FPGA 顶层文件里，因 PS 模块没有管脚输出，所以这里的 FPGA 顶层和 PS 端顶层都是空的

```

1 module top();

2

3 //ps_demo

4 design_0 design_0_inst(

5

6 );

7

8 endmodule

9

```

图 4-19 例化 PS 模块

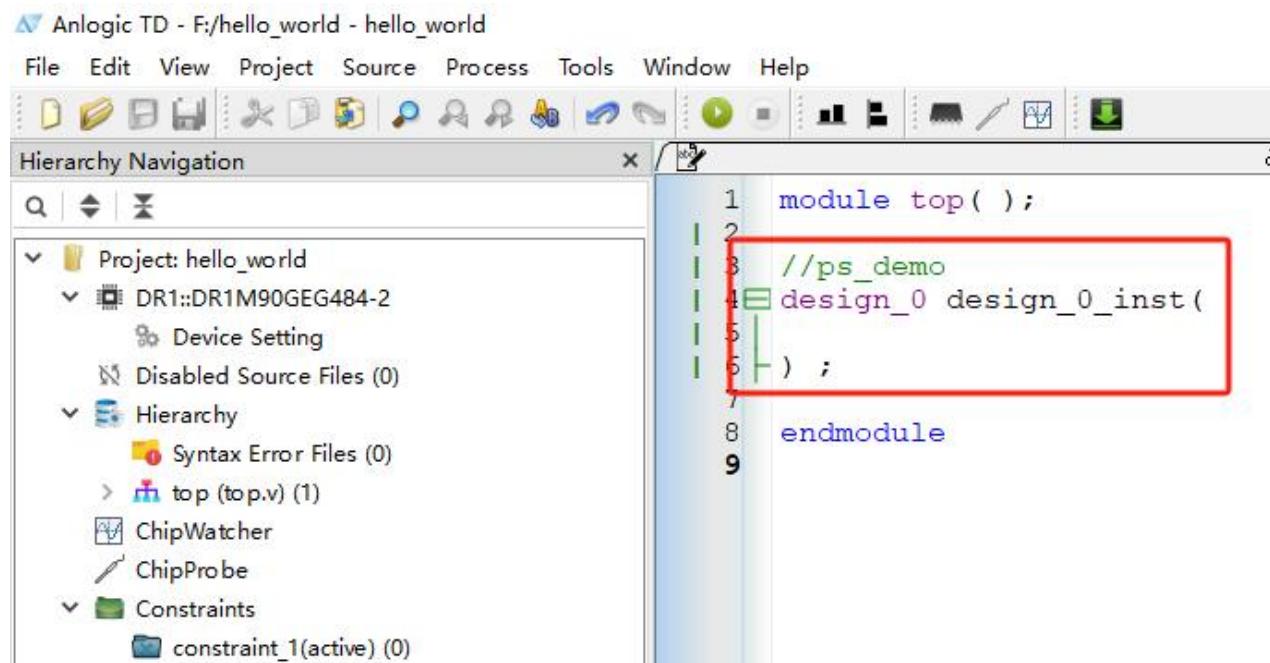

#### 4.1.7. 编译 FPGA 工程

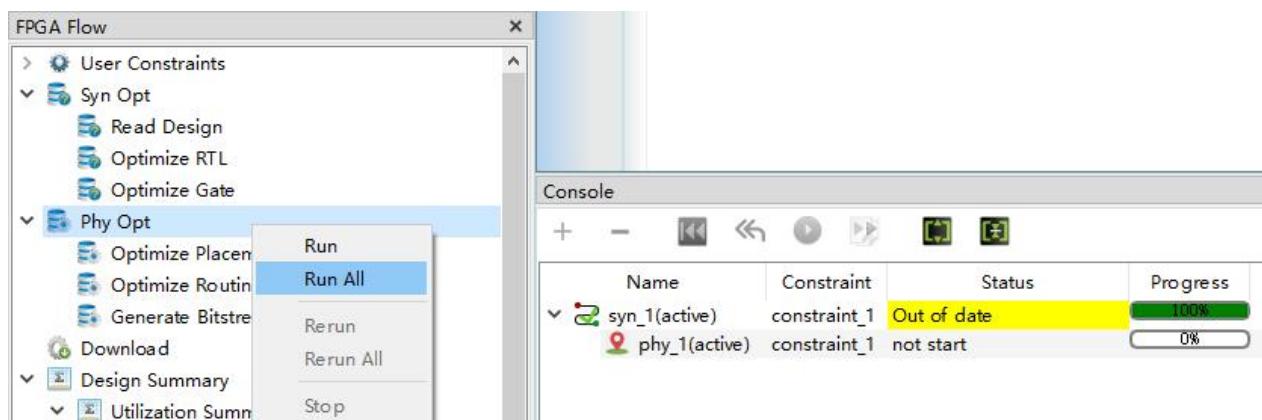

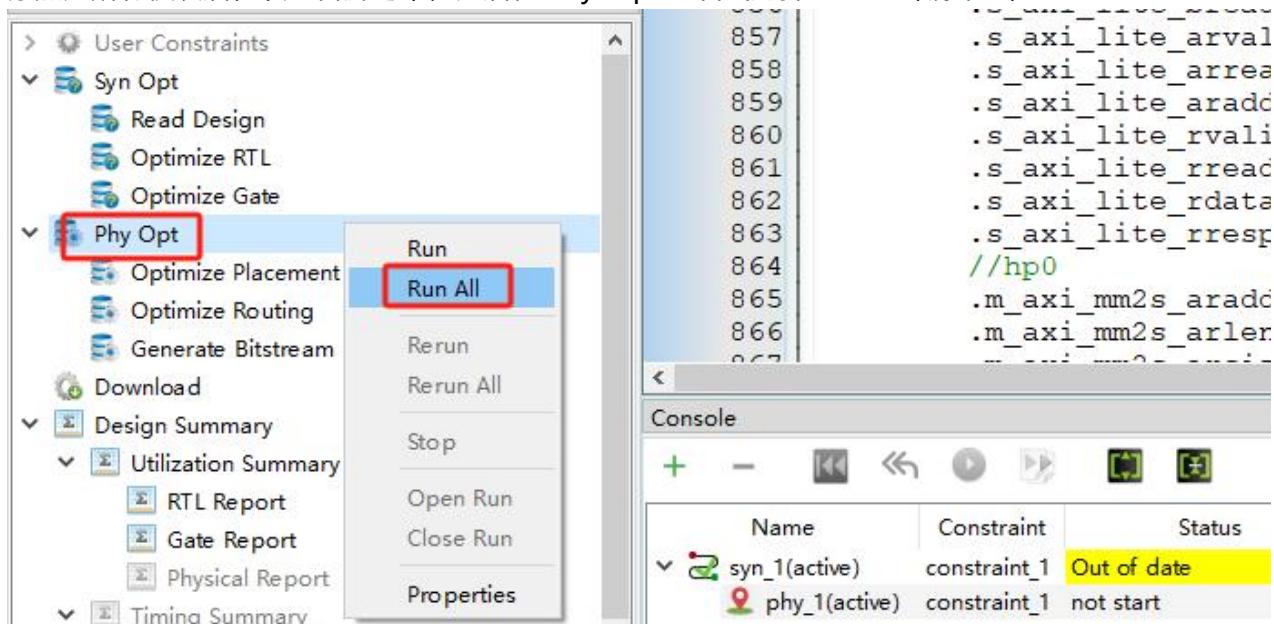

在 Phy Opt 上右击选择 Run All 编译整个工程

图 4-20 编译工程

FPGA 工程编译完成

图 4-21 工程编译完成

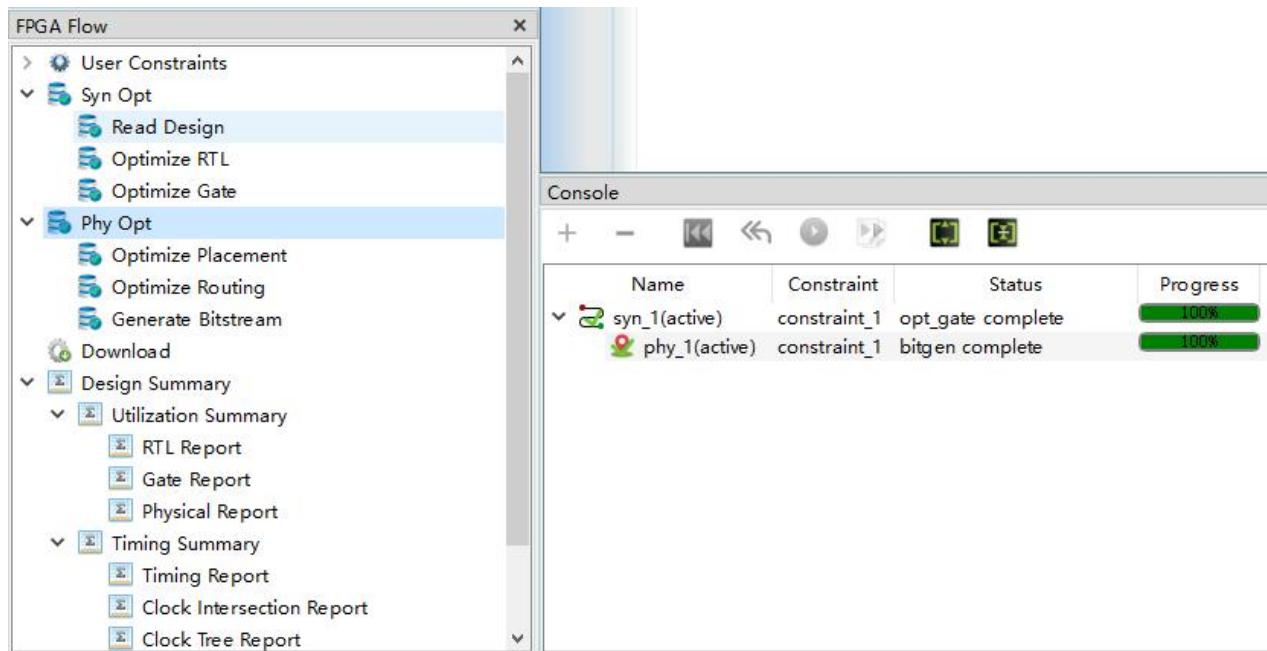

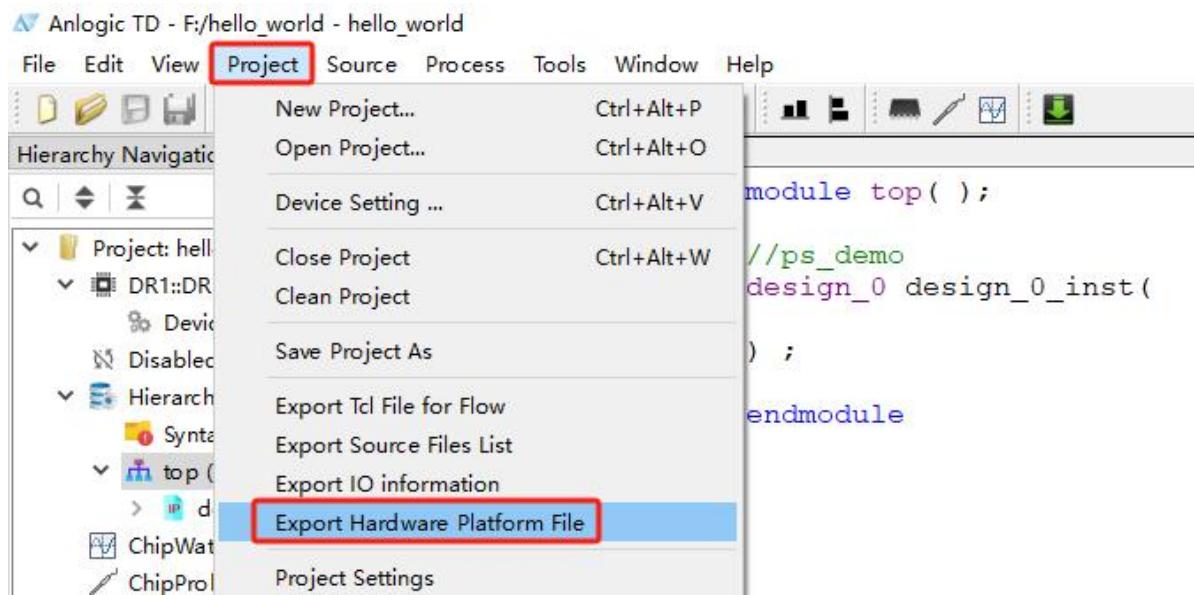

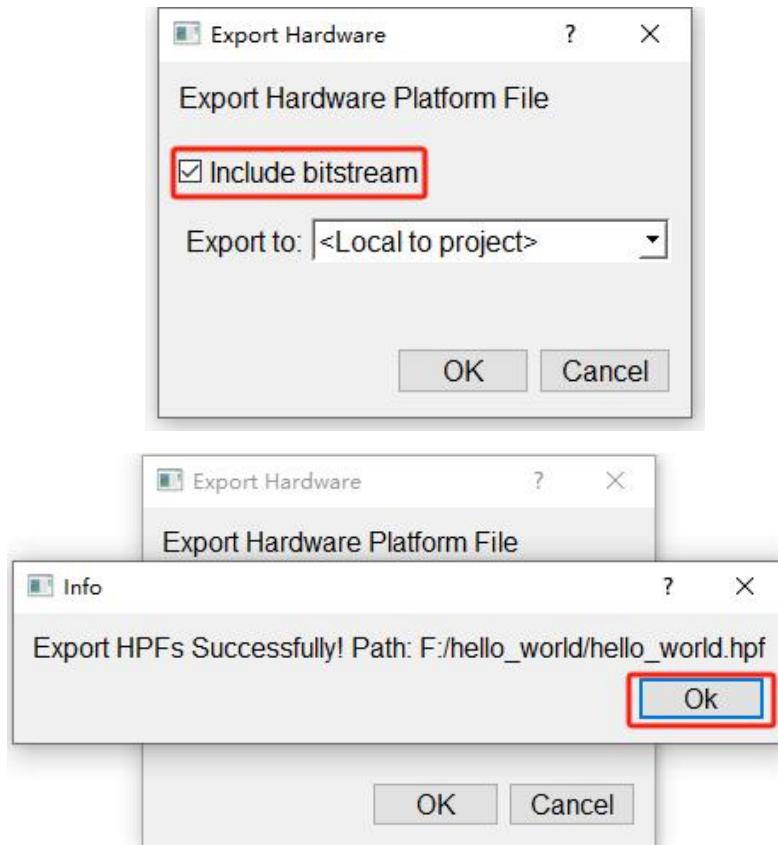

#### 4.1.8. 导出 HPF 工程

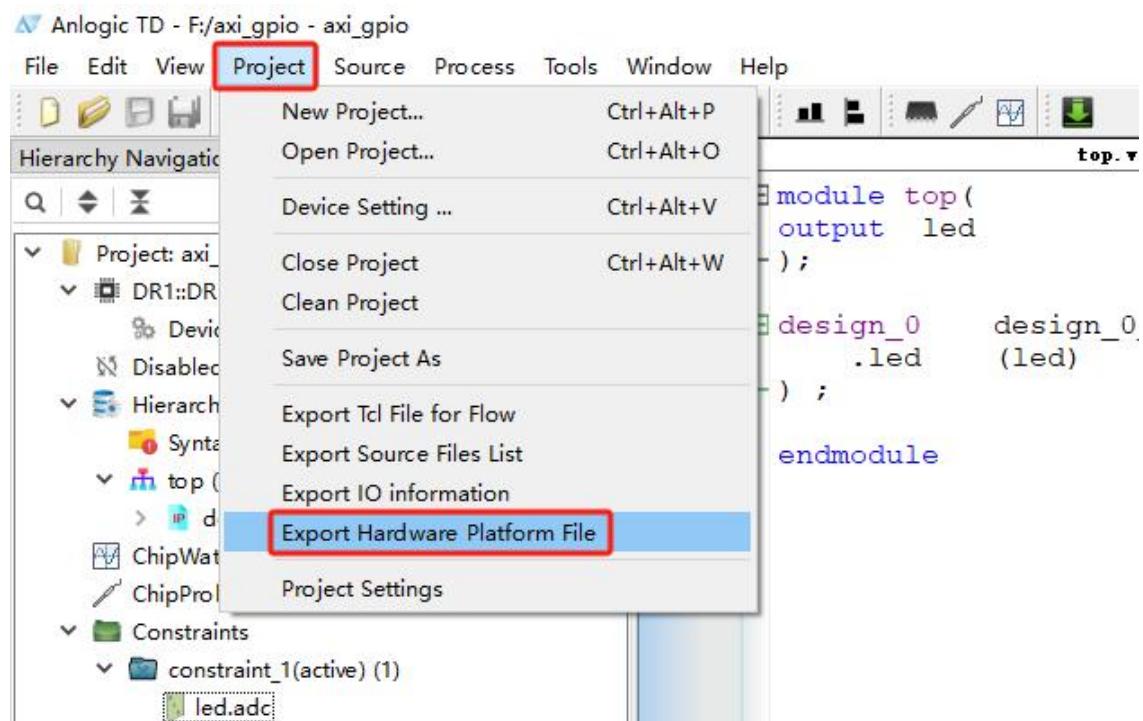

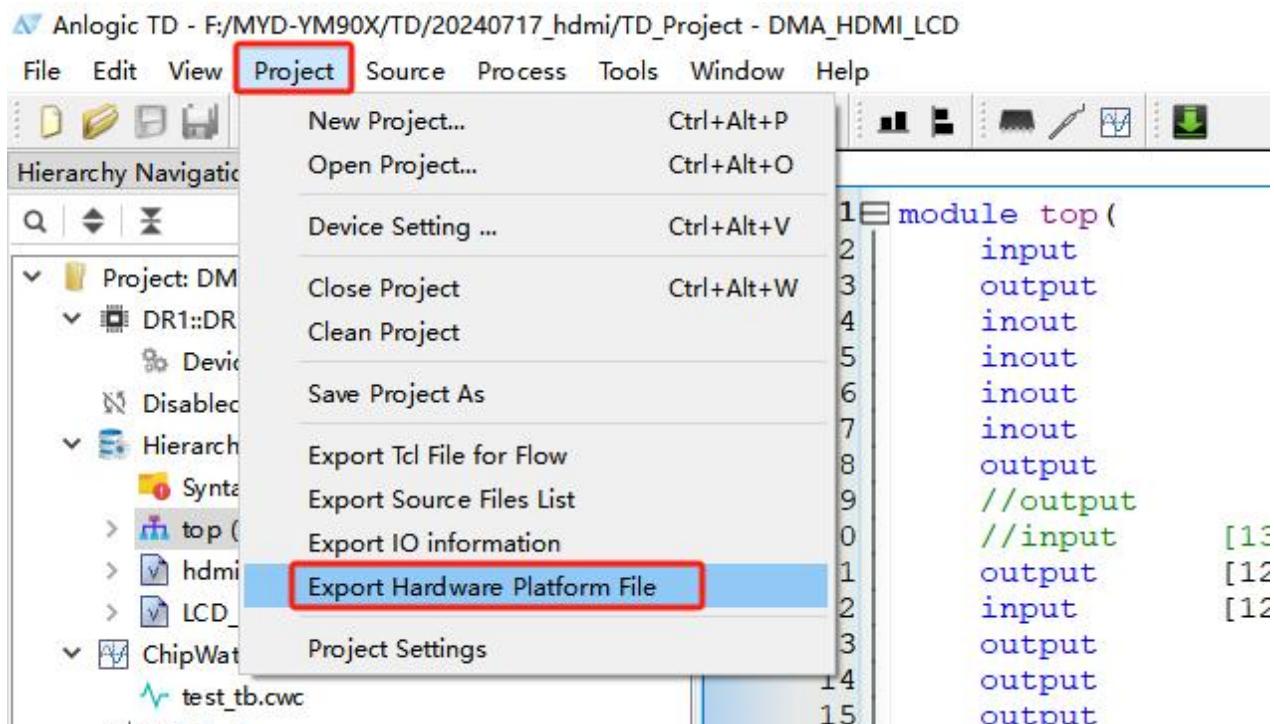

点击 Project-->Export Hardware Platform File 导出 hpf 文件

图 4-22 导出 hpf 文件

勾选 Include bitstream，表示输出的 hpf 文件包含 bit 文件，点击 OK

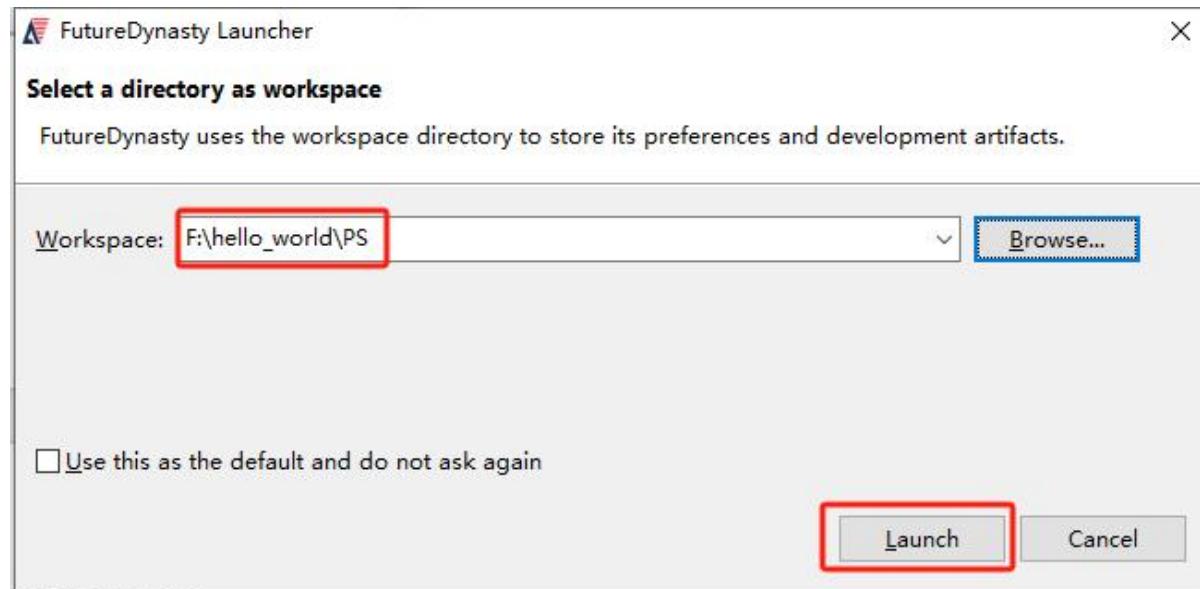

#### 4.1.9. 新建 BSP 工程

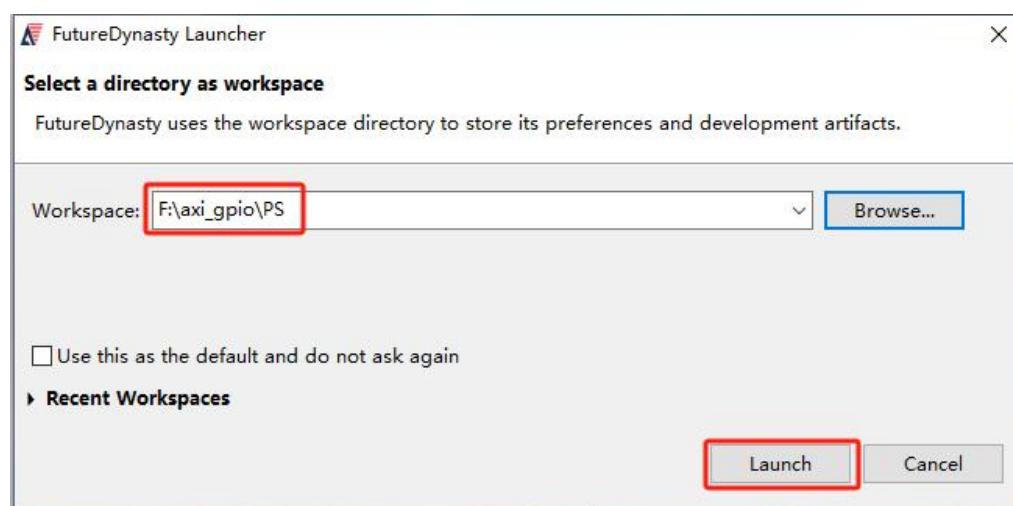

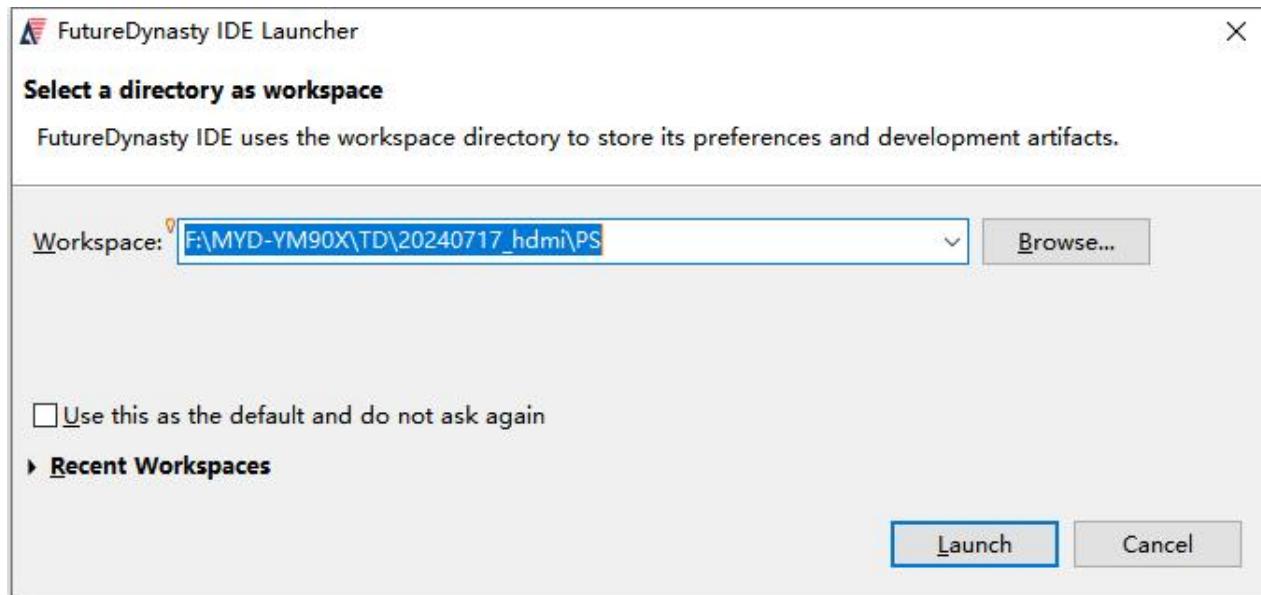

在 hello\_world 工程新建一个 PS 文件夹，将 FD 工程保存指向 PS 文件夹，然后点击 Launch

图 4-23 打开 FD 软件

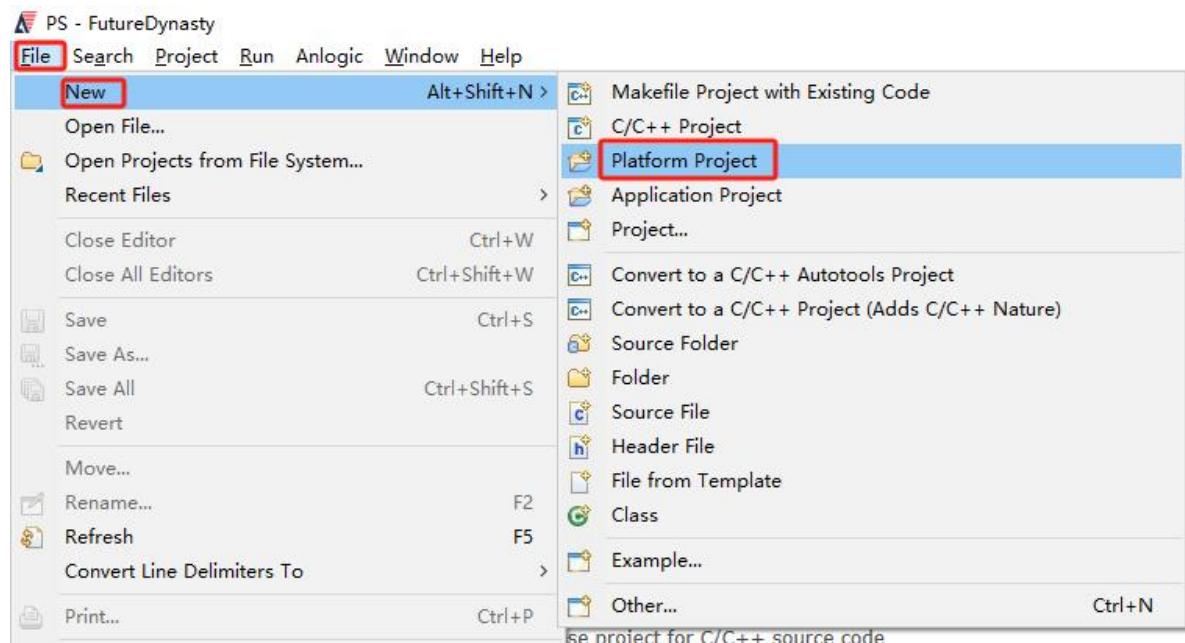

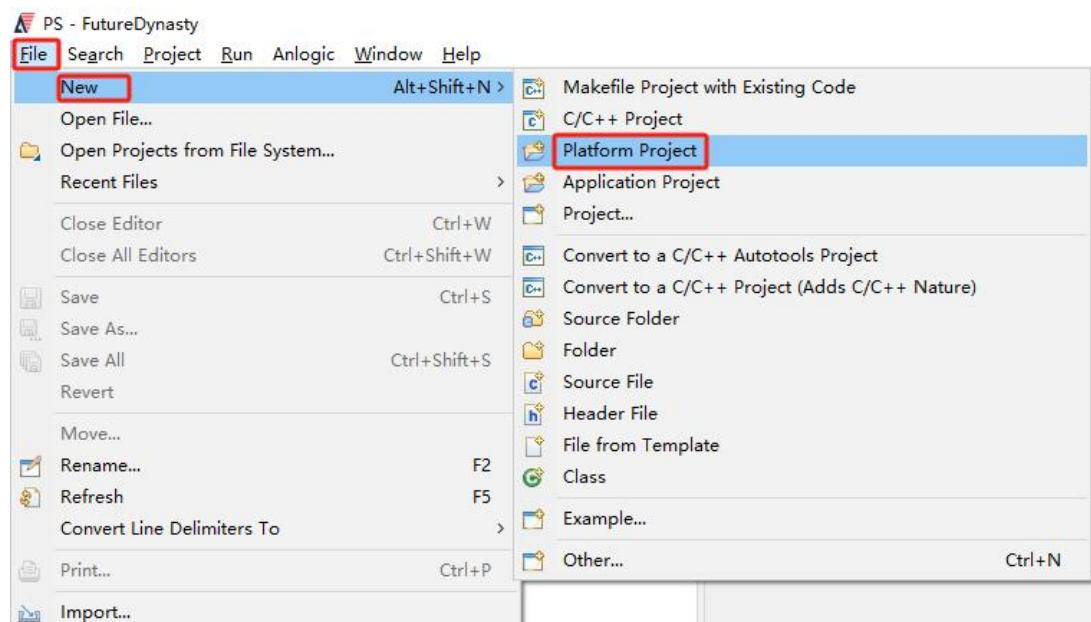

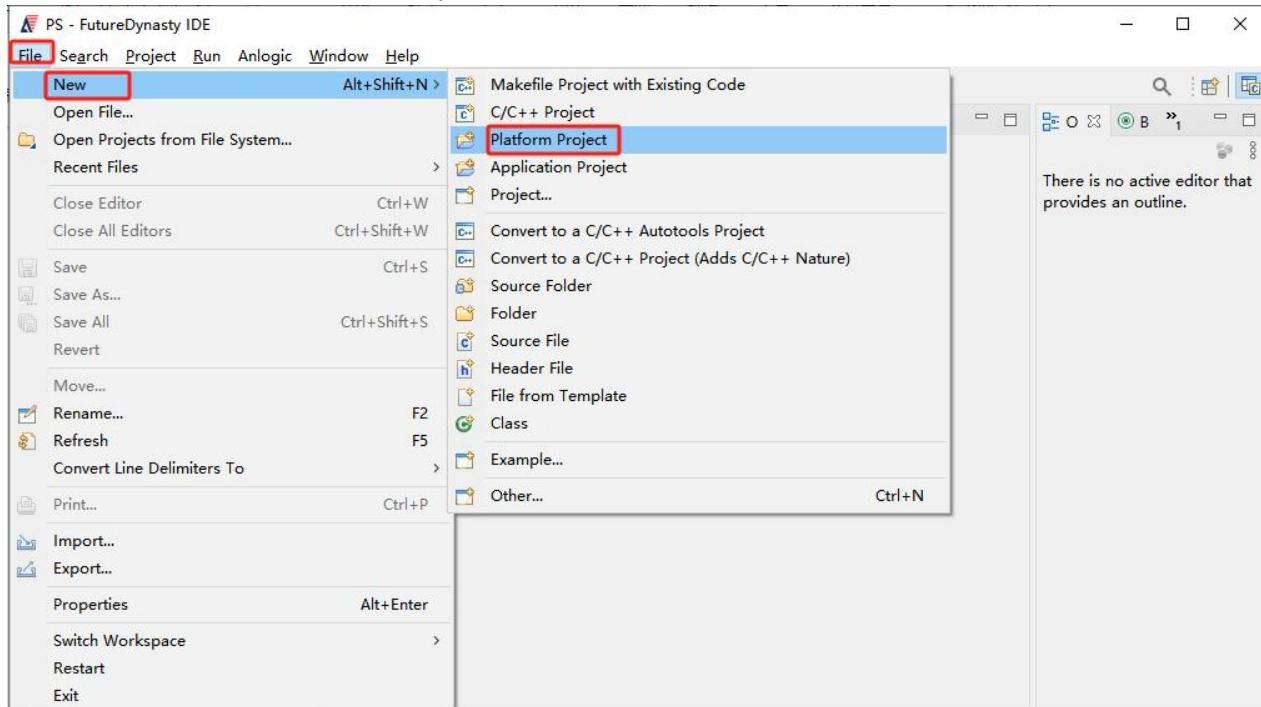

点击 File-->New-->Platform Project 新建 bsp

图 4-24 新建 BSP

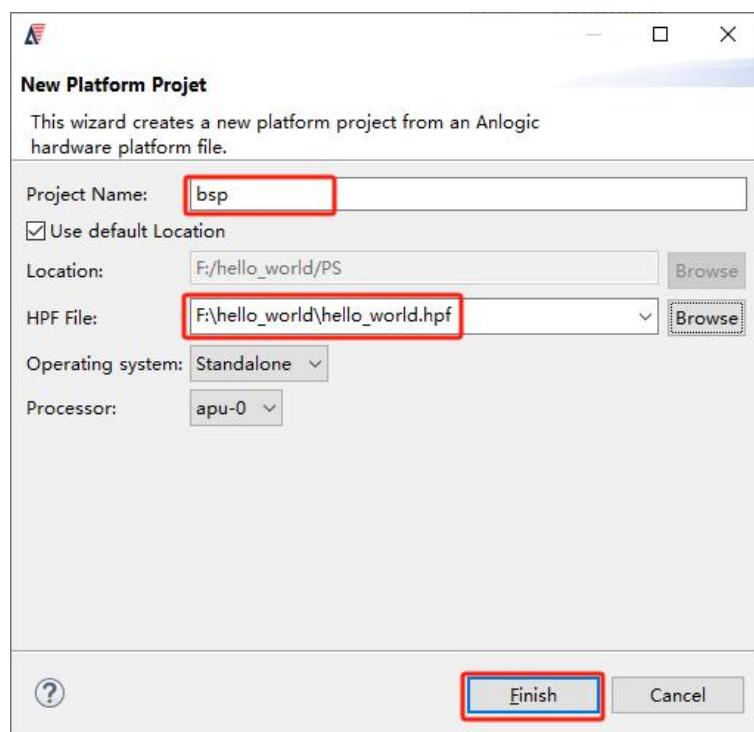

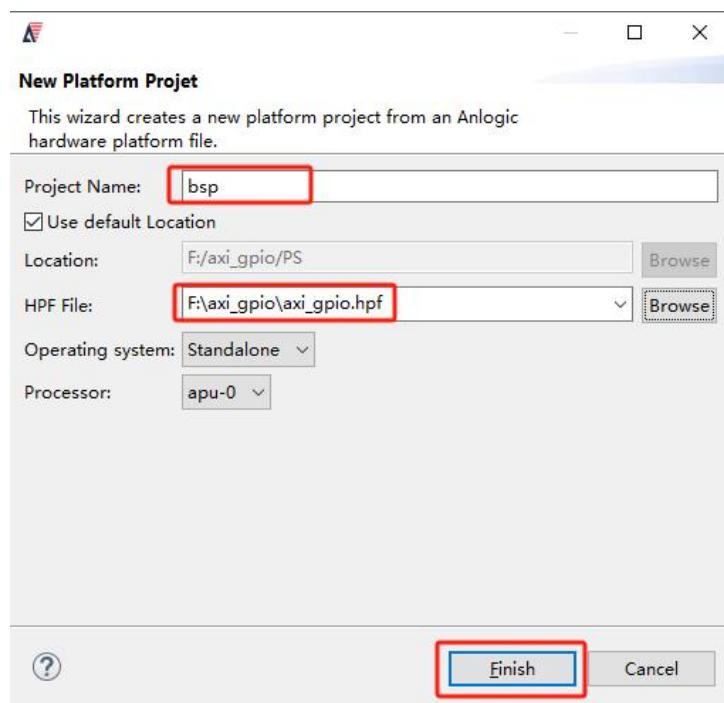

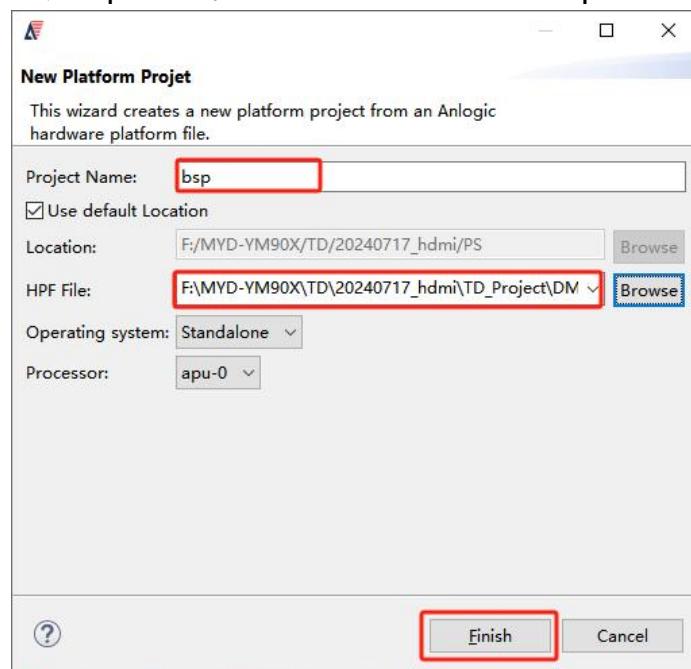

填写工程名 bsp，添加 hpf 文件，然后点击 Finish

图 4-25 BSP 文件设置

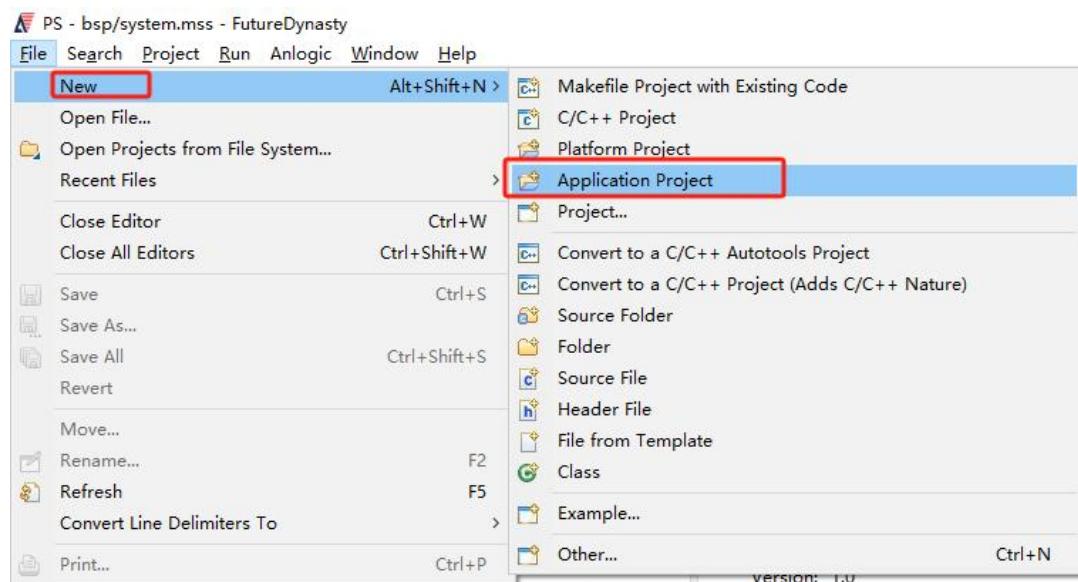

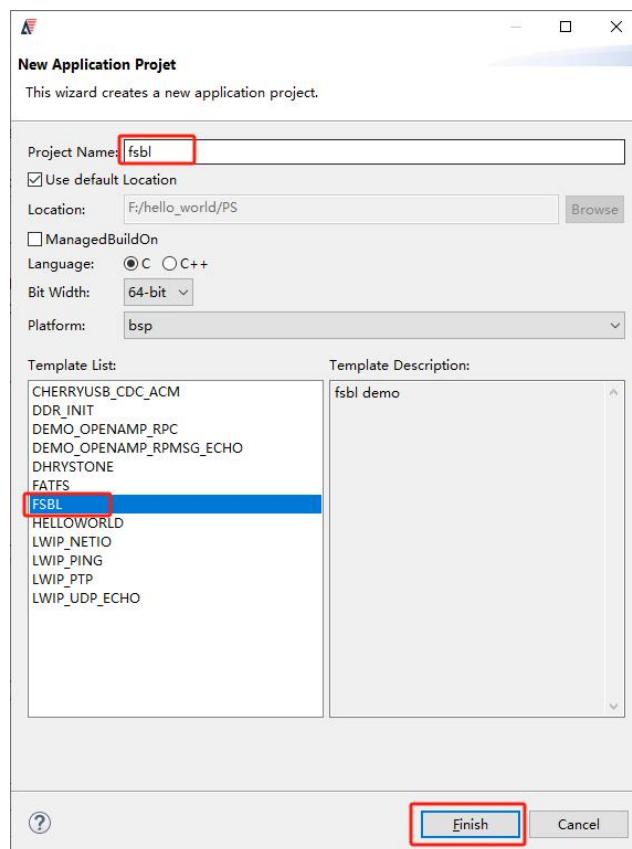

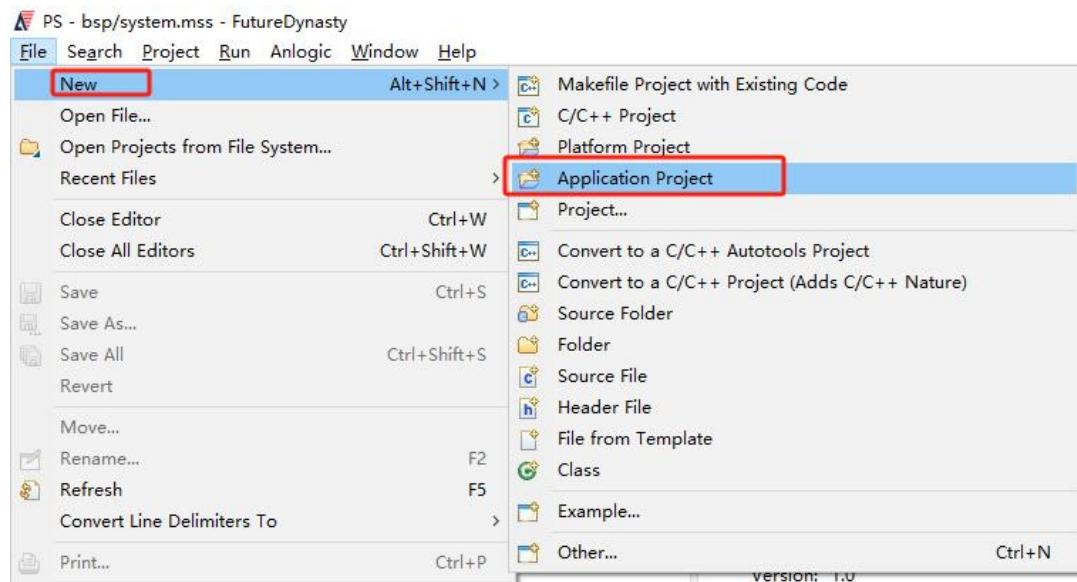

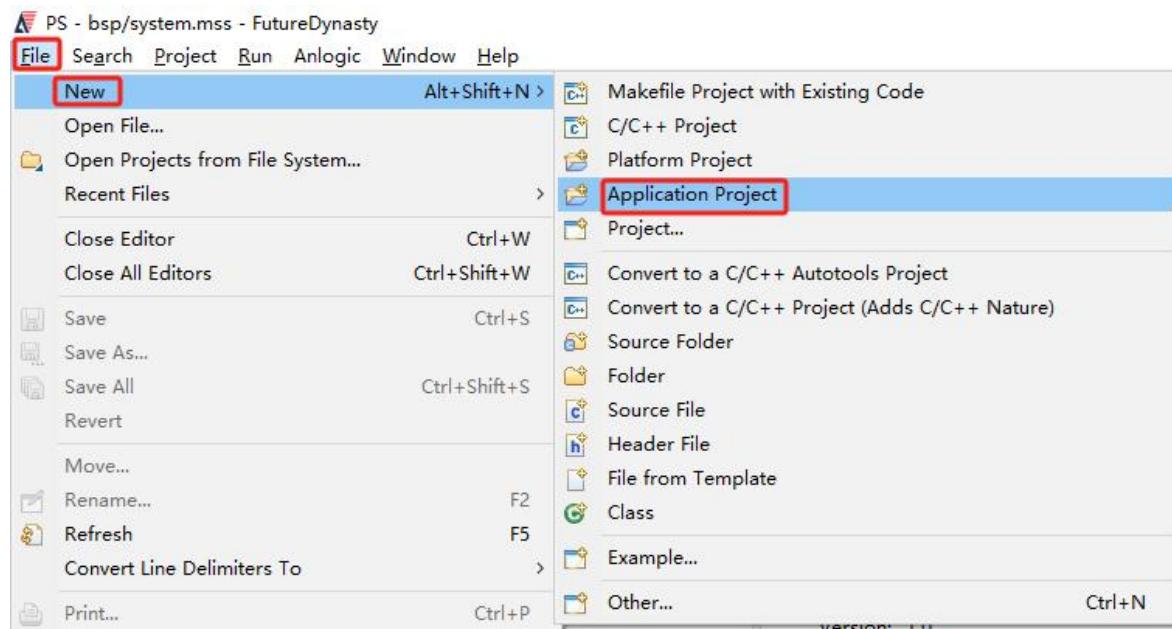

选择 File-->New-->Application Project 新建 fsbl 文件

图 4-26 新建 fsbl

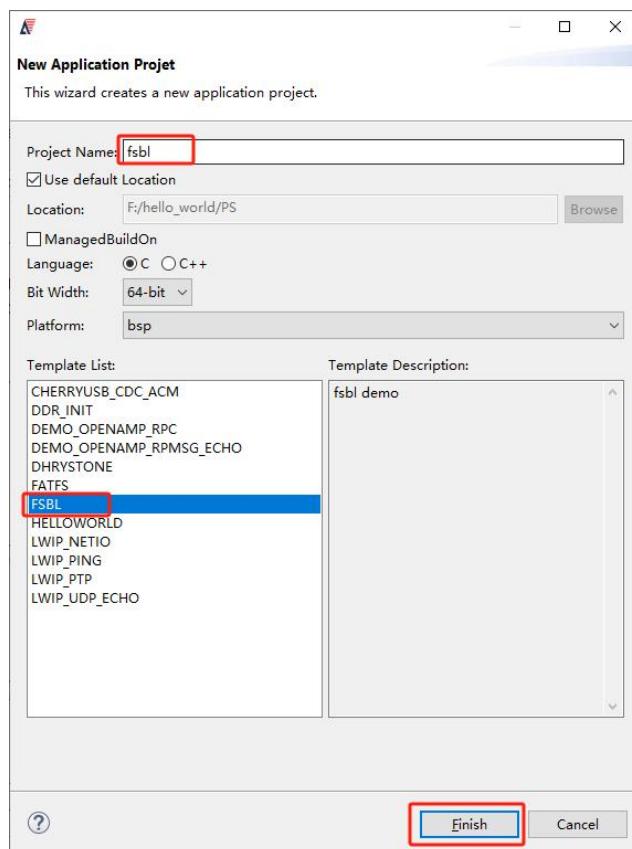

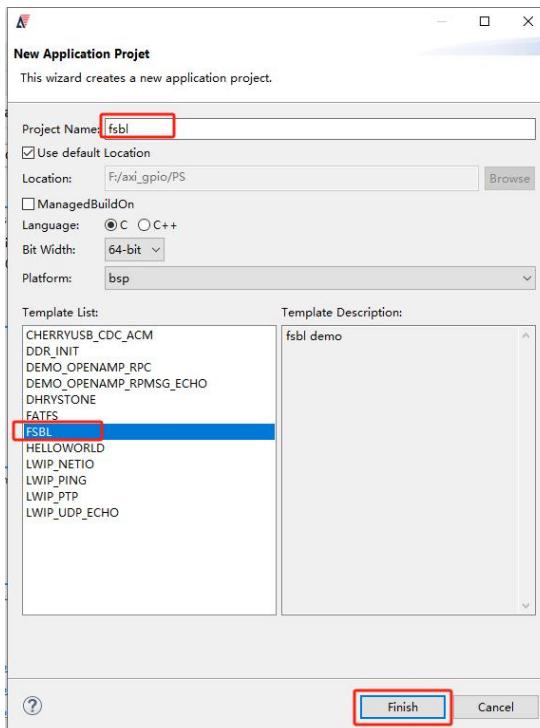

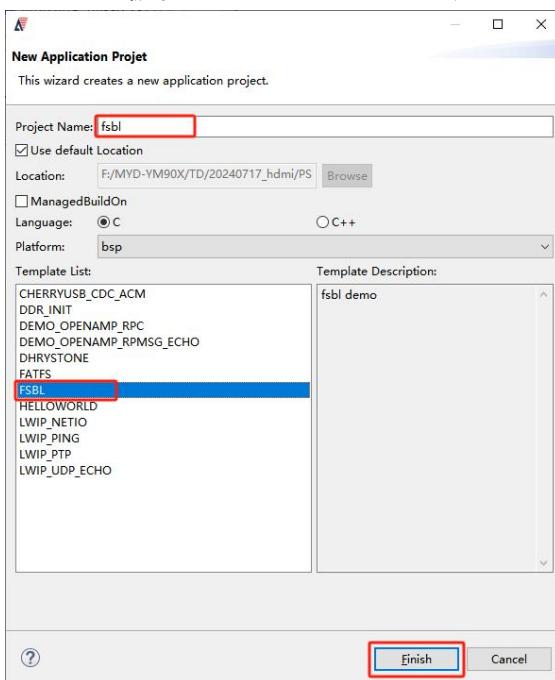

填写工程名为 fsbl,选择 FSBL 模板, 然后点击 Finish

图 4-27 生成 fsbl

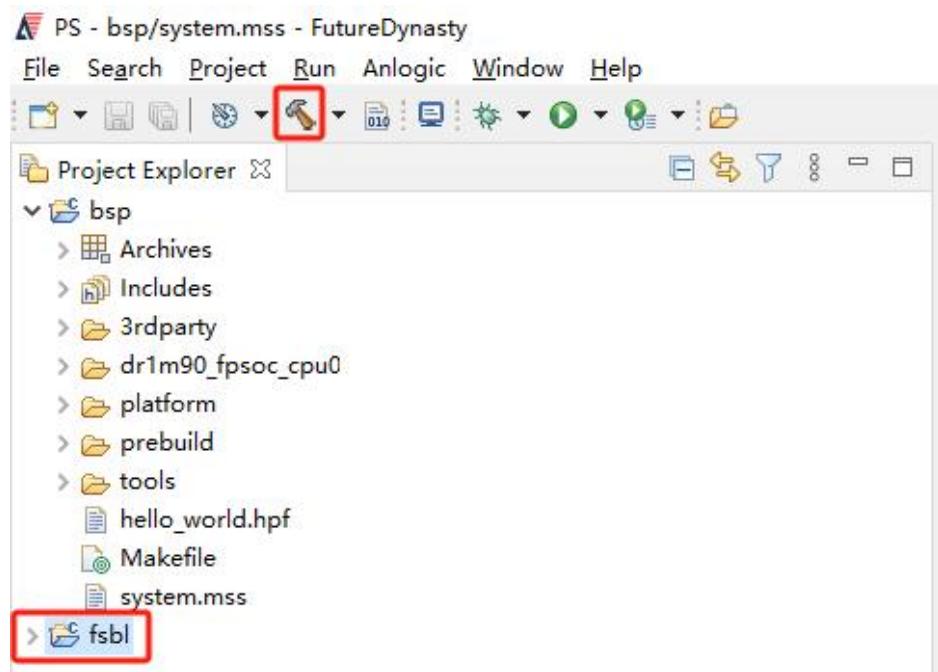

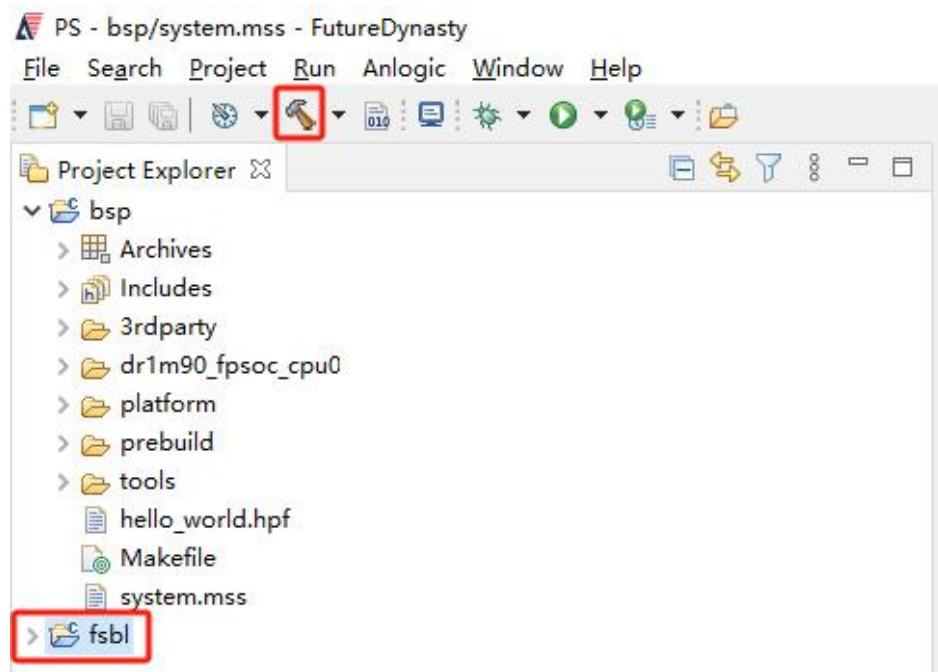

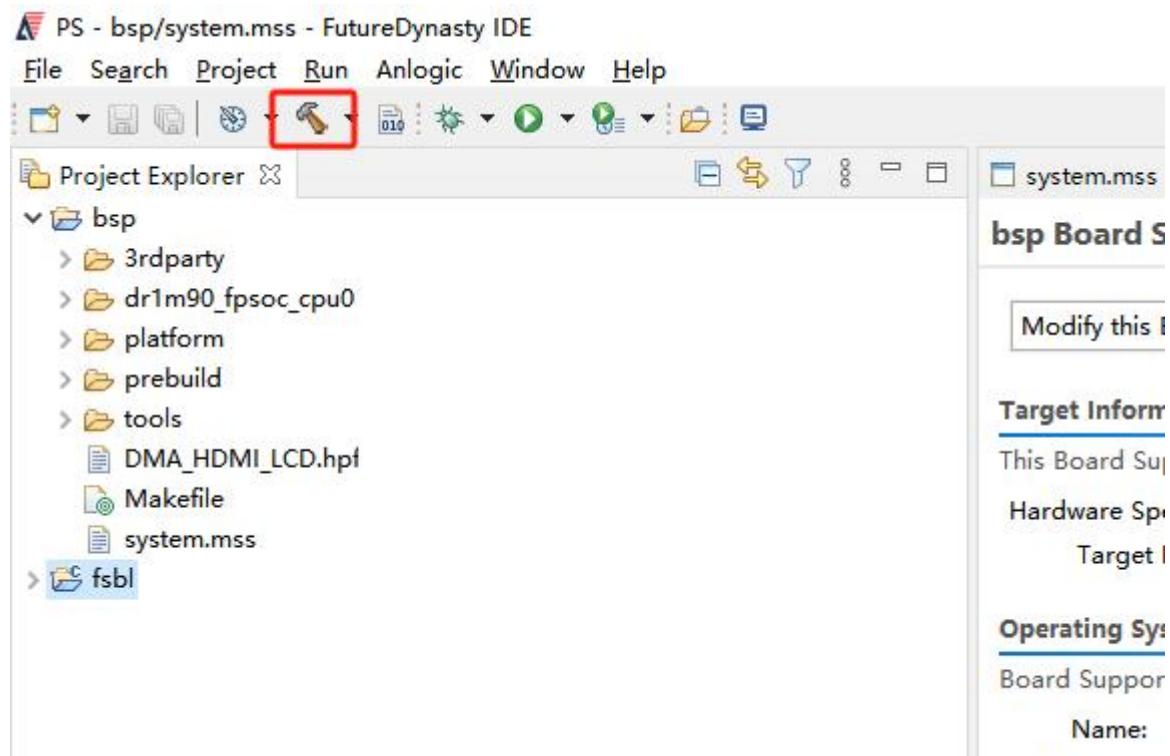

选中 fsbl,点击快捷图标编译 fsbl 文件

图 4-28 编译 fsbl

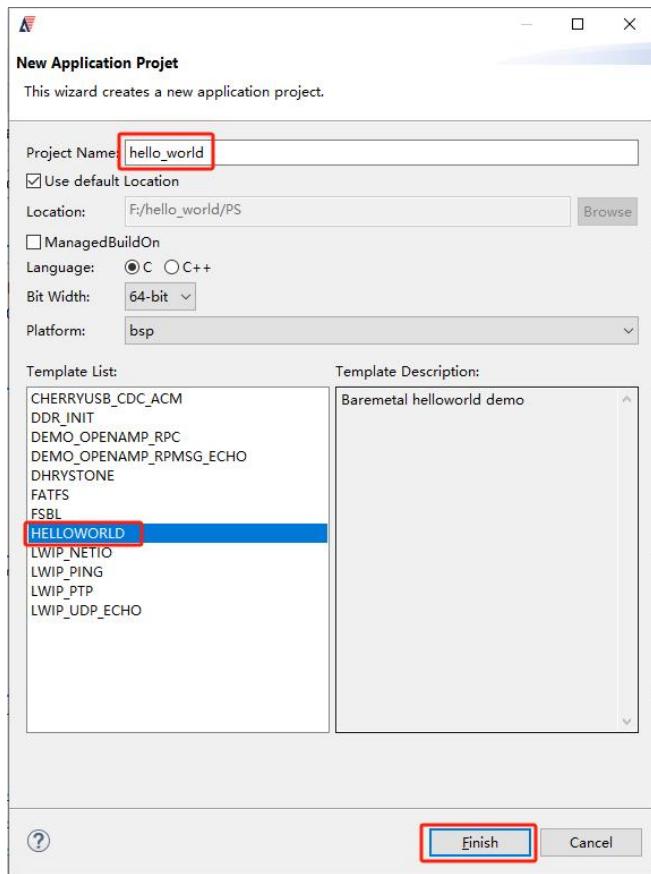

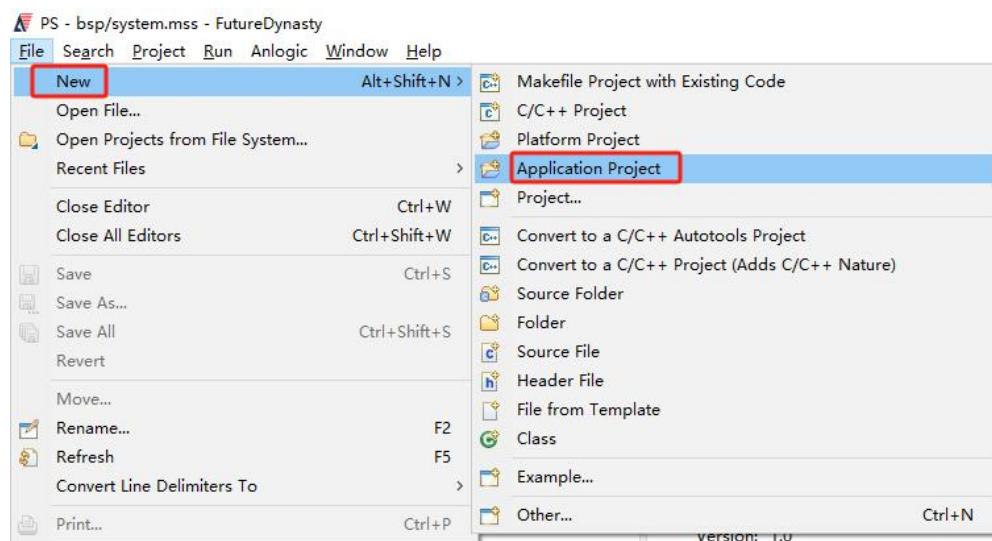

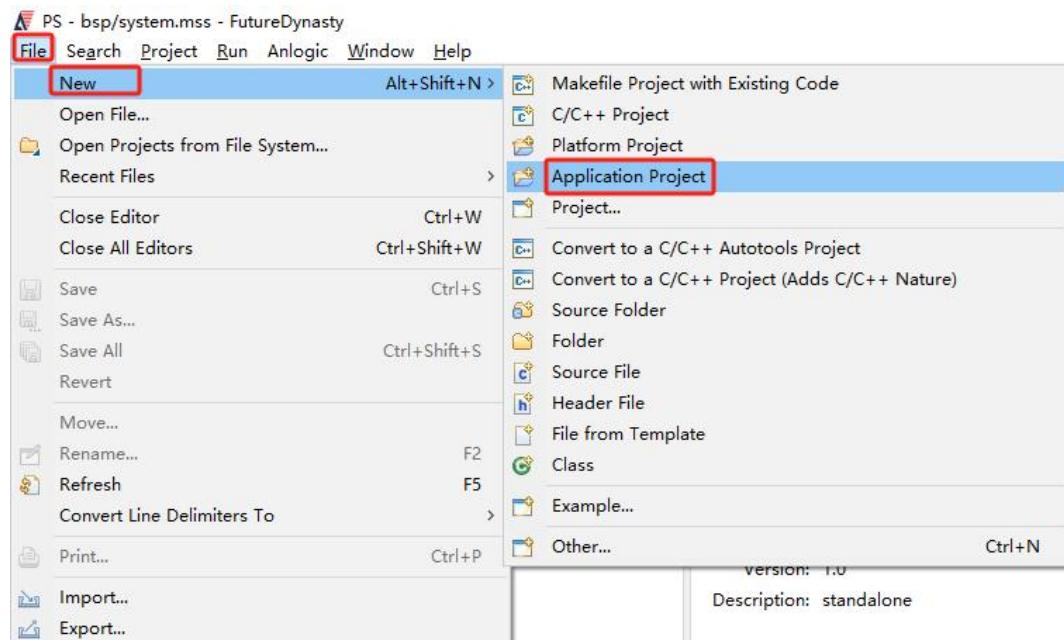

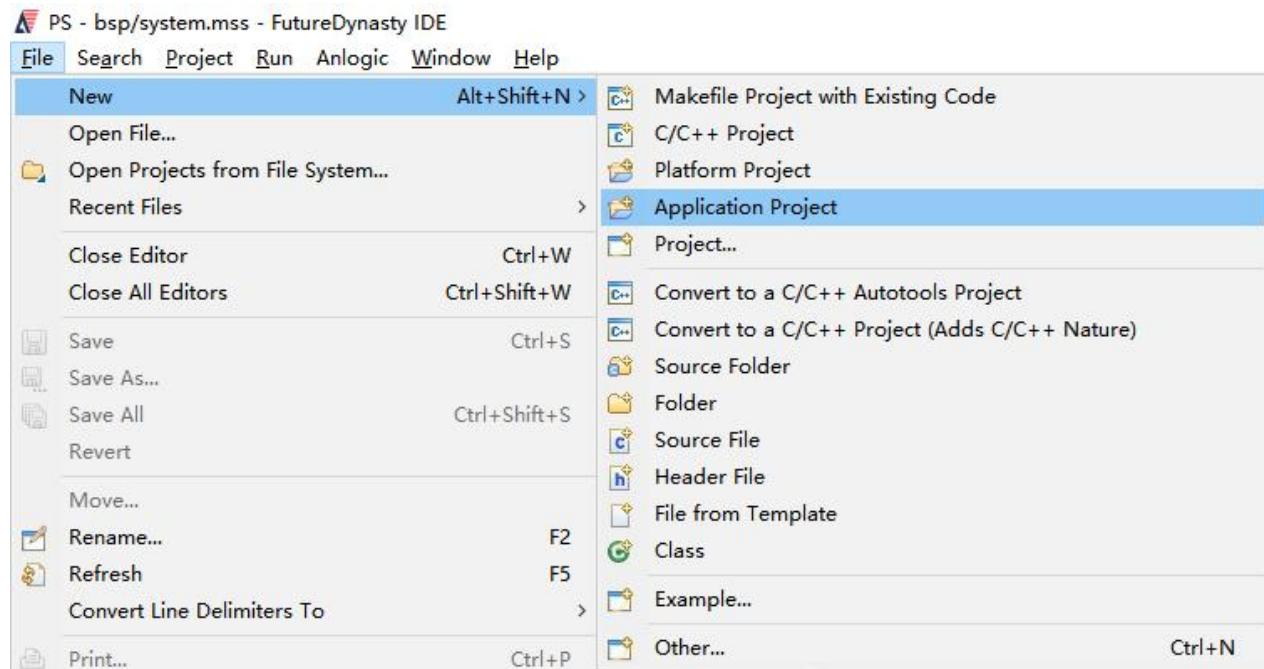

点击 File-->New-->Application Project 新建 hello\_world 工程

图 4-29 新建 hello\_world 工程

填写工程名 hello\_world，选择 HELLOWORLD 模板，点击 Finish

图 4-30 生成 hello\_world 工程

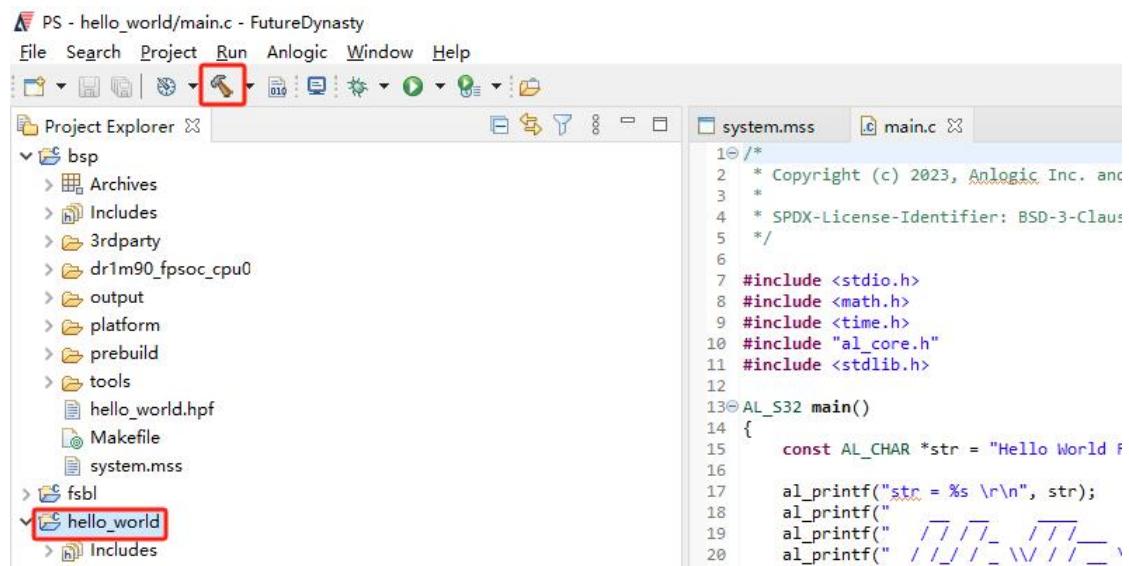

选择 hello\_world 工程，然后点击编译快捷图标进行编译

图 4-31 编译 hello\_world 工程

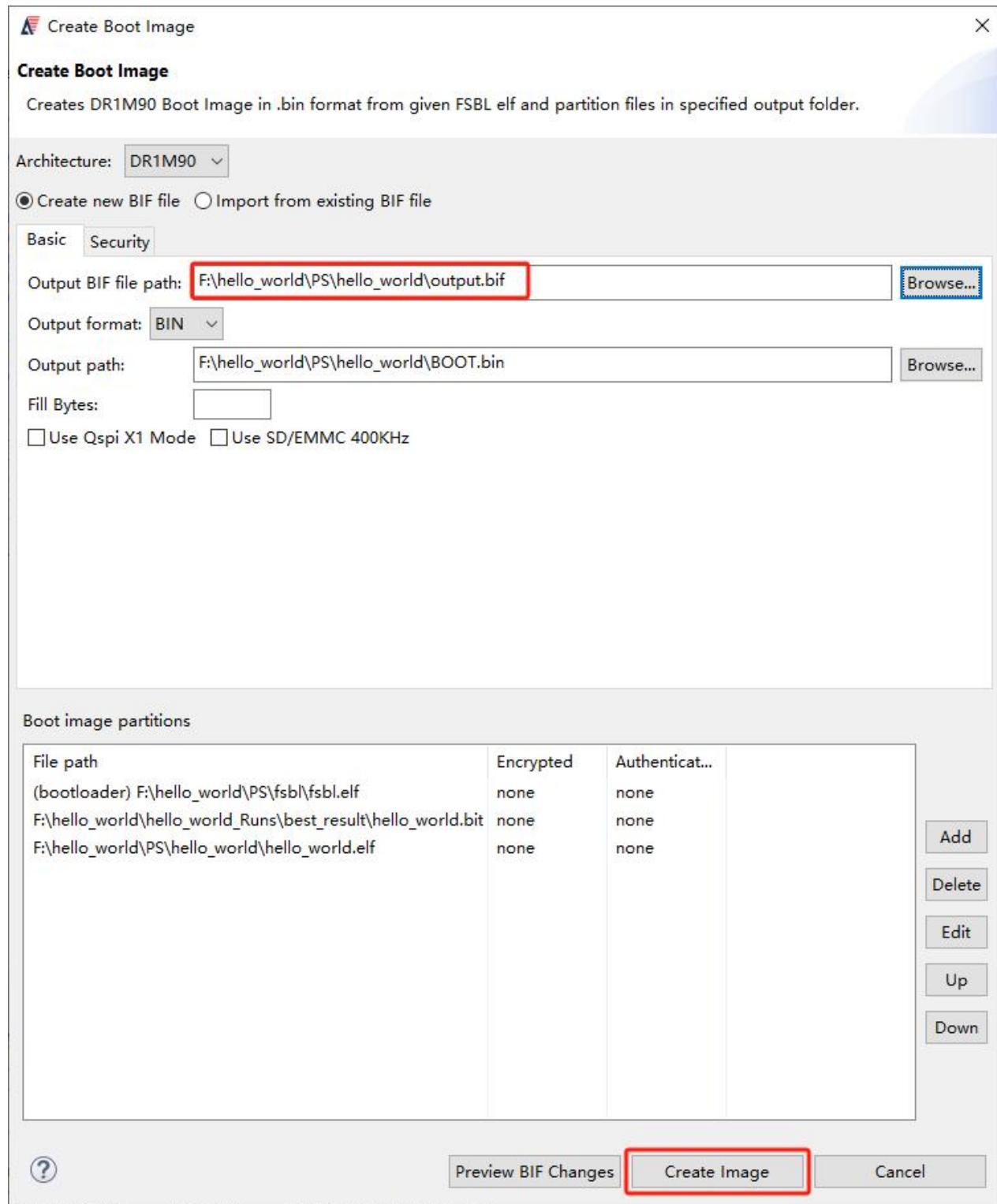

#### 4.1.10. 生成 BOOT.bin 文件

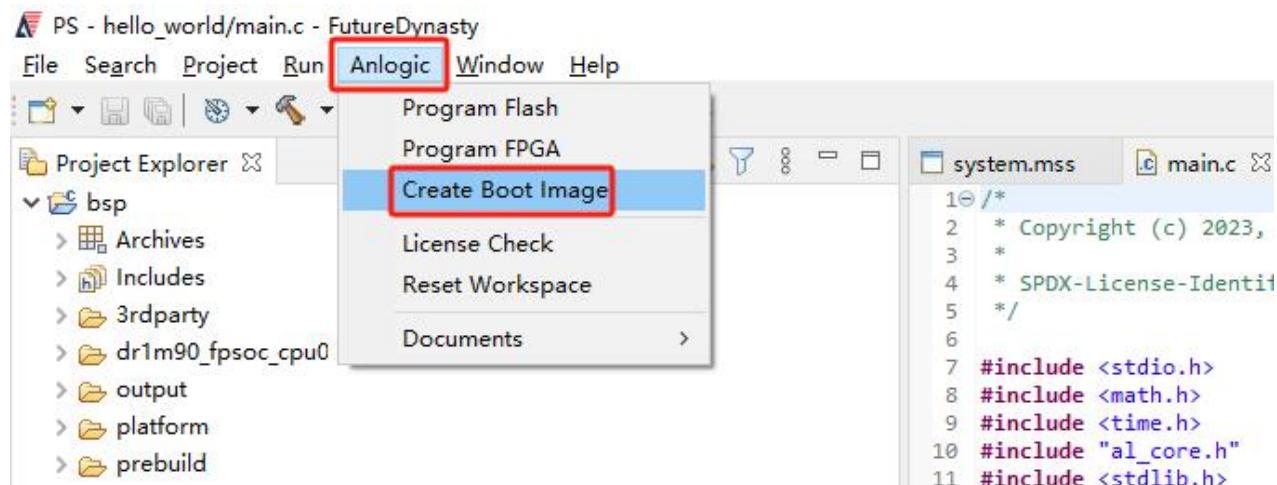

点击 Anlogic-->Create Boot Image 生成 bin 文件

图 4-32 选择生成 bin 文件菜单

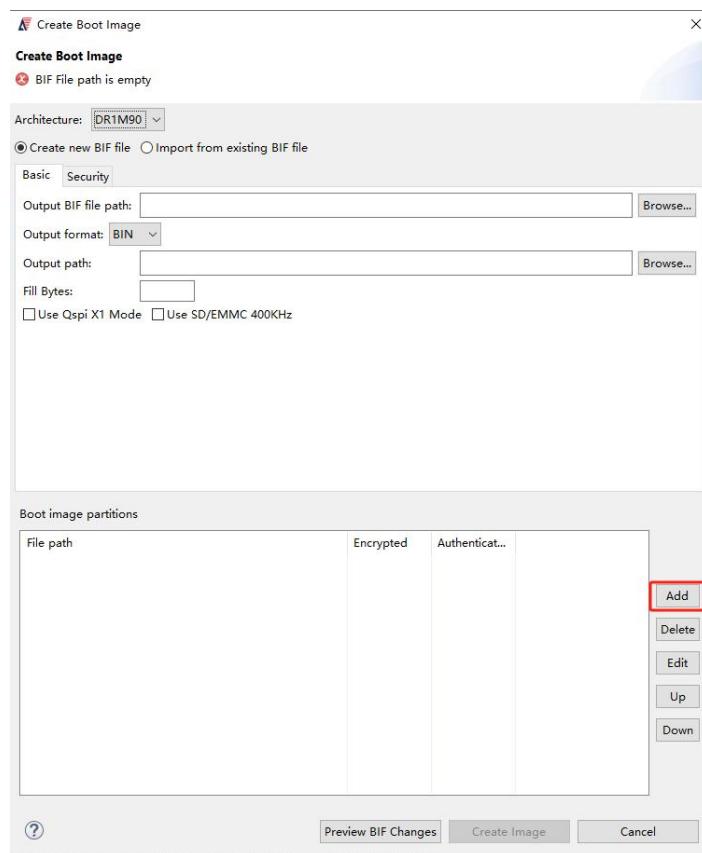

点击 Add, 添加文件

图 4-33 添加文件

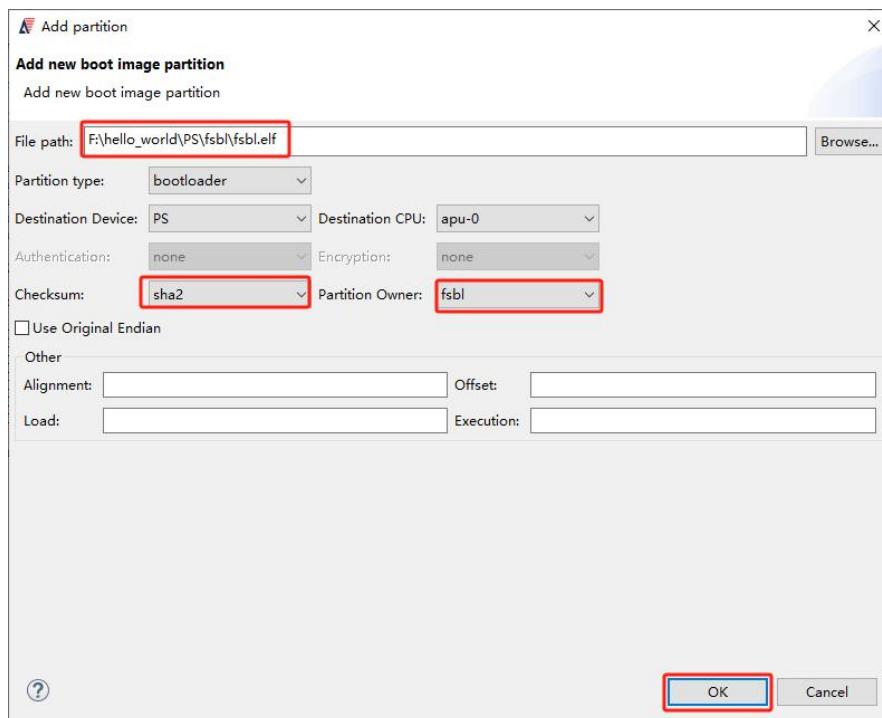

在添加对话框，选择添加 fsbl.elf 文件，设置为 sha2 和 fsbl，点击 OK 完成添加

图 4-34 添加 fsbl 文件

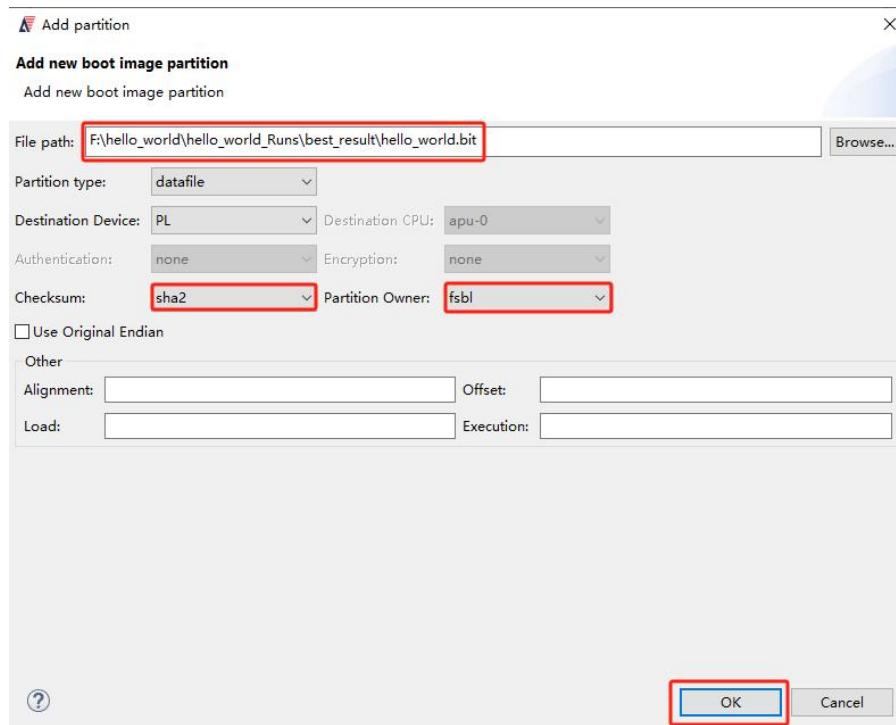

点击 Add，选择添加 hello\_world.bit 文件，设置为 sha2 和 fsbl，点击 OK 完成添加

图 4-35 添加 bit 文件

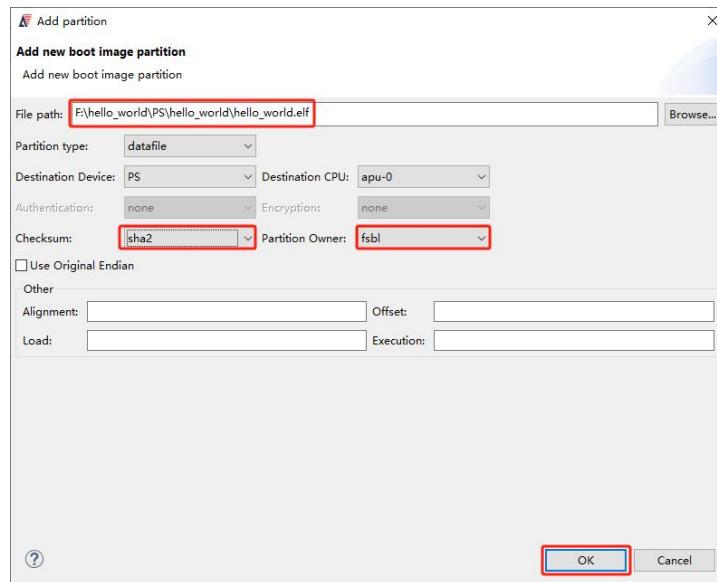

点击 Add 添加 hello\_world.elf 文件，设置为 sha2 和 fsbl，点击 OK 完成添加

图 4-36 添加 hello\_world.elf 文件

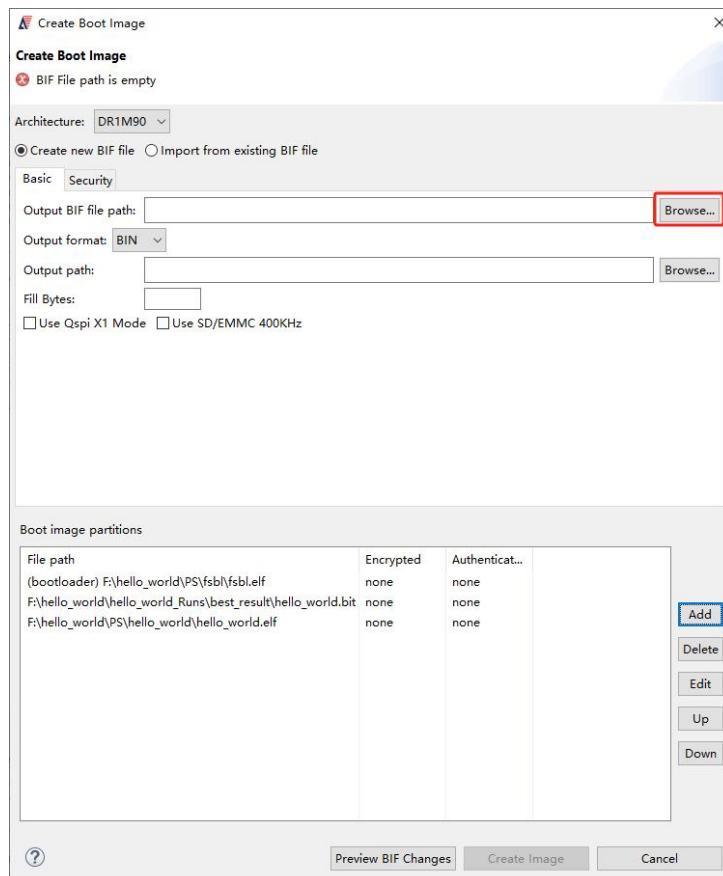

点击 Browse，添加 bin 文件存储路径

图 4-37 添加 bin 文件存储路径

添加 bin 文件存储路径后，点击 Create Image 生成 bin 文件

图 4-38 生成 bin 文件

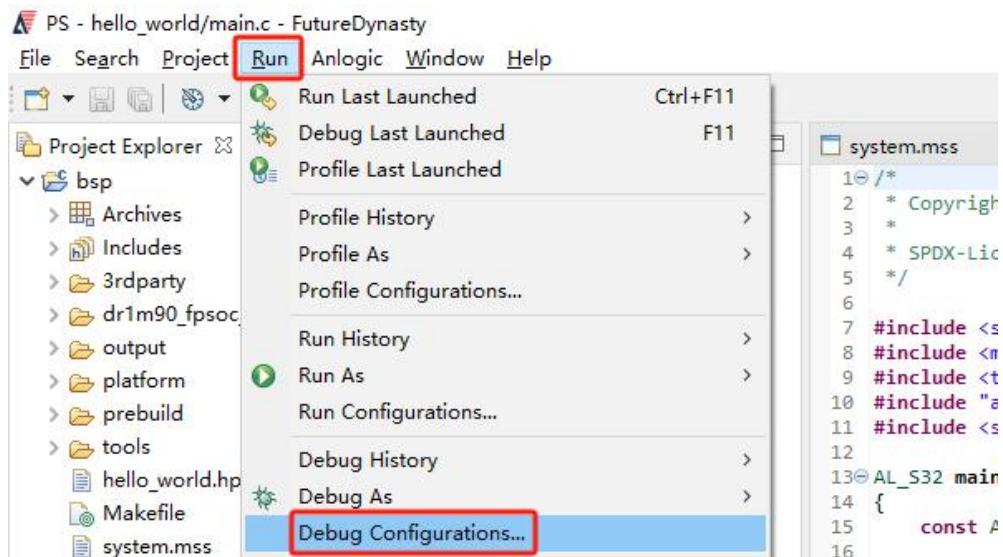

## 4.1.11. Debug 调试

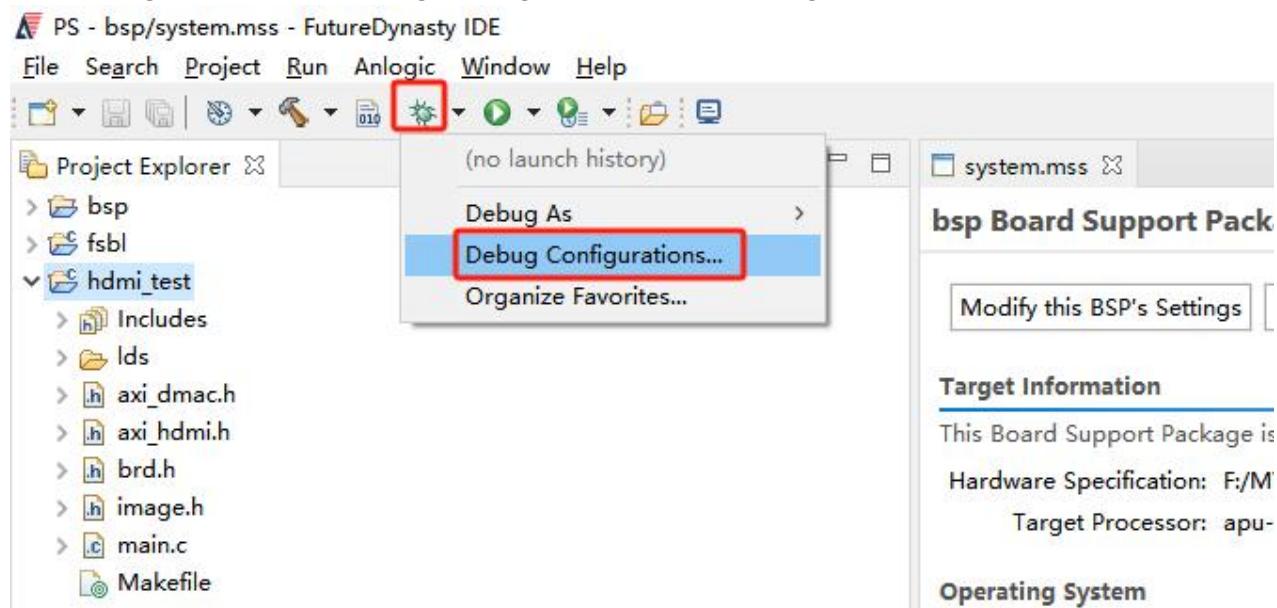

点击 Run-->Debug Configurations，打开 debug 调试对话框

图 4-39 打开 debug 调试对话框

选择 hello\_world，勾选 Program FPGA，添加 hello\_world.bin 文件，点击 Debug 开始将 pl 和 ps 程序下载到开发板运行

图 4-40 配置 debug 调试对话框

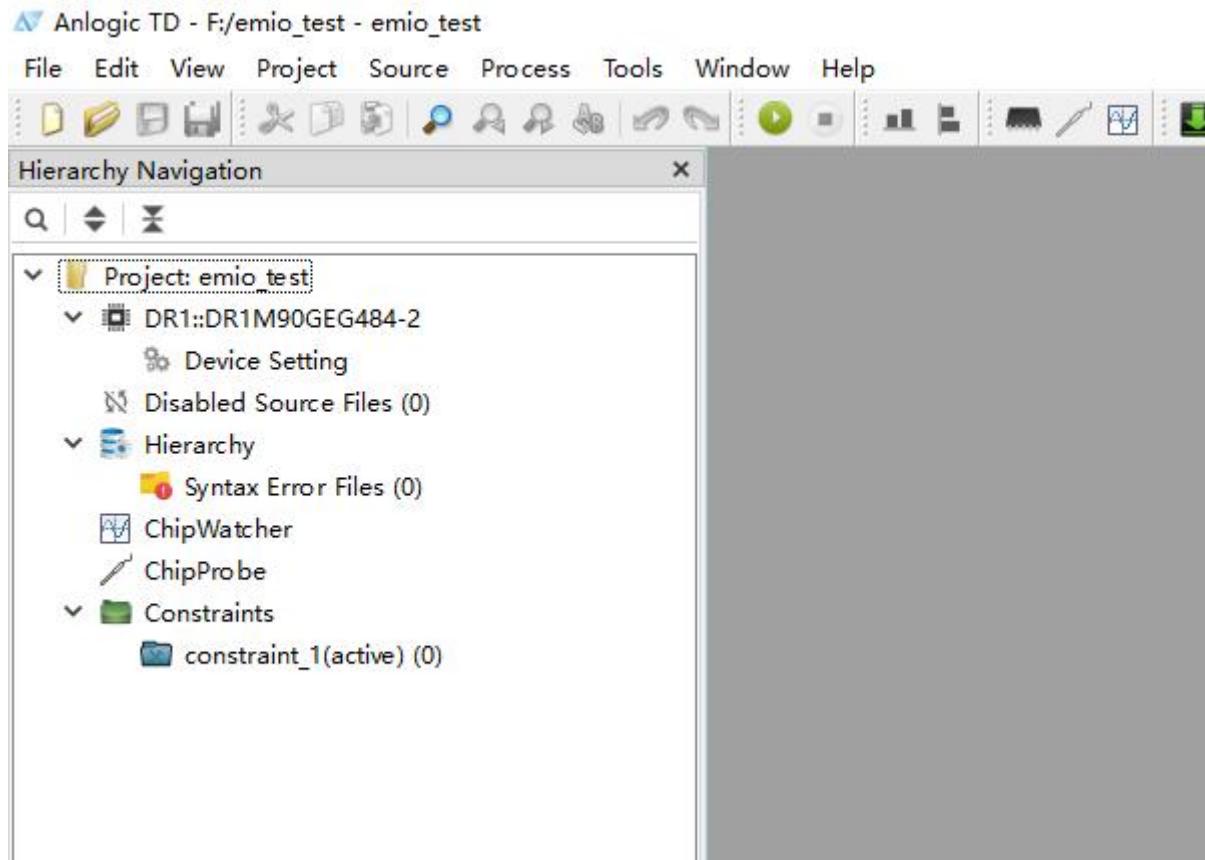

# 第五章 GPIO-EMIO 输出测试

MYD-YM90X 的平台主要是 FPGA 和 ARM 两部分，上一个章节主要介绍怎么使用 FPGA 平台，这章节着重介绍使用 ARM 平台，怎么配置 PS 端设备，ARM 端将会用到 FD 软件平台，本章节主要介绍 PS 端接口配置，以及 FD 软件平台的简单使用方法。

## 5.1. GPIO-EMIO 工程介绍

本章节主要讲解怎么使用 FD 来控制 FPGA 端的管脚，如果需要在 FD 里面使用裸机来控制 FPGA 端的管脚，需将 ARM 的核配置为 EMIO 方式，EMIO 方式管脚约束为 FPGA 管脚，本章节着重于如何配置 EMIO，以及 TD 的顶层如何更改为 EMIO 的使用方式。

### 5.1.1. 新建 Emio\_test 工程

因新建工程部分和前一章节一样，这里不再重复新建 TD 工程步骤，不熟练的可以参考上一章节新建工程的方法。

图 5-1. 新建 TD 工程

## 5.1.2. 打开 Design Integrator

为了方便用户在 TD 中使用 IP，避免手写 IP 端扣间连接的重复操作，开发了 Design Integrator 工具，其主要功能是：根据用户定制的 ip 以及端口，在连线后生成对应 RTL 代码。

选择 Tools-->Design Integrator

图 5-2. 打开 Design Integrator

## 5.1.3. 新建 Design

点击 Flow-->Create Design

填写 design 名称和存储路径，然后点击 OK

图 5-3. 新建 design

#### 5.1.4. 调用 PS 端 IP

点击 Add IP 添加 PS 端 ip

图 5-4. 添加 ps 端 ip

在弹出的对话框中，双击 ARM Processor System 调用 ip 核

图 5-5. 调用 ps 端 ip

调用的 PS 端 IP

图 5-6. 调用的 ps 端 ip

双击 ip 核，设置 PS 端的 uart 管脚为 MIO50~MIO51，Bank 电压都设置为 1.8V,然后点击 OK

图 5-7. 配置 uart 管脚

配置 DDR，勾选 DDR 使能和参考，配置完成后点击 OK

图 5-8. 配置 DDR 参数

IP 核生成成功，点击 OK 关闭对话框

图 5-9. IP 核生成成功

双击 p2f\_clk0 连接 master\_gp0\_axi\_aclk 管脚，因 GP 接口没有使用这里不需要引出

图 5-10 连接 GP 接口时钟管脚

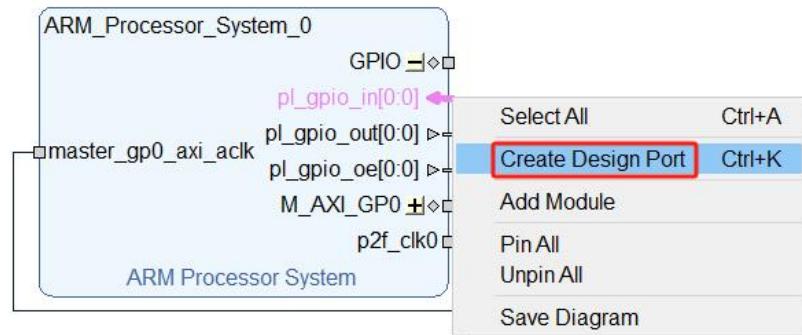

展开 gpio 管脚右击选择 Create Design Port 引出 gpio 的管脚

图 5-11 引出 gpio 管脚

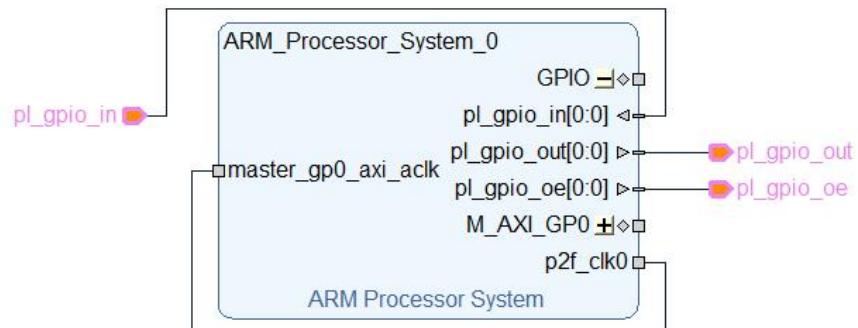

引出三路 gpio 管脚

图 5-12 引出三路 gpio 管脚

点击 Validate Design 检查是否有设计上的错误

图 5-13 设计验证

### 5.1.5. 导出 Design

点击 Flow-->Generate Design 导出 design

图 5-14 选择导出 design 菜单

点击 Generate, 导出 design 配置

图 5-15 导出 design

导出的 design 文件树

图 5-16 导出的 design 文件树

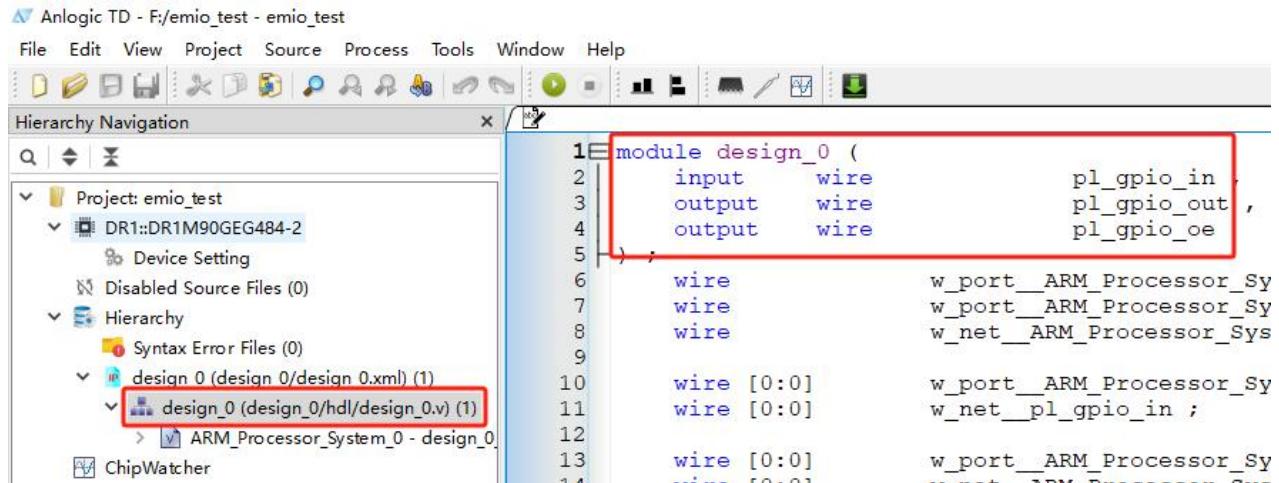

design 生成的顶层文件，如果下图所示，因此工程主要使用 PS 端 ip，所以可以看到右边顶层文件没有 FPGA 管脚输出口

图 5-17 生成的 design 模块顶层文件

### 5.1.6. 新建 FPGA 顶层文件

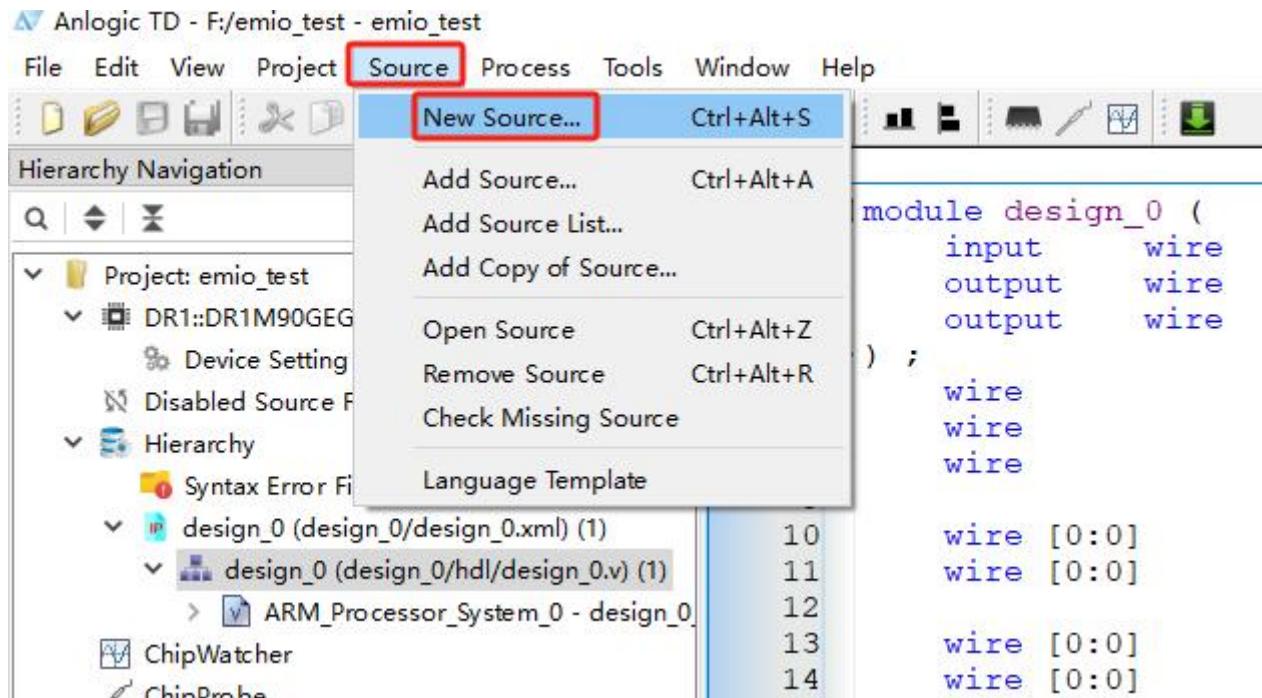

点击 Source-->New Source, 新建 FPGA 文件

图 5-18 新建 FPGA 顶层文件

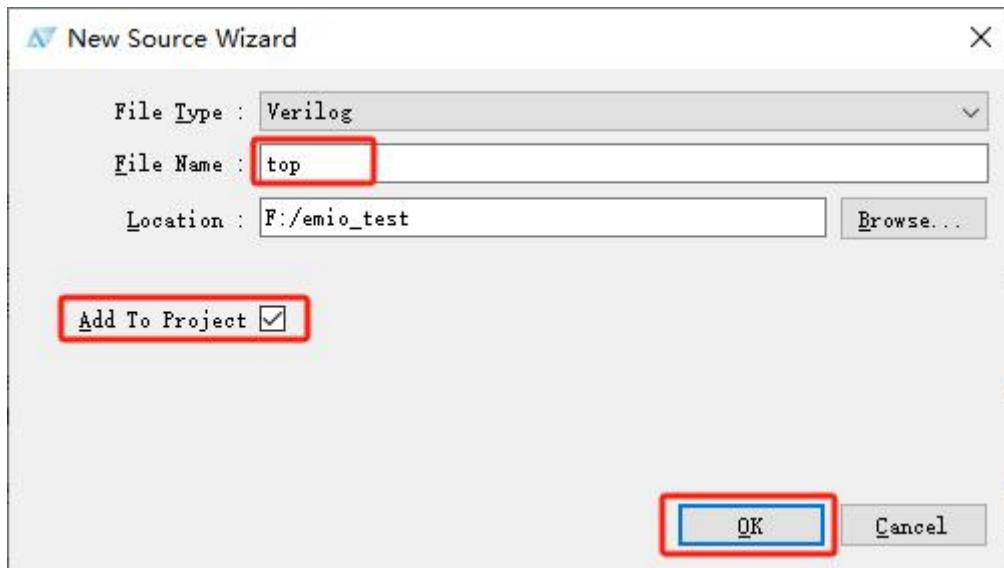

设置顶层文件名为 top，加入到工程里，然后点击 OK

图 5-19 设置顶层文件

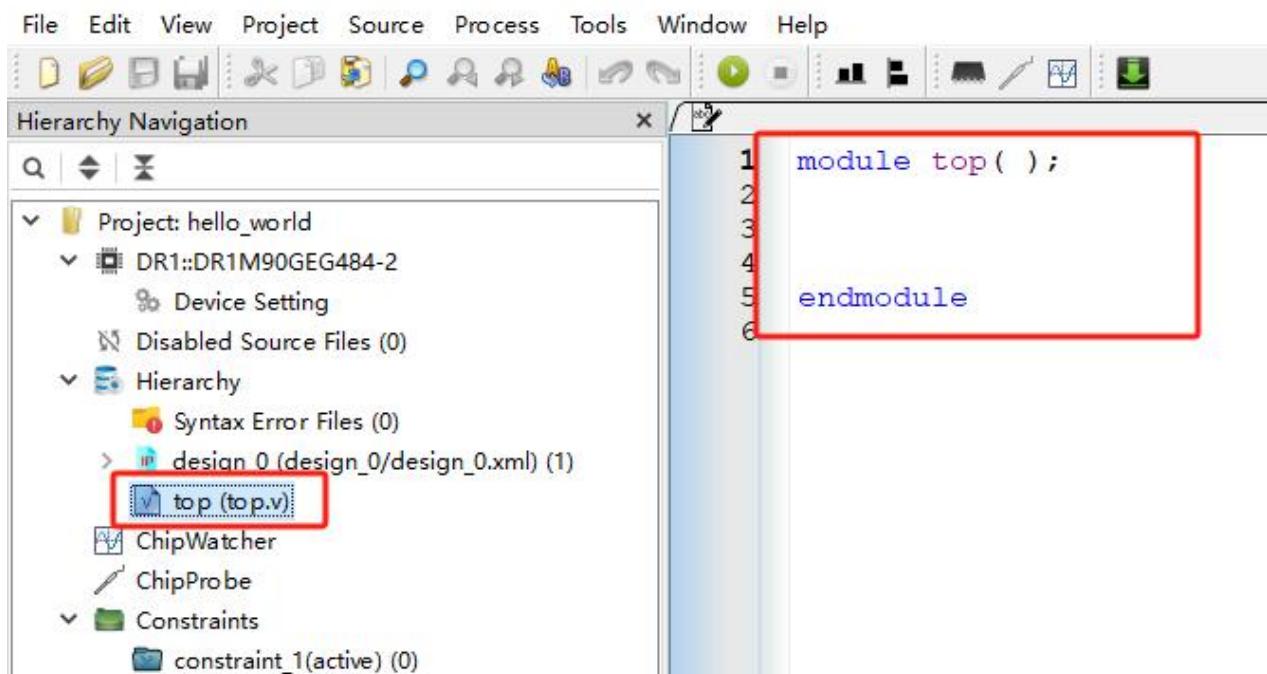

生成的顶层文件 top，如下图所示

图 5-20 生成顶层文件 top

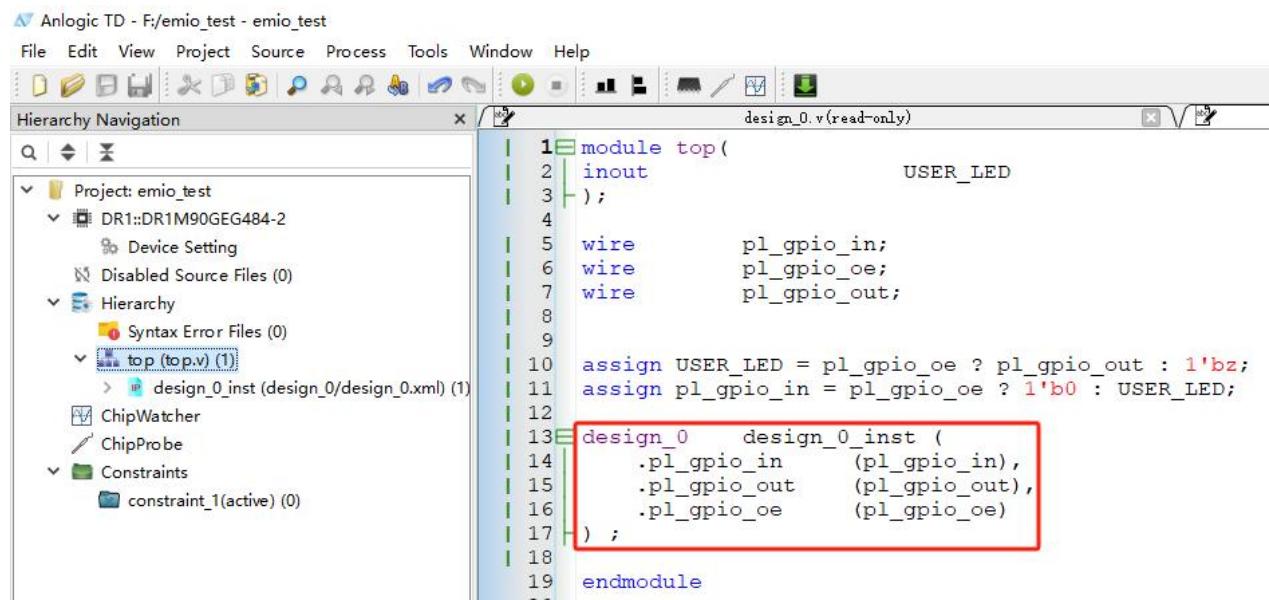

将 design 顶层例化到 FPGA 顶层文件里，设置 gpio 输出方式为双向口 inout 类型

```

1 module top();

2   inout USER_LED;

3 endmodule

4

5 wire pl_gpio_in;

6 wire pl_gpio_oe;

7 wire pl_gpio_out;

8

9

10 assign USER_LED = pl_gpio_oe ? pl_gpio_out : 1'bz;

11 assign pl_gpio_in = pl_gpio_oe ? 1'b0 : USER_LED;

12

13 design_0 design_0_inst (

14   .pl_gpio_in    (pl_gpio_in),

15   .pl_gpio_out   (pl_gpio_out),

16   .pl_gpio_oe    (pl_gpio_oe)

17 );

18

19 endmodule

```

图 5-21 例化 PS 模块

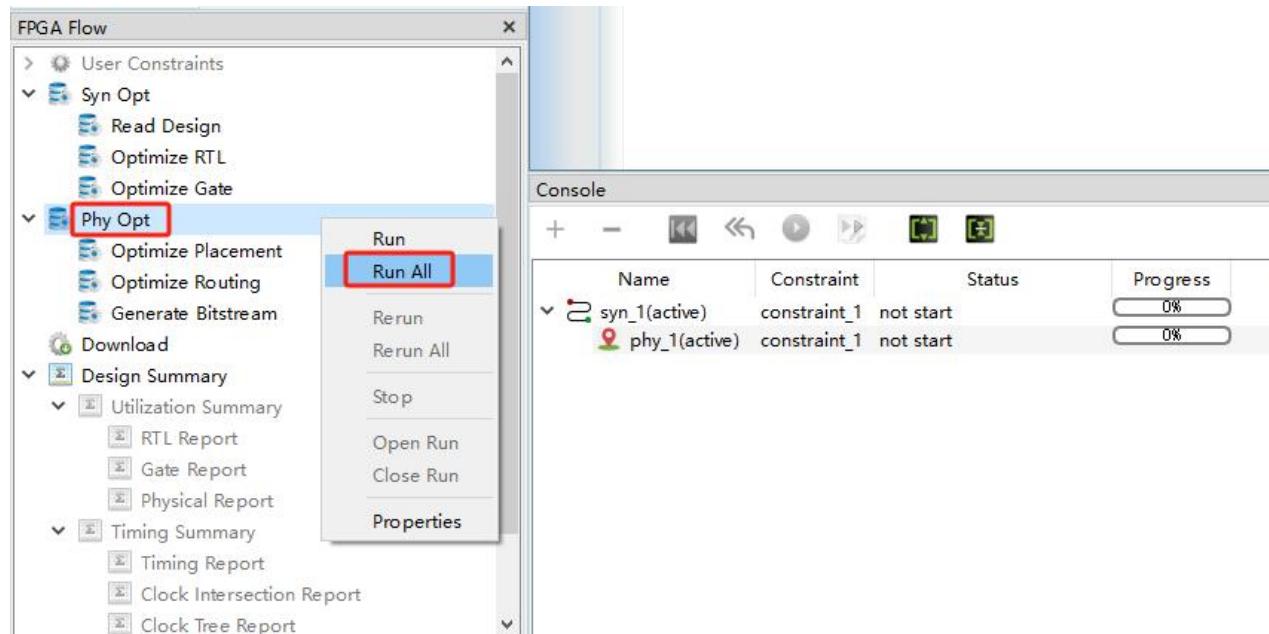

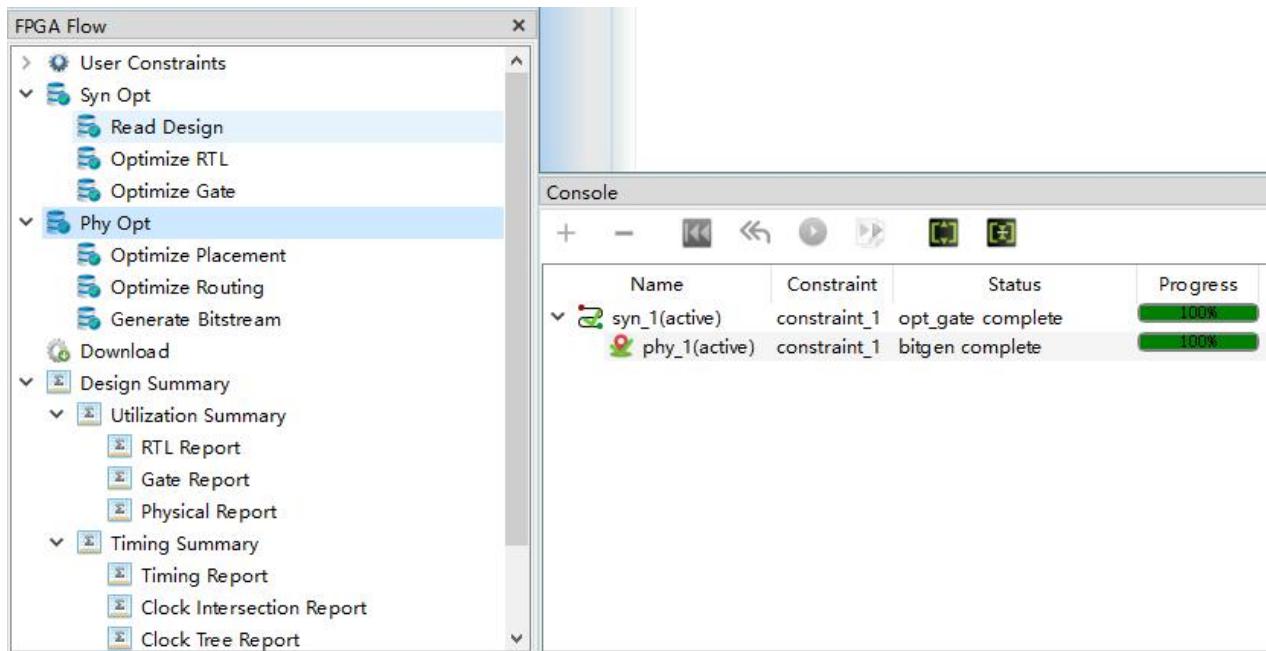

### 5.1.7. 编译 FPGA 工程

在 Phy Opt 上右击选择 Run All 编译整个工程

图 5-22 编译工程

FPGA 工程编译完成

图 5-23 工程编译完成

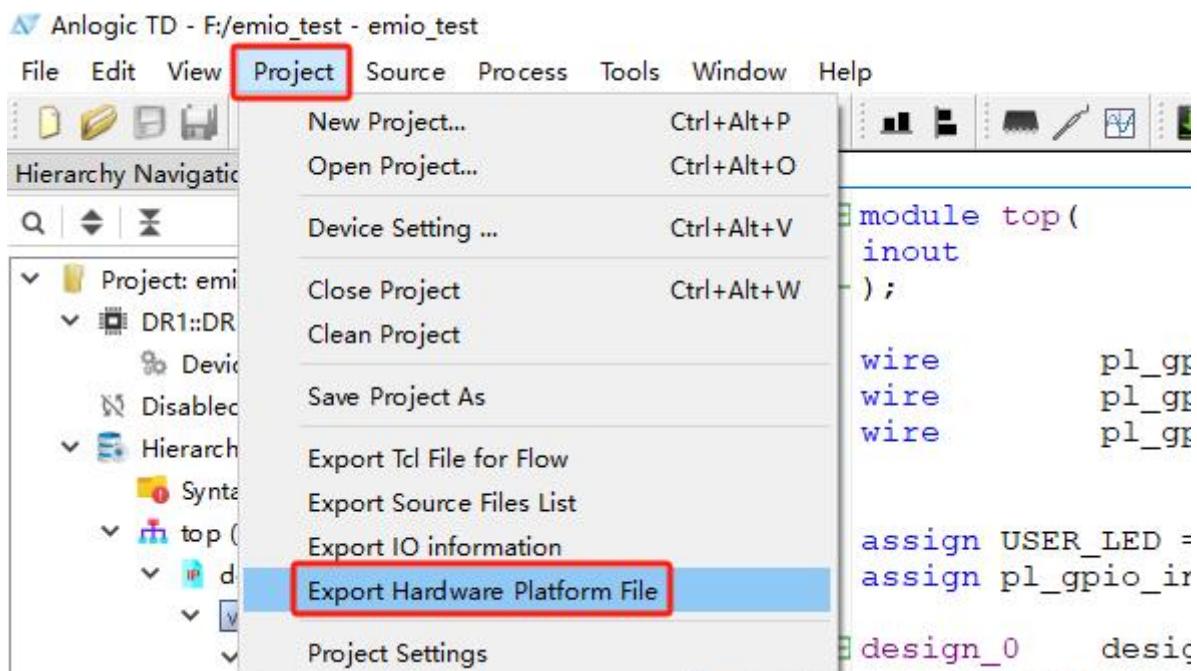

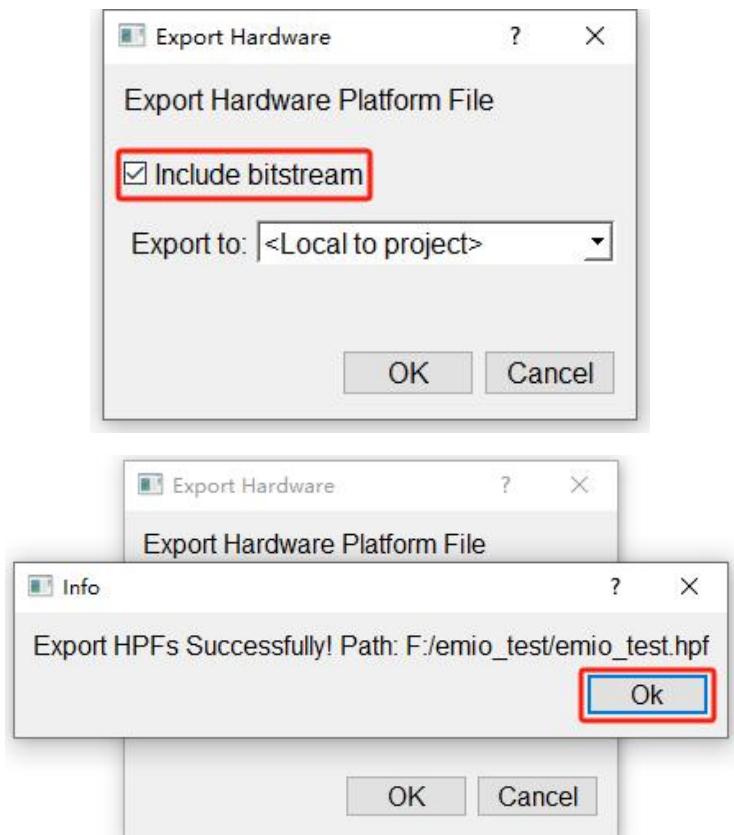

### 5.1.8. 导出 HPF 工程

点击 Project-->Export Hardware Platform File 导出 hpf 文件

图 5-24 导出 hpf 文件

勾选 Include bitstream，表示输出的 hpf 文件包含 bit 文件，点击 OK

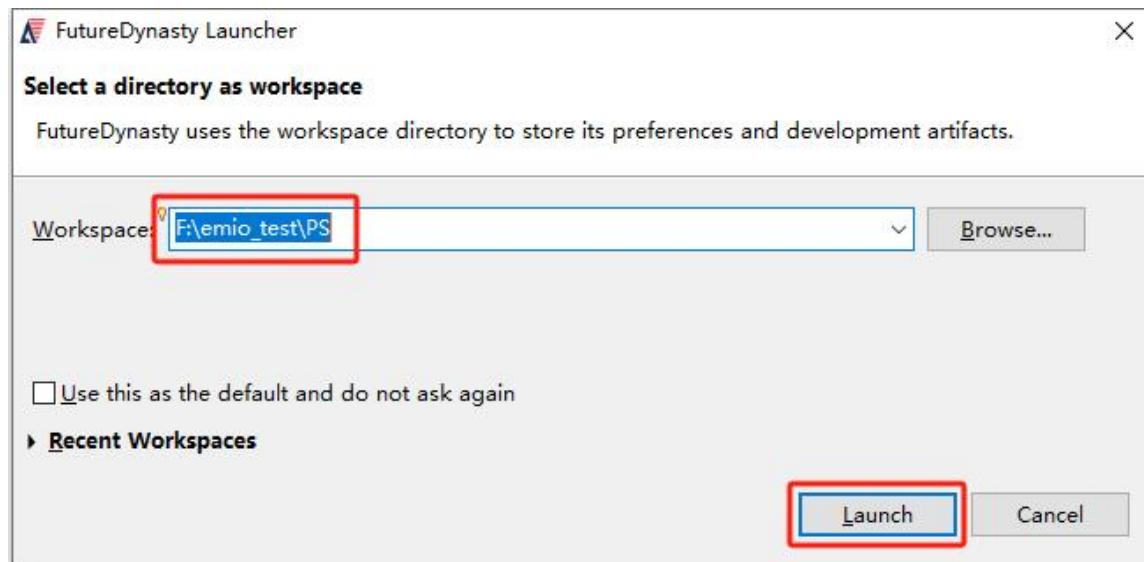

### 5.1.9. 新建 BSP 工程

在 emio\_test 工程新建一个 PS 文件夹，将 FD 工程保存指向 PS 文件夹，然后点击 Launch

图 5-25 打开 FD 软件

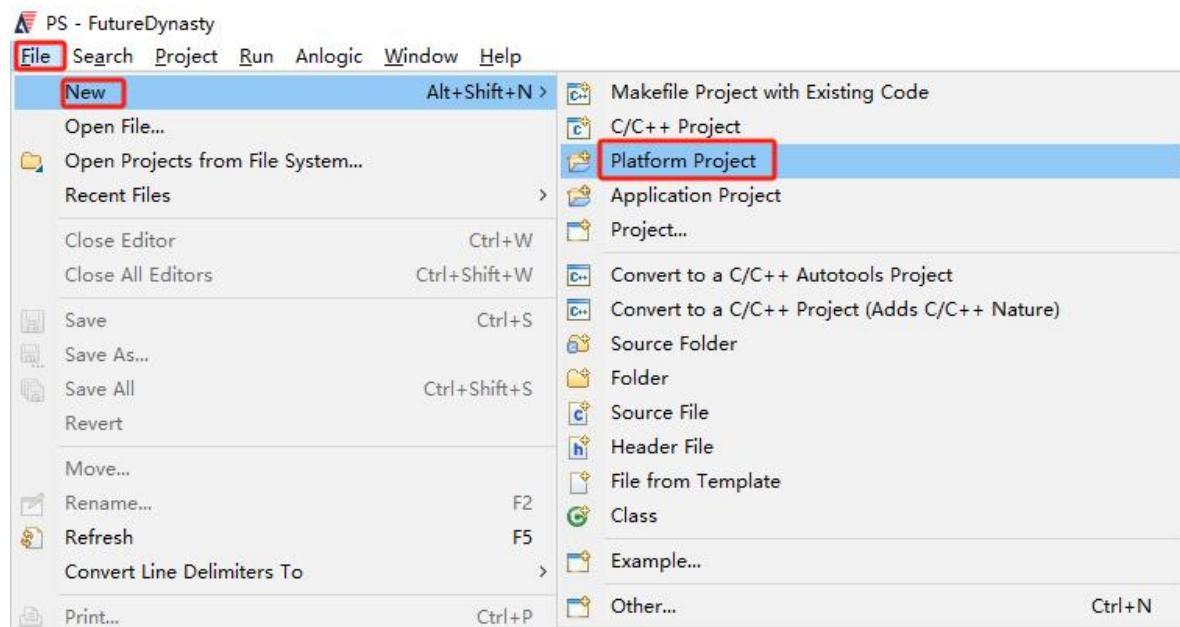

点击 File-->New-->Platform Project 新建 bsp

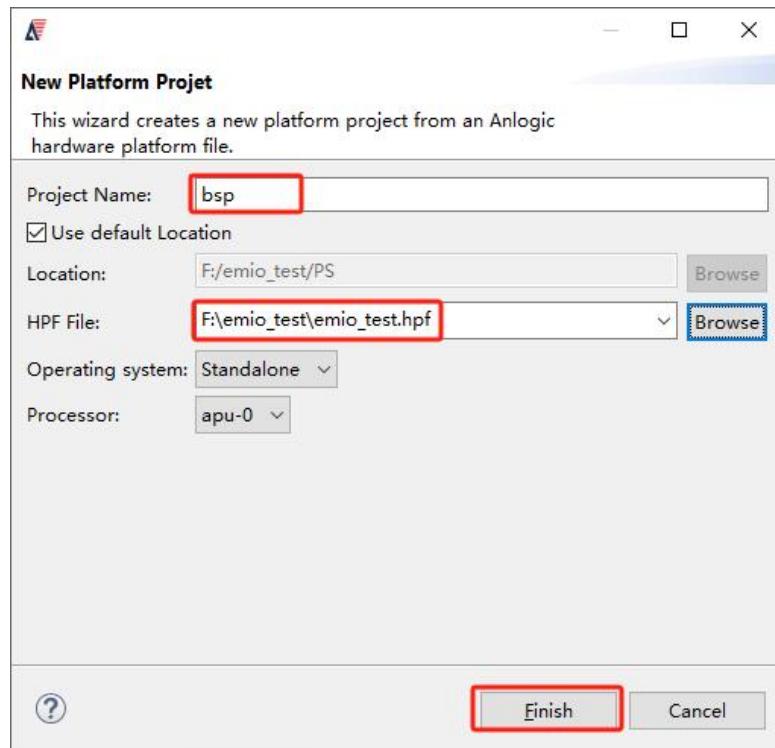

图 5-26 新建 BSP

填写工程名 bsp，添加 hpf 文件，然后点击 Finish

图 5-27 BSP 文件设置

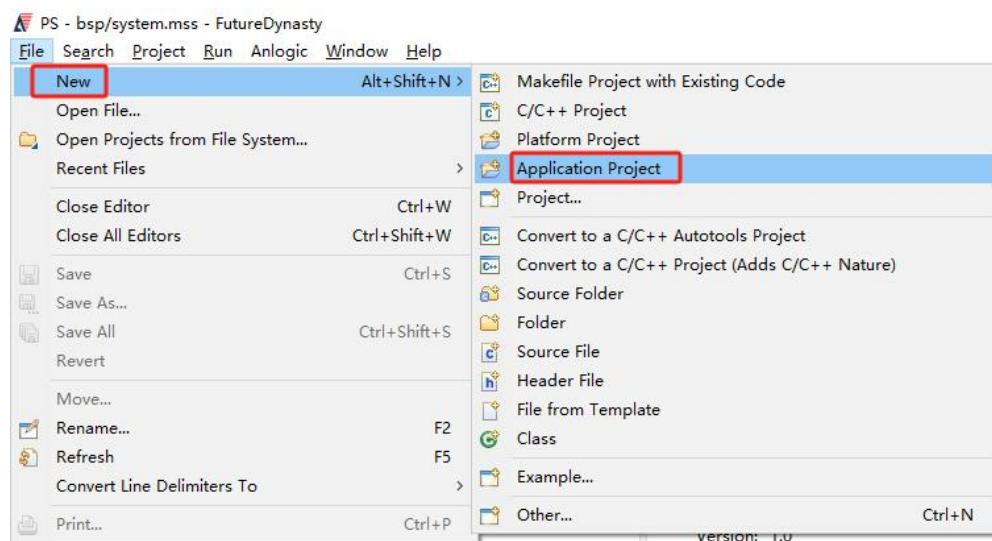

选择 File-->New-->Application Project 新建 fsbl 文件

图 5-28 新建 fsbl

填写工程名为 fsbl,选择 FSBL 模板, 然后点击 Finish

图 5-29 生成 fsbl

选中 fsbl,点击快捷图标编译 fsbl 文件

图 5-30 编译 fsbl

点击 File-->New-->Application Project 新建 hello\_world 工程

图 5-31 新建 hello\_world 工程

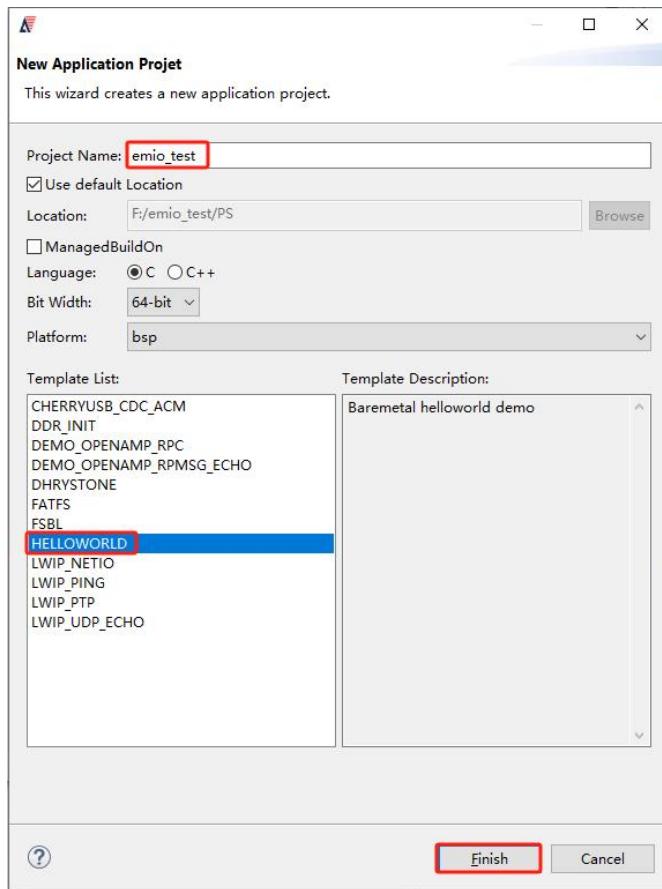

填写工程名 emio\_test，选择 HELLOWORLD 模板，点击 Finish

图 5-32 生成 hello world 工程

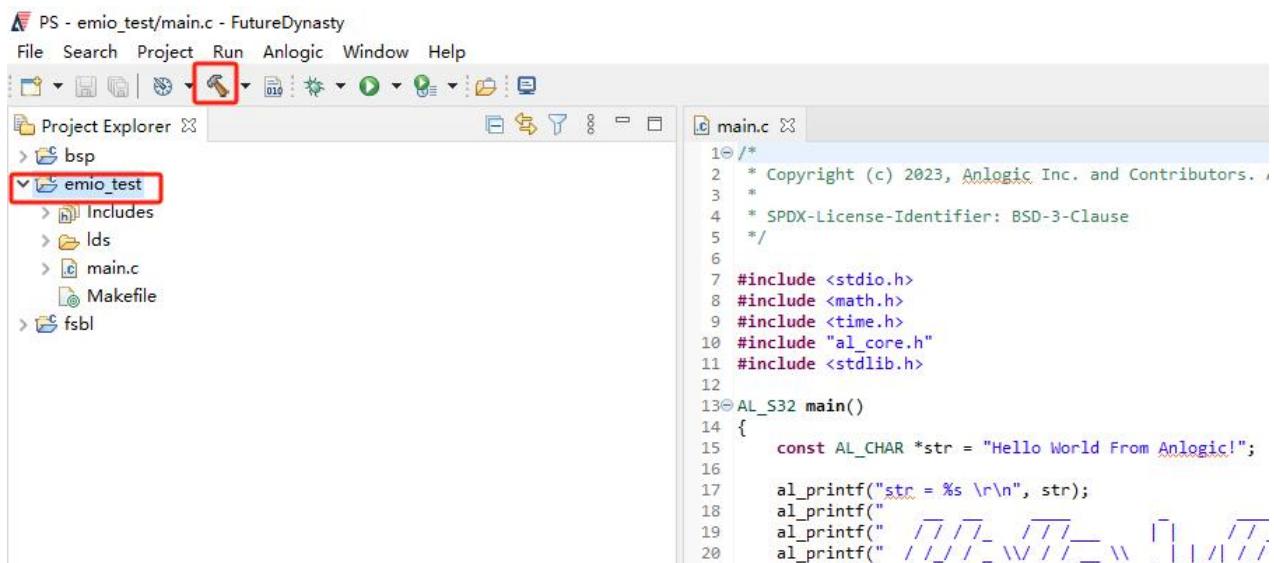

选择 emio test 工程，然后点击编译快捷图标进行编译

图 5-33 编译 hello world 工程

## 5.1.10. 生成 BOOT.bin 文件

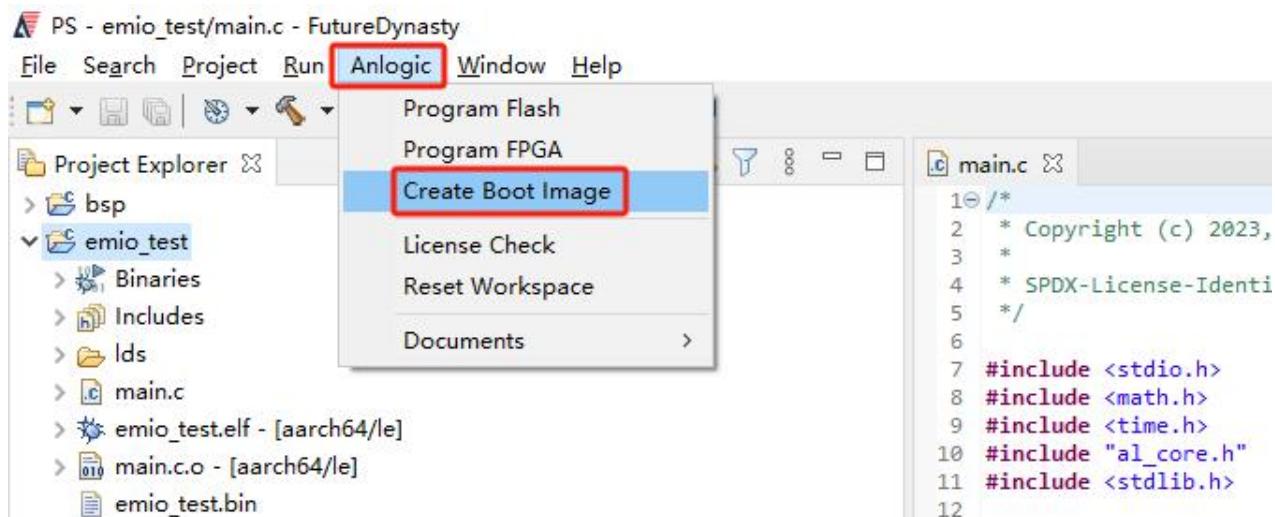

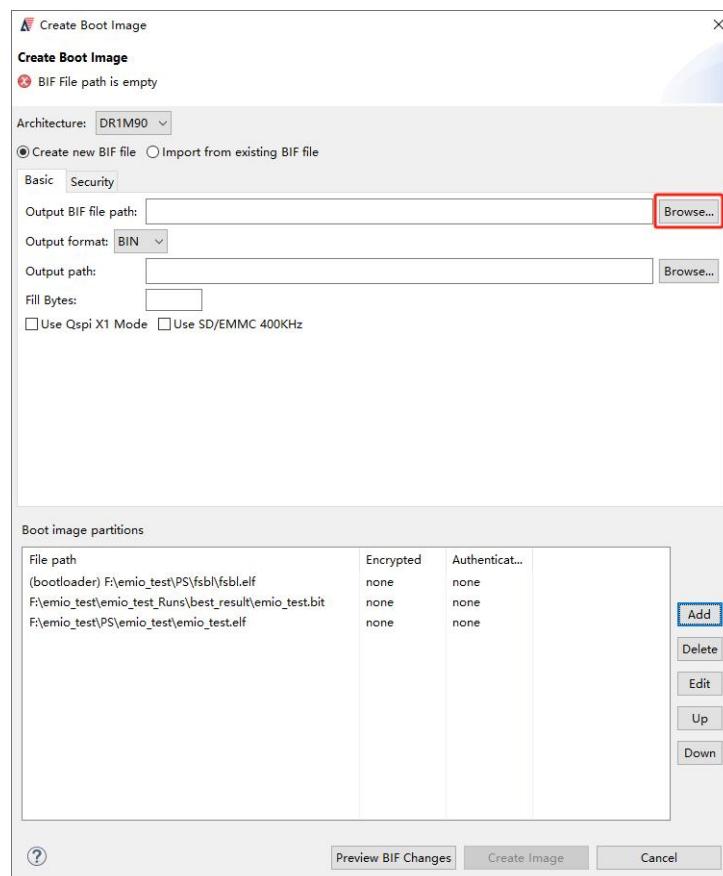

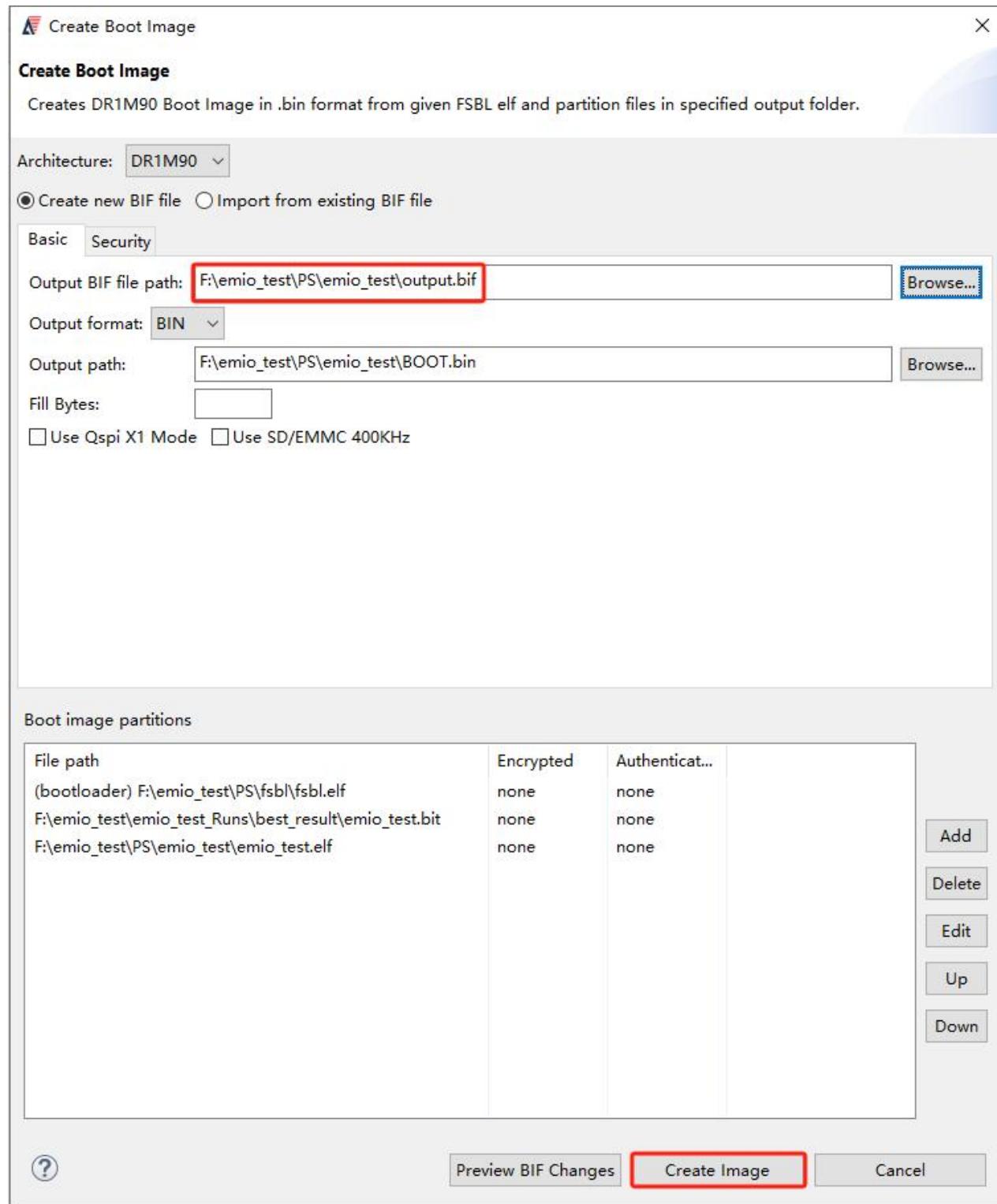

点击 Anlogic-->Create Boot Image 生成 bin 文件

图 5-34 选择生成 bin 文件菜单

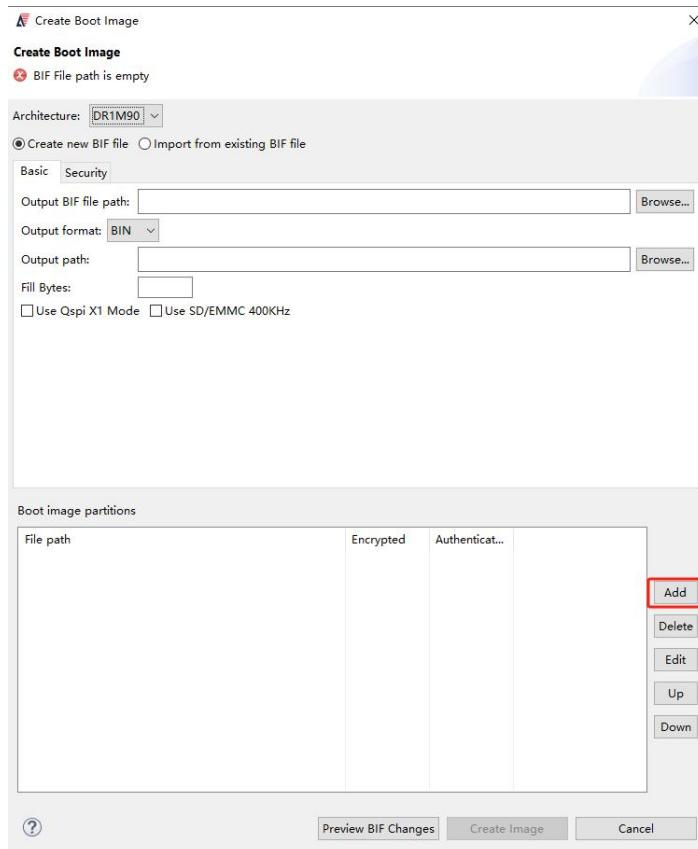

点击 Add, 添加文件

图 5-35 添加文件

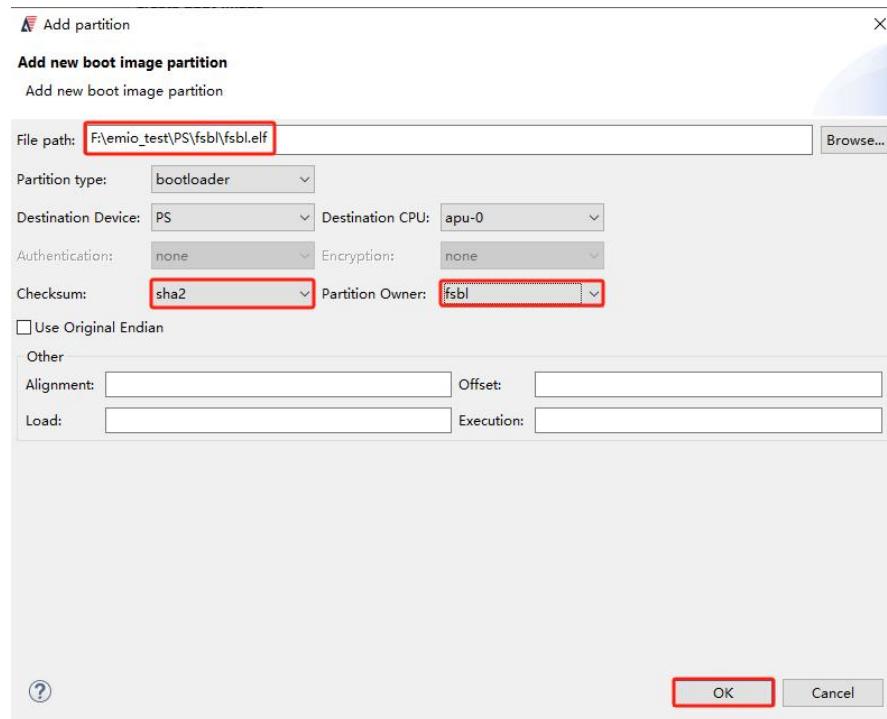

在添加对话框，选择添加 fsbl.elf 文件，设置为 sha2 和 fsbl，点击 OK 完成添加

图 5-36 添加 fsbl 文件

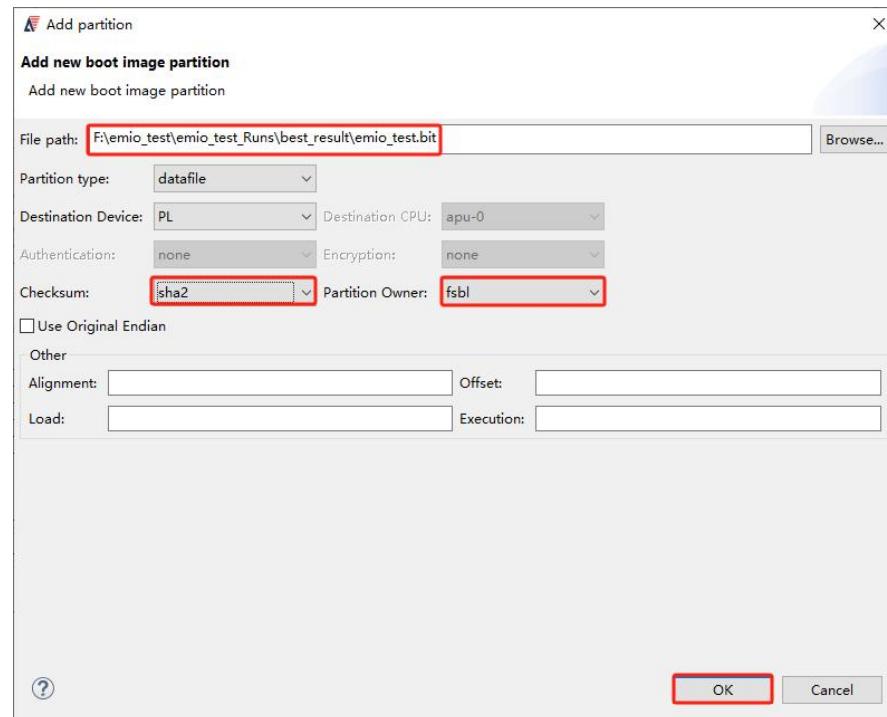

点击 Add，选择添加 emio\_test.bit 文件，设置为 sha2 和 fsbl，点击 OK 完成添加

图 5-37 添加 bit 文件

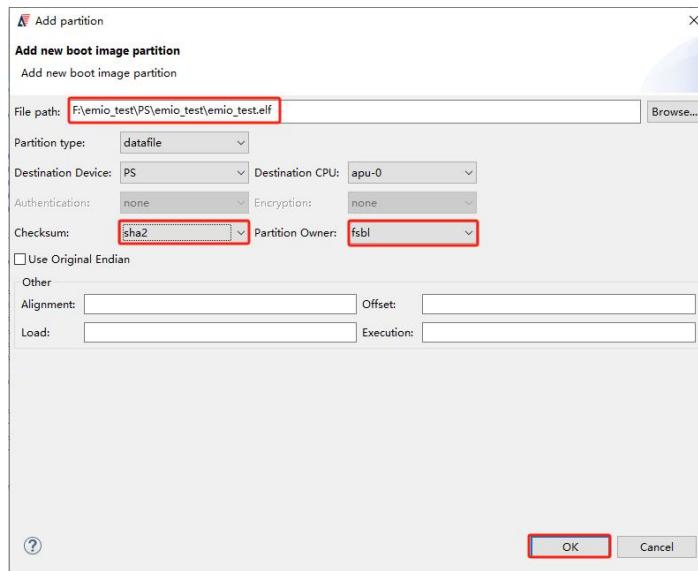

点击 Add 添加 emio\_test.elf 文件，设置为 sha2 和 fsbl，点击 OK 完成添加

图 5-38 添加 emio\_test.elf 文件

点击 Browse，添加 bin 文件存储路径

图 5-39 添加 bin 文件存储路径

添加 bin 文件存储路径后，点击 Create Image 生成 bin 文件

图 5-40 生成 bin 文件

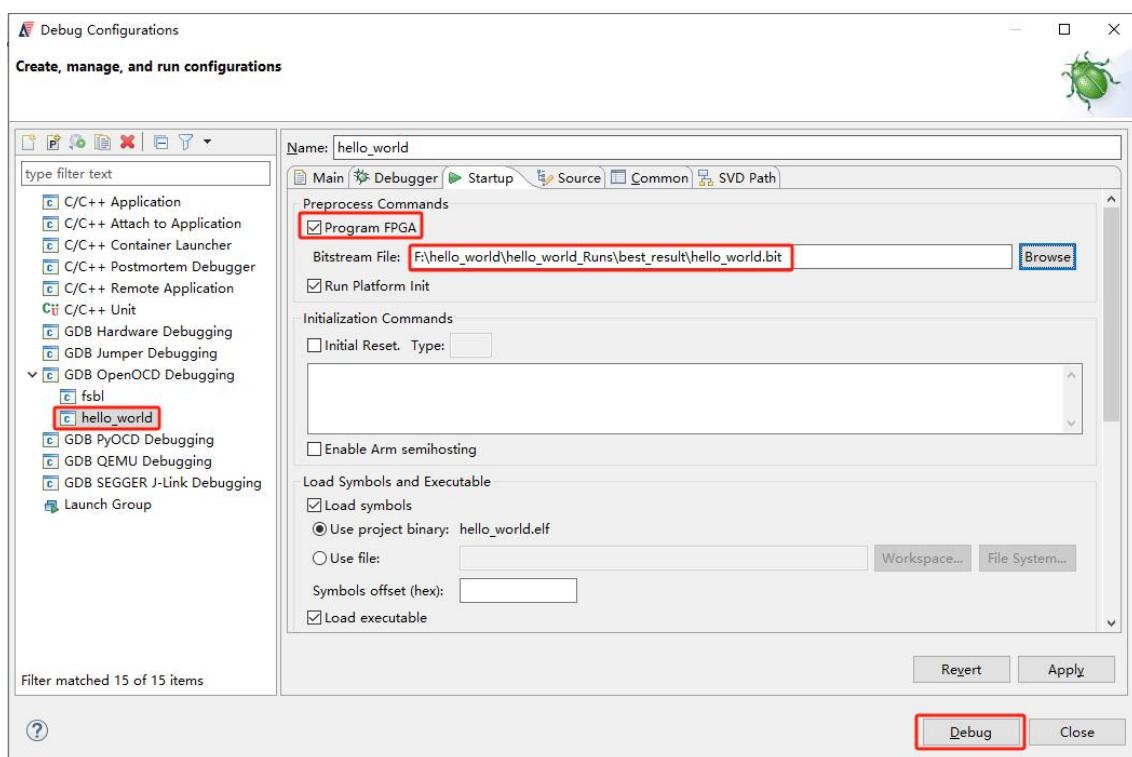

## 5.1.11. Debug 调试

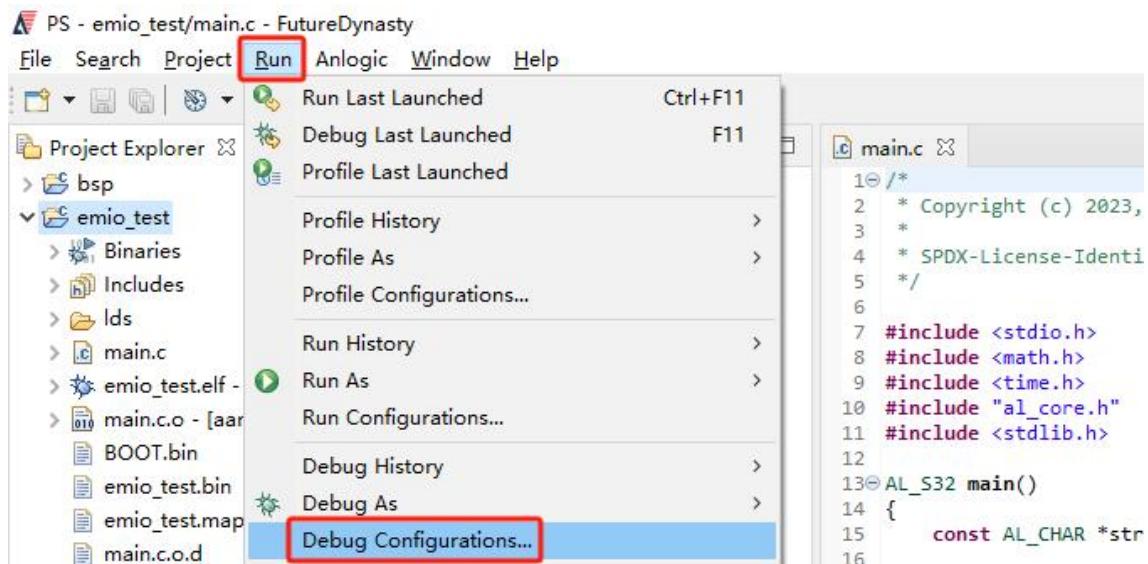

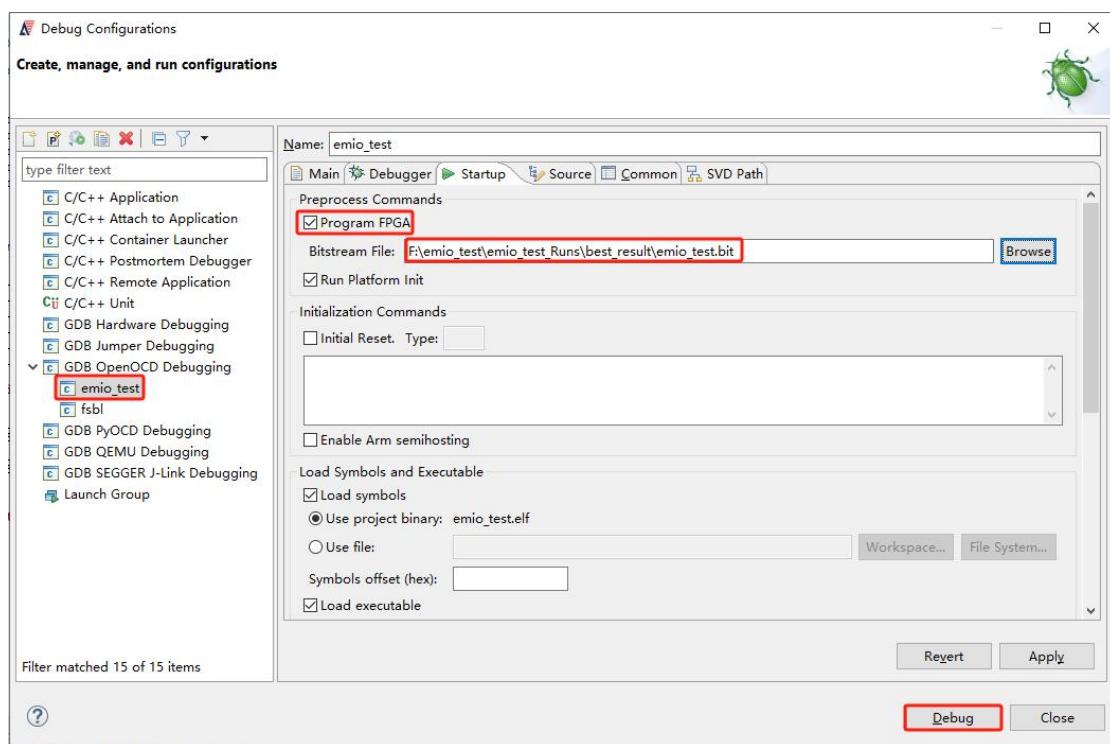

点击 Run-->Debug Configurations，打开 debug 调试对话框

图 5-41 打开 debug 调试对话框

选择 emio\_test，勾选 Program FPGA，添加 hello\_world.bin 文件，点击 Debug 开始将 pl 和 ps 程序下载到开发板运行

图 5-42 配置 debug 调试对话框

# 第六章 AXI4-Lite 总线使用

MYD-YM90X 的平台主要是 FPGA 和 ARM 两部分，FPGA 和 ARM 进行交互使用的是 AXI 总线，本章节主要着重于 PL 和 PS 如何通过 AXI 总线进行交互，相对于上一个章节，本章节不仅包含 FD 软件的使用，也会加入 TD 上加入 AXI 总线接口，相当于一个基本的 PL 和 PS 交互的基本工程。

## 6.1. AXI4-Lite 工程介绍

本章节主要介绍如何调用和新建一个带有 AXI 总线的工程，其中需要注意的是 PS 端的 ARM 配置和以及 AXI 总线模块设置，本例程相当于一个基础的 FPGA+ARM 的工程，不仅涉及到 PL 端，也需要添加 PS 端设备，此章节主要为后面的带有复杂的 AXI 总线工程打基础，希望大家能重视此章节。

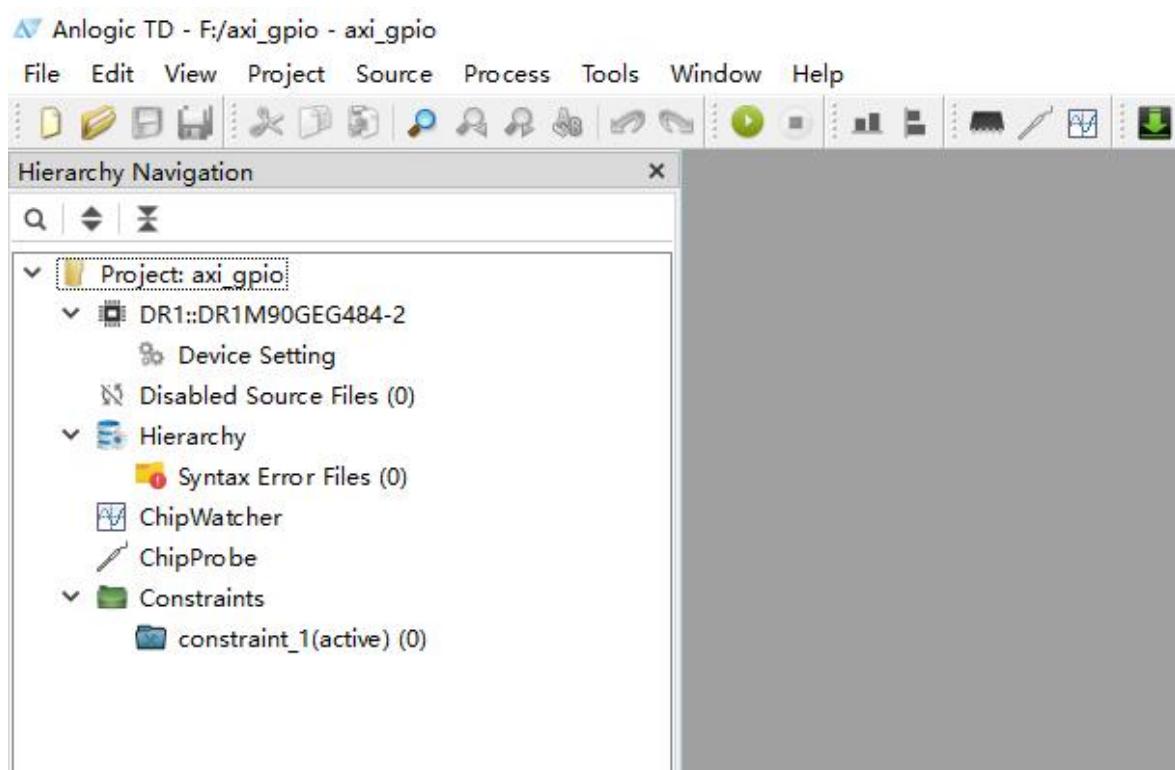

### 6.1.1. 新建 Axi\_gpio 工程

按照前面的教程新建一个 axi\_gpio 工程

图 6-1. axi\_gpio 工程

## 6.1.2. 打开 Design Integrator

点击 Tools-->Design Integrator

图 6-2. 打开 Design Integrator

## 6.1.3. 新建 Design

点击 Flow-->Create Design 新建 Design

图 6-3. 新建 Design

点击 OK，选择新建的 Design 的存储位置

图 6-4. 新建 design 设置

#### 6.1.4. 调用 PS 端 IP

点击添加 ip 图标，双击 ARM Processor System 模块

图 6-5. 调用 ps 端 ip

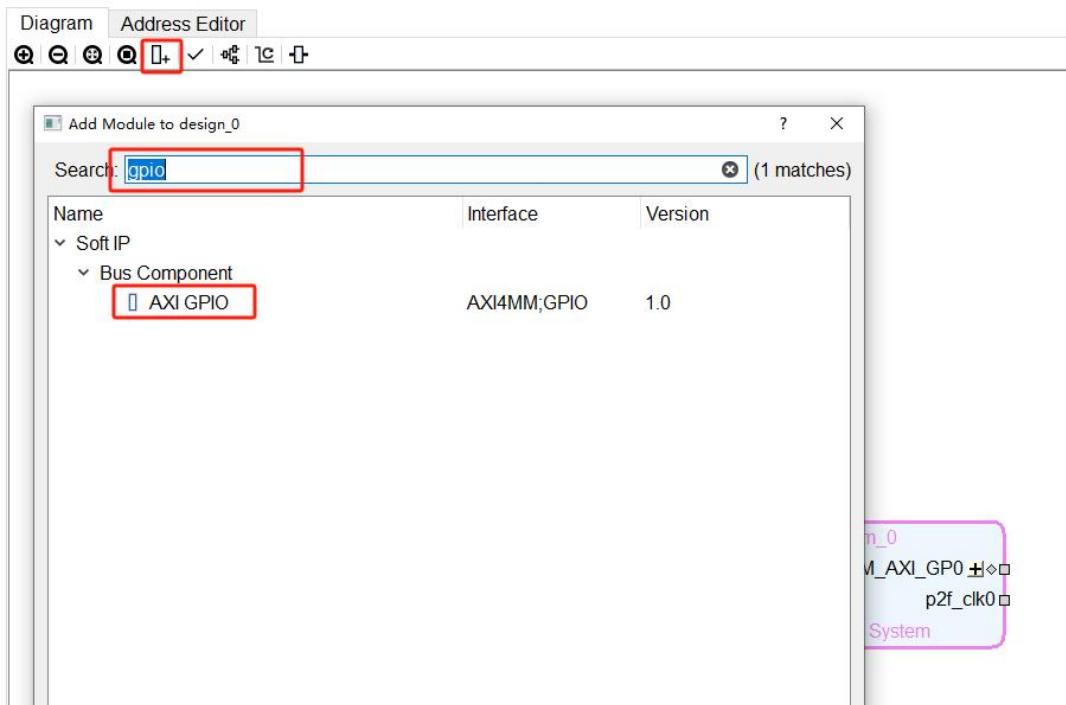

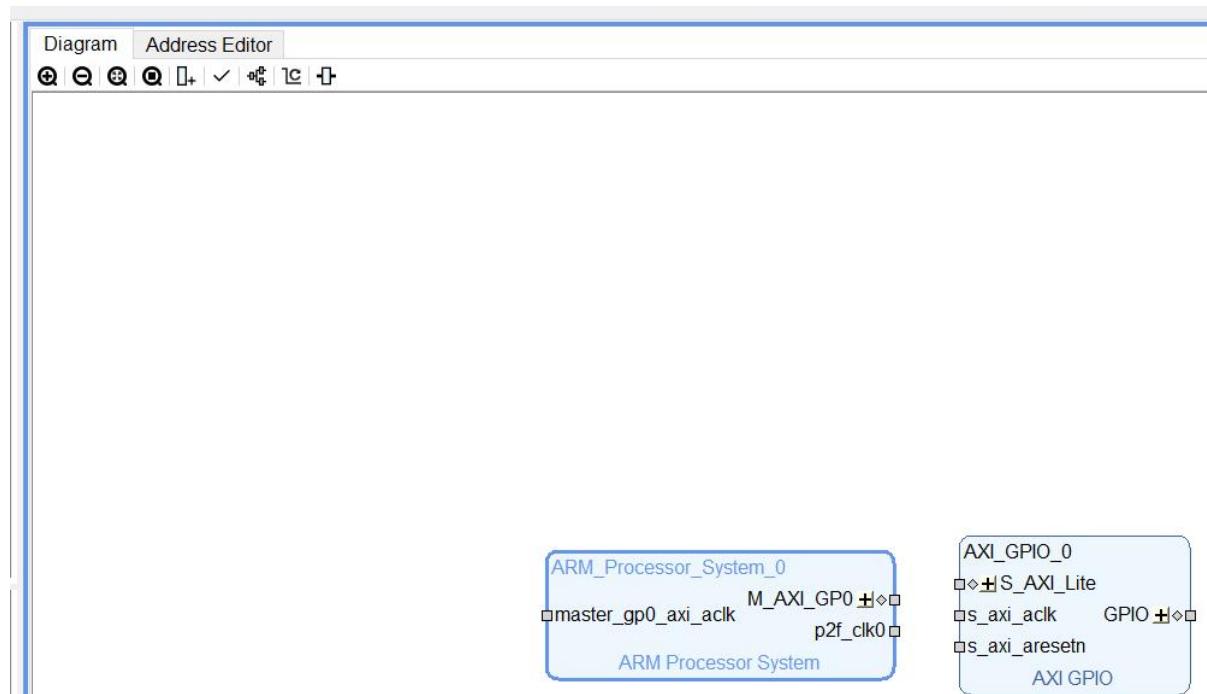

点击添加 ip 的快捷键，在搜索栏输入 gpio，双击 AXI GPIO 调用 GPIO 模块

图 6-6. 调用 axi\_gpio

调用的 gpio 模块，如下图所示

图 6-7. 调用的 axi\_gpio 模块

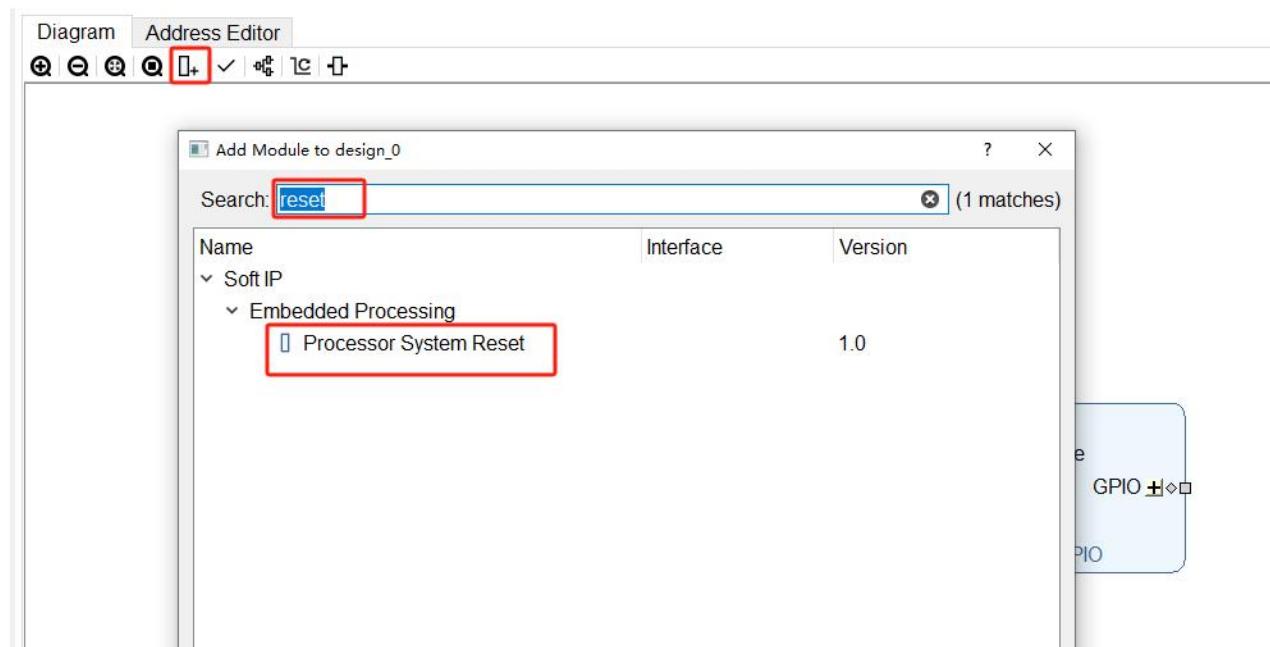

点击添加 ip 的快捷键，在搜索栏输入 reset，双击 Processor System Reset 添加复位模块

图 6-8. 调用 System Reset 复位模块

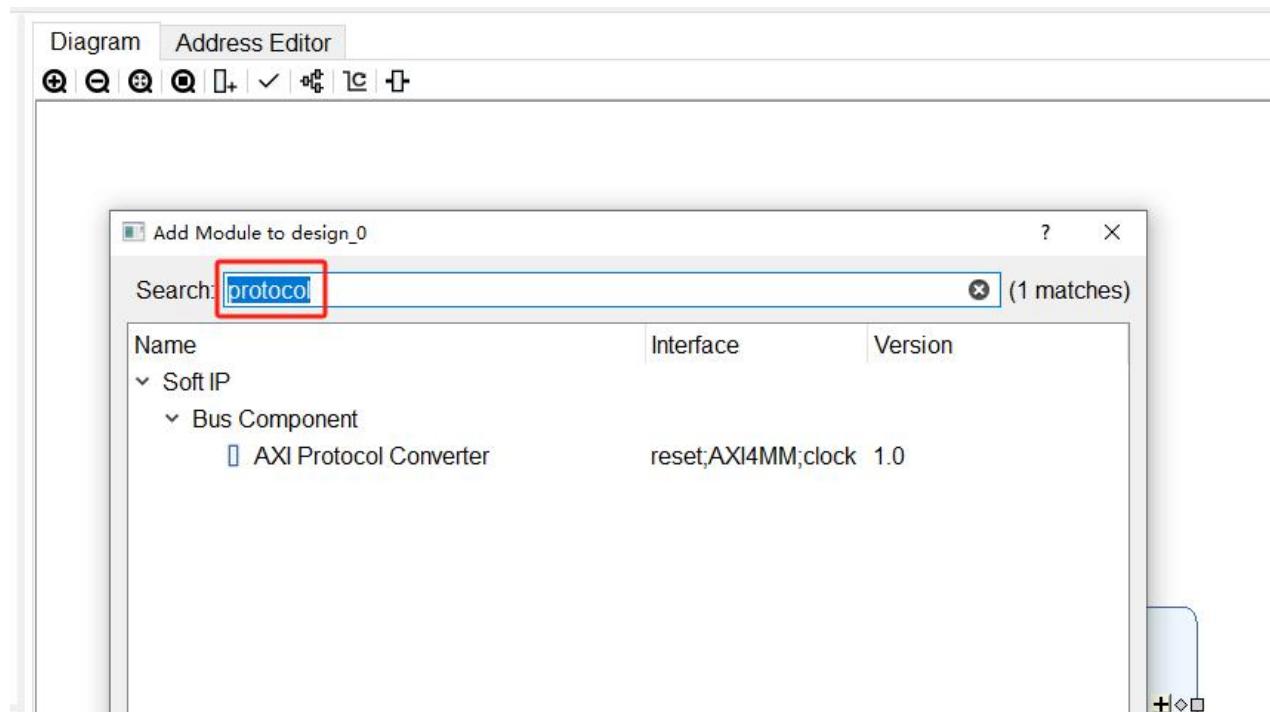

在搜索栏输入 protocol，双击 AXI Protocol Converter 添加 axi 协议转换模块

图 6-9. 调用 axi 转换模块

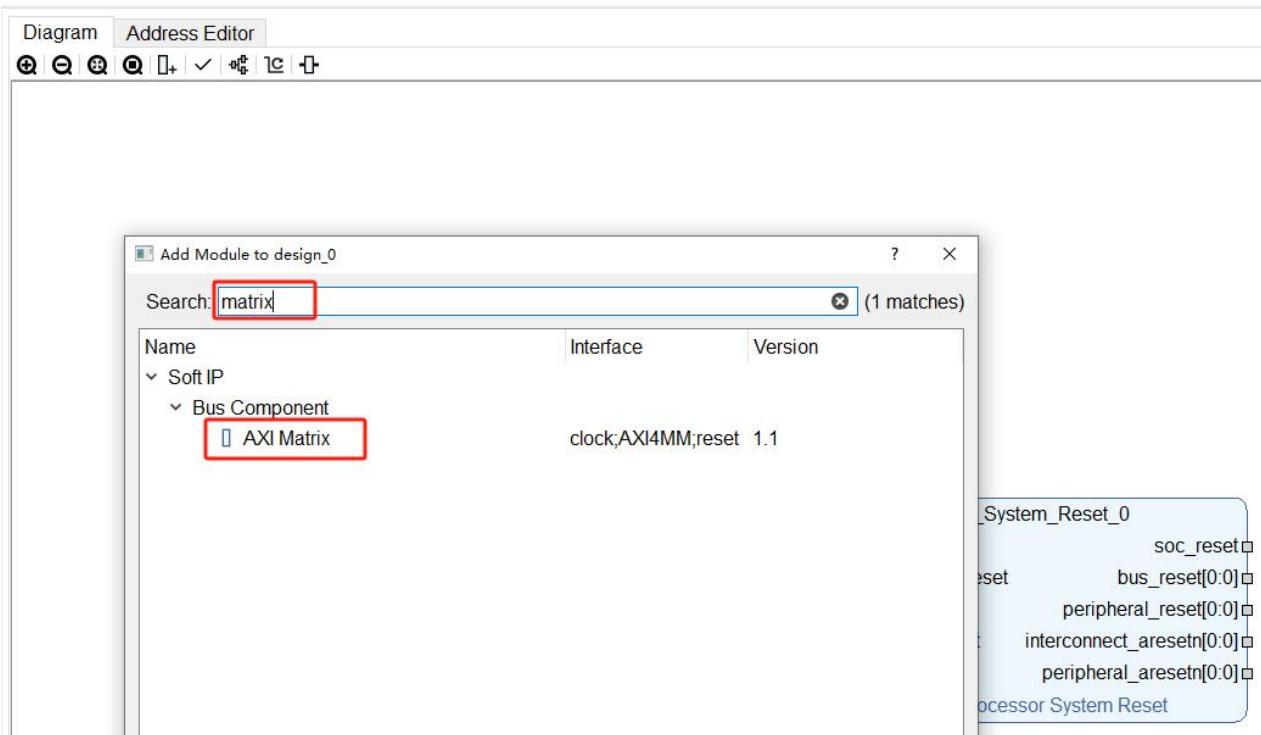

在搜索栏输入 matrix，双击 AXI Matrix 添加 axi 扩展模块

图 6-10. 调用 axi 扩展模块

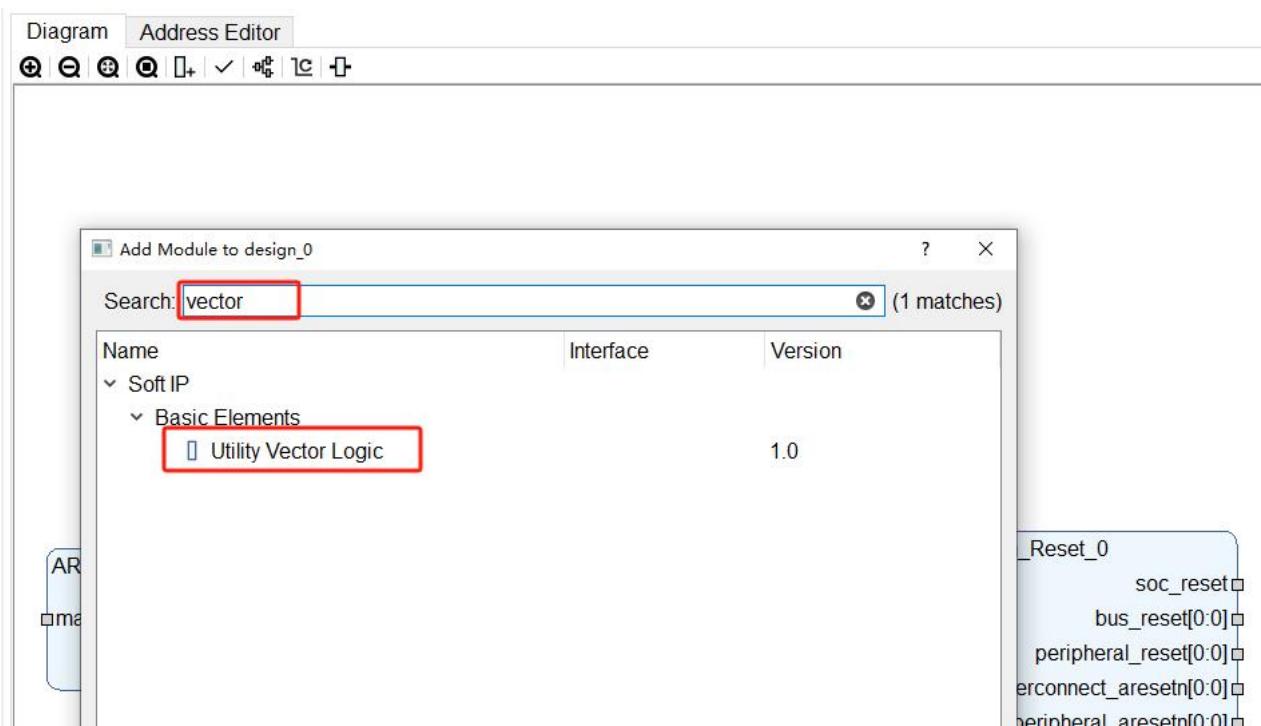

在搜索栏输入 vector，双击 Utility Vector Logic 添加模块

图 6-11. 调用 Utility Vector Logic 模块

## 6.1.5. 配置 PS 端 IP

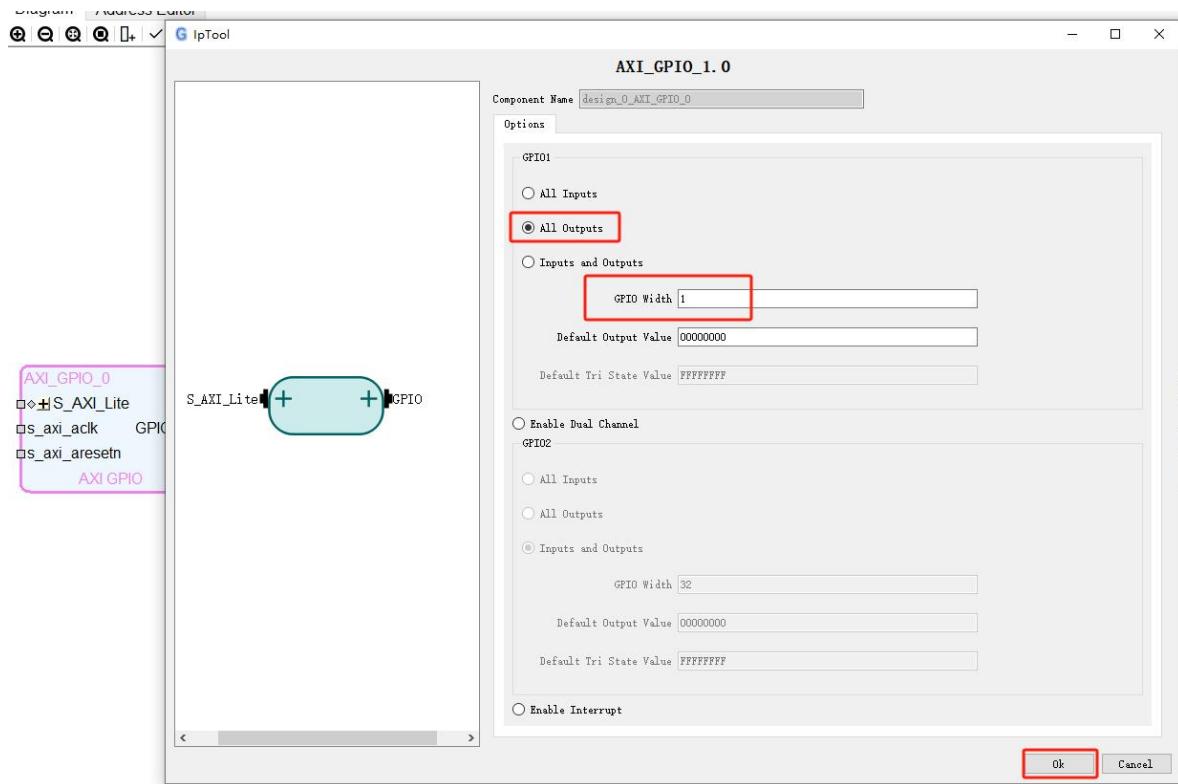

双击 axi\_gpio 模块，设置为输出口，设置 gpio 位宽为 1，然后点击 OK

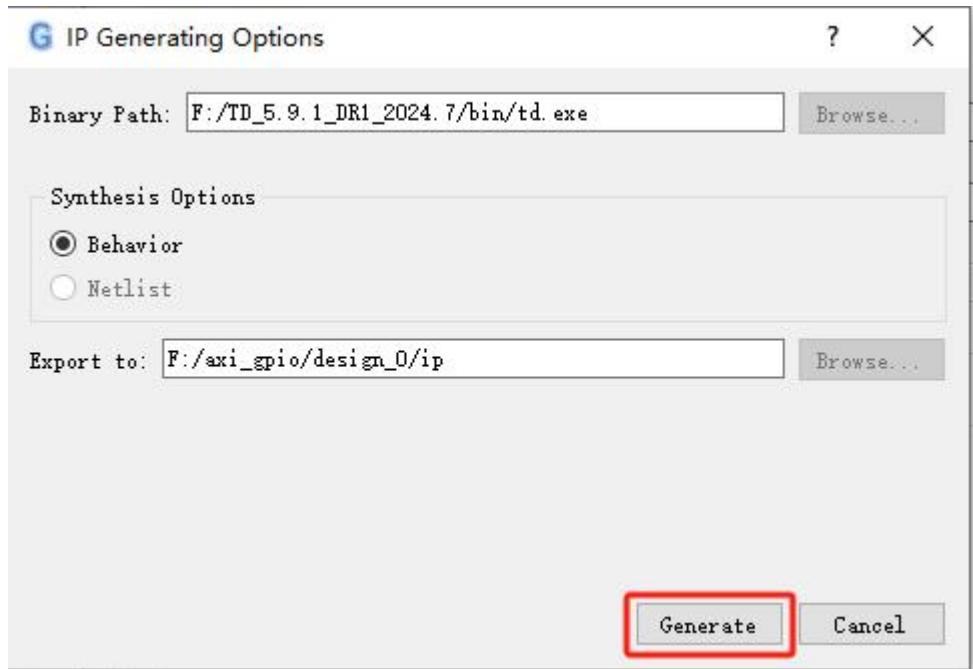

在弹出的对话框点击 Generate 生成配置

图 6-12. 设置 gpio 模块

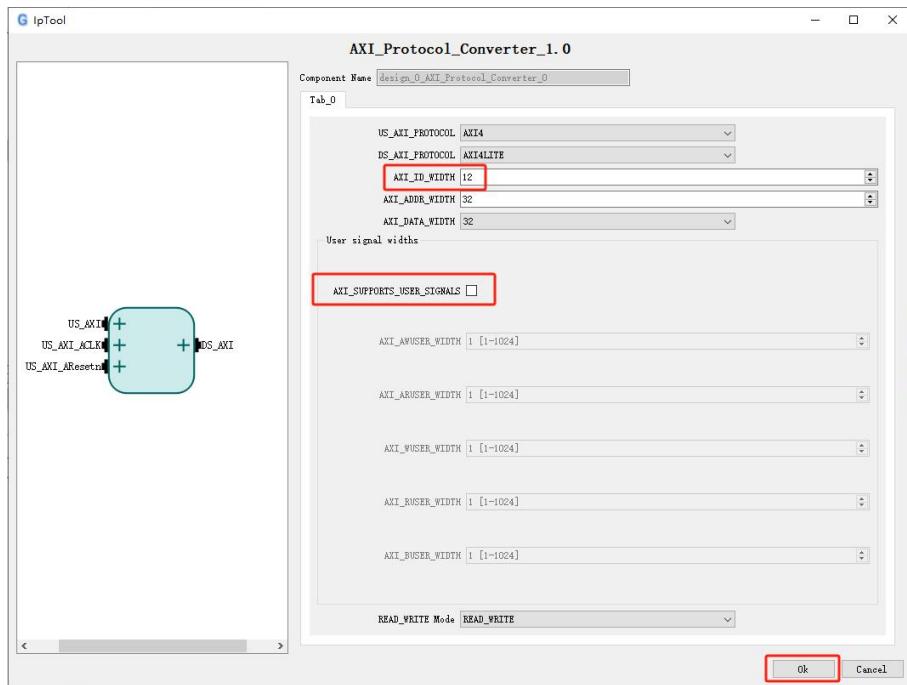

双击 AXI Protocol Converter 模块，设置 ID 位宽为 12，去掉 AXI\_SUPPORTS\_USER\_SIGNALS 勾选，然后点击 OK

图 6-13. 设置 AXI Protocol Converter 模块

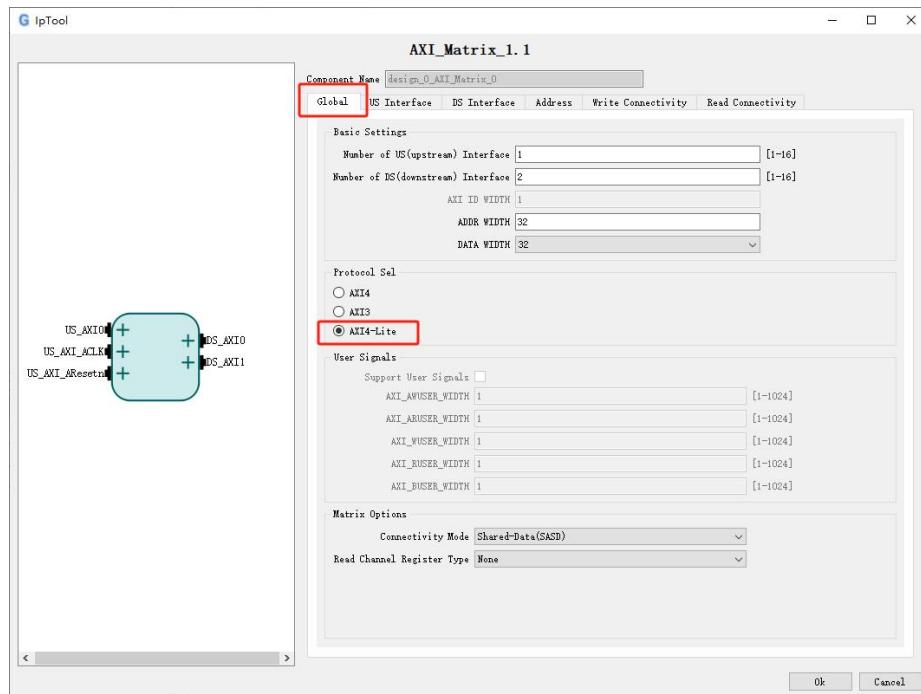

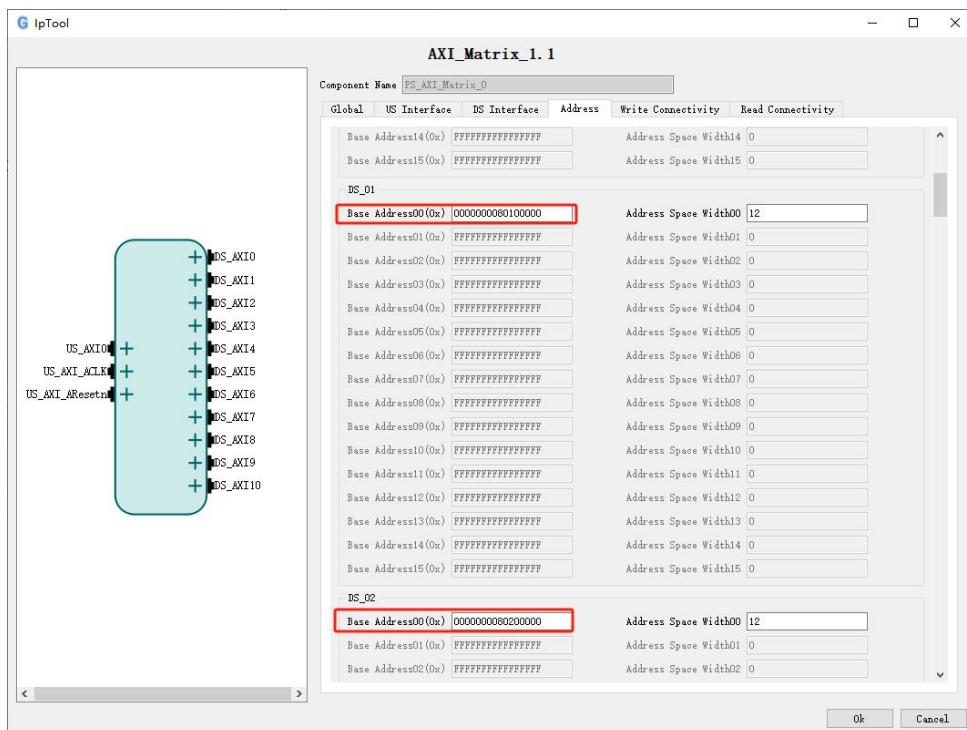

双击 AXI Matrix 模块，在 Global 选项卡，选择 AXI4-Lite

图 6-14. 设置 AXI Matrix 模块总线类型

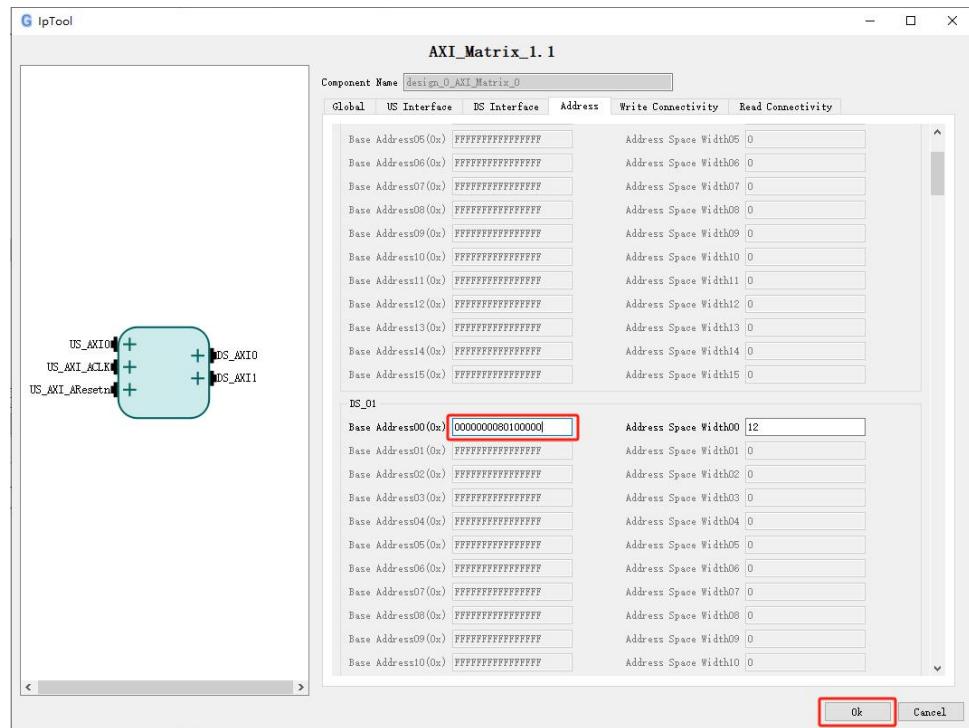

在 AXI Matrix 模块，在 Address 选项卡，设置通道 DS\_01 基地址为 0x80100000，然后点击 OK

图 6-15. 设置 AXI Matrix 模块总线地址

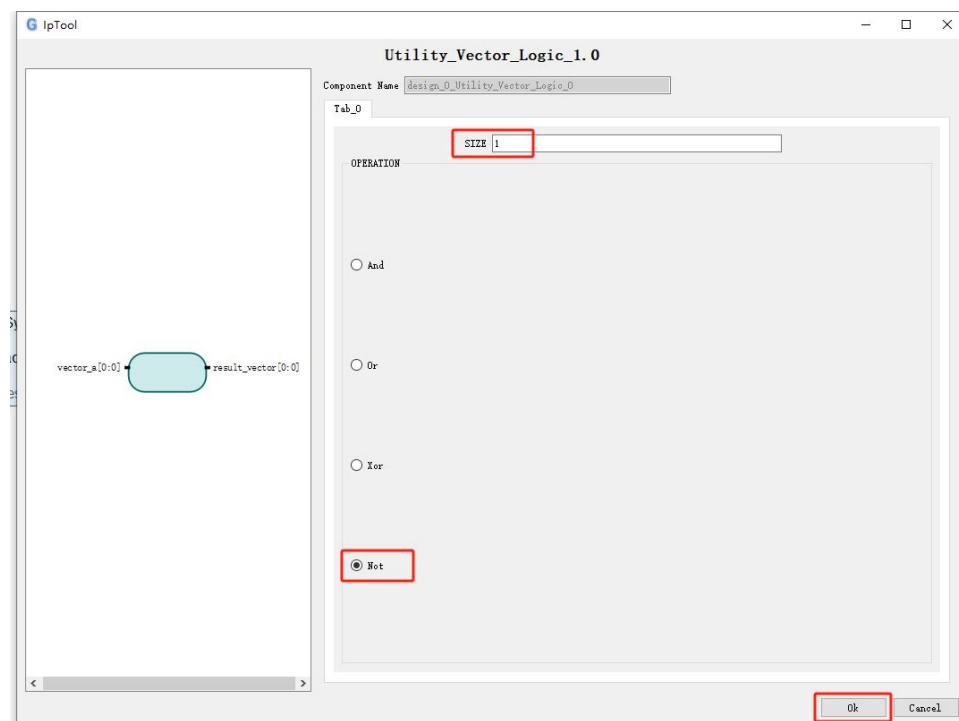

双击 Utility Vector Logic 模块，设置 SIZE 为 1，设置类型为 Not，然后点击 OK

图 6-16. 设置 Utility Vector Logic 模块

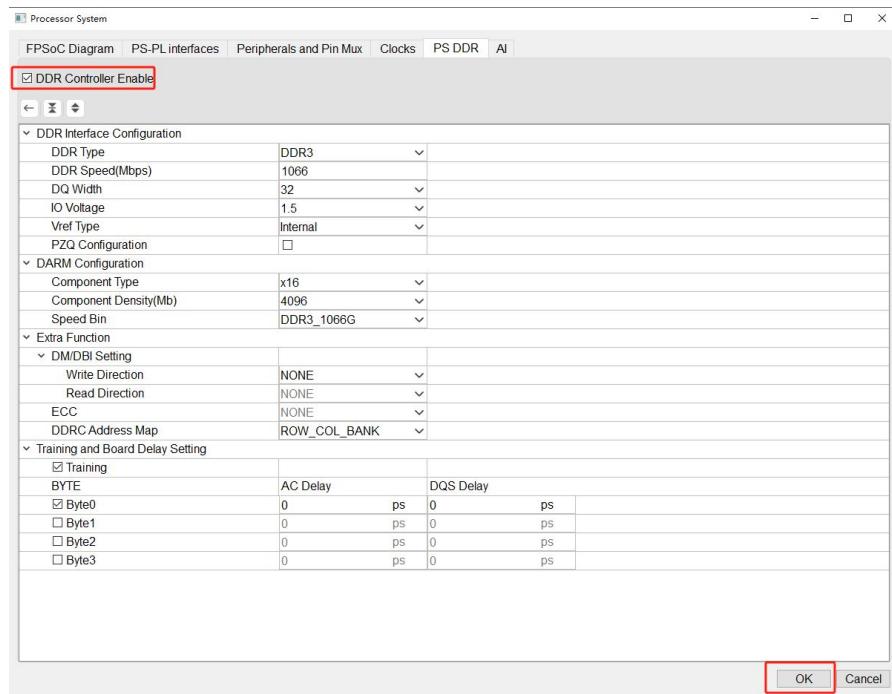

双击 ARM Processor System 模块，在 PS DDR3 选项卡勾选 DDR Controller Enable,然后按照截图中参数配置 DDR，配置完成后点击 OK

图 6-17. 设置 Utility Vector Logic 模块

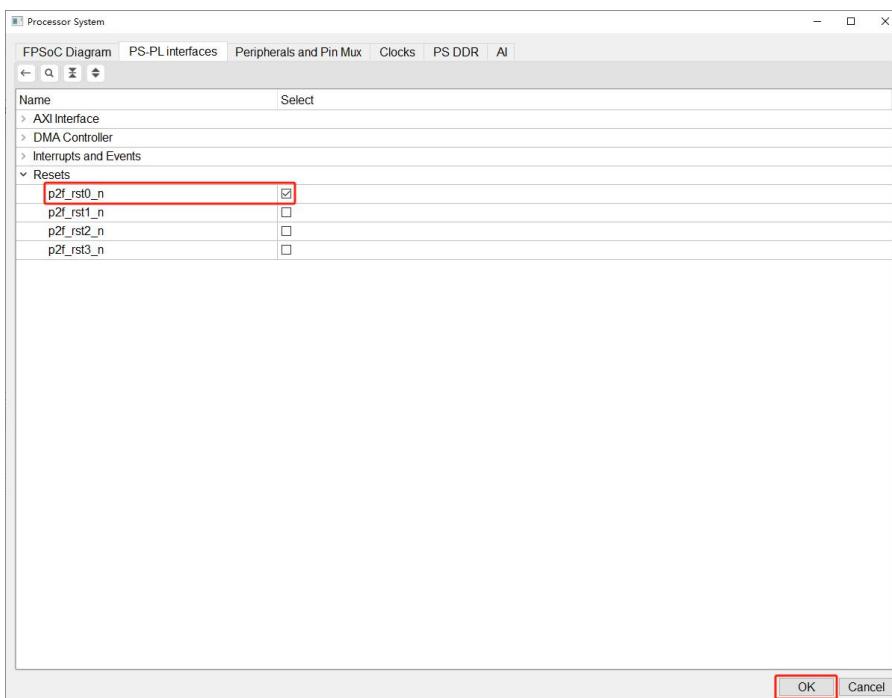

双击 ARM Processor System 模块，在 PS-PL interfaces 选项卡勾选 p2f\_rst0\_n 输出 PS 复位管脚

图 6-18. 设置 PS 复位管脚

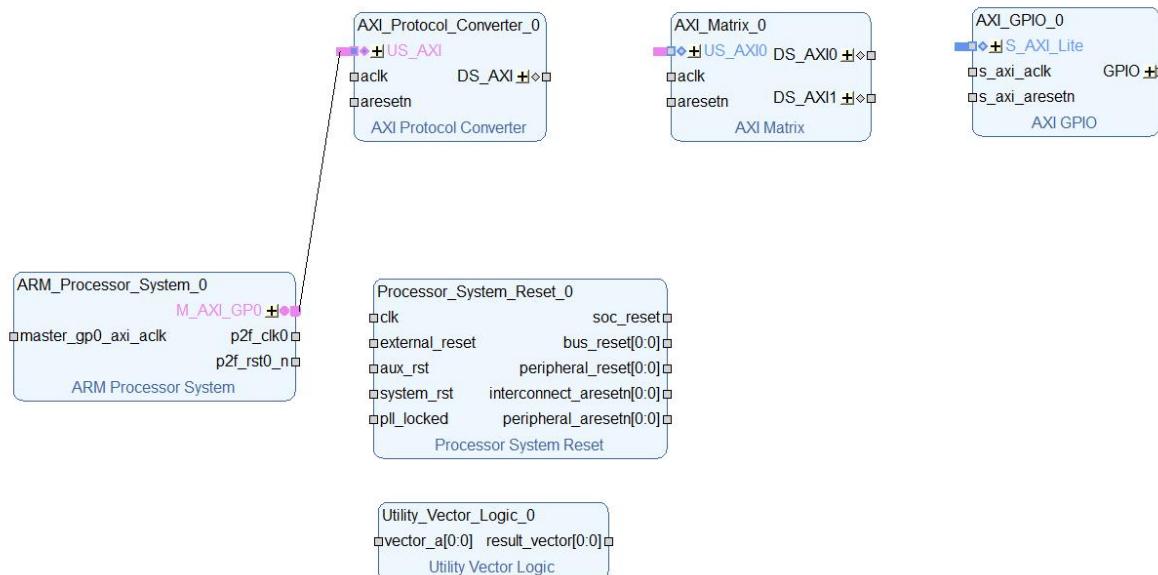

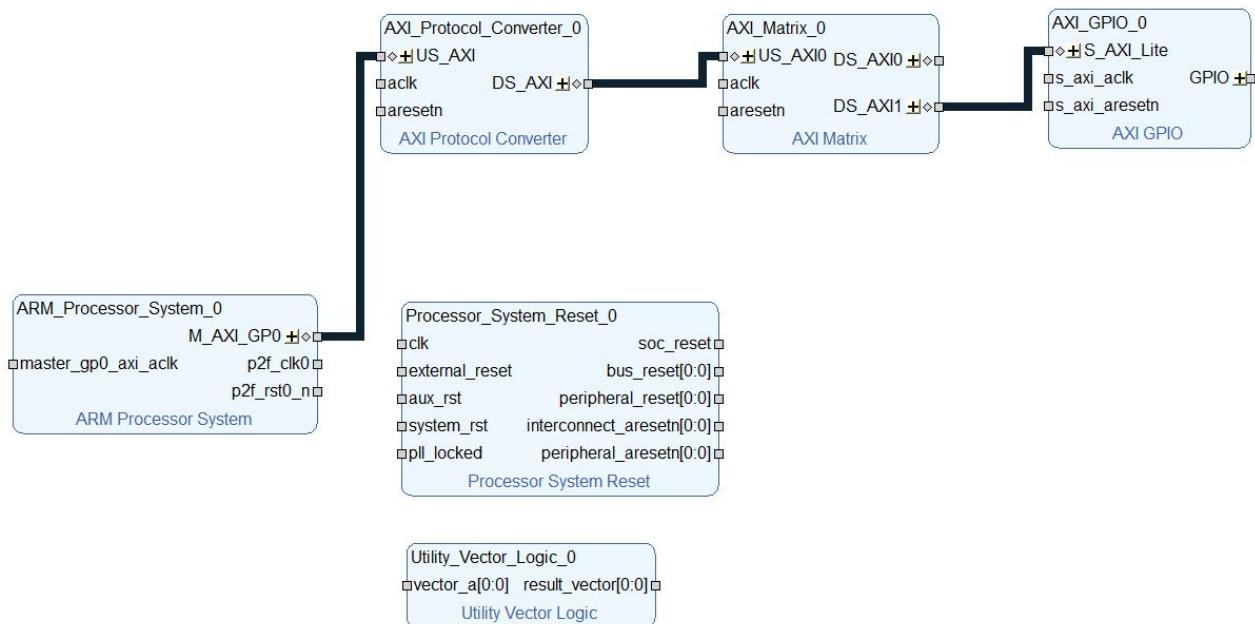

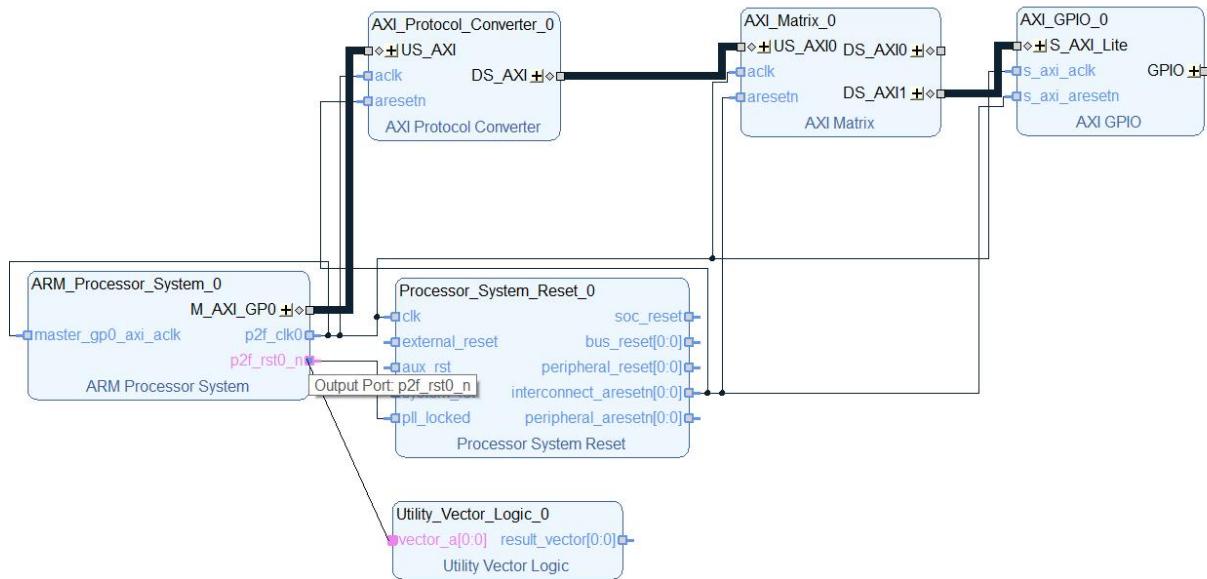

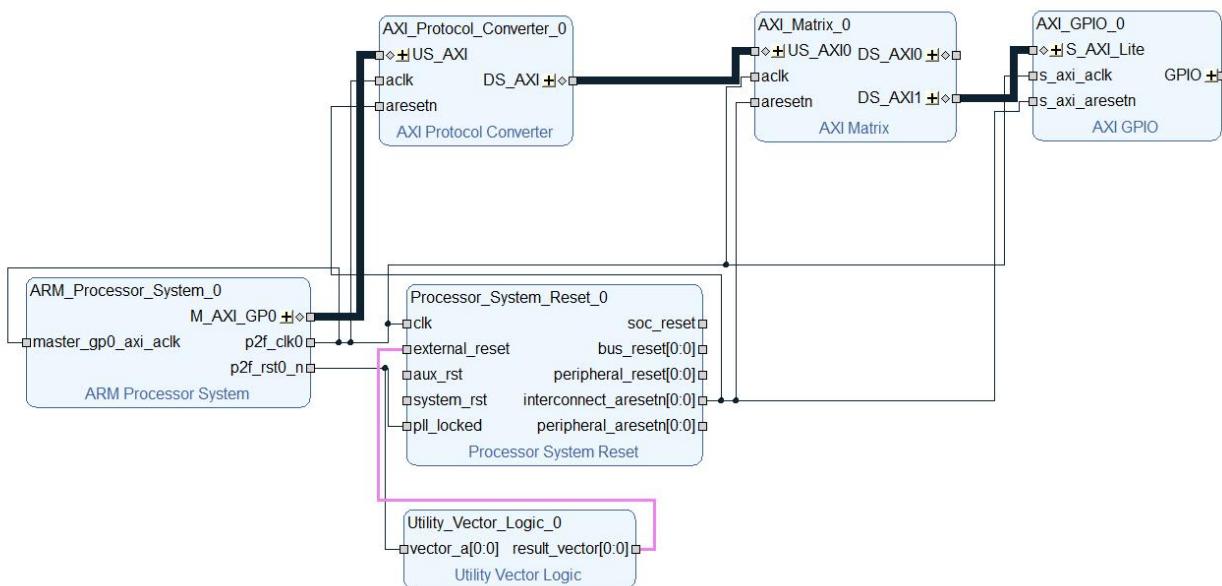

## 6.1.6. PS 端模块连接

双击 GP 总线接口，待总线出现导线将其拉到 US\_AXI 接口

图 6-19. 总线连接

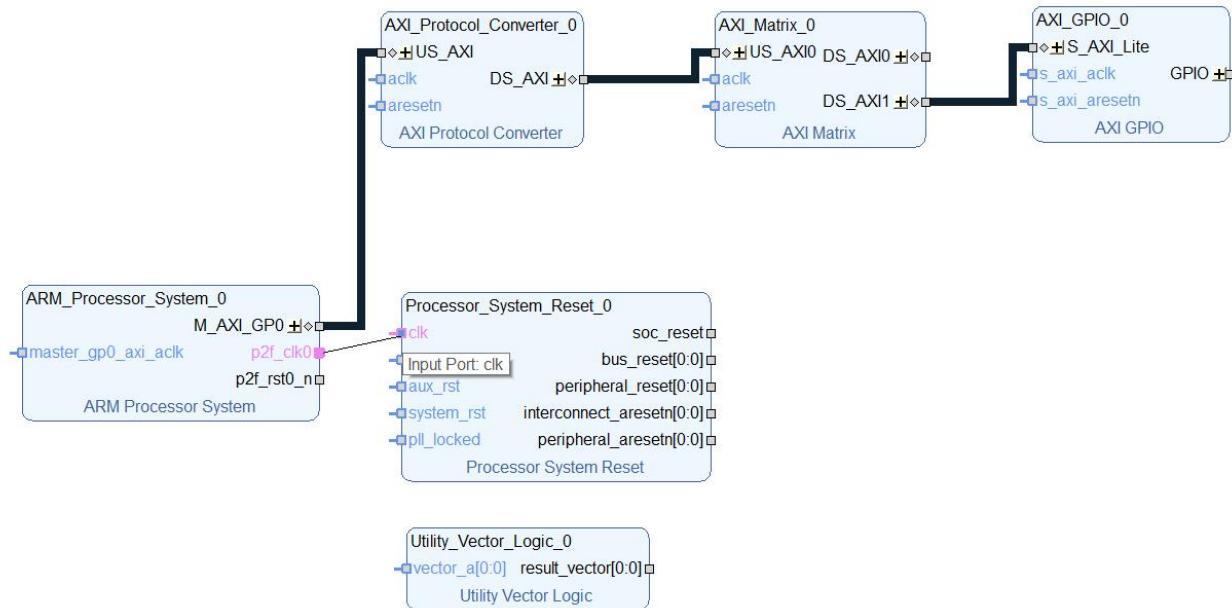

将其它的 axi 总线按照同样的方法连接起来，如下图所示

图 6-20. 连接 axi 总线

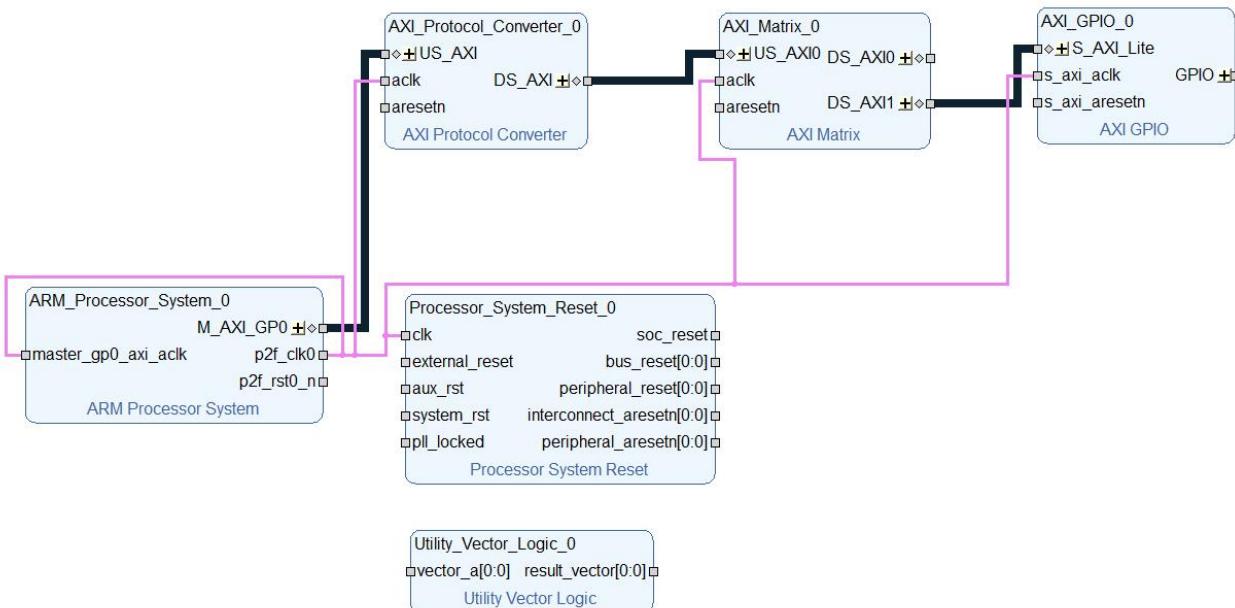

在 p2f\_clk0 上双击，待变成线条后连接 clk 管脚

图 6-21. 连接 PS 时钟

按照上面的方法连接所有模块的时钟管脚

图 6-22. 连接所有时钟管脚

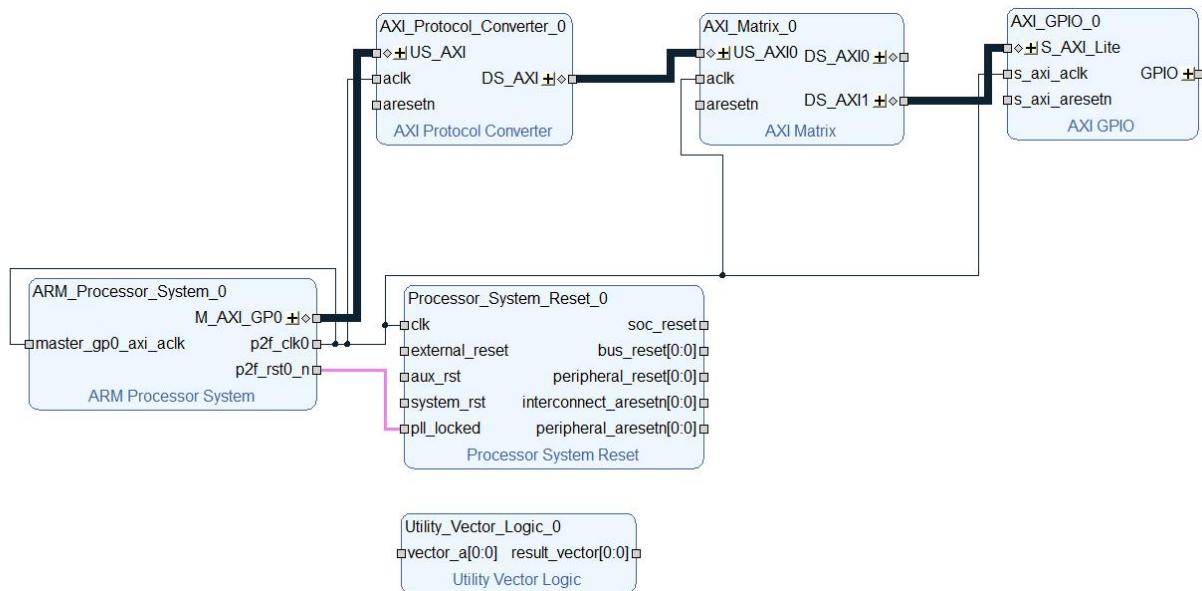

将 PS 复位管脚连接复位模块 pll\_locked 管脚

图 6-23. 连接模块复位管脚

将系统复位模块输出的复位管脚，连接其它 axi 总线的复位管脚

图 6-24. 连接 axi 总线复位管脚

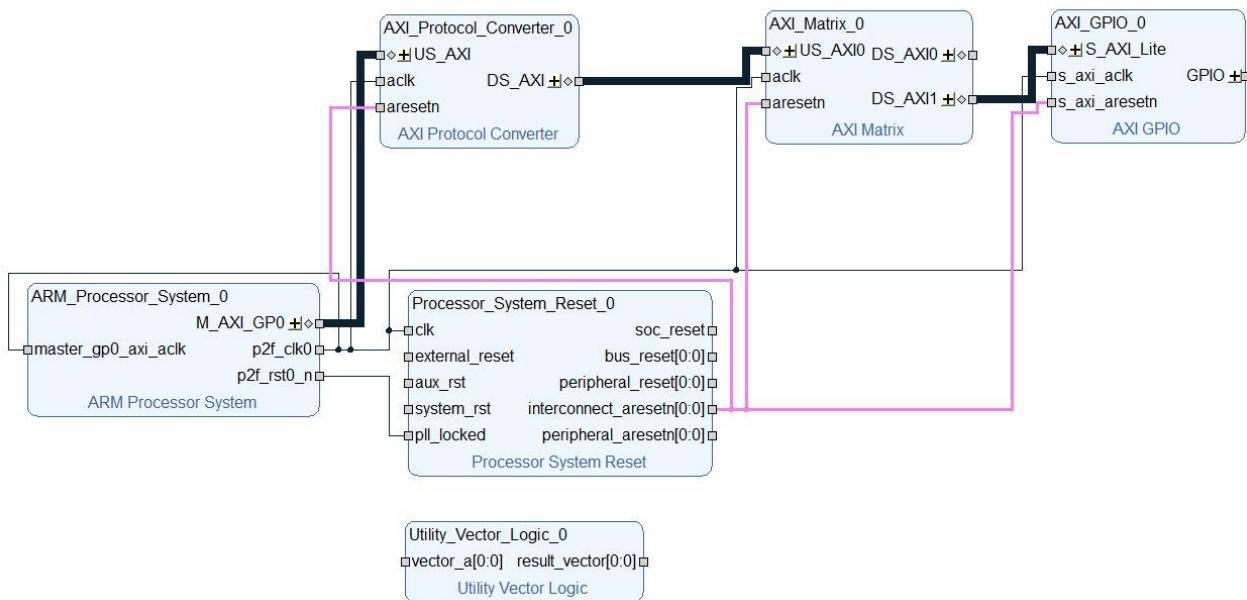

将 Utility Vector Logic 模块的输入端口连接 p2f\_rst0\_n 管脚

图 6-25. 将 Utility Vector Logic 模块连接 PS 复位管脚

将 Utility Vector Logic 模块输出，连接到系统复位模块的 external\_reset 管脚

图 6-26. 将 Utility Vector Logic 模块输出连接系统复位模块管脚

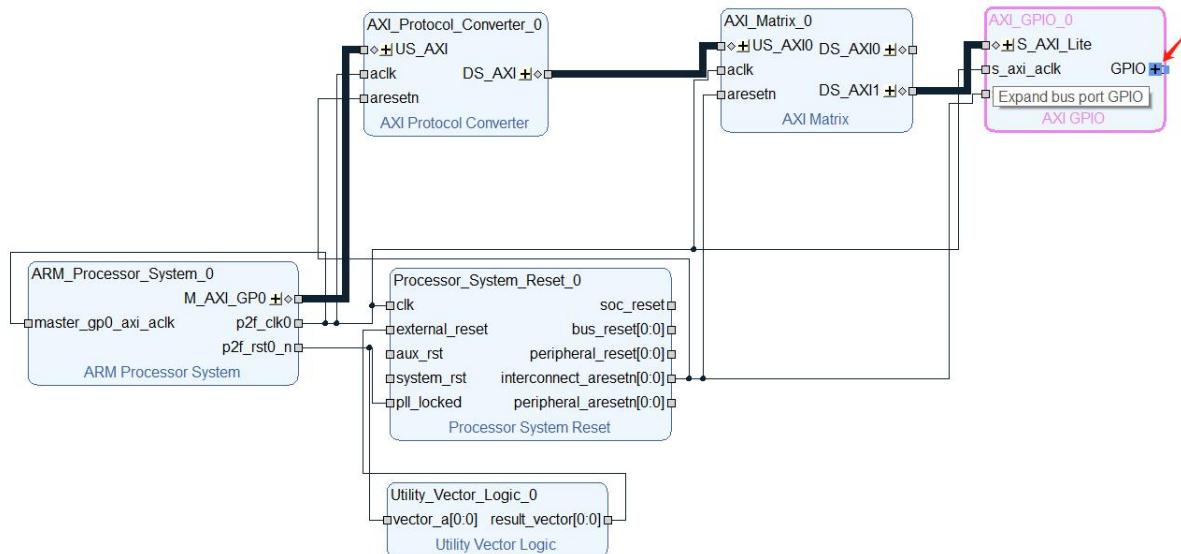

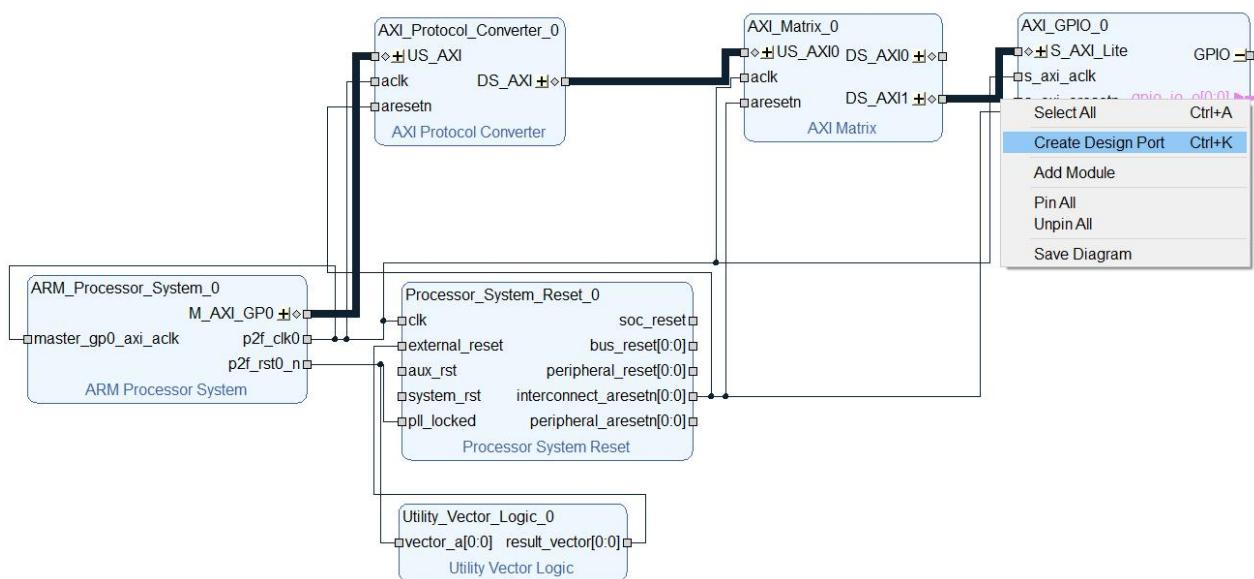

### 6.1.7. PS 端管脚输出配置

用鼠标点击 GPIO 管脚的+号，展开 GPIO 的管脚

图 6-27. 展开 GPIO 模块管脚

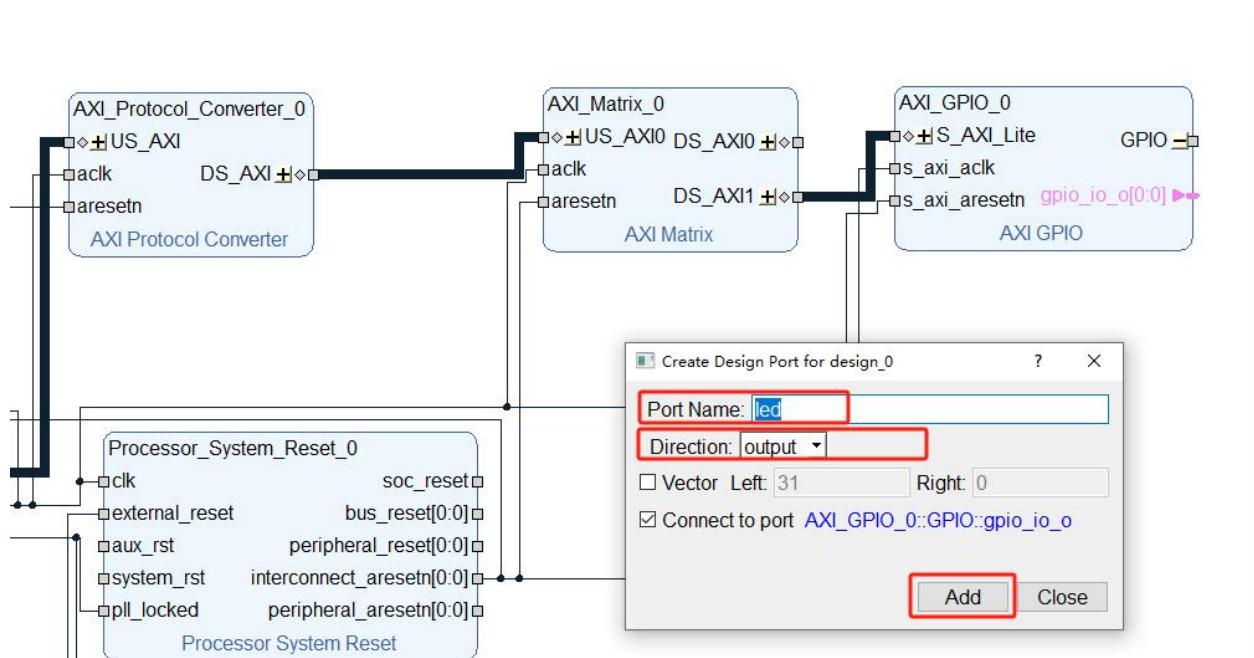

在展开的 GPIO 模块上右击选择 Create Design Port 引出 GPIO 管脚

图 6-28. 引出 GPIO 模块管脚

在弹出的 GPIO 管脚设置对话框，填写管脚名称为 led，设为输出管脚，然后点击 Add 添加管脚，设置完成后点击 Close 管脚对话框

图 6-29. GPIO 管脚输出设置

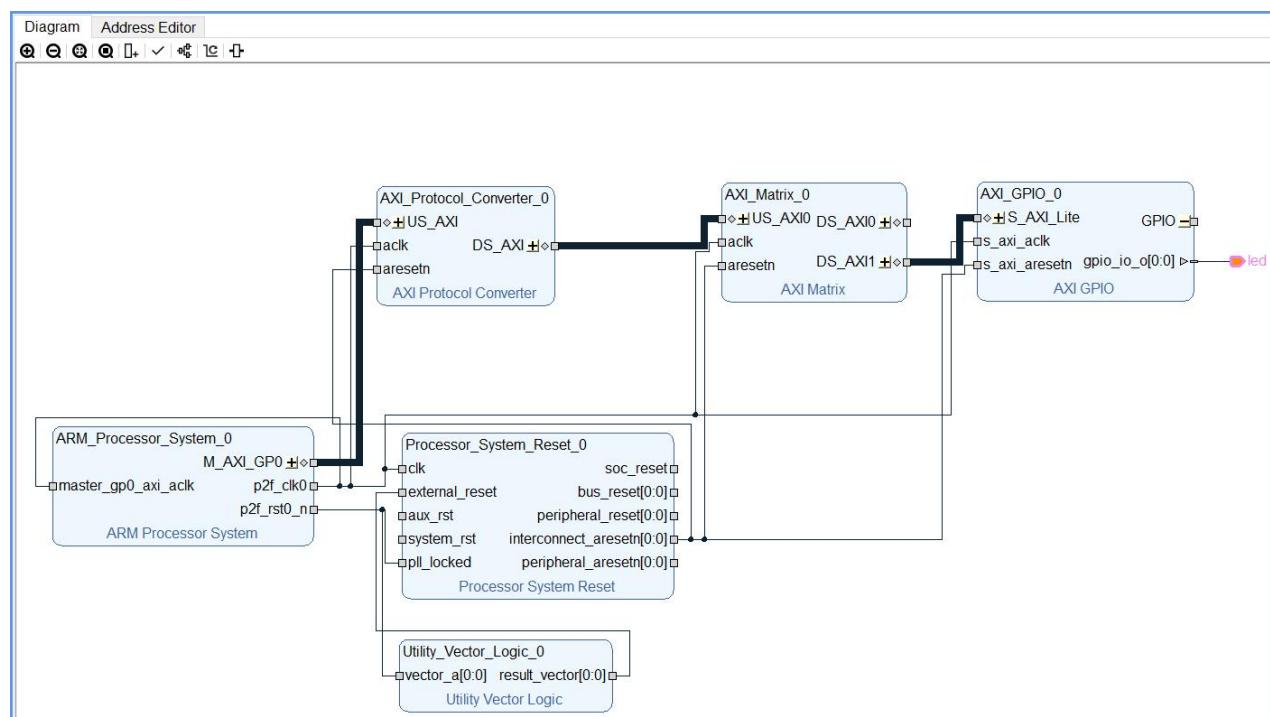

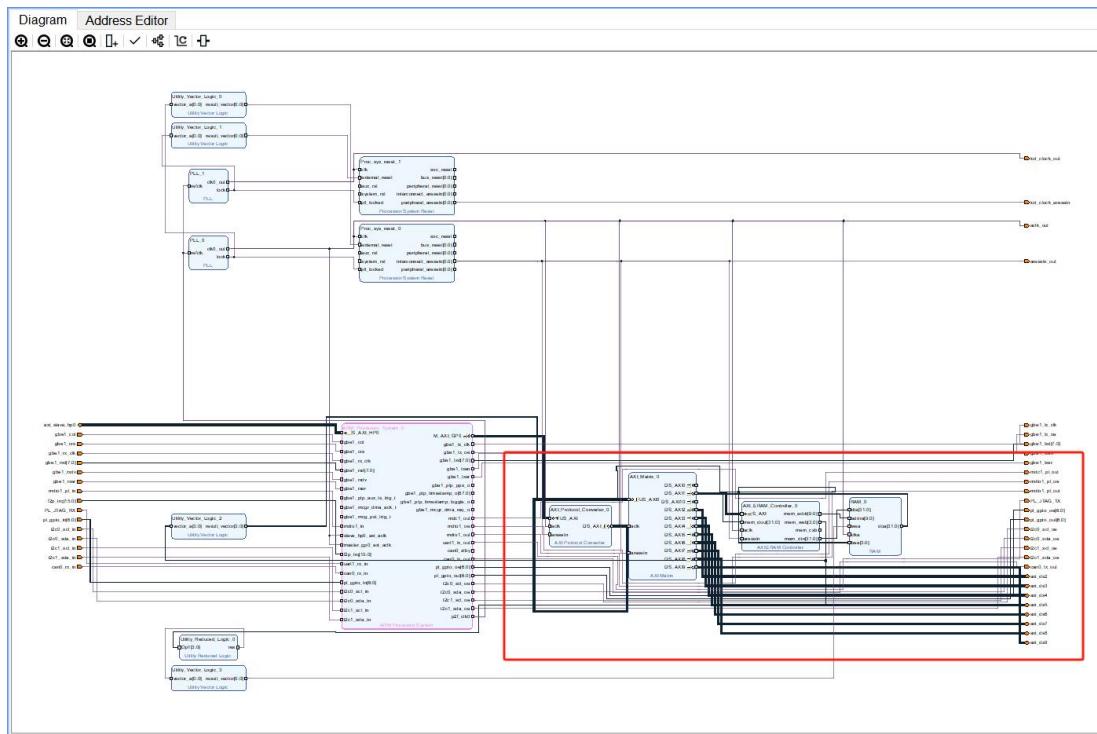

axi\_gpio 工程所有模块连接方式，如下图所示

图 6-30. axi\_gpio 工程连接图

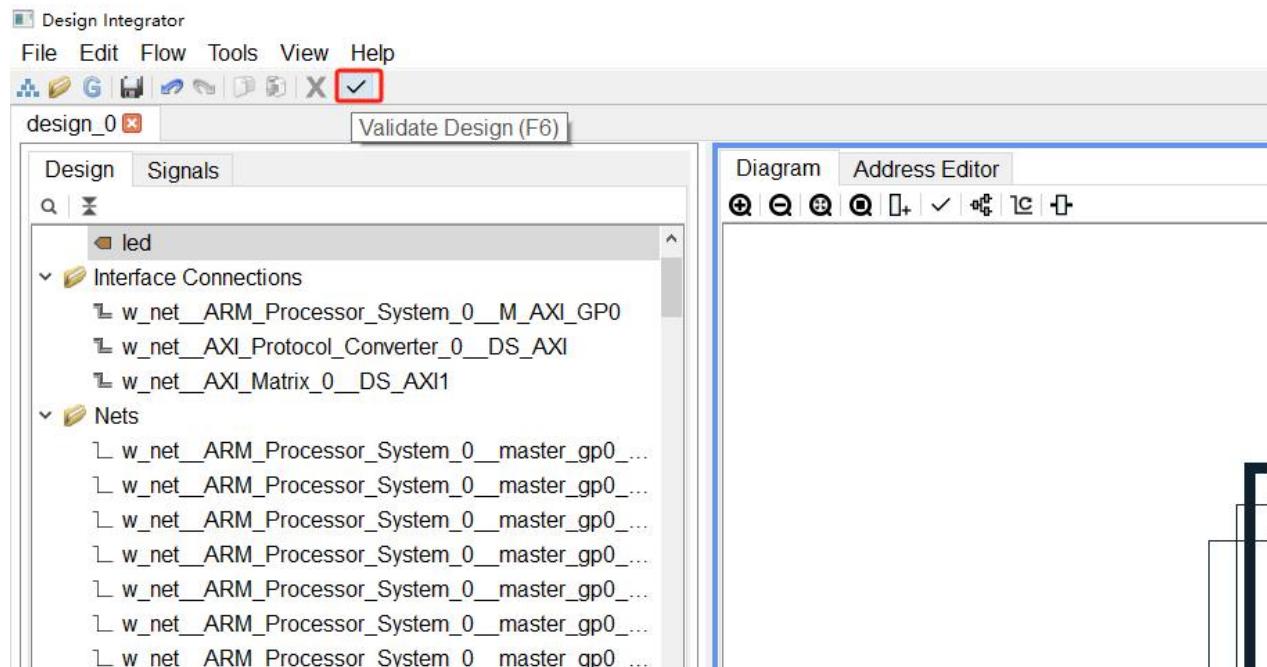

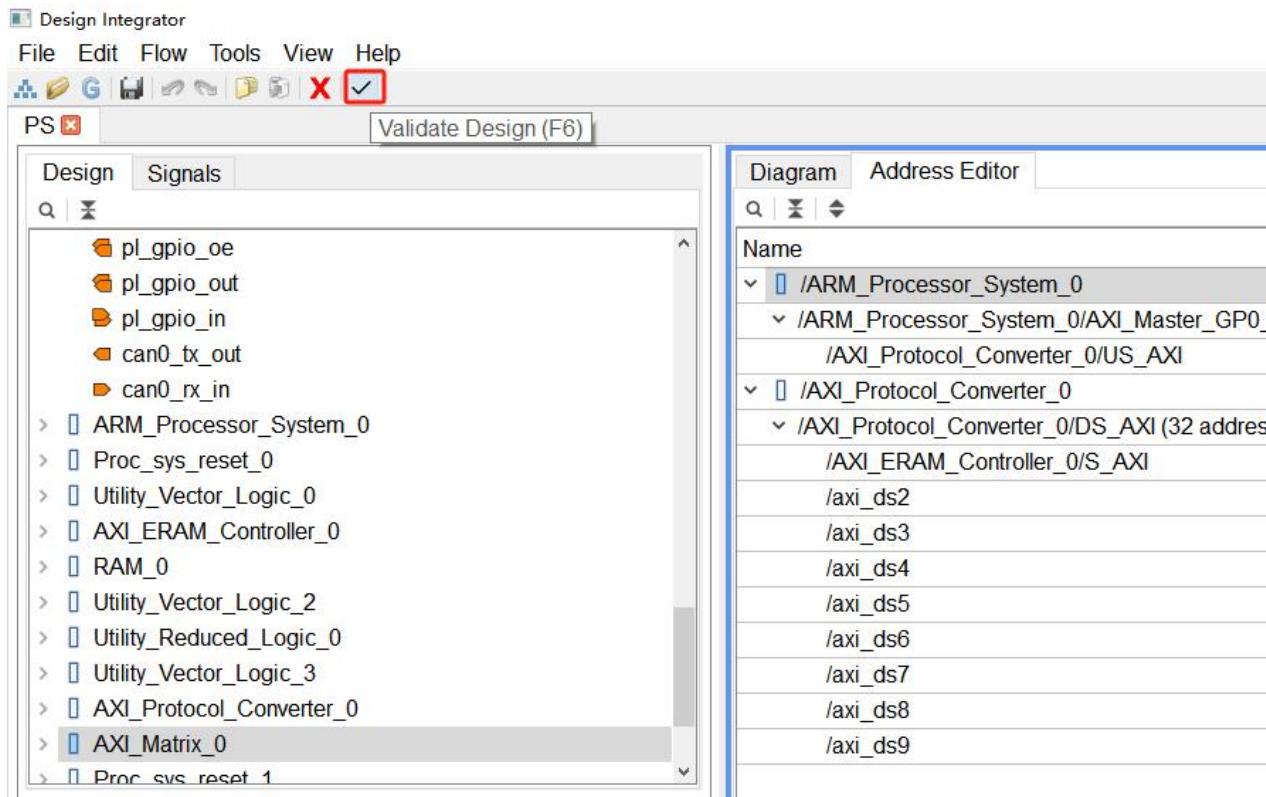

## 6.1.8. PS 端工程设计验证

点击 Validate Design 验证设计，看工程是否有报错

图 6-31. 验证工程设计

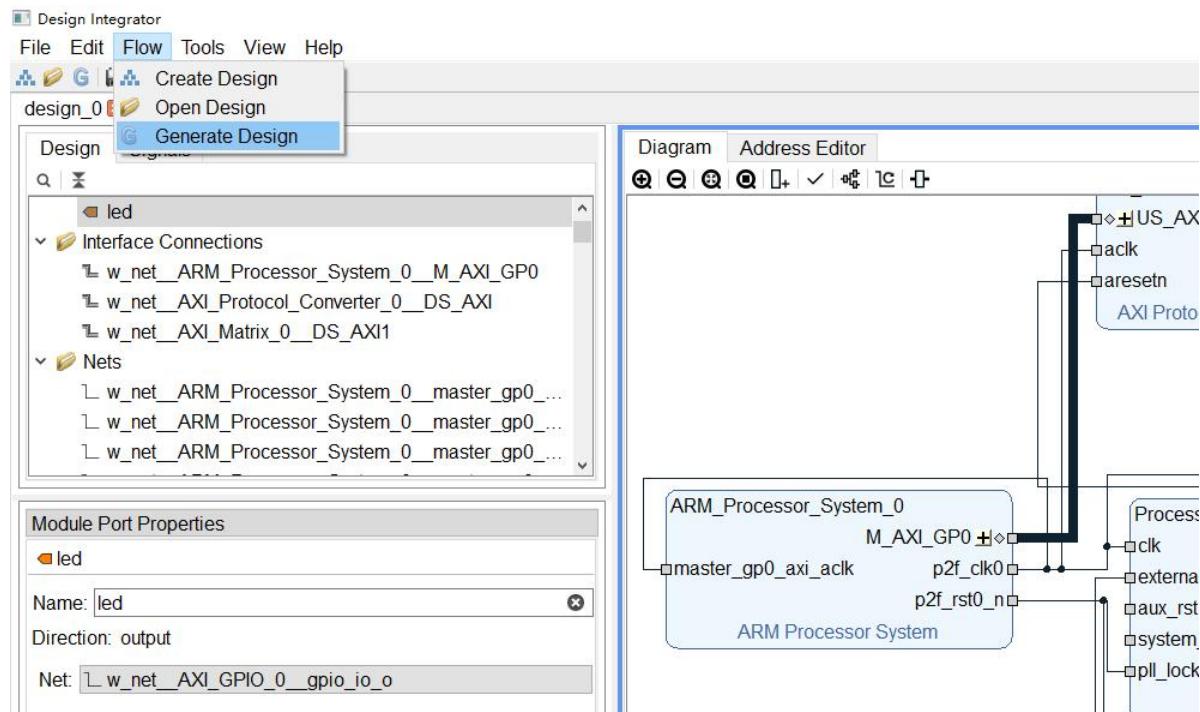

## 6.1.9. PS 端导出 Design

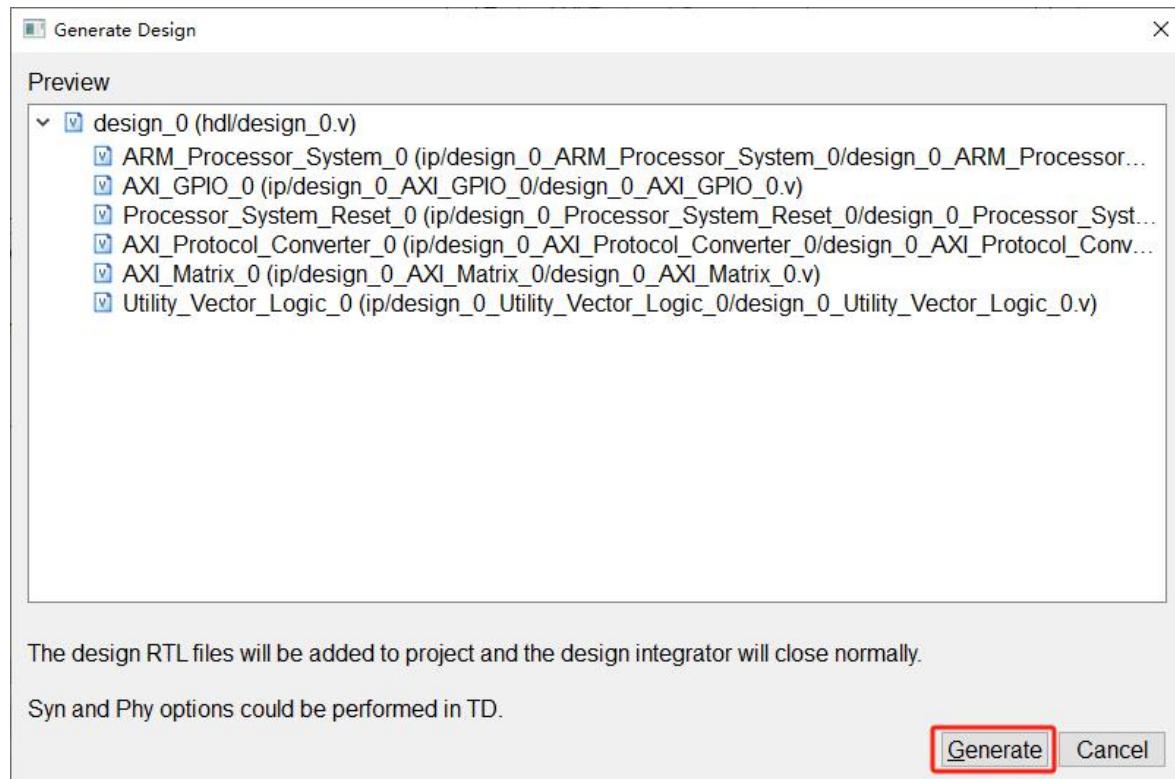

点击 Flow-->Generate Design 导出 Design

在弹出的对话框中点击 Generate

图 6-32. 导出 Design 工程设计

生成的 design\_0 模块 ip

图 6-33. 生成的 ps 模块 ip

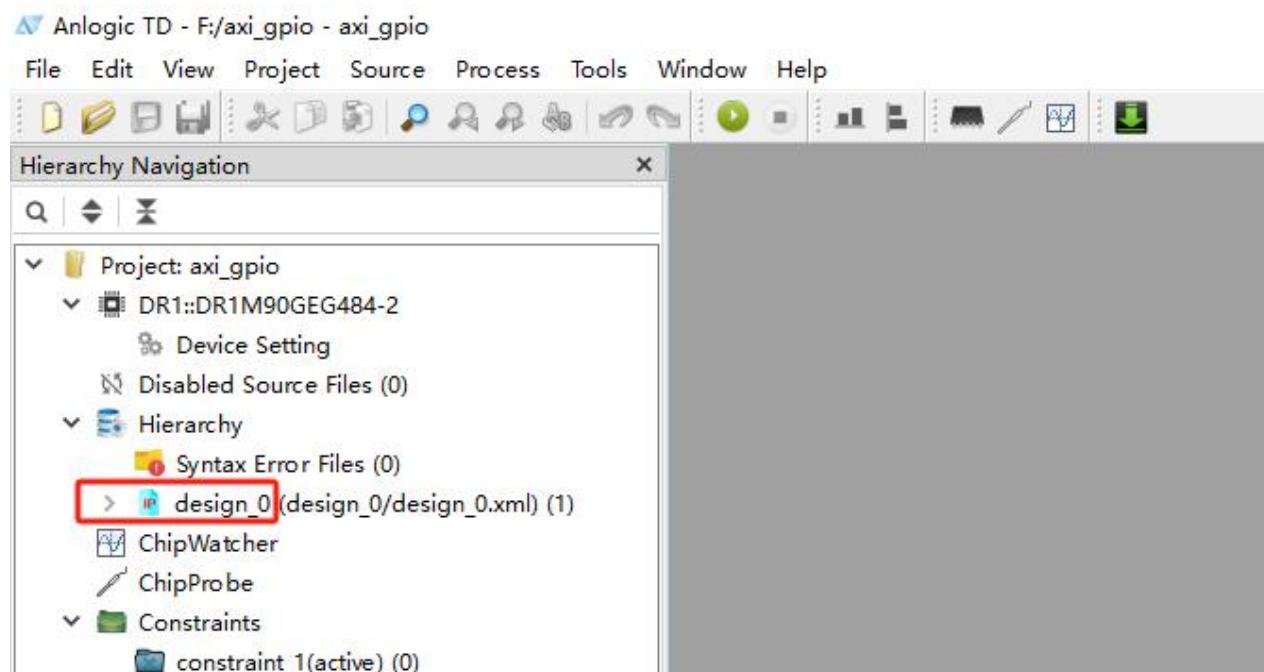

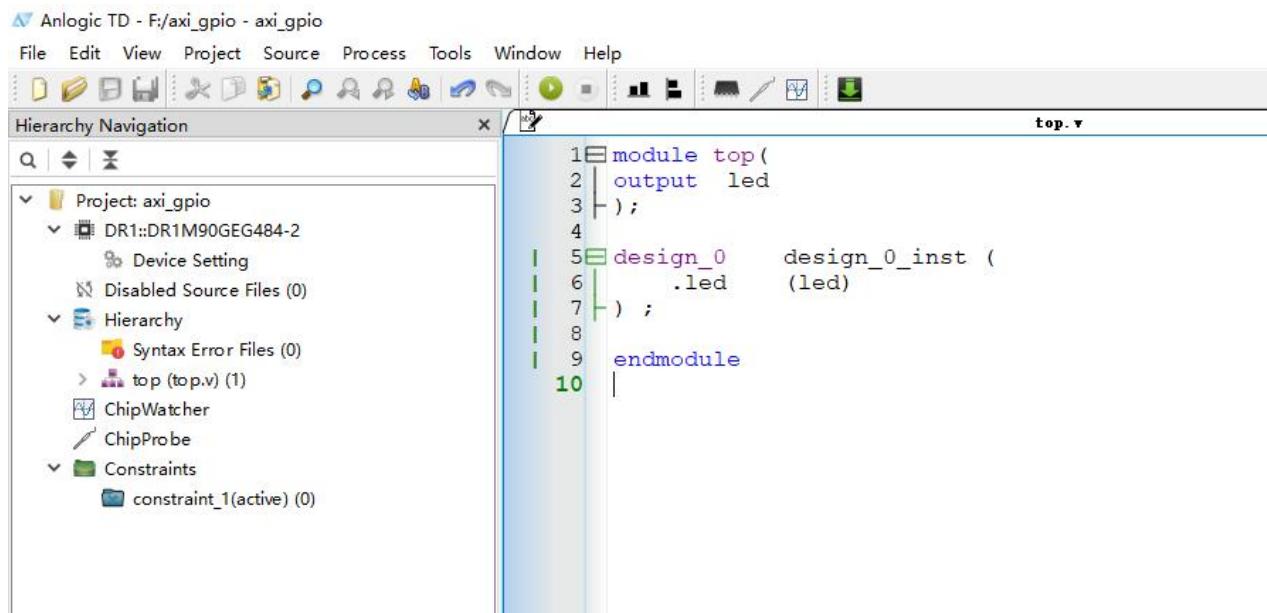

## 6.1.10. 顶层例化 Design

新建一个模块 top，例化 ps 端模块(这个步骤如果不熟悉，可以参考前面章节的详细步骤)

```

1 module top(

2   output led

3 );

4

5   design_0      design_0_inst (

6     .led        (led)

7   );

8

9 endmodule

10

```

图 6-34. 将 ps 模块例化到 top 模块

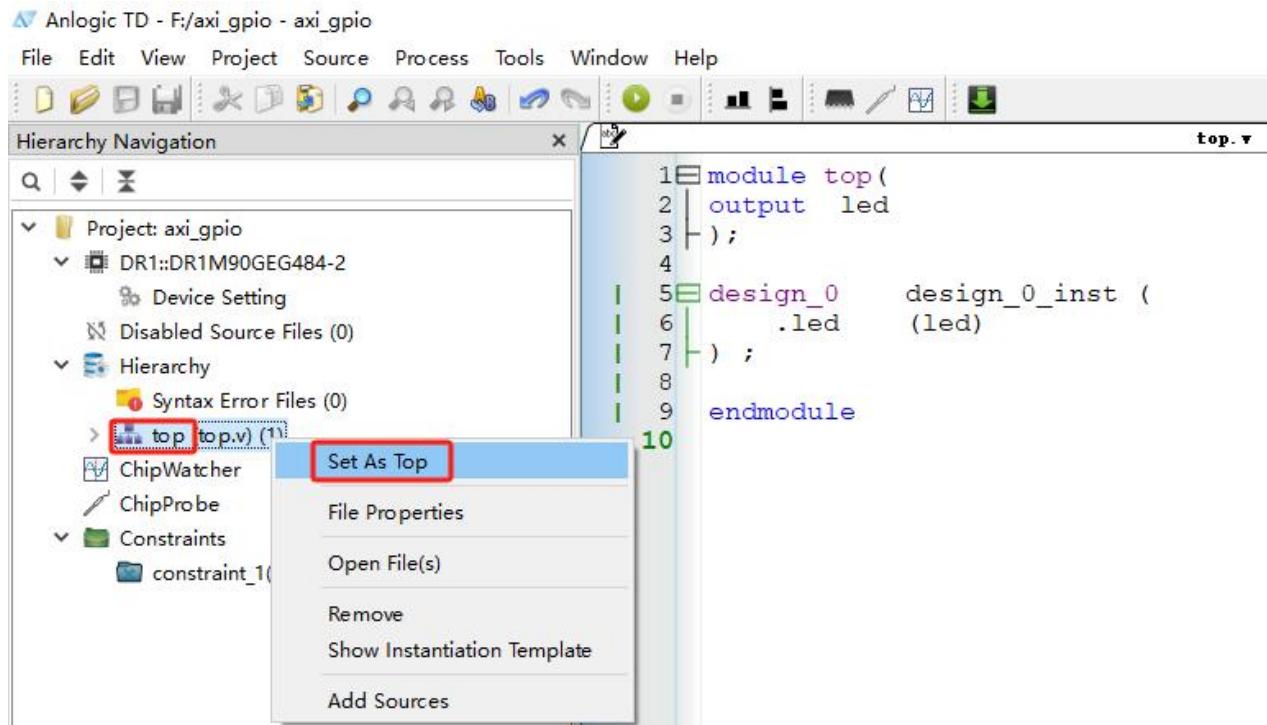

在模块 top 上右击选择 Set As Top，将 top 模块设置为顶层模块

图 6-35. 设置顶层模块

### 6.1.11. 设置顶层管脚约束

将工程编译后，选择菜单 Tools-->IO Constraint 设置管脚约束

图 6-36. 设置管脚约束

设置管脚约束后点击保存

在弹出的对话框点击 OK

添加保存约束文件的名称，点击保存

图 6-37. 保存管脚约束文件

### 6.1.12. 生成 bit 文件

设置完管脚约束后，在 phy opt 上右击选择 Run All，编译整个工程生成 bit 文件

图 6-38. 生成 bit 文件

### 6.1.13. 导出 hpf 文件

点击 Project-->Export Hardware Platform File 导出 hpf 文件，在弹出的对话框中勾选 bit 文件，然后点击 OK

图 6-39. 导出 hpf 文件

### 6.1.14. 新建 BSP 工程

打开 FD 软件，添加一个 FD 工程的存储路径，点击 Launch

图 6-40. 打开 FD 软件

点击 File-->New-->Platform Project 新建 bsp 工程

图 6-41. 新建 bsp

填写工程名为 bsp，添加 hpf 文件，然后点击 Finish

图 6-42. bsp 文件设置

点击 File-->New-->Application Project 新建 fsbl 文件

图 6-43. 新建 fsbl 文件

添加工程名为 fsbl，选择 FSBL 模板，然后点击 Finish 完成 fsbl 文件创建

图 6-44. 创建 fsbl 文件

再次点击 File-->New-->Application Project

图 6-45. 新建 app 工程

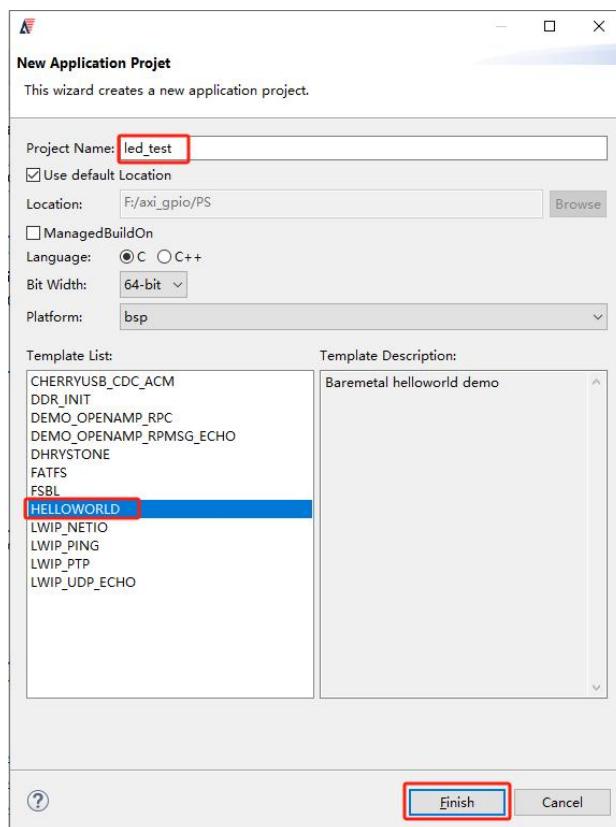

选择 HELLOWORLD 模块，然后点击 Finish，创建 led\_test 工程

图 6-46. 创建 led\_test 工程

- 99 -

更改 led\_test 文件，如下图所示

```

1/*

2 * Copyright (c) 2023, Anlogic Inc. and Contributors. All rights reserved.

3 *

4 * SPDX-License-Identifier: BSD-3-Clause

5 */

6

7 #include <stdio.h>

8 #include <math.h>

9 #include <time.h>

10 #include "al_core.h"

11 #include <stdlib.h>

12

13 #define AXI_GPIO_BASEADDR (0x80100000)

14

15 AL_S32 main()

16 {

17     uint32_t val;

18

19

20     while(1)

21     {

22         AlSys_MDelay(100);

23         AL_REG32_WWRITE(AXI_GPIO_BASEADDR , 0x1);

24         AlSys_MDelay(100);

25         AL_REG32_WWRITE(AXI_GPIO_BASEADDR , 0x0);

26     }

27

28 }

29

30

31 }

```

图 6-47. 更改 led\_test 工程

## 6.1.15. 编译 FD 工程

点击快捷按键编译工程

```

1/*

2 * Copyright (c) 2023, Anlogic Inc. and Contributors. All rights reserved.

3 *

4 * SPDX-License-Identifier: BSD-3-Clause

5 */

6

7 #include <stdio.h>

8 #include <math.h>

9 #include <time.h>

10 #include "al_core.h"

11 #include <stdlib.h>

12

13 #define AXI_GPIO_BASEADDR (0x80100000)

14

15 AL_S32 main()

16 {

17     uint32_t val;

```

图 6-48. 编译 led\_test 工程

## 6.1.16. FD 工程下载

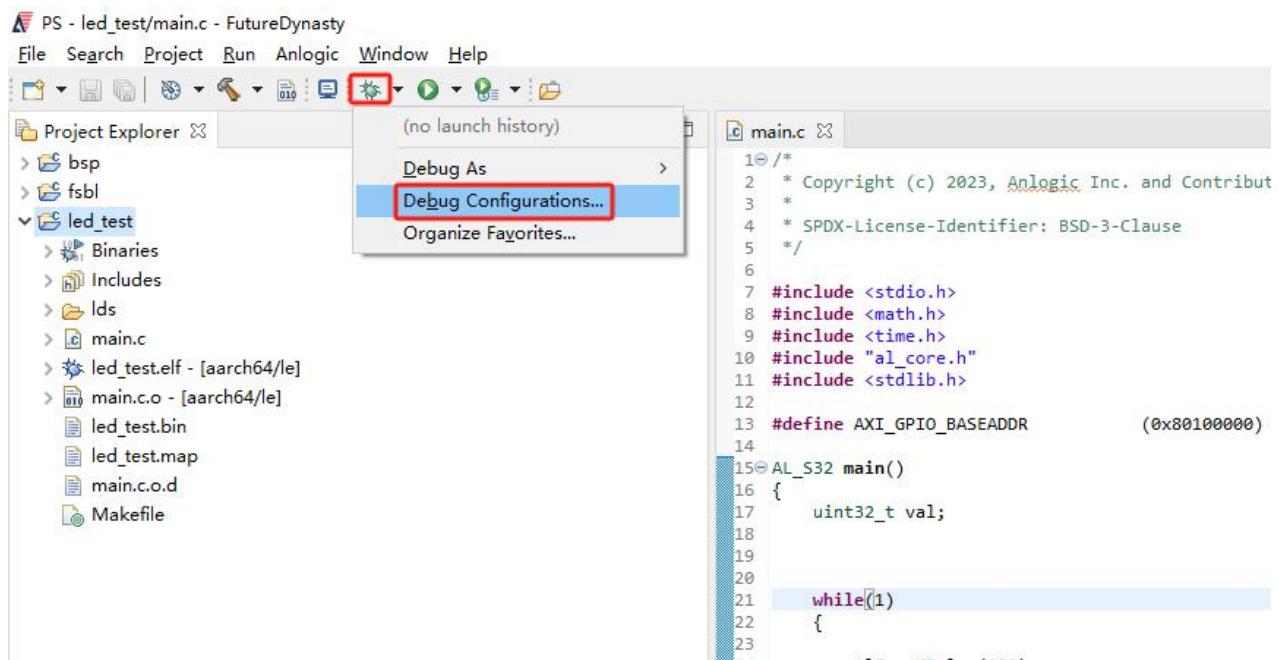

点击快捷图标-->Debug Configurations 进行 debug 调试

图 6-49.debug 调试

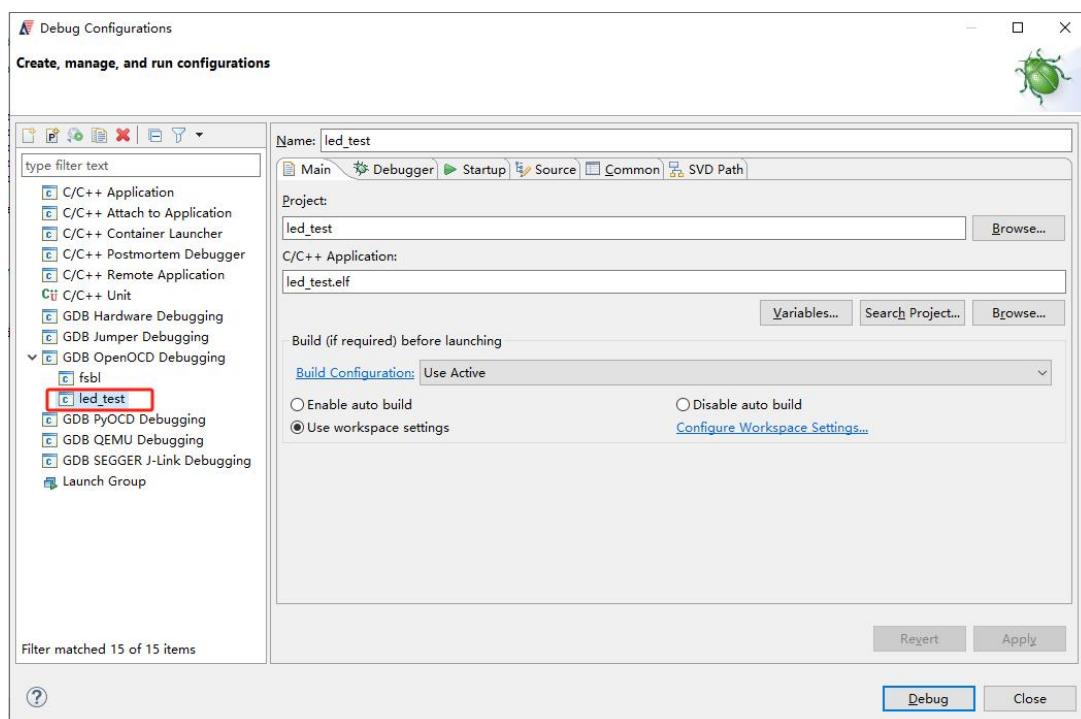

在调试对话框中选择 led\_test 工程

图 6-50.debug 调试设置

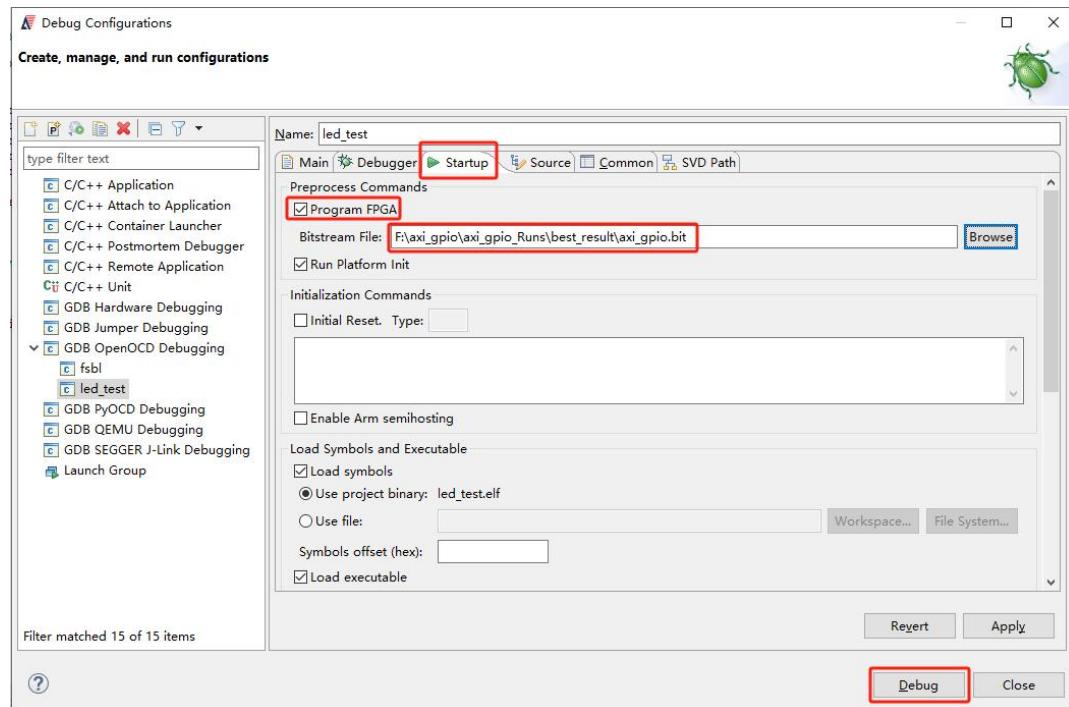

在调试对话中选择 Startup 选项卡，勾选添加 FPGA 文件，然后加入工程的 bit 文件，点击 debug 进行下载

图 6-51.添加 bit 文件

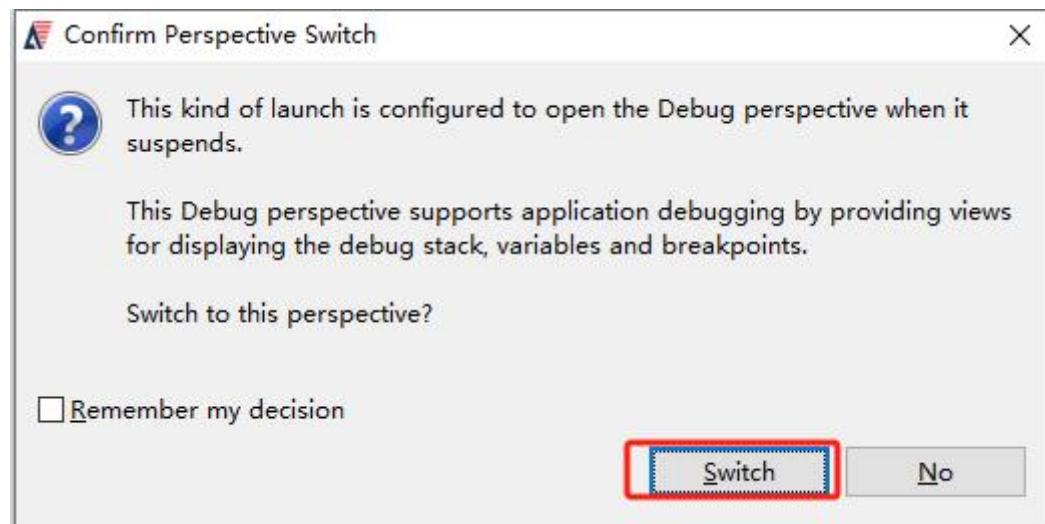

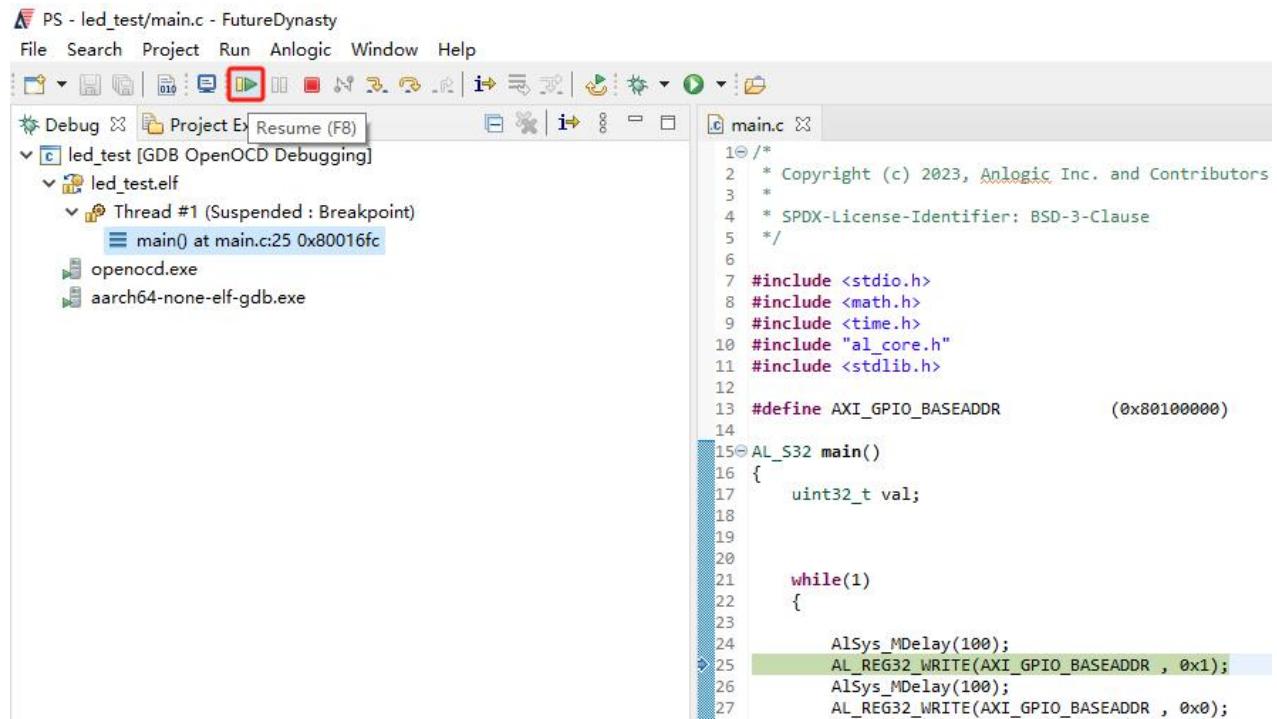

在弹出的对话框中，选择 Switch

在弹出的 debug 调试界面点击 Resume 图标，下载到开发板的程序开始运行，可以看到开发板上的 led 灯开始闪烁

图 6-52.debug 调试运行

# 第七章 HDMI 输出显示测试

前面的章节大多数围绕 PL 或者 PS 端展开，而且 PL 和 PS 着重点也不一样，本章节将会是一个完整的 PL 和 PS 工程，包含开发板的 PL 和 PS 所有外设接口，所以在学习本章节前，请务必先将前面几个章节都要看一遍，这样才能正常搭建本章节工程。

## 7.1. HDMI 显示工程介绍

因 HDMI 显示工程比较复杂，本章节只是进行简单的工程搭建，具体工程请参考我们提供的 HDMI 显示工程，而且章节中加入了很多其它的 AXI 总线接口，需要自己去官方下载对应手册，章节中 VDMA 核比较复杂，需用户自行进行波形抓取和官方手册对应进行学习，才能掌握 VDMA 核的使用，FD 里面是对各个 AXI 总线进行配置，具体的寄存器请参考官方提供的寄存器手册。

### 7.1.1. 新建 HDMI 显示工程

## 新建的 HDMI 工程

图 7-1.新建的 HDMI 工程

## 7.1.2. 配置 PS 端设备

点击 PS\_inst 开始配置 ARM 端设备

```

//Slave

.s_axi;

.s_axi;

.s_axi;

.s_axi;

.s_axi;

);

assign f2p_irq

vdma_mm2s #((

.HACTIVE (8)

```

图 7-2.配置 ARM 端接口设备

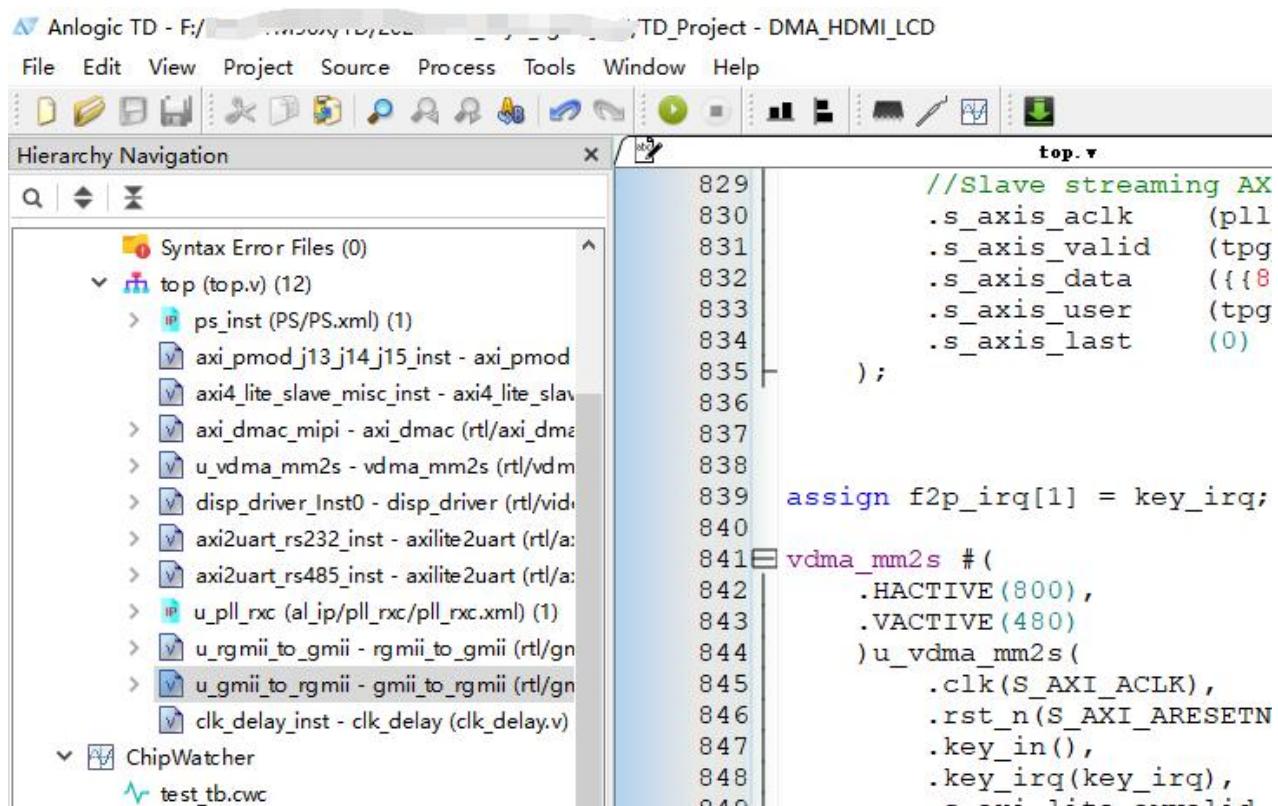

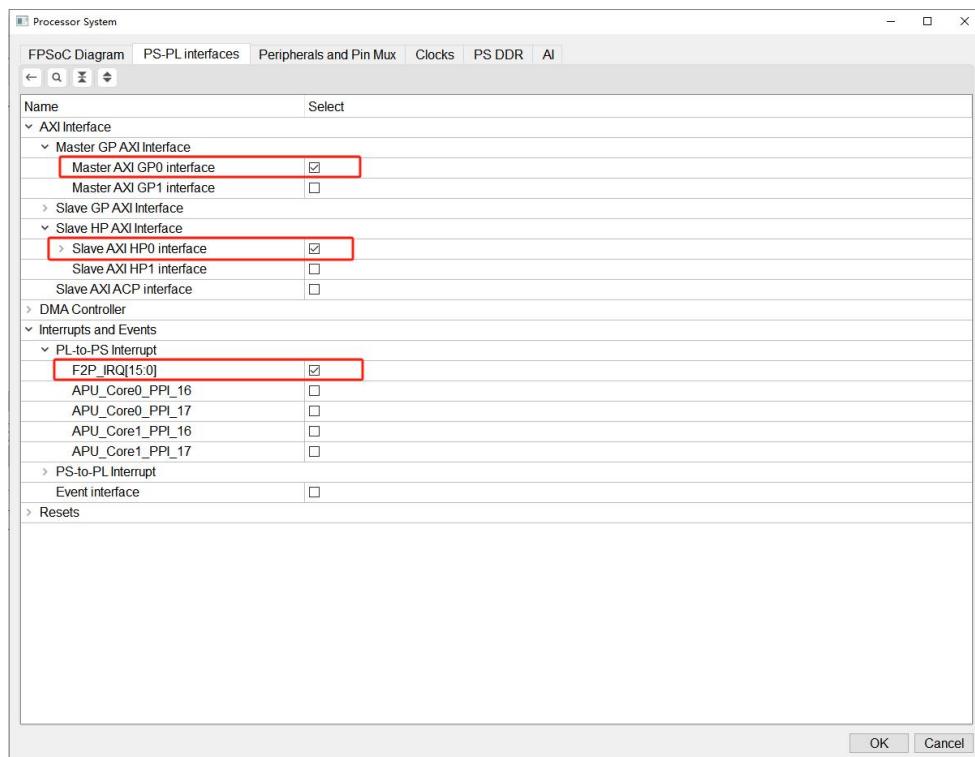

在 PS-PL interfaces 选项卡勾选 GP 接口，HP 接口，中断 IRQ

图 7-3.配置 GP,HP 和中断

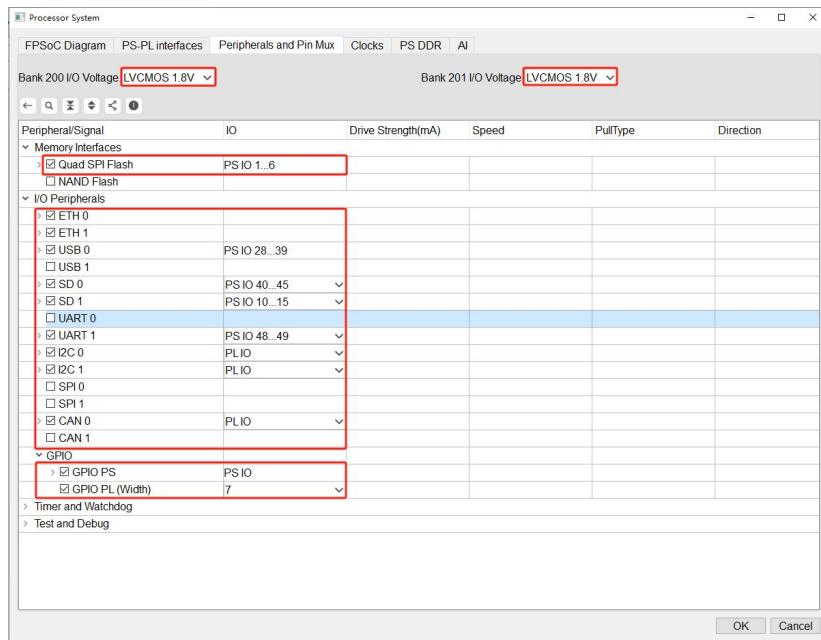

在 Peripherals and Pin Mux 选项卡，设置 bank 电压为 1.8V，然后配置 QSPI，ETH，USB，SD，UART，IIC，CAN，GPIO 接口，因配置的管脚比较多，具体的请参考我们提供的工程，其中 ETH0 为 PS 端口号，ETH1 为 PL 端口号，SD0 为 SD 卡设备，SD1 为 emmc 设备。

图 7-4.PS 端设备接口配置

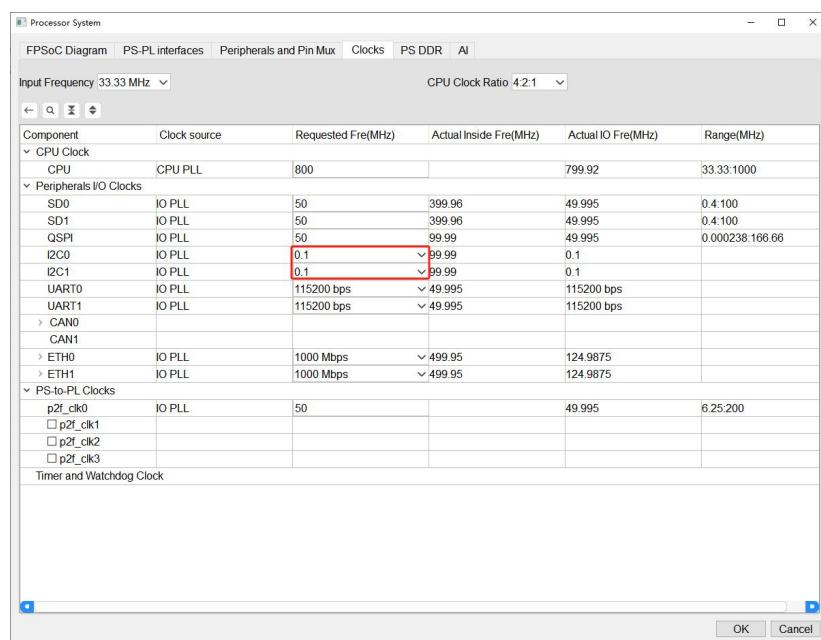

在 Clocks 选项卡，可以设备不同的设备接口时钟，一般会更改 IIC 时钟，设置为 100K 或者 400K 其它的可以使用默认设置

图 7-5.配置时钟

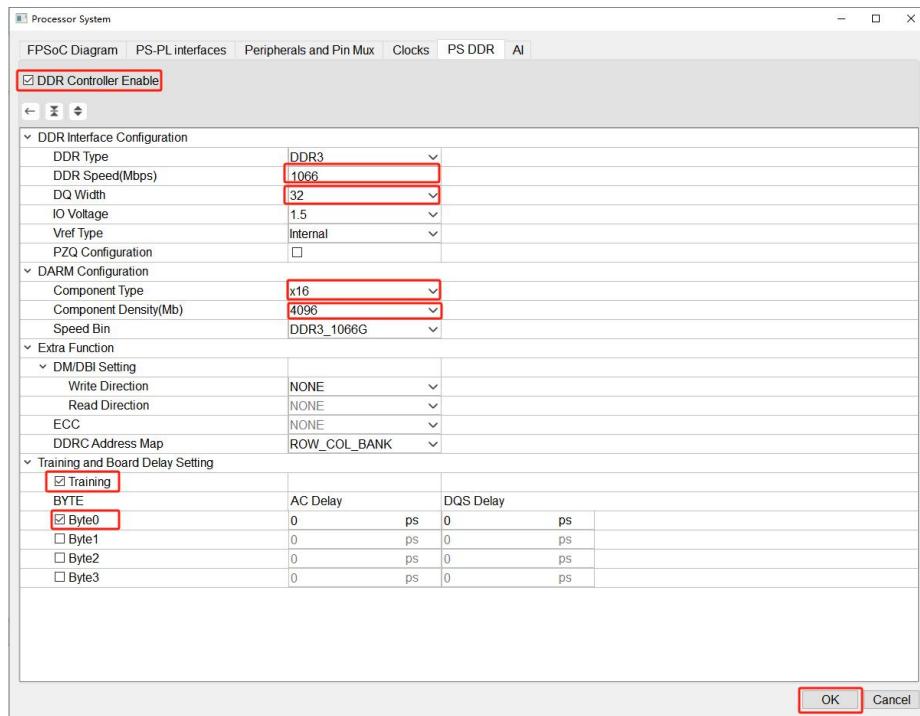

在 PS DDR 选项卡，勾选 DDR Controller Enable 使能 DDR，在 ddr 设置选项卡里设置 DDR 速度，数据位宽，DDR 大小等参数，最后勾选 Training 和 Byte0，点击 OK 完成 DDR 配置

图 7-6.配置 DDR 参数

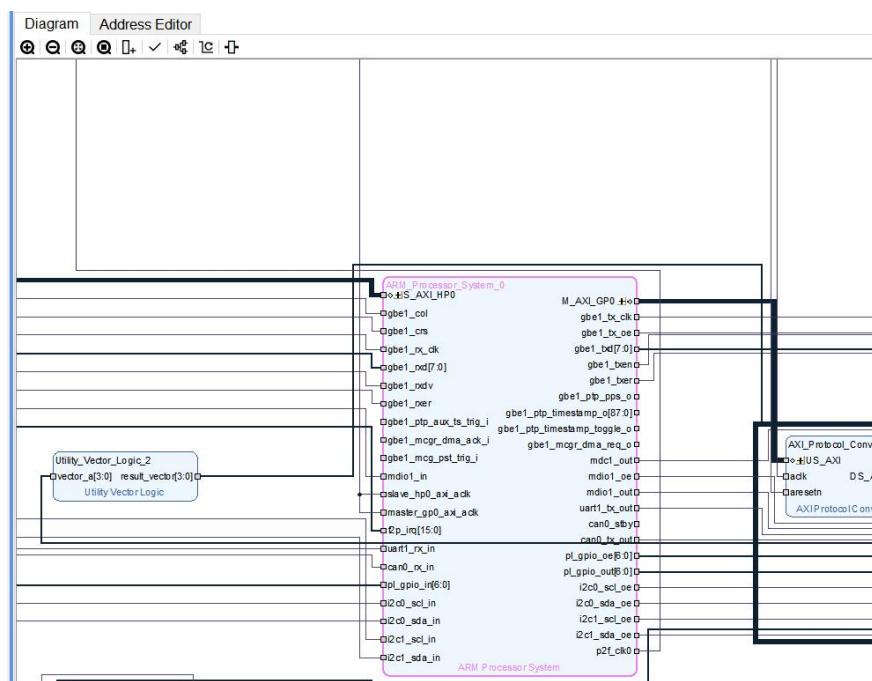

配置完成后的 ARM 核，如下图所示

图 7-7.配置 DDR 参数

arm 核配置完成后，引出 axi 总线接口，此引出的方式和前面章节一样

图 7-8.添加 axi 总线

这里通过 Matrix 引出了 11 路 axi 总线接口，每路总线地址需到在 ip 里进行单独设置

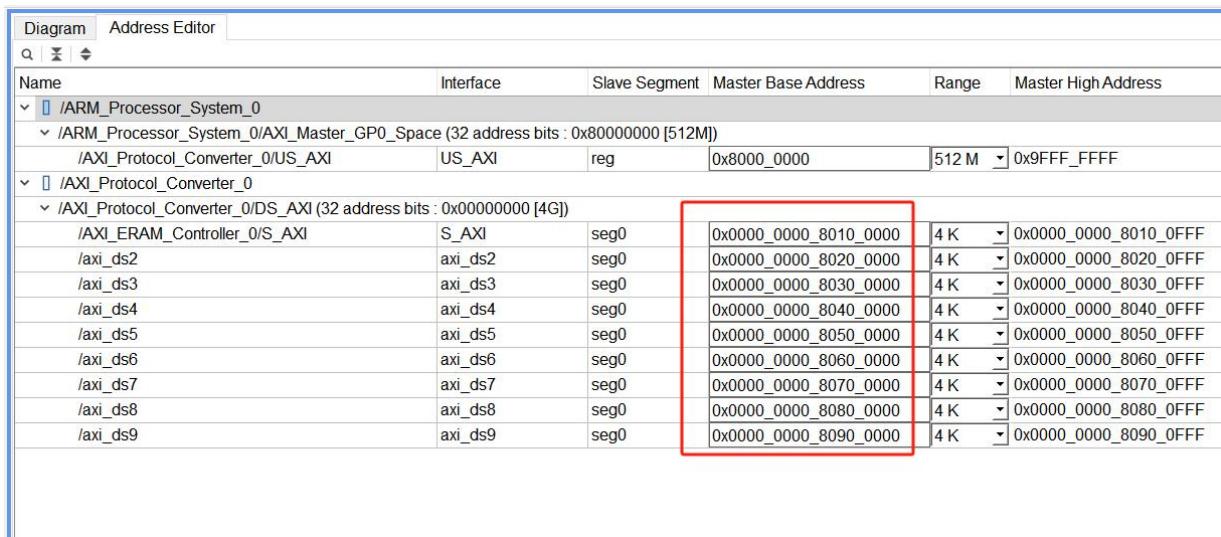

图 7-9.设置 axi 总线地址

因前面在 Matrix 上设置了不同的地址，所以这个地方可以看到每个 axi 总线都分配了一个唯一地址

| Name                                                                               | Interface | Slave Segment | Master Base Address   | Range | Master High Address   |

|------------------------------------------------------------------------------------|-----------|---------------|-----------------------|-------|-----------------------|

| /ARM_Processor_System_0                                                            |           |               |                       |       |                       |

| /ARM_Processor_System_0/AXI_Master_GP0_Space (32 address bits : 0x80000000 [512M]) |           |               |                       |       |                       |

| /AXI_Protocol_Converter_0/US_AXI                                                   | US_AXI    | reg           | 0x8000_0000           | 512 M | 0x9FFF_FFFF           |

| /AXI_Protocol_Converter_0                                                          |           |               |                       |       |                       |

| /AXI_Protocol_Converter_0/DS_AXI (32 address bits : 0x00000000 [4G])               |           |               |                       |       |                       |

| /AXI_ERAM_Controller_0/S_AXI                                                       | S_AXI     | seg0          | 0x0000_0000_8010_0000 | 4 K   | 0x0000_0000_8010_0FFF |

| /axi_ds2                                                                           | axi_ds2   | seg0          | 0x0000_0000_8020_0000 | 4 K   | 0x0000_0000_8020_0FFF |

| /axi_ds3                                                                           | axi_ds3   | seg0          | 0x0000_0000_8030_0000 | 4 K   | 0x0000_0000_8030_0FFF |

| /axi_ds4                                                                           | axi_ds4   | seg0          | 0x0000_0000_8040_0000 | 4 K   | 0x0000_0000_8040_0FFF |

| /axi_ds5                                                                           | axi_ds5   | seg0          | 0x0000_0000_8050_0000 | 4 K   | 0x0000_0000_8050_0FFF |

| /axi_ds6                                                                           | axi_ds6   | seg0          | 0x0000_0000_8060_0000 | 4 K   | 0x0000_0000_8060_0FFF |

| /axi_ds7                                                                           | axi_ds7   | seg0          | 0x0000_0000_8070_0000 | 4 K   | 0x0000_0000_8070_0FFF |

| /axi_ds8                                                                           | axi_ds8   | seg0          | 0x0000_0000_8080_0000 | 4 K   | 0x0000_0000_8080_0FFF |

| /axi_ds9                                                                           | axi_ds9   | seg0          | 0x0000_0000_8090_0000 | 4 K   | 0x0000_0000_8090_0FFF |

图 7-10.设备地址

### 7.1.3. 工程设计检查

更改完配置后，点击 Validate Design 检查工程是否有报错

图 7-11.设计检查

## 7.1.4. 导出 PS 端工程

点击 Flow-->Generate Design 重新生成 PS 端 ip

图 7-12.重新生成 ip

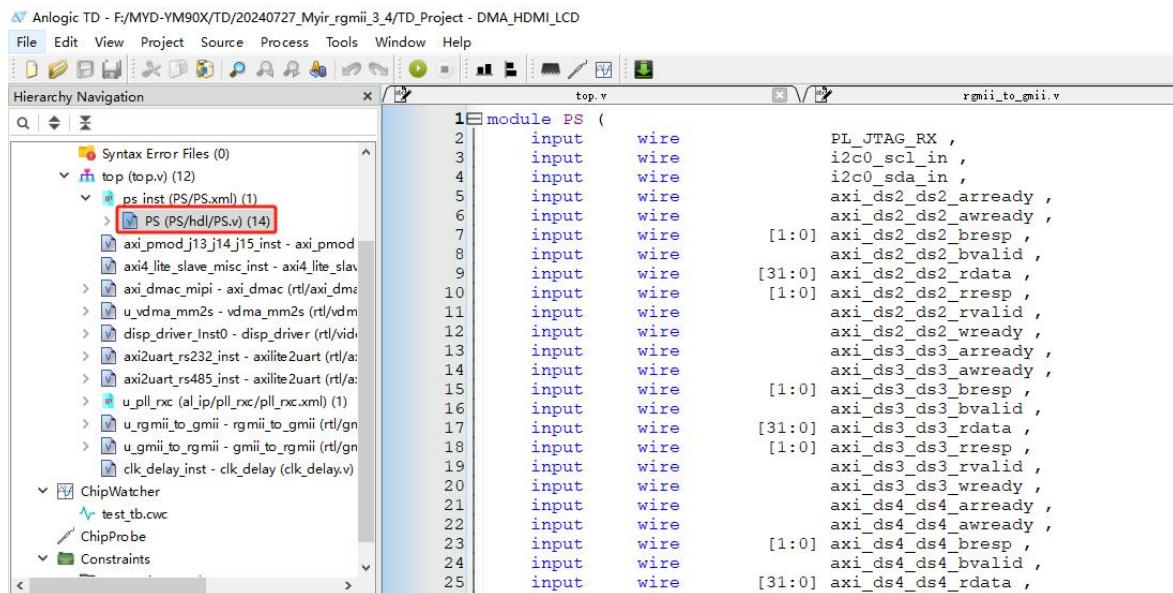

点击 ps\_inst 下面的 PS.v 文件，可以看到刚刚生成的 axi 总线接口，每一个总线都可以挂不同的设备

图 7-13.PS 端总线接口

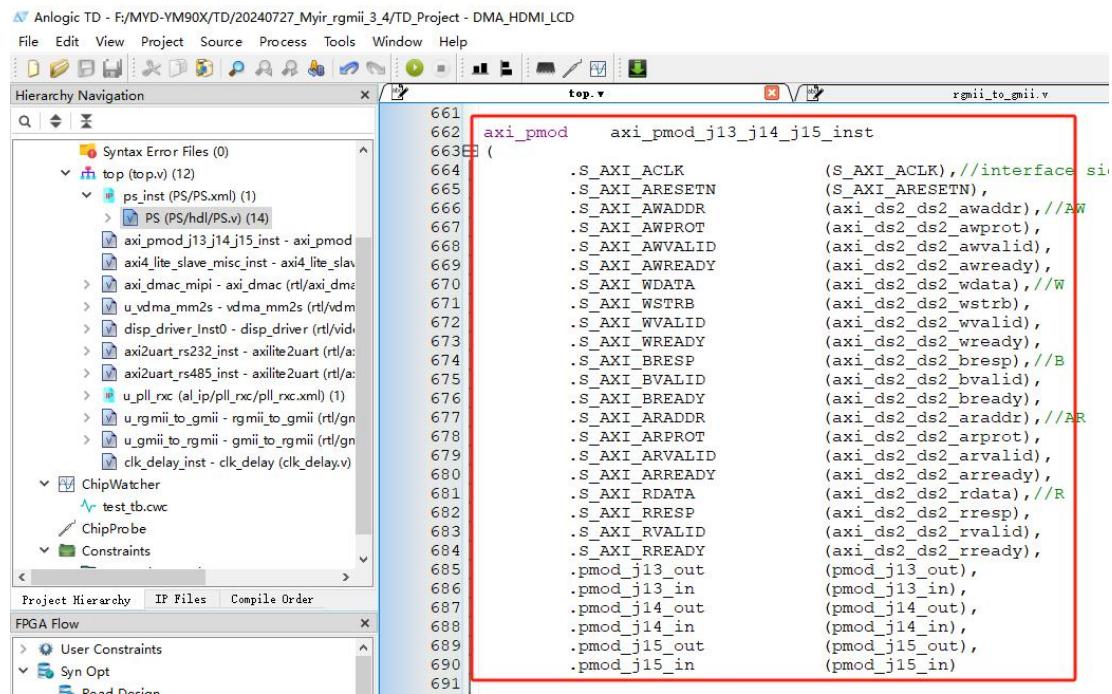

在 axi\_ds2 上面挂接一个 pmod 测试模块

```

Anlogic TD - F:/MYD-YM90X/TD/20240727_Myir_rgmi_3_4/TD_Project - DMA_HDMI_LCD

File Edit View Project Source Process Tools Window Help

Hierarchy Navigation top.v rgmii_to_gmii.v

Syntax Error Files (0)

top (top.v) (12)

ps_inst (PS/PS.xml) (1)

PS (PS/hdl/PS.v) (14)

axi_pmod_j13_j14_j15_inst - axi_pmod

axi4_lite_slave_msc_inst - axi4_lite_slave

axi_dmac_mipi - axi_dmac (rtl/axi_dmac)

u_vdma_mm2s - vdma_mm2s (rtl/vdm)

disp_driver_Inst0 - disp_driver (rtl/vid)

axi2uart_rs232_inst - axilite2uart (rtl/axi2uart)

axi2uart_rs485_inst - axilite2uart (rtl/axi2uart)

u_pll_rxc (al_ip/pll_rxc/pll_rxc.xml) (1)

u_rgmi_to_gmii - rgmii_to_gmii (rtl/gm)

u_gmii_to_rgmi - gmii_to_rgmi (rtl/gn)

clk_delay_inst - clk_delay (clk_delay.v)

ChipWatcher

test.tb.cvc

ChipProbe

Constraints

Project Hierarchy IP Files Compile Order

FPGA Flow

User Constraints

Syn Opt

Read Design

```

```

661 axi_pmod      axi_pmod_j13_j14_j15_inst

662 (

663   .S_AXI_ACLK          (S_AXI_ACLK), //interface si

664   .S_AXI_ARESETN        (S_AXI_ARESETN),

665   .S_AXI_AWADDR         (axi_ds2.ds2_awaddr), //AW

666   .S_AXI_AWPROT         (axi_ds2.ds2_awprot),

667   .S_AXI_AWVALID        (axi_ds2.ds2_awvalid),

668   .S_AXI_AWREADY        (axi_ds2.ds2_awready),

669   .S_AXI_WDATA          (axi_ds2.ds2_wdata), //W

670   .S_AXI_WSTRB          (axi_ds2.ds2_wstrb),

671   .S_AXI_WVALID          (axi_ds2.ds2_wvalid),

672   .S_AXI_WREADY          (axi_ds2.ds2_wready),

673   .S_AXI_BRESP           (axi_ds2.ds2_bresp), //B

674   .S_AXI_BVALID          (axi_ds2.ds2_bvalid),

675   .S_AXI_BREADY          (axi_ds2.ds2_bready),

676   .S_AXI_ARADDR          (axi_ds2.ds2_araddr), //AR

677   .S_AXI_ARPROT          (axi_ds2.ds2_arprot),

678   .S_AXI_ARVALID         (axi_ds2.ds2_arvalid),

679   .S_AXI_ARREADY         (axi_ds2.ds2_arready),

680   .S_AXI_RDATA            (axi_ds2.ds2_rdata), //R

681   .S_AXI_RRESP            (axi_ds2.ds2_rresp),

682   .S_AXI_RVALID          (axi_ds2.ds2_rvalid),

683   .S_AXI_RREADY          (axi_ds2.ds2_rready),

684   .pmod_j13_out           (pmod_j13_out),

685   .pmod_j13_in            (pmod_j13_in),

686   .pmod_j14_out           (pmod_j14_out),

687   .pmod_j14_in            (pmod_j14_in),

688   .pmod_j15_out           (pmod_j15_out),

689   .pmod_j15_in            (pmod_j15_in)

690

691

```

图 7-14.axi 总线接口接 PMOD 模块

### 7.1.5. 添加 VDMA 模块

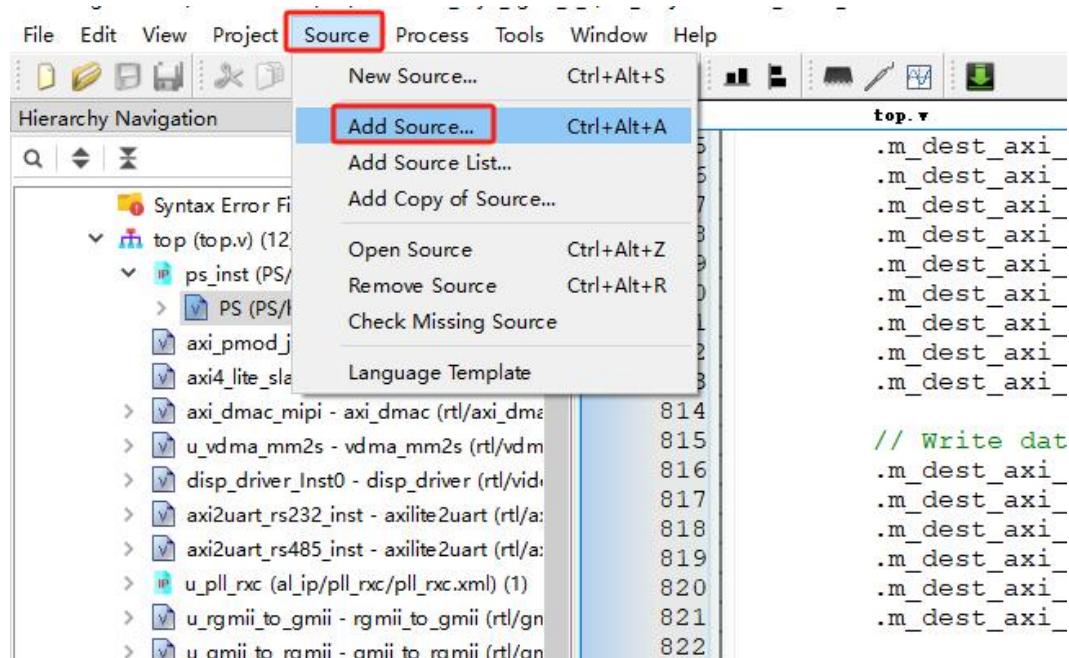

点击 Source-->Add Source 添加文件

图 7-15.选择添加文件菜单

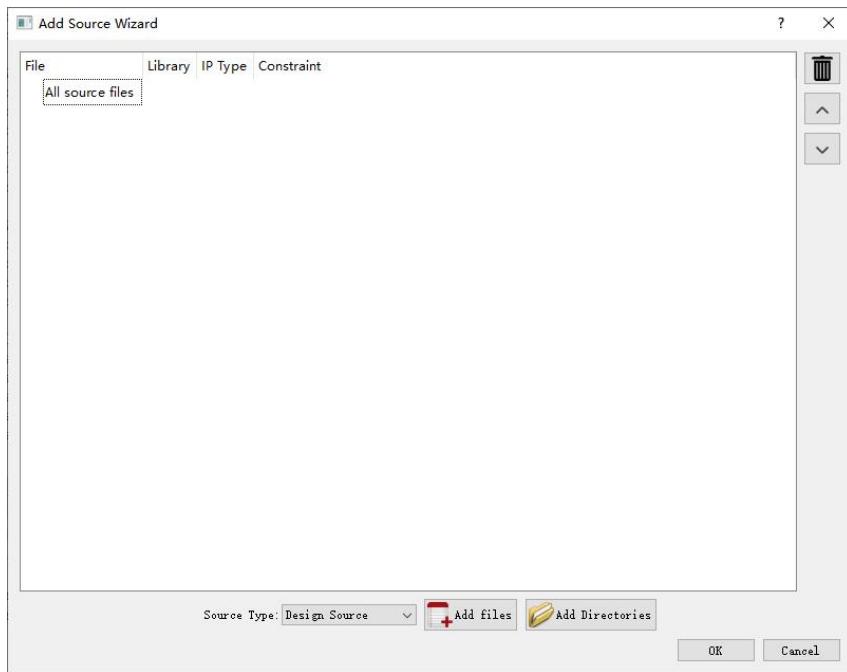

在弹出的对话框中选择 Add files

图 7-16.开始添加文件

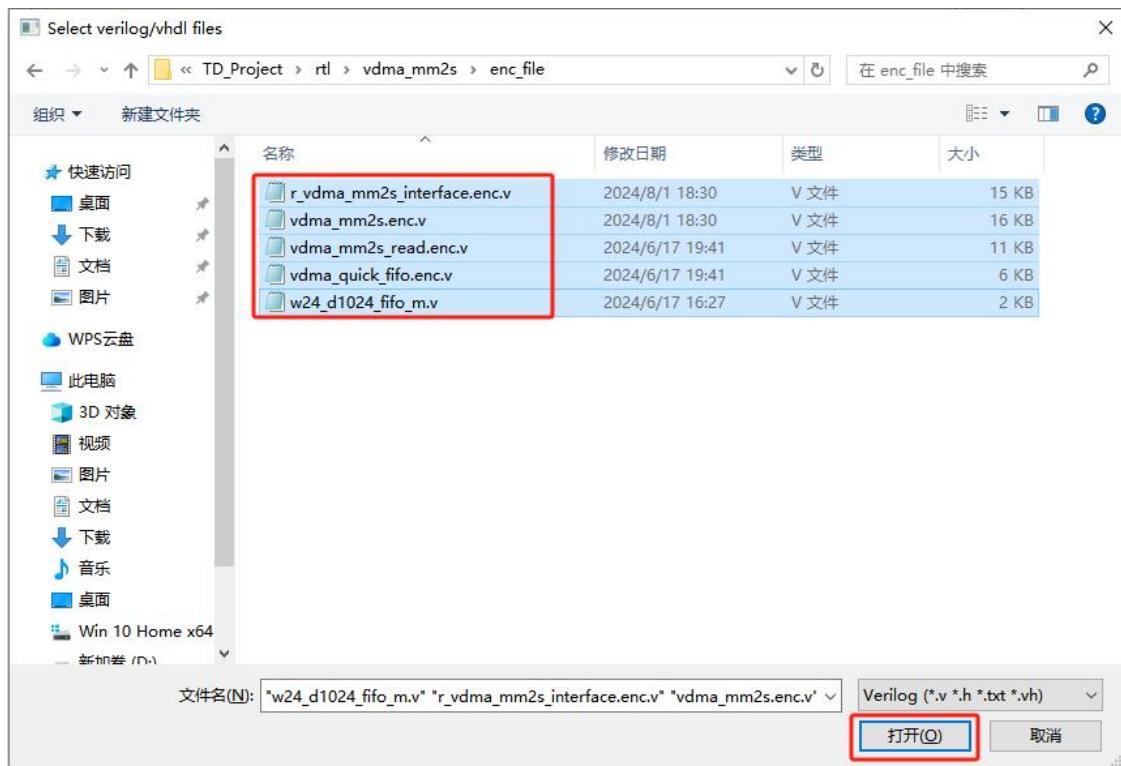

选择 vdma 模块文件存放路径，选择所有的文件，然后点击打开

图 7-17.添加 vdma 文件

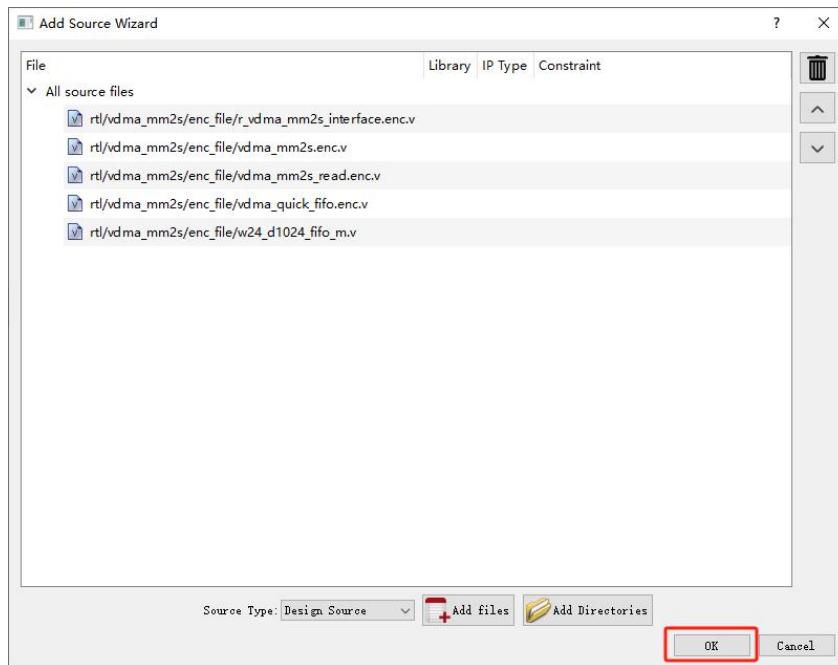

点击 OK，添加 vdma 模块所需的文件

图 7-18.添加 vdma 文件

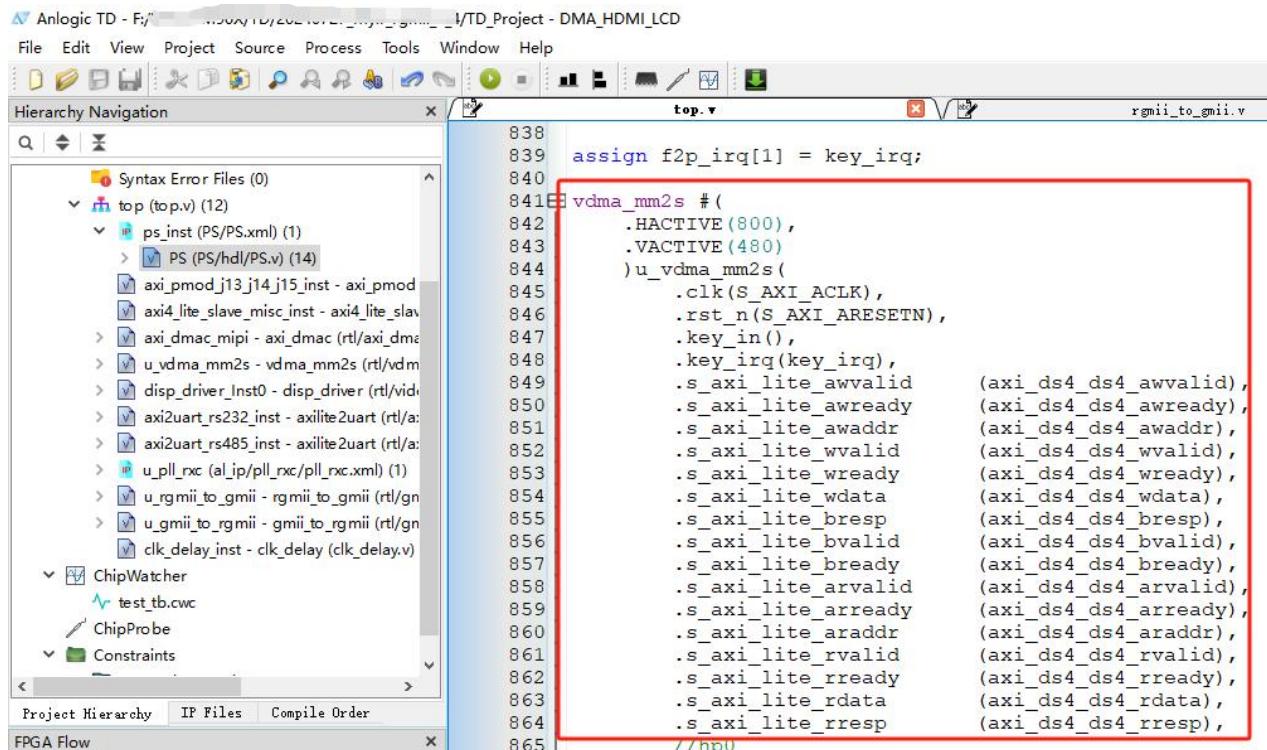

将 VDMA 模块例化到 fpga 工程的顶层，其它模块的添加方式和 VMDA 一样

图 7-19.例化 vdma 模块

## 7.1.6. 编译工程

添加完所有模块后，设置管脚约束，然后在 Phy Opt 上右击选择 Run All,编译工程

图 7-20.编译工程

## 7.1.7. 导出 HPF 文件

点击 Project-->Export Hardware Platform File 导出 hpf 文件

图 7-21.导出 hpf 文件

## 7.1.8. 打开 FD 软件

点击 FD 软件，打开 FD 软件后选择一个 FD 工程存储路径，然后点击 Launch

图 7-22. 打开 FD 软件

## 7.1.9. 生成 BSP 文件

点击 File-->New-->Platform Project 新建 bsp 文件

图 7-23. 新建 bsp 文件

填写工程名为 bsp，添加 hpf 文件，然后点击 Finish 生成 bsp 文件

图 7-24.生成 bsp 文件

点击 File-->New-->Application Project 新建一个 fsbl 文件

图 7-25.新建 fsbl 文件

填写工程名为 fsbl，使用 FSBL 模板，然后点击 Finish 新建 fsbl 文件

图 7-26.生成 fsbl 文件

点击快捷工具栏上的编译图标，编译 fsbl 文件

图 7-27.编译 fsbl 文件

点击 File-->New-->Application Project 新建 hdmi 测试 app

图 7-28.新建 hdmi 测试 app

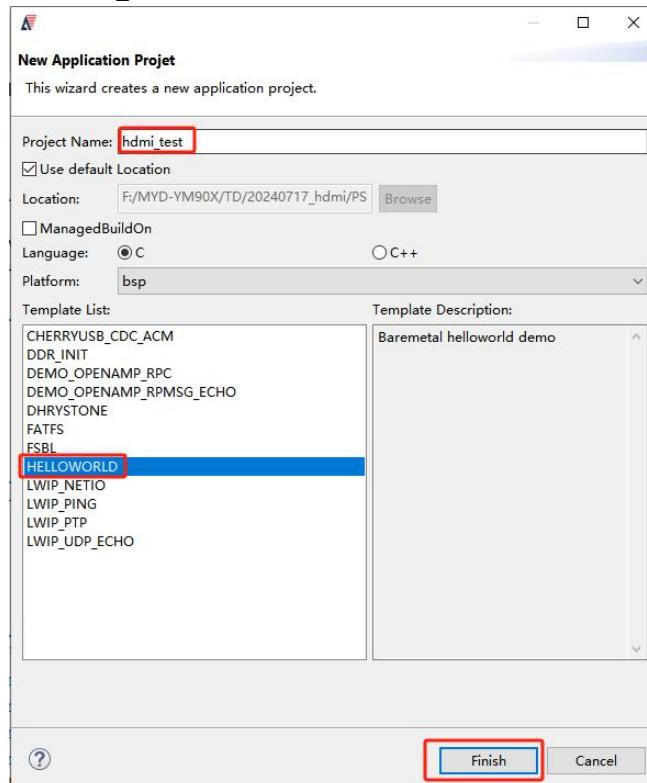

在弹出对话框填写工程名为 hdmi\_test，选择 HELLOWORLD 模板，然后点击 Finish 生成测试工程

图 7-29.生成 hdmi 测试 app

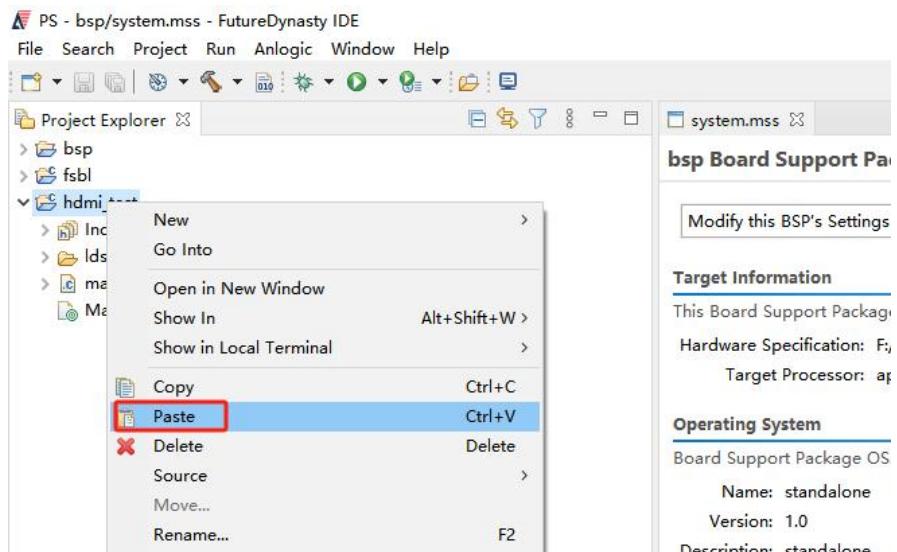

在新建的 hdmi\_test 文件上右击选择 paste，将我们提供的 hdmi 裸机工程复制进去

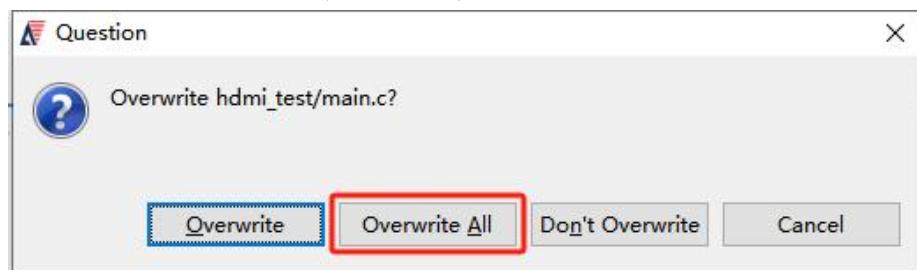

点击 Overwrite All 添加 hdmi 测试文件

图 7-30. 复制 hdmi 测试文件

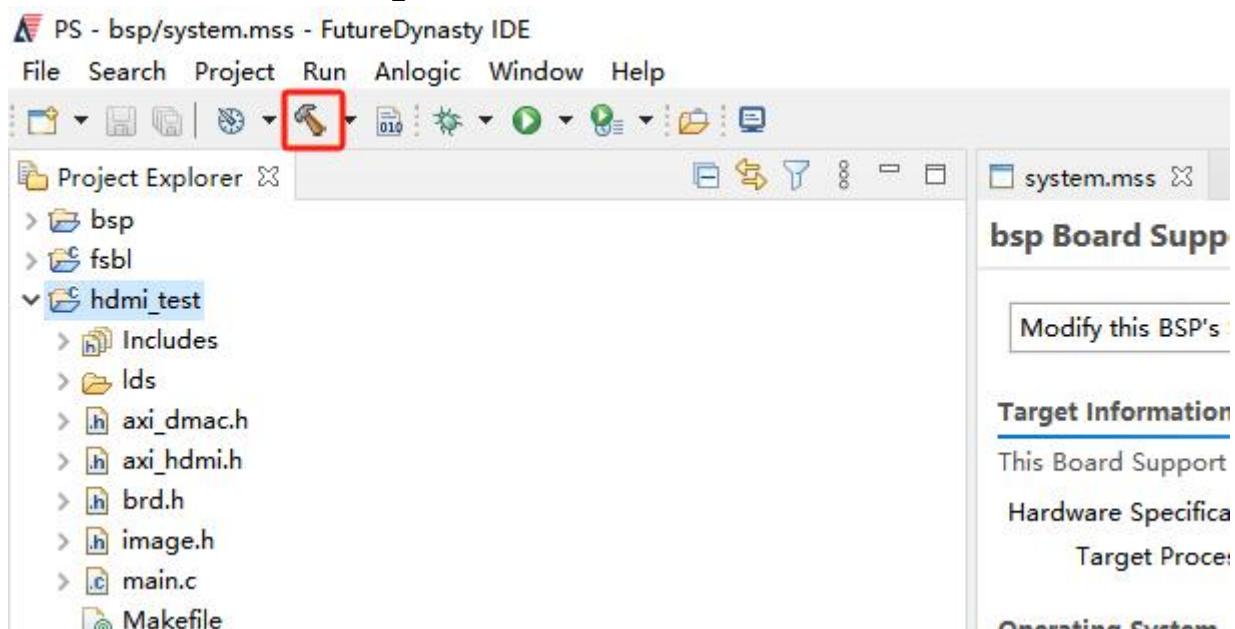

点击编译快捷图标，编译 hdmi\_test 工程

图 7-31. 编译 hdmi\_test 工程

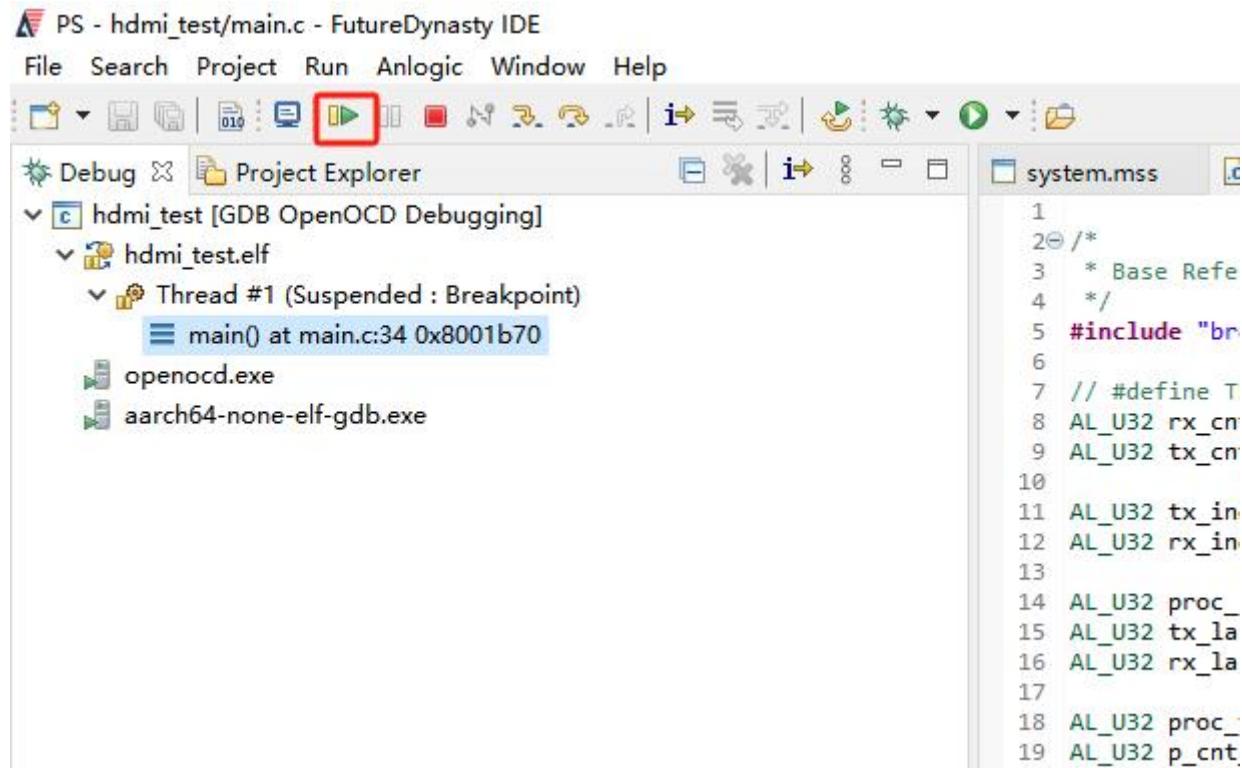

点击 debug 快捷图标选择 Debug Configurations, 进行 debug 调试

图 7-32.debug 调试

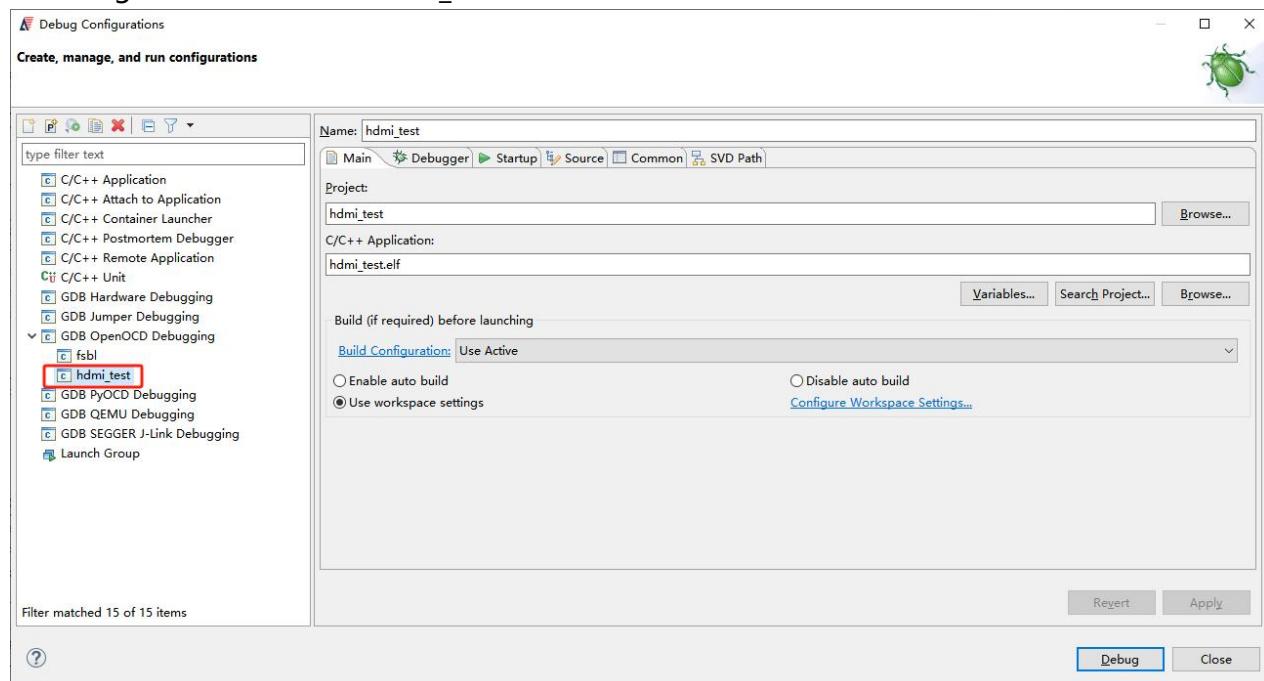

在 debug 调试对话框中选中 hdmi\_test 作为调试工程

图 7-33. 调试工程设置

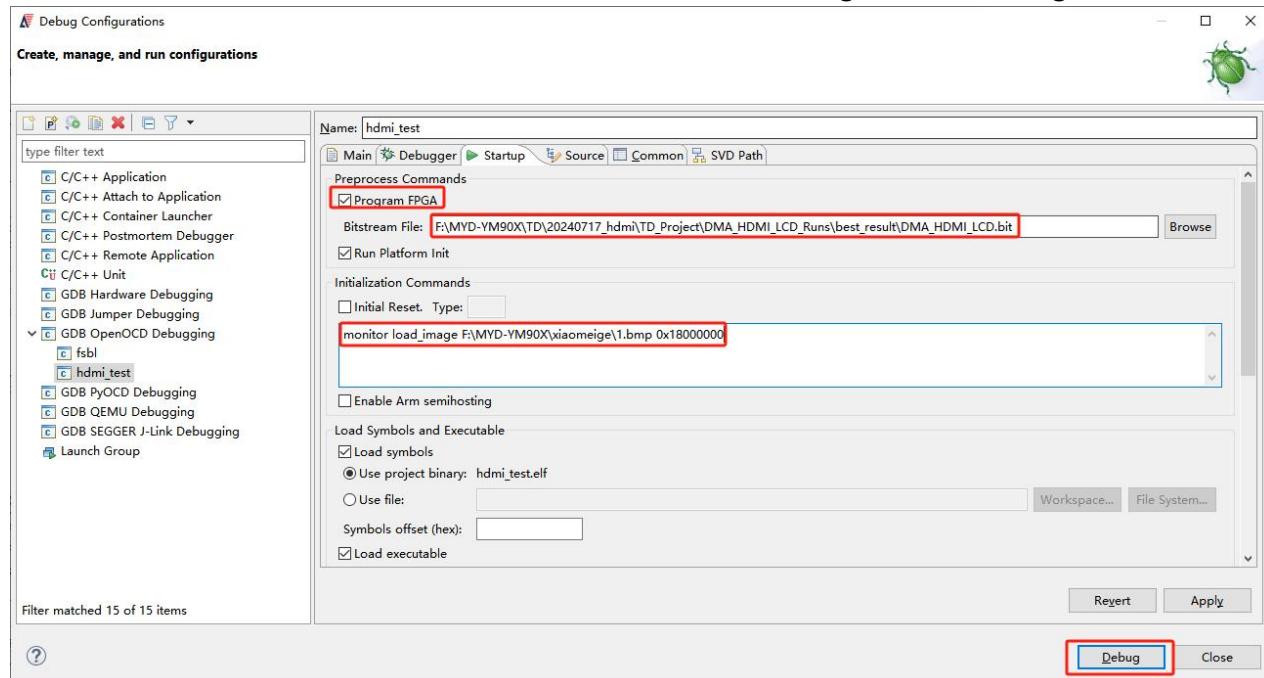

在 debug 调试对话框的 Startup 选项卡，勾选 FPGA 文件，在 Type 里面填写电脑本地图片地址，将电脑本地图片传到开发板的 ddr，通过 hdmi 输出显示，点击 debug 开始进行 debug 调试

图 7-34.debug 下载设置

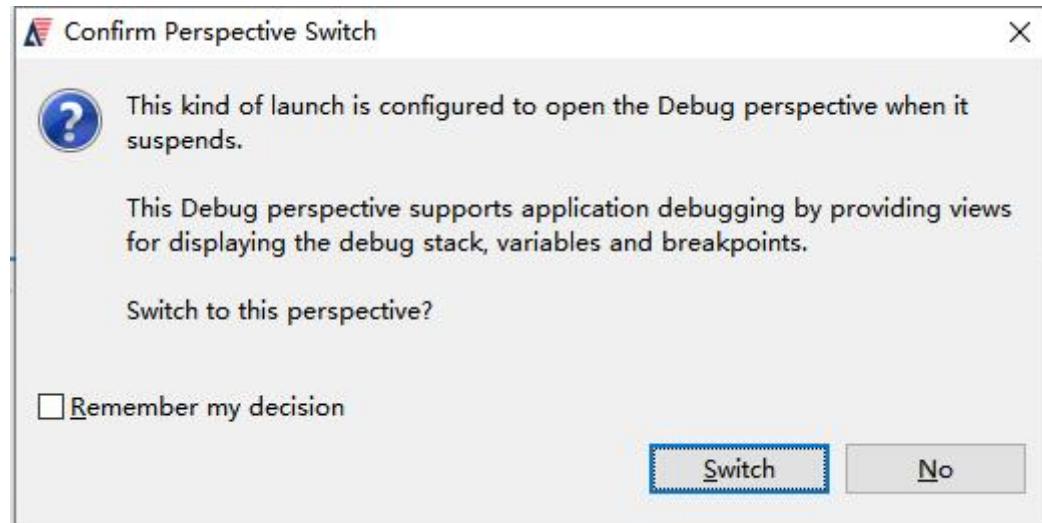

在弹出的对话框点击 Switch 开始进行调试

点击 debug 调试界面运行快捷图标，运行开发板程序，可以看到 hdmi 显示输出图片

图 7-35.HDMI 输出显示图片

# 附录一 联系我们

## 深圳总部

地址：深圳市龙岗区坂田街道发达路云里智能园 2 栋 6 楼 04 室

负责区域：广东、广西、海南、重庆、云南、贵州、四川、西藏、香港、澳门

传真：0755-25532724

电话：0755-25622735

## 武汉研发中心

地址：武汉东湖新技术开发区关南园一路 20 号当代科技园 4 号楼 1601 号

电话：027-59621648

## 华东地区

地址：上海市浦东新区金吉路 778 号浦发江程广场 1 号楼 805 室

负责区域：上海、福建、浙江、江苏、安徽、山东

传真：021-62087085

电话：021-62087019

## 华北地区

地址：北京市大兴区荣华中路 8 号院力宝广场 10 号楼 901 室

负责区域：辽宁、吉林、黑龙江、北京、天津、河北、山西、内蒙古、湖北、湖南、江西、河南、陕西、甘肃、宁夏、青海、新疆

传真：010-64125474

电话：010-84675491

## 销售联系方式

网址：[www.myir.cn](http://www.myir.cn)

邮箱：[sales.cn@myir.cn](mailto:sales.cn@myir.cn)

## 技术支持联系方式

邮箱：[support.cn@myir.cn](mailto:support.cn@myir.cn)

武汉研发中心电话: 027-59621648

深圳总部技术电话: 0755-22316235

如果您通过邮件获取帮助时, 请使用以下格式书写邮件标题:

**[公司名称/个人--开发板型号] 问题概述**

这样可以使我们更快速跟进您的问题, 以便相应开发组可以处理您的问题。

## 附录二 售后服务与技术支持

凡是通过米尔电子直接购买或经米尔电子授权的正规代理商处购买的米尔电子全系列产品，均可享受以下权益：

- 1、6个月免费保修服务周期

- 2、终身免费技术支持服务

- 3、终身维修服务

- 4、免费享有所购买产品配套的软件升级服务

- 5、免费享有所购买产品配套的软件源代码，以及米尔电子开发的部分软件源代码

- 6、可直接从米尔电子购买主要芯片样品，简单、方便、快速；免去从代理商处购买时，漫长的等待周期

- 7、自购买之日起，即成为米尔电子永久客户，享有再次购买米尔电子任何一款软硬件产品的优惠政策

- 8、OEM/ODM 服务

如有以下情况之一，则不享有免费保修服务：

- 1、超过免费保修服务周期

- 2、无产品序列号或无产品有效购买单据

- 3、进液、受潮、发霉或腐蚀

- 4、受撞击、挤压、摔落、刮伤等非产品本身质量问题引起的故障和损坏

- 5、擅自改造硬件、错误上电、错误操作造成的故障和损坏

- 6、由不可抗拒自然因素引起的故障和损坏

**产品返修：**

用户在使用过程中由于产品故障、损坏或其他异常现象，在寄回维修之前，请先致电米尔电子客服部，与工程师进行沟通以确认问题，避免故障判断错误造成不必要的运费损失及周期的耽误。

**维修周期：**

收到返修产品后，我们将即日安排工程师进行检测，我们将在最短的时间内维修或更换并寄回。一般的故障维修周期为3个工作日（自我司收到物品之日起，不计运输过程时间），由于特殊故障导致无法短期内维修的产品，我们会与用户另行沟通并确认维修周期。

**维修费用：**

在免费保修期内的产品，由于产品质量问题引起的故障，不收任何维修费用；不属于免费保修范围内的故障或损坏，在检测确认问题后，我们将与客户沟通并确认维修费用，我们仅收取元器件材料费，不收取维修服务费；超过保修期限的产品，根据实际损坏的程度来确定收取的元器件材料费和维修服务费。

**运输费用：**

产品正常保修时，用户寄回的运费由用户承担，维修后寄回给用户的费用由我司承担。非正常保修产品来回运费均由用户承担。