# Capacitance-Digital-Converter LSI for Electrostatic Capacitive Touch Sensors

#### Overview

The LC71F7001PVB is capacitance digital converter LSI designed for electrostatic capacitance touch sensors. A total of 14 capacitance sensors (7 pairs with 14 sensors in the differential input mode) can be connected to the input pin and, depending on how the sensors are combined, 14 or more switch functions can be provided. The LC71F7001PVB is also provided with up to 14 general-purpose output ports (GPO) that can be used as LED drive ports. The detected capacitance values are output as 16-bit digital data through the  $I^2C^{\text{TM}}$  serial interface. The detection sensitivity and capacitance offset value can be adjusted and set (calibrated) from an external device through the  $I^2C$  serial interface.

#### **Features**

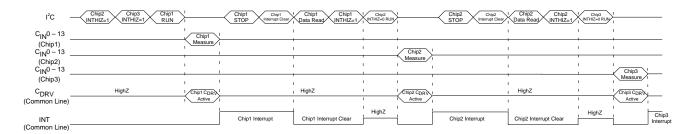

- Detection System: 14 Electrostatic Capacitance Sensors Single/Differential Input, Differential Capacitance Value Output. By the Use of Multiple (Up to 8) LC71F7001PVB Capacitance Digital Converter LSI, They Can Increase the Number of the Input

- Input Capacitance Resolution: Less than 1 fF.

- Measurement Time (14 Single Inputs):

0.84 ms (high-speed mode: f<sub>CDRV</sub> = 200 kHz, OSR = 4) to 107.5 ms (high-resolution mode: f<sub>CDRV</sub> = 200 kHz, OSR = 512)

OSR: Oversampling Ratio

- External Components: Not Required

- On-chip Calibration: Function for Removing Environmental Factors

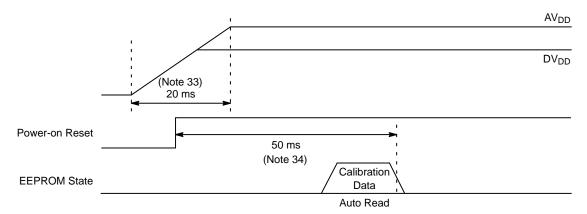

- Built-in EEPROM: For Storing Calibration Data, EEPROM Rewriting Times 10000 Cycles, EEPROM Data Retention Time 20 years

- Interface: I<sup>2</sup>C Serial Interface Compatible

- Low Power Consumption: Typ 10 μA (during intermittent operation) to Typ 0.8 mA (during continuous operation).

- Supply Voltage: 2.6 V to 3.6 V

# **Typical Applications**

- Consumer: Home Appliance, Digital Cameras

- Industrial: Remote Controllers

- Computing: Cell Phones, Portable Devices, Game Machines

# ON Semiconductor®

www.onsemi.com

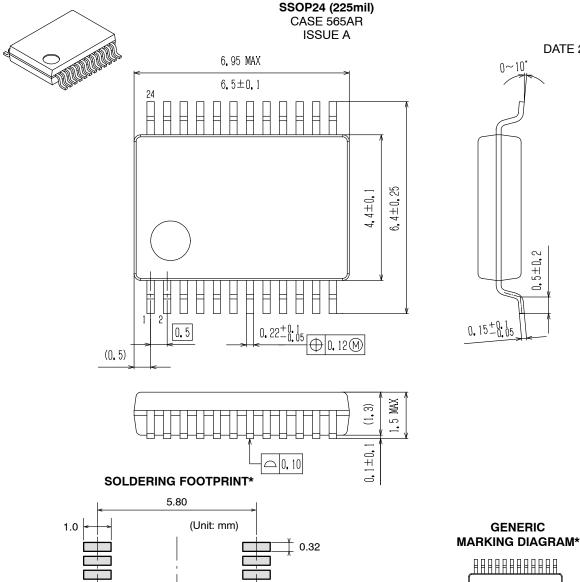

SSOP24 (225 mil) CASE 565AR

#### MARKING DIAGRAM

XXXXX = Specific Device Code Y = Year M = Month DDD = Additional Traceability Data

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 36 of this data sheet.

# **Specifications**

Table 1. ABSOLUTE MAXIMUM RATINGS  $(T_A = 25^{\circ}C, V_{SS} = 0 \text{ V})$

| Parameter           | Symbol                             | Ratings                        | Unit | Remarks                                                                                        |

|---------------------|------------------------------------|--------------------------------|------|------------------------------------------------------------------------------------------------|

| Supply Voltage      | AV <sub>DD</sub> /DV <sub>DD</sub> | -0.3 to +4.0                   | V    |                                                                                                |

| Input Voltage       | V <sub>IN1</sub>                   | -0.3 to AV <sub>DD</sub> + 0.3 | V    | C <sub>IN</sub> 0 to 13, TEST, C <sub>REF</sub>                                                |

|                     | V <sub>IN2</sub>                   | -0.3 to DV <sub>DD</sub> + 0.3 |      | SCL, SDA                                                                                       |

| Output Voltage      | V <sub>OUT1</sub>                  | -0.3 to AV <sub>DD</sub> + 0.3 | V    | GPO0 to 13, C <sub>DRV</sub> , C <sub>DRV</sub> X, C <sub>DRV</sub> Y, C <sub>DRV</sub> B, INT |

|                     | V <sub>OUT2</sub>                  | -0.3 to DV <sub>DD</sub> + 0.3 | V    | SDA                                                                                            |

| Power Dissipation   | P <sub>d max</sub>                 | 200                            | mW   | T <sub>A</sub> = +85°C                                                                         |

| Storage Temperature | T <sub>stg</sub>                   | -55 to +125                    | °C   |                                                                                                |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

**Table 2. RECOMMENDED OPERATING CONDITIONS**

| Parameter                          | Symbol           | Conditions | Min  | Тур | Max              | Unit | Remarks |

|------------------------------------|------------------|------------|------|-----|------------------|------|---------|

| Operating Supply Voltage           | $AV_{DD}$        |            | 2.6  | 2.8 | 3.6              | V    |         |

| Operating Supply Voltage (for I/F) | $DV_DD$          |            | 1.65 | -   | AV <sub>DD</sub> | V    |         |

| Operating Temperature              | T <sub>opr</sub> |            | -40  | 25  | 85               | °C   |         |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### **Table 3. ELECTRICAL CHARACTERISTICS**

$(V_{SS} = 0 \text{ V}, \text{AV}_{DD} = \text{DV}_{DD} = 2.6 \text{ to } 3.6 \text{ V}, T_A = -40 \text{ to } +85^{\circ}\text{C}, \text{Unless otherwise specified, the CDRV drive frequency and oversampling ratio setting are <math>f_{CDRV} = 100 \text{ kHz}$  and OSR = 512, respectively.)

| Parameter                                                                                             | Symbol                           | Pin Name/Conditions                                                                                                                                          | Min                  | Тур | Max                  | Unit   | Remarks      |

|-------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|----------------------|--------|--------------|

| Capacitance Detection<br>Resolution                                                                   | N                                |                                                                                                                                                              |                      |     | 16                   | bit    |              |

| Output Noise RMS                                                                                      | N <sub>RMS</sub>                 | Differential input, minimum gain setting                                                                                                                     |                      |     | ±1.0                 | LSB    | (Notes 1, 3) |

| Input Offset Capacitance                                                                              | Coff <sub>RANGE</sub>            | C <sub>IN</sub> (single input mode)                                                                                                                          |                      |     | 12.0                 | pF     | (Notes 1, 3) |

| Adjustment Range                                                                                      |                                  | C <sub>IN</sub> (differential input mode)                                                                                                                    |                      |     | ±6.0                 |        |              |

| Input Offset Capacitance<br>Adjustment Resolution                                                     | Coff <sub>RESO</sub>             |                                                                                                                                                              |                      | 7   |                      | bit    |              |

| C <sub>IN</sub> Offset Drift                                                                          | C <sub>INDRIFT</sub>             | Differential input, minimum gain setting                                                                                                                     |                      |     | ±2000                | LSB    | (Note 1)     |

| C <sub>IN</sub> Detection Sensitivity                                                                 | C <sub>INSENSE</sub>             | Differential input, minimum gain setting                                                                                                                     | 10                   |     | 30                   | LSB/fF | (Note 2)     |

| C <sub>IN</sub> Pin Leak Current                                                                      | I <sub>CIN</sub>                 | C <sub>IN</sub> = HighZ                                                                                                                                      |                      | ±25 | ±500                 | nA     |              |

| C <sub>IN</sub> Allowable Parasitic                                                                   | C <sub>INSUB</sub>               | Against V <sub>SS</sub> (C <sub>IN</sub> )                                                                                                                   |                      |     | 30                   | pF     | (Notes 1, 3) |

| Input Capacitance                                                                                     | C <sub>INCDRV</sub> 1            | Against C <sub>DRV</sub> (C <sub>IN</sub> ) Differential input mode After static offset calibration is performed                                             |                      | 4   |                      |        |              |

|                                                                                                       | C <sub>INCDRV</sub> 2            | Against C <sub>DRV</sub> (C <sub>IN</sub> )<br>Single input mode<br>After static offset calibration<br>is performed                                          |                      | 8   |                      |        |              |

| C <sub>DRV</sub> Drive Frequency                                                                      | f <sub>CDRV</sub>                | at 200 kHz                                                                                                                                                   | 120                  |     | 280                  | kHz    |              |

| C <sub>DRV</sub> Pin Leak Current                                                                     | I <sub>CDRV</sub>                | C <sub>DRV</sub> = HighZ                                                                                                                                     |                      | ±25 | ±500                 | nA     |              |

| GPO/C <sub>DRV</sub> /C <sub>DRV</sub> X/C <sub>DRV</sub> Y/<br>C <sub>DRV</sub> B/INT Output Voltage | V <sub>OH_GPO</sub>              | High output (I <sub>GPO</sub> = 3 mA)                                                                                                                        | 0.7 AV <sub>DD</sub> |     |                      | V      | (Note 4)     |

|                                                                                                       | V <sub>OL_GPO</sub>              | Low output (I <sub>GPO</sub> = -3 mA)                                                                                                                        |                      |     | 0.3 AV <sub>DD</sub> |        |              |

| I <sup>2</sup> C Interface Pin Input                                                                  | V <sub>IH_I</sub> <sup>2</sup> C | SCL, SDA high input                                                                                                                                          | 0.8 DV <sub>DD</sub> |     |                      | V      |              |

| Voltage                                                                                               | V <sub>IL_I</sub> <sup>2</sup> C | SCL, SDA low input                                                                                                                                           |                      |     | 0.2 DV <sub>DD</sub> |        |              |

| SDA Output Voltage                                                                                    | V <sub>OL_I</sub> <sup>2</sup> C | SDA low output (I <sub>SDA</sub> = -3 mA)                                                                                                                    |                      |     | 0.4                  | V      |              |

| I <sup>2</sup> C Interface Pin Leak<br>Current                                                        | l <sub>l</sub> <sup>2</sup> C    | SCL, SDA<br>(SDA = HighZ)                                                                                                                                    |                      |     | ±1                   | μΑ     |              |

| Current Consumption                                                                                   | I <sub>DD</sub> 1                | Intermittent operation mode<br>(4 inputs)<br>Measurement interval =<br>256 ms set<br>f <sub>CDRV</sub> = 200 kHz set<br>OSR = 8, moving average<br>count = 8 |                      | 10  | 30                   | μΑ     | (Note 5)     |

|                                                                                                       | I <sub>DD</sub> 2                | Continuous operation mode<br>Measurement Interval = 0 ms<br>set                                                                                              |                      | 0.8 | 1.2                  | mA     | (Note 5)     |

|                                                                                                       | I <sub>STBY</sub>                | Standby mode                                                                                                                                                 |                      |     | 2.0                  | μΑ     | (Note 5)     |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- Design guarantee values (not tested before shipment).

- 2. Measurements conducted using the test mode in the LSI.

- 3.  $T_A = 25^{\circ}C$ .

- 4. Maximum output of 3 mA for each port (GPO/C<sub>DRV</sub>/C<sub>DRV</sub>X/C<sub>DRV</sub>Y/C<sub>DRV</sub>B/INT), total output are 9 mA maximum.

- 5.  $AV_{DD} = DV_{DD} = 2.8 \text{ V}, T_A = 25^{\circ}\text{C}.$

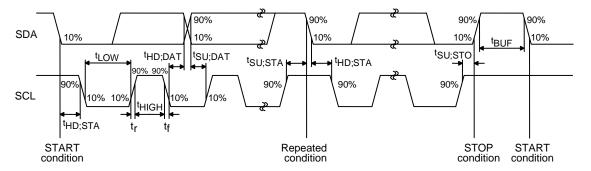

# Table 4. I<sup>2</sup>C COMPATIBLE BUS INTERFACE TIMING CHARACTERISTICS

(V<sub>SS</sub> = 0 V, AV<sub>DD</sub> = DV<sub>DD</sub> = 2.6 to 3.6 V,  $T_A$  = -40 to +85°C)

| Parameter                               | Symbol              | Pin Name/Conditions | Min | Тур | Max | Unit | Remarks  |

|-----------------------------------------|---------------------|---------------------|-----|-----|-----|------|----------|

| SCL Clock Frequency                     | f <sub>SCL</sub>    | SCL                 |     |     | 400 | kHz  |          |

| Start Condition Hold Time               | t <sub>HD;STA</sub> | SCL, SDA            | 0.6 |     |     | μs   |          |

| SCL Clock Low Period                    | t <sub>LOW</sub>    | SCL                 | 1.3 |     |     | μs   |          |

| SCL Clock High Period                   | t <sub>HIGH</sub>   | SCL                 | 0.6 |     |     | μs   |          |

| Repeated Start Condition<br>Set Up Time | t <sub>SU;STA</sub> | SCL, SDA            | 0.6 |     |     | μs   |          |

| Data Hold Time                          | t <sub>HD;DAT</sub> | SCL, SDA            | 0   |     | 0.9 | μs   |          |

| Data Setup Time                         | t <sub>SU;DAT</sub> | SCL, SDA            | 100 |     |     | ns   | (Note 6) |

| SDA, SCL Rise Time                      | t <sub>r</sub>      | SCL, SDA            |     |     | 300 | ns   | (Note 6) |

| SDA, SCL Fall Time                      | t <sub>f</sub>      | SCL, SDA            |     |     | 300 | ns   | (Note 6) |

| Stop Condition Setup Time               | t <sub>SU;STO</sub> | SCL, SDA            | 0.6 |     |     | μs   |          |

| Stop-to-Start Bus Release<br>Time       | t <sub>BUF</sub>    | SCL, SDA            | 1.3 |     |     | μs   |          |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

6. Design guarantee values (not tested before shipment).

Figure 1. I<sup>2</sup>C Bus Timing Definition (FAST-MODE: 400 kHz)

7. The SCL and SDA lines are easily subject to noise. They must be connected with lines that are as short as possible.

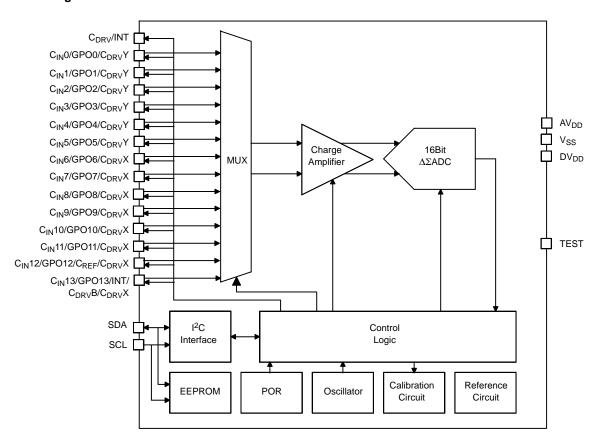

#### **Block Diagram**

Figure 2. Simplified Block Diagram

The LC71F7001PVB is capacitance digital converter LSI capable of detecting changes in capacitance in the order of femtofarads (fF). It consists of an I<sup>2</sup>C serial interface that enables serial communication with external devices, a reference circuit that generates the reference current and voltage, a power-on reset circuit that resets the system when the power is turned on, an oscillation circuit that generates the system clock, a calibration circuit for adjusting the detection sensitivity levels and capacitance offset amounts,

an EEPROM that stores the calibration data of the detection sensitivity levels and capacitance offset amounts which have been set, GPO ports with a general-purpose digital output capability, a multiplexer that selects the input channels, a charge amplifier that detects the changes in the capacitance and outputs analog amplitude values, a 16-bit  $\Delta\Sigma A/D$  converter circuit that converts the analog amplitude values into digital data, and a control logic that controls the entire chip.

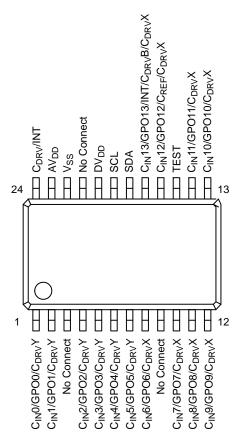

# **Pin Assignment**

Figure 3. Pin Assignment (Top View)

**Table 5. PIN ASSIGNMENT**

| Pin No. | Pin Name                                                           |

|---------|--------------------------------------------------------------------|

| 1       | C <sub>IN</sub> 0/GPO0/C <sub>DRV</sub> Y                          |

| 2       | C <sub>IN</sub> 1/GPO1/C <sub>DRV</sub> Y                          |

| 3       | No Connect                                                         |

| 4       | C <sub>IN</sub> 2/GPO2/C <sub>DRV</sub> Y                          |

| 5       | C <sub>IN</sub> 3/GPO3/C <sub>DRV</sub> Y                          |

| 6       | C <sub>IN</sub> 4/GPO4/C <sub>DRV</sub> Y                          |

| 7       | C <sub>IN</sub> 5/GPO5/C <sub>DRV</sub> Y                          |

| 8       | C <sub>IN</sub> 6/GPO6/C <sub>DRV</sub> X                          |

| 9       | No Connect                                                         |

| 10      | C <sub>IN</sub> 7/GPO7/C <sub>DRV</sub> X                          |

| 11      | C <sub>IN</sub> 8/GPO8/C <sub>DRV</sub> X                          |

| 12      | C <sub>IN</sub> 9/GPO9/C <sub>DRV</sub> X                          |

| 13      | C <sub>IN</sub> 10/GPO10/C <sub>DRV</sub> X                        |

| 14      | C <sub>IN</sub> 11/GPO11/C <sub>DRV</sub> X                        |

| 15      | TEST (Note 8)                                                      |

| 16      | C <sub>IN</sub> 12/GPO12/C <sub>REF</sub> /C <sub>DRV</sub> X      |

| 17      | C <sub>IN</sub> 13/GPO13/INT/C <sub>DRV</sub> B/C <sub>DRV</sub> X |

| 18      | SDA                                                                |

| 19      | SCL                                                                |

| 20      | DV <sub>DD</sub>                                                   |

| 21      | No Connect                                                         |

| 22      | V <sub>SS</sub>                                                    |

| 23      | AV <sub>DD</sub>                                                   |

| 24      | C <sub>DRV</sub> /INT                                              |

<sup>8.</sup> Must be connected to  $V_{\mbox{\scriptsize SS}}$  when mounted.

**Table 6. PIN FUNCTION**

| Pin Name                                                                                                                                                                                                                                                                       | I/O | Pin Functions                                                                                                                         | Pin Type                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| C <sub>IN</sub> 0/GPO0/C <sub>DRV</sub> Y<br>C <sub>IN</sub> 1/GPO1/C <sub>DRV</sub> Y<br>C <sub>IN</sub> 2/GPO2/C <sub>DRV</sub> Y<br>C <sub>IN</sub> 3/GPO3/C <sub>DRV</sub> Y<br>C <sub>IN</sub> 4/GPO4/C <sub>DRV</sub> Y<br>C <sub>IN</sub> 5/GPO5/C <sub>DRV</sub> Y     | I/O | Capacitance sensor input/<br>General-purpose output/<br>Y-axis capacitance drive output                                               | CV AMP  BUFFER  V <sub>SS</sub> |

| C <sub>IN</sub> 6/GPO6/C <sub>DRV</sub> X<br>C <sub>IN</sub> 7/GPO7/C <sub>DRV</sub> X<br>C <sub>IN</sub> 8/GPO8/C <sub>DRV</sub> X<br>C <sub>IN</sub> 9/GPO9/C <sub>DRV</sub> X<br>C <sub>IN</sub> 10/GPO10/C <sub>DRV</sub> X<br>C <sub>IN</sub> 11/GPO11/C <sub>DRV</sub> X | I/O | Capacitance sensor input/<br>General-purpose output/<br>X-axis capacitance drive output                                               | CV AMP  BUFFER  VSS             |

| C <sub>IN</sub> 12/GPO12/<br>C <sub>REF</sub> /C <sub>DRV</sub> X                                                                                                                                                                                                              | I/O | Capacitance sensor input/<br>General-purpose output/<br>Reference capacitance connection/<br>X-axis capacitance drive output          | CV AMP  BUFFER  VSS             |

| C <sub>IN</sub> 13/GPO13/INT/<br>C <sub>DRV</sub> B/C <sub>DRV</sub> X                                                                                                                                                                                                         | I/O | Capacitance sensor input/ General-purpose output/ Interrupt output/ C <sub>DRV</sub> inverted output/ X-axis capacitance drive output | CV AMP  BUFFER  VSS             |

| C <sub>DRV</sub> /INT                                                                                                                                                                                                                                                          | 0   | Capacitance drive common output/<br>Interrupt output                                                                                  | BUFFER V <sub>SS</sub>          |

Table 6. PIN FUNCTION (continued)

| Pin Name         | I/O | Pin Functions                                                                | Pin Type                                      |

|------------------|-----|------------------------------------------------------------------------------|-----------------------------------------------|

| SDA              | I/O | I <sup>2</sup> C serial data input/output                                    | DV <sub>DD</sub><br>BUFFER<br>V <sub>SS</sub> |

| SCL              | I   | I <sup>2</sup> C serial clock input                                          | DV <sub>DD</sub> BUFFER  V <sub>SS</sub>      |

| TEST             | I   | Shipment time TEST input It must always be connected to V <sub>SS</sub>      |                                               |

| $V_{SS}$         | -   | Ground                                                                       |                                               |

| DV <sub>DD</sub> | -   | I <sup>2</sup> C serial interface power supply (1.65 V to AV <sub>DD</sub> ) |                                               |

| AV <sub>DD</sub> | _   | Power supply (2.6 V to 3.6 V)                                                |                                               |

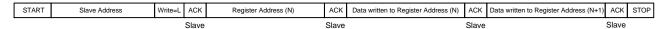

# I<sup>2</sup>C-compatible Bus Interface Formats

• Write format (data can be written into sequentially incremented addresses)

Figure 4.

• Read format (data can be read from sequentially incremented addresses)

| START   | Slave Address | Write=L | ACK   | Register Address (N)                | ACK   |                                       |       |                                       |       |      |

|---------|---------------|---------|-------|-------------------------------------|-------|---------------------------------------|-------|---------------------------------------|-------|------|

|         |               |         | Slave |                                     | Slave | -                                     |       |                                       |       |      |

| RESTART | Slave Address | Read=H  | ACK   | Data read from Register Address (N) | ACK   | Data read from Register Address (N+1) | ACK   | Data read from Register Address (N+2) | NACK  | STOP |

|         |               |         | Slave |                                     | Maste | r                                     | Maste | r                                     | Maste | er   |

Figure 5.

- 9. Controller slave address: bxxxxxxx (7-bit data written into 0x00 EEPROM address. Any address can be set after shipment) EEPROM slave address: b1010xxx (lower-order 3 bits are set to one of the 8 address types prior to shipment. Refer to Table 7)

- 10. EEPROM rewrite time: 10 ms after stop condition (ACK signal is not output during rewrite operation)

- 11. When data is written sequentially into the EEPROM, only the lower-order 4 bits of the register addresses are incremented. <u>Example:</u> When the 4-byte sequential writes are started from address 0x0D, the data is written into the address in the order of 0x0D => 0x0E => 0x0F => 0x00.

Table 7. EEPROM SLAVE ADDRESS SETTINGS (Product Name Differs Depending on Address Type)

| Address Type | Product Name         | EEPROM Slave Address Lower-order 3 bits |

|--------------|----------------------|-----------------------------------------|

| A0           | LC71F7001PVBS0-TLM-H | (0, 0, 0)                               |

| A1           | -                    | (0, 0, 1)                               |

| A2           | -                    | (0, 1, 0)                               |

| A3           | -                    | (0, 1, 1)                               |

| A4           | -                    | (1, 0, 0)                               |

| A5           | -                    | (1, 0, 1)                               |

| A6           | -                    | (1, 1, 0)                               |

| A7           | -                    | (1, 1, 1)                               |

#### **General Registers**

**Table 8. CONTROL REGISTER**

|         | Bit   | 7       | 6   | 5      | 4     | 3     | 2     | 1     | 0   |

|---------|-------|---------|-----|--------|-------|-------|-------|-------|-----|

| Address | Name  | SoftRst | FFR | INTHIZ | IVAL3 | IVAL2 | IVAL1 | IVAL0 | RUN |

| 0x00    | Reset | 0       | 1   | 0      | 0     | 0     | 0     | 0     | 0   |

|         | W/R   | W       | RW  | W      | RW    | RW    | RW    | RW    | RW  |

SoftRst: Software reset

0: Not used

1: Reset (Disabled when the value of 0x24 First Fixed Register is any value other than 0x00)

FFR: Initialization register

0: Normal operation mode

1: Reset value

INTHIZ: Interrupt output high-impedance select

0: Normal operation mode

1: Interrupt output high-impedance

IVAL0-IVAL3: MEASUREMENT INTERVALS, f<sub>CDRV</sub> = 200 kHz SET

| IVAL3 | IVAL2 | IVAL1 | IVAL0 | Measurement Interval |

|-------|-------|-------|-------|----------------------|

| 0     | 0     | 0     | 0     | 0 ms                 |

| 0     | 0     | 0     | 1     | 1 ms                 |

| 0     | 0     | 1     | 0     | 2 ms                 |

| 0     | 0     | 1     | 1     | 4 ms                 |

| 0     | 1     | 0     | 0     | 8 ms                 |

| 0     | 1     | 0     | 1     | 16 ms                |

| 0     | 1     | 1     | 0     | 32 ms                |

| 0     | 1     | 1     | 1     | 64 ms                |

| 1     | 0     | 0     | 0     | 128 ms               |

| 1     | 0     | 0     | 1     | 256 ms               |

| 1     | 0     | 1     | 0     | 512 ms               |

| 1     | 0     | 1     | 1     | 1024 ms              |

| 1     | 1     | 0     | 0     | 2048 ms              |

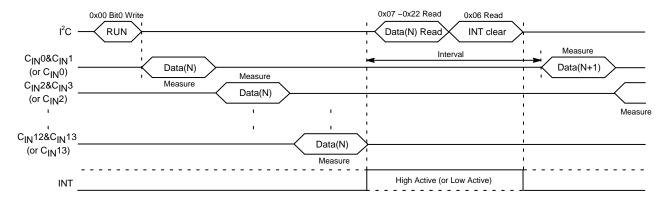

**RUN**: Measurement start

0: Standby (sensor-connection pin is high-impedance state)

1: Measurement start (if OFFCAL = 1, automatic offset calibration is started)

12. When RUN is set to 1, do not write a register value other than RUN = 0 (standby).

**Table 9. CONFIGURATION REGISTER 1**

|         | Bit   | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|-------|------|------|------|------|------|------|------|------|

| Address | Name  | INTZ | SCF3 | SCF2 | SCF1 | SCF0 | OSR2 | OSR1 | OSR0 |

| 0x01    | Reset | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

|         | W/R   | RW   |

INTZ: Interrupt output type select

0: CMOS output

1: N-channel open drain

SCF0-SCF3: SAMPLING CLOCK FREQUENCY (CDRV DRIVE FREQUENCY)

| SCF3 | SCF2 | SCF1 | SCF0 | Sampling Clock Frequency |

|------|------|------|------|--------------------------|

| 0    | 0    | 0    | 0    | 20.8 kHz                 |

| 0    | 0    | 0    | 1    | 31.3 kHz                 |

| 0    | 0    | 1    | 0    | 50.0 kHz                 |

| 0    | 0    | 1    | 1    | 83.3 kHz                 |

| 0    | 1    | 0    | 0    | 100.0 kHz                |

| 0    | 1    | 0    | 1    | 125.0 kHz                |

| 0    | 1    | 1    | 0    | 166.7 kHz                |

| 0    | 1    | 1    | 1    | 200.0 kHz                |

| 1    | 0    | 0    | 0    | 250.0 kHz                |

| 1    | 0    | 0    | 1    | 333.3 kHz                |

| 1    | 0    | 1    | 0    | 500.0 kHz                |

<sup>13.</sup> The optimum frequency varies depending on the sensor load.

#### **OSR0-OSR2: OVERSAMPLING RATIO**

| OSR2 | OSR1 | OSR0 | OSR       |  |  |  |

|------|------|------|-----------|--|--|--|

| 0    | 0    | 0    | 512 times |  |  |  |

| 0    | 0    | 1    | 256 times |  |  |  |

| 0    | 1    | 0    | 128 times |  |  |  |

| 0    | 1    | 1    | 64 times  |  |  |  |

| 1    | 0    | 0    | 32 times  |  |  |  |

| 1    | 0    | 1    | 16 times  |  |  |  |

| 1    | 1    | 0    | 8 times   |  |  |  |

| 1    | 1    | 1    | 4 times   |  |  |  |

**Table 10. CONFIGURATION REGISTER 2**

|         | Bit   | 7      | 6 | 5     | 4       | 3      | 2      | 1    | 0    |

|---------|-------|--------|---|-------|---------|--------|--------|------|------|

| Address | Name  | OFFCAL | - | TPDRV | OFINTEN | INTPOL | INTSEL | AVG1 | AVG0 |

| 0x02    | Reset | 0      | - | 0     | 0       | 0      | 0      | 0    | 0    |

|         | W/R   | RW     | - | RW    | RW      | RW     | RW     | RW   | RW   |

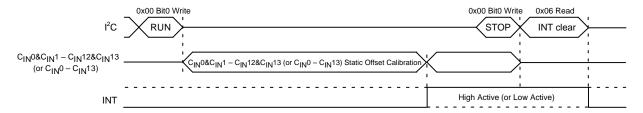

#### OFFCAL: Static offset calibration

- 0: Normal operation mode

- 1: Static offset calibration mode

# TPDRV: Touch panel drive function enable/disable

- 0: Disables the touch panel drive function

- 1: Enables the touch panel drive function. ( $C_{IN}0$  to  $C_{IN}5$  are capacitance drive outputs during X-axis sensing;  $C_{IN}6$  to  $C_{IN}13$  are capacitance drive outputs during Y-axis sensing.)

# OFINTEN: Dynamic offset overflow interrupt enable/disable

- 0: Disables dynamic offset interrupts

- 1: Enables dynamic offset interrupts

<sup>14.</sup> It performs offset calibration for the parasitic capacitance of the sensor pattern using the on-chip capacitance of the LSI. The calibration data is automatically stored in the C<sub>IN</sub> Static Offset Registers.

<sup>15.</sup> When static offset calibration is performed, dynamic offset calibration must be disabled without fail. (Using both static offset calibration and dynamic offset calibration at the same time is prohibited.)

INTPOL: Interrupt polarity

0: High active 1: Low active

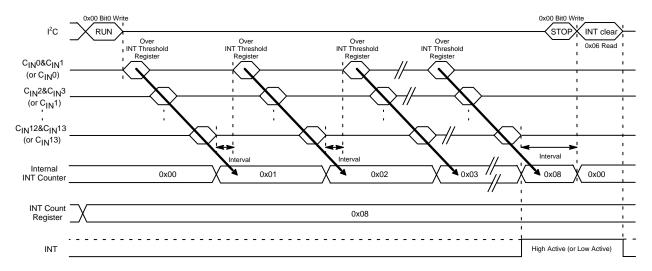

#### **INSEL: INTERRUPT MODE SELECT**

| INTSEL | Interrupt Occurrence Conditions                                                                                                                                                                                                         |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | When the first valid data is established after measurement is started. When offset calibration is completed. When a dynamic offset calibration overflow occurs.                                                                         |

| 1      | When output data whose value exceeds the one specified in the Threshold Register occurs successively the number of times specified in the INT Count Register (operations detected).  When a dynamic offset calibration overflow occurs. |

#### **AVG0-AVG1: MOVING AVERAGING COUNT**

| AVG1 | AVG0      | Moving Averaging Count |  |  |

|------|-----------|------------------------|--|--|

| 0    | 0         | 1 time (no averaging)  |  |  |

| 0    | 1         | 2 times                |  |  |

| 1    | 0 4 times |                        |  |  |

| 1    | 1         | 8 times                |  |  |

16. Assume that the moving average count specified in AVG0–AVG1 is N (= 1, 2, 4, 8). When the number of measurement times is under N, the following averaging data is output.

(Data\_N + Data\_ (N-1) + ~ + Data\_1 + Data\_1 + Data\_1) / N

When the number of measurement times is N or more, the following averaging data is output.

$(Data_N + Data_(N-1) + \sim + Data_3 + Data_2 + Data_1) / N$

Table 11, GPO CONTROL REGISTER 1

|         | Bit   | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|-------|------|------|------|------|------|------|------|------|

| Address | Name  | GPO7 | GPO6 | GPO5 | GPO4 | GPO3 | GPO2 | GPO1 | GPO0 |

| 0x03    | Reset | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

|         | W/R   | RW   |

GPO0-GPO7: GPO output control

0: Low level output 1: High level output

Table 12. GPO CONTROL REGISTER 2

|         | Bit   | 7 | 6 | 5     | 4     | 3     | 2     | 1    | 0    |

|---------|-------|---|---|-------|-------|-------|-------|------|------|

| Address | Name  | - | - | GPO13 | GPO12 | GPO11 | GPO10 | GPO9 | GPO8 |

| 0x04    | Reset | - | - | 0     | 0     | 0     | 0     | 0    | 0    |

|         | W/R   | - | - | RW    | RW    | RW    | RW    | RW   | RW   |

GPO8-GPO13: GPO output control

0: Low level output 1: High level output

#### **Table 13. INT STATUS REGISTER 1**

|         | Bit  | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|------|

| Address | Name | INT7 | INT6 | INT5 | INT4 | INT3 | INT2 | INT1 | INT0 |

| 0x05    | W/R  | R    | R    | R    | R    | R    | R    | R    | R    |

INT0-INT7: C<sub>IN</sub>0 to C<sub>IN</sub>7 operation detection interrupt status flag

0: No interrupt has occurred

1: An interrupt has occurred

**Table 14. INT STATUS REGISTER 2**

|         | Bit  | 7      | 6 | 5     | 4     | 3     | 2     | 1    | 0    |

|---------|------|--------|---|-------|-------|-------|-------|------|------|

| Address | Name | INTOFF | - | INT13 | INT12 | INT11 | INT10 | INT9 | INT8 |

| 0x06    | W/R  | R      | - | R     | R     | R     | R     | R    | R    |

INTOFF: Dynamic offset overflow

0: No interrupt has occurred

1: The dynamic offset has exceeded the expected range (Dynamic Offset Threshold register > C<sub>IN</sub> Dynamic Offset Register)

INT8-INT13:  $C_{IN}8$  to  $C_{IN}13$  operation detection interrupt status flag

0: No interrupt has occurred

1: An interrupt has occurred

17. Reading the INT Status Register 2 in byte units clears the interrupt outputs and the interrupt status flags.

When the INT Status Register 2 is read in sequential order, the interrupt outputs and interrupt status flags are not cleared.

Table 15. DATA00 REGISTER TO DATA27 REGISTER

|              | Bit  | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| Address      | Name | DATA7 | DATA6 | DATA5 | DATA4 | DATA3 | DATA2 | DATA1 | DATA0 |

| 0x07 to 0x22 | W/R  | R     | R     | R     | R     | R     | R     | R     | R     |

These registers store the computation results for Data Register =  $\Sigma\Delta A/D$  converter data +  $C_{IN}$  Static Offset Registers (0x49 to 0x52) +  $C_{IN}$  Dynamic Offset Registers (0x53 to 0x66) in two's complement number.

# Example:

0x7FFF = +32767  $0x0000 = \pm 0$ 0x8000 = -32768

| Data00 Register | C <sub>IN</sub> 0 measurement data (higher-order 8 bits)                                                                  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------|

| Data01 Register | C <sub>IN</sub> 1 measurement data (higher-order 8 bits) C <sub>IN</sub> 0 data is valid in the differential input mode   |

| Data02 Register | C <sub>IN</sub> 2 measurement data (higher-order 8 bits)                                                                  |

| Data03 Register | C <sub>IN</sub> 3 measurement data (higher-order 8 bits) C <sub>IN</sub> 2 data is valid in the differential input mode   |

| Data04 Register | C <sub>IN</sub> 4 measurement data (higher-order 8 bits)                                                                  |

| Data05 Register | C <sub>IN</sub> 5 measurement data (higher-order 8 bits) C <sub>IN</sub> 4 data is valid in the differential input mode   |

| Data06 Register | C <sub>IN</sub> 6 measurement data (higher-order 8 bits)                                                                  |

| Data07 Register | C <sub>IN</sub> 7 measurement data (higher-order 8 bits) C <sub>IN</sub> 6 data is valid in the differential input mode   |

| Data08 Register | C <sub>IN</sub> 8 measurement data (higher-order 8 bits)                                                                  |

| Data09 Register | C <sub>IN</sub> 9 measurement data (higher-order 8 bits) C <sub>IN</sub> 8 data is valid in the differential input mode   |

| Data10 Register | C <sub>IN</sub> 10 measurement data (higher-order 8 bits)                                                                 |

| Data11 Register | C <sub>IN</sub> 11 measurement data (higher-order 8 bits) C <sub>IN</sub> 10 data is valid in the differential input mode |

| Data12 Register | C <sub>IN</sub> 12 measurement data (higher-order 8 bits)                                                                 |

| Data13 Register | C <sub>IN</sub> 13 measurement data (higher-order 8 bits) C <sub>IN</sub> 12 data is valid in the differential input mode |

|-----------------|---------------------------------------------------------------------------------------------------------------------------|

| Data14 Register | C <sub>IN</sub> 0 measurement data (lower-order 8 bits)                                                                   |

| Data15 Register | C <sub>IN</sub> 1 measurement data (lower-order 8 bits) C <sub>IN</sub> 0 data is valid in the differential input mode    |

| Data16 Register | C <sub>IN</sub> 2 measurement data (lower-order 8 bits)                                                                   |

| Data17 Register | C <sub>IN</sub> 3 measurement data (lower-order 8 bits) C <sub>IN</sub> 2 data is valid in the differential input mode    |

| Data18 Register | C <sub>IN</sub> 4 measurement data (lower-order 8 bits)                                                                   |

| Data19 Register | C <sub>IN</sub> 5 measurement data (lower-order 8 bits) C <sub>IN</sub> 4 data is valid in the differential input mode    |

| Data20 Register | C <sub>IN</sub> 6 measurement data (lower-order 8 bits)                                                                   |

| Data21 Register | C <sub>IN</sub> 7 measurement data (lower-order 8 bits) C <sub>IN</sub> 6 data is valid in the differential input mode    |

| Data22 Register | C <sub>IN</sub> 8 measurement data (lower-order 8 bits)                                                                   |

| Data23 Register | C <sub>IN</sub> 9 measurement data (lower-order 8 bits) C <sub>IN</sub> 8 data is valid in the differential input mode    |

| Data24 Register | C <sub>IN</sub> 10 measurement data (lower-order 8 bits)                                                                  |

| Data25 Register | C <sub>IN</sub> 11 measurement data (lower-order 8 bits) C <sub>IN</sub> 10 data is valid in the differential input mode  |

| Data26 Register | C <sub>IN</sub> 12 measurement data (lower-order 8 bits)                                                                  |

| Data27 Register | C <sub>IN</sub> 13 measurement data (lower-order 8 bits) C <sub>IN</sub> 12 data is valid in the differential input mode  |

|                 |                                                                                                                           |

#### Table 16. EEPROM WRITE PROTECT/INITIALIZE REGISTER

|         | Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|---------|-------|---|---|---|---|---|---|---|-------|

| Address | Name  | - | - | - | - | - | - | - | EEPWP |

| 0x23    | Reset | - | - | - | - | - | - | - | 0     |

|         | W/R   | _ | - | _ | _ | - | _ | - | RW    |

Internal EEPROM write protection and initialization

# EEPWP:

0: Enables write operation (default)

1: Disables write operation

18. Be sure to perform writes to this register in the order of  $0x01 \rightarrow 0x00 \rightarrow 0x01$  during power-on-time initialization.

**Table 17. FIRST FIXED REGISTER**

|         | Bit   | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|-------|------|------|------|------|------|------|------|------|

| Address | Name  | FFR7 | FFR6 | FFR5 | FFR4 | FFR3 | FFR2 | FFR1 | FFR0 |

| 0x24    | Reset | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

|         | W/R   | RW   |

Initialization register

#### FFR0-FFR7:

0: Reset value (fixed)

1: Write protected

19. Be sure to write a 0x00 into this register when using the LSI. The LSI will not run normally with any value other than 0x00.

#### **Parameter Registers**

Table 18. CONTROLLER I2C SLAVE ADDRESS REGISTER

|         | Bit  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0 |

|---------|------|--------|--------|--------|--------|--------|--------|--------|---|

| Address | Name | SLAVE6 | SLAVE5 | SLAVE4 | SLAVE3 | SLAVE2 | SLAVE1 | SLAVE0 | - |

| 0x25    | W/R  | R      | R      | R      | R      | R      | R      | R      | - |

SLAVE0-SLAVE6: Controller side  $I^2C$  Slave Address (7 bits not including the R/W bit). This takes effect by turning the LSI off and back on again after writing this value into the EEPROM address 0x00

Table 19. C<sub>IN</sub>0-C<sub>IN</sub>1: CONFIGURATION REGISTER 1

|         | Bit  | 7 | 6       | 5       | 4                   | 3                   | 2                    | 1                    | 0                      |

|---------|------|---|---------|---------|---------------------|---------------------|----------------------|----------------------|------------------------|

| Address | Name | - | Cref1EN | Cref0EN | C <sub>IN</sub> 1EN | C <sub>IN</sub> 0EN | C <sub>IN</sub> 1POL | C <sub>IN</sub> 0POL | C <sub>IN</sub> 01diff |

| 0x26    | W/R  | - | RW      | RW      | RW                  | RW                  | RW                   | RW                   | RW                     |

Cref0EN-Cref1EN: C<sub>IN</sub>0, C<sub>IN</sub>1 external reference capacitance connection enable/disable

- 0: Connects no reference capacitance in the single input mode

- 1: Connects the reference capacitance in the single input mode

C<sub>IN</sub>0EN-C<sub>IN</sub>1EN: C<sub>IN</sub>0, C<sub>IN</sub>1 capacitance (touch) detection enable/disable

- 0: Disables capacitance (touch) detection (the sensor connection pin is in high-impedance state)

- 1: Enables capacitance (touch) detection

20. In the differential input mode, CINOEN and CIN1EN must be set to 0 or 1 at the same time (setting them to 01 and 10 is prohibited).

C<sub>IN</sub>0POL-C<sub>IN</sub>1POL: C<sub>IN</sub>0, C<sub>IN</sub>1 charge amplifier input polarity (valid only when single input has been selected)

- 0: Positive input

- 1: Negative input

C<sub>IN</sub>01diff: C<sub>IN</sub>0, C<sub>IN</sub>1 single input/differential input select

- 0: Single input

- 1: Differential input (C<sub>IN</sub>0 is connected to the positive input of the charge amplifier, and C<sub>IN</sub>1 is connected to the negative input)

Table 20. C<sub>IN</sub>0-C<sub>IN</sub>1: CONFIGURATION REGISTER 2

|                 | Bit  | 7            | 6            | 5            | 4            | 3            | 2            | 1      | 0      |

|-----------------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------|--------|

| Address<br>0x27 | Name | OFFCAL<br>D1 | OFFCAL<br>D0 | GPO1SE<br>L1 | GPO1SE<br>L0 | GPO0SE<br>L1 | GPO0SE<br>L0 | INT1EN | INT0EN |

|                 | W/R  | RW           | RW           | RW           | RW           | RW           | RW           | RW     | RW     |

OFFCALD0-OFFCALD1: C<sub>IN</sub>0, C<sub>IN</sub>1 dynamic offset calibration. Any offset caused by changes in temperature and other factors is compensated using dynamic computation.

- 0: Normal operation mode

- 1: Dynamic offset calibration mode

21. In the differential input mode, OFFCALD0 and OFFCALD1 must be set to 0 or 1 at the same time (setting them to 01 and 10 is prohibited).

# GPO0(1)SEL0-GPO0(1)SEL1: CINO, CIN1 PIN GPO MODE SELECT

| GPO0(1)SEL1 | GPO0(1)SEL0 | Mode                                                                                                                                          |

|-------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 0           | 0           | Normal capacitance detection mode                                                                                                             |

| 0           | 1           | Standard GPO mode The values set by the GPO Control Register 1, 2 are output at all times. Capacitance detection is not performed.            |

| 1           | 0           | LED drive mode The values set by the GPO Control Register 1, 2 are output during the measurement interval time after capacitance is detected. |

<sup>22.</sup> In the differential input mode, the standard GPO mode cannot be used.

INT0EN-INT1EN: C<sub>IN</sub>0, C<sub>IN</sub>1 operation detection interrupt enable/disable

- 0: Disables operation detection interrupts.

- 1: Enables operation detection interrupts.

- 23. In the differential input mode, INT0EN and INT1EN must be set to 0 or 1 at the same time (setting them to 01 and 10 is prohibited).

- $C_{IN}2-C_{IN}3$  Configuration Register 1 (Address 0x28) => The contents are the same as those in the  $C_{IN}0-C_{IN}1$  Configuration Register 1.

- $C_{IN}2-C_{IN}3$  Configuration Register 2 (Address 0x29) => The contents are the same as those in the  $C_{IN}0-C_{IN}1$  Configuration Register 2.

- $C_{IN}4-C_{IN}5$  Configuration Register 1 (Address 0x2A) => The contents are the same as those in the  $C_{IN}0-C_{IN}1$  Configuration Register 1.

- $C_{IN}4-C_{IN}5$  Configuration Register 2 (Address 0x2B) => The contents are the same as those in the  $C_{IN}0-C_{IN}1$  Configuration Register 2.

- $C_{IN}6-C_{IN}7$  Configuration Register 1 (Address 0x2C) => The contents are the same as those in the  $C_{IN}0-C_{IN}1$  Configuration Register 1.

- $C_{IN}6-C_{IN}7$  Configuration Register 2 (Address 0x2D) => The contents are the same as those in the  $C_{IN}0-C_{IN}1$  Configuration Register 2.

- $C_{IN}8-C_{IN}9$  Configuration Register 1 (Address 0x2E) => The contents are the same as those in the  $C_{IN}0-C_{IN}1$  Configuration Register 1.

- $C_{IN}8-C_{IN}9$  Configuration Register 2 (Address 0x2F) => The contents are the same as those in the  $C_{IN}0-C_{IN}1$  Configuration Register 2.

- $C_{IN}10$ – $C_{IN}11$  Configuration Register 1 (Address 0x30) => The contents are the same as those in the  $C_{IN}0$ – $C_{IN}1$  Configuration Register 1.

- $C_{IN}10-C_{IN}11$  Configuration Register 2 (Address 0x31) => The contents are the same as those in the  $C_{IN}0-C_{IN}1$  Configuration Register 2.

Table 21. C<sub>IN</sub>12-C<sub>IN</sub>13: CONFIGURATION REGISTER 1

|         | Bit  | 7                    | 6   | 5                    | 4                    | 3                    | 2                     | 1                     | 0                        |

|---------|------|----------------------|-----|----------------------|----------------------|----------------------|-----------------------|-----------------------|--------------------------|

| Address | Name | C <sub>DRV</sub> SEL | FFR | C <sub>DRV</sub> BEN | C <sub>IN</sub> 13EN | C <sub>IN</sub> 12EN | C <sub>IN</sub> 13POL | C <sub>IN</sub> 12POL | C <sub>IN</sub> 1213diff |

| 0x32    | W/R  | RW                   | RW  | RW                   | RW                   | RW                   | RW                    | RW                    | RW                       |

CDRVSEL: CDRV/INT pin function select

- 0: Normal capacitance drive pin

- 1: Interrupt output pin

FFR: Initialization register

- 0: Normal operation mode

- 1: Prohibited

C<sub>DRV</sub>BEN: C<sub>IN</sub>13 C<sub>DRV</sub>B (inverted signal of C<sub>DRV</sub>) capacitance drive enable/disable

- 0: Does not set C<sub>IN</sub>13 as the C<sub>DRV</sub>B capacitance drive pin

- 1: Set C<sub>IN</sub>13 as the C<sub>DRV</sub>B capacitance drive pin

# C<sub>IN</sub>12EN-C<sub>IN</sub>13EN:

C<sub>IN</sub>12 capacitance (touch) detection enable/external reference capacitance connection pin

$C_{IN}13$  capacitance (touch) detection enable and  $C_{DRV}B$  output/interrupt output select

- 0: Does not perform capacitance (touch) detection. (Sensor connection pin C<sub>IN</sub>12 => external reference capacitance connection pin; sensor connection pin C<sub>IN</sub>13 => C<sub>DRV</sub>B output/interrupt output)

- 1: Performs capacitance (touch) detection

24. In the differential input mode, C<sub>IN</sub>12EN and C<sub>IN</sub>13EN must be set to 0 or 1 at the same time (setting them to 01 and 10 is prohibited).

C<sub>IN</sub>12POL-C<sub>IN</sub>13POL: C<sub>IN</sub>12, C<sub>IN</sub>13 charge amplifier input polarity (valid only when single input is selected)

- 0: Positive input

- 1: Negative input

C<sub>IN</sub>1213diff: C<sub>IN</sub>12, C<sub>IN</sub>13 single/differential input select

- 0: Single input

- 1: Differential input (C<sub>IN</sub>12 is connected to the positive input of the charge amplifier, and C<sub>IN</sub>13 is connected to the negative input).

| C <sub>DRV</sub> BEN | C <sub>IN</sub> 13EN | C <sub>IN</sub> 12EN | C <sub>IN</sub> 1213Diff | C <sub>IN</sub> 13 Pin    | C <sub>IN</sub> 12 Pin             |

|----------------------|----------------------|----------------------|--------------------------|---------------------------|------------------------------------|

| 1                    | 0                    | 0                    | 0                        | C <sub>DRV</sub> B output | Connected to reference capacitance |

| 0                    | 0                    | 0                    | 0 Interrupt output       |                           | Disabled                           |

| 0                    | 0                    | 1                    | 0 Interrupt output       |                           | Capacitance sensor input           |

| 0                    | 1                    | 0                    | 0                        | Capacitance sensor input  | Disabled                           |

| 0                    | 1                    | 1                    | 0                        | Capacitance sensor input  | Capacitance sensor input           |

| 0                    | 0                    | 0                    | 1                        | Disabled                  | Disabled                           |

| 0                    | 1                    | 1                    | 1                        | Capacitance sensor input  | Capacitance sensor input           |

<sup>25.</sup> Any value combinations other than those listed above are not allowed.

Table 22. C<sub>IN</sub>12-C<sub>IN</sub>13: CONFIGURATION REGISTER 2

|         | Bit  | 7         | 6         | 5         | 4         | 3         | 2         | 1       | 0       |

|---------|------|-----------|-----------|-----------|-----------|-----------|-----------|---------|---------|

| Address | Name | OFFCALD13 | OFFCALD12 | GPO13SEL1 | GPO13SEL0 | GPO12SEL1 | GPO12SEL0 | INT13EN | INT12EN |

| 0x33    | W/R  | W         | W         | W         | W         | W         | W         | RW      | RW      |

OFFCALD12-OFFCALD13: C<sub>IN</sub>12, C<sub>IN</sub>13 dynamic offset calibration. Any offset caused by changes in temperature and other factors is compensated by dynamic computation.

- 0: Normal operation mode

- 1: Dynamic offset calibration mode

26. In the differential input mode, OFFCALD12 and OFFCALD13 must be set to 0 or 1 at the same time (setting them to 01 and 10 is prohibited).

# GPO12(13)SEL0-GPO12(13)SEL1: C<sub>IN</sub>12, C<sub>IN</sub>13 PIN GPO MODE SELECT

| GPO12(13)SEL1 | GPO12(13)SEL0 | Mode                                                                                                                                          |

|---------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | 0             | Normal capacitance detection mode                                                                                                             |

| 0             | 1             | Standard GPO mode The values set by the GPO Control Register 1, 2 are output at all times. Capacitance detection is not performed.            |

| 1             | 0             | LED drive mode The values set by the GPO Control Register 1, 2 are output during the measurement interval time after capacitance is detected. |

<sup>27.</sup> n the differential input mode, the standard GPO mode cannot be used.

INT12EN-INT13EN: C<sub>IN</sub>12, C<sub>IN</sub>13 operation detection interrupt enable/disable

- 0: Disables operation detection interrupts

- 1: Enables operation detection interrupts

- 28. In the differential input mode, INT12EN and INT13EN must be set to 0 or 1 at the same time (setting them to 01 and 10 is prohibited).

#### **Table 23. DATA CENTER REGISTER**

|         | Bit  | 7 | 6 | 5 | 4 | 3 | 2 | 1       | 0       |

|---------|------|---|---|---|---|---|---|---------|---------|

| Address | Name | - | - | - | - | - | - | CENTER1 | CENTER0 |

| 0x34    | W/R  | _ | - | _ | - | - | _ | RW      | RW      |

Reference values used when no touch operations are performed. Offset calibration is performed in such a way that the values specified in the Data Center Register are set.

| CENTER1 | CENTER0 | Offset Calibration Center Value |

|---------|---------|---------------------------------|

| 0       | 0       | -24576                          |

| 0       | 1       | -16384                          |

| 1       | 0       | -8192                           |

| 1       | 1       | ±0                              |

<sup>29.</sup> In the differential input mode, the offset calibration center value is fixed at  $\pm 0$ .

**Table 24. SINGLE INT THRESHOLD REGISTER**

|         | Bit  | 7 | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|------|---|-------|-------|-------|-------|-------|-------|-------|

| Address | Name | - | SMTH6 | SMTH5 | SMTH4 | SMTH3 | SMTH2 | SMTH1 | SMTH0 |

| 0x35    | W/R  | - | RW    |

This register determines the threshold value beyond which interrupt occurs in the single input mode.

The operation detection interrupt is generated when the condition in which the measurement data is greater than the threshold value in the single input mode has occurred continuously for the number of times specified in the INT Count Register. The interrupt generation flag in the INT Status Register 1, 2 is then set.

| Single INT Threshold Register | Threshold Value |

|-------------------------------|-----------------|

| 0x00                          | -32768          |

| 0x01                          | -32256          |

| 0x02                          | -31744          |

|                               |                 |

| 0x7D                          | +31232          |

| 0x7E                          | +31744          |

| 0x7F                          | +32256          |

#### Table 25. DIFFERENTIAL INT THRESHOLD REGISTER

|         | Bit  | 7 | 6 | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|------|---|---|--------|--------|--------|--------|--------|--------|

| Address | Name | - | - | DMPTH5 | DMPTH4 | DMPTH3 | DMPTH2 | DMPTH1 | DMPTH0 |

| 0x36    | W/R  | _ | _ | RW     | RW     | RW     | RW     | RW     | RW     |

This register determines the threshold value beyond which positive side interrupt occurs in the differential input mode. The operation detection interrupt is generated when the condition in which the measurement data exceeds the threshold value range in the differential input mode has occurred continuously for the number of times specified in the INT Count Register. The interrupt generation flag in the INT Status Register 1, 2 is then set.

| Differential INT Threshold Register | Threshold Value  |

|-------------------------------------|------------------|

| 0x00                                | ±0               |

| 0x01                                | -512 to +511     |

| 0x02                                | -1024 to +1023   |

|                                     |                  |

| 0x3D                                | -31232 to +31231 |

| 0x3E                                | -31744 to +31743 |

| 0x3F                                | -32256 to +32255 |

# **Table 26. INT COUNT REGISTER**

|         | Bit  | 7 | 6 | 5 | 4 | 3       | 2       | 1       | 0       |

|---------|------|---|---|---|---|---------|---------|---------|---------|

| Address | Name | - | - | - | - | INTCNT3 | INTCNT2 | INTCNT1 | INTCNT0 |

| 0x37    | W/R  | _ | - | - | - | RW      | RW      | RW      | RW      |

#### Interrupt count setting:

An interrupt is generated when the condition in which the measured value that exceeds the Threshold Register range occurs continuously for the number of times specified in the INT Count Register.

$0x00 \Rightarrow 1 \text{ time } 0x0F \Rightarrow 16 \text{ times}$

# Table 27. C<sub>IN</sub>0 GAIN REGISTER

|         | Bit  | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|---------|------|----------|----------|----------|----------|----------|----------|----------|----------|

| Address | Name | Gain0_B3 | Gain0_B2 | Gain0_B1 | Gain0_B0 | Gain0_A3 | Gain0_A2 | Gain0_A1 | Gain0_A0 |

| 0x38    | W/R  | RW       |

Gain0\_A0-Gain0\_A3: Gain of the first stage charge amplifier (0000 => minimum gain, 1111 => maximum gain)

Gain0\_B0-Gain0\_B3: Gain of the subsequent stage charge amplifier (0000 => minimum gain, 1111 => maximum gain)

C<sub>IN</sub>0 (1-13) First stage charge amplifier gain settings

Calculation formula:  $\Delta V = \Delta C/Cf \times C_{DRV}$

Where:

$\Delta V$ : Output voltage of the first stage amplifier

$\Delta C$ : Change in input capacitance  $C_{DRV}$ : Output voltage of  $C_{DRV}$

| Gain A3 | Gain A2 | Gain A1 | Gain A0 | Cf (fF)                     |

|---------|---------|---------|---------|-----------------------------|

| 0       | 0       | 0       | 0       | 1600 (minimum gain setting) |

| 0       | 0       | 0       | 1       | 1500                        |

| 0       | 0       | 1       | 0       | 1400                        |

| 0       | 0       | 1       | 1       | 1300                        |

| 0       | 1       | 0       | 0       | 1200                        |

| 0       | 1       | 0       | 1       | 1100                        |

| 0       | 1       | 1       | 0       | 1000                        |

| 0       | 1       | 1       | 1       | 900                         |

| 1       | 0       | 0       | 0       | 800                         |

| 1       | 0       | 0       | 1       | 700                         |

| 1       | 0       | 1       | 0       | 600                         |

| 1       | 0       | 1       | 1       | 500                         |

| 1       | 1       | 0       | 0       | 400                         |

| 1       | 1       | 0       | 1       | 300                         |

| 1       | 1       | 1       | 0       | 200                         |

| 1       | 1       | 1       | 1       | 100 (maximum gain setting)  |

C<sub>IN</sub>0 (1–13) Subsequent stage amplifier gain settings

| Gain B3 | Gain B2 | Gain B1 | Gain B0 | Gain (Times)              |

|---------|---------|---------|---------|---------------------------|

| 0       | 0       | 0       | 0       | 1 (minimum gain setting)  |

| 0       | 0       | 0       | 1       | 2                         |

| 0       | 0       | 1       | 0       | 3                         |

| 0       | 0       | 1       | 1       | 4                         |

| 0       | 1       | 0       | 0       | 5                         |

| 0       | 1       | 0       | 1       | 6                         |

| 0       | 1       | 1       | 0       | 7                         |

| 0       | 1       | 1       | 1       | 8                         |

| 1       | 0       | 0       | 0       | 9                         |

| 1       | 0       | 0       | 1       | 10                        |

| 1       | 0       | 1       | 0       | 11                        |

| 1       | 0       | 1       | 1       | 12                        |

| 1       | 1       | 0       | 0       | 13                        |

| 1       | 1       | 0       | 1       | 14                        |

| 1       | 1       | 1       | 0       | 15                        |

| 1       | 1       | 1       | 1       | 16 (maximum gain setting) |

C<sub>IN</sub>1 Gain Register (Address 0x39) => The contents are the same as those in the C<sub>IN</sub>0 Gain Register. The value of C<sub>IN</sub>0 Gain Register is valid in the differential input mode. C<sub>IN</sub>2 Gain Register (Address 0x3A) => The contents are the same as those in the C<sub>IN</sub>0 Gain Register. C<sub>IN</sub>3 Gain Register (Address 0x3B) => The contents are the same as those in the C<sub>IN</sub>0 Gain Register. The value of C<sub>IN</sub>2 Gain Register is valid in the differential input mode. C<sub>IN</sub>4 Gain Register (Address 0x3C) => The contents are the same as those in the C<sub>IN</sub>0 Gain Register. C<sub>IN</sub>5 Gain Register (Address 0x3D) => The contents are the same as those in the C<sub>IN</sub>0 Gain Register. The value of C<sub>IN</sub>4 Gain Register is valid in the differential input mode. C<sub>IN</sub>6 Gain Register (Address 0x3E)  $\Rightarrow$  The contents are the same as those in the  $C_{IN}0$  Gain Register. C<sub>IN</sub>7 Gain Register (Address 0x3F) => The contents are the same as those in the C<sub>IN</sub>0 Gain Register. The value of C<sub>IN</sub>6 Gain Register is valid in the differential input mode.

| C <sub>IN</sub> 8 Gain Register (Address 0x40)<br>C <sub>IN</sub> 9 Gain Register (Address 0x41)   | The contents are the same as those in the $C_{IN}0$ Gain Register. The contents are the same as those in the $C_{IN}0$ Gain Register. The value of $C_{IN}8$ Gain Register is valid in the differential input mode.  |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C <sub>IN</sub> 10 Gain Register (Address 0x42)<br>C <sub>IN</sub> 11 Gain Register (Address 0x43) | The contents are the same as those in the $C_{IN}0$ Gain Register. The contents are the same as those in the $C_{IN}0$ Gain Register. The value of $C_{IN}10$ Gain Register is valid in the differential input mode. |

| C <sub>IN</sub> 12 Gain Register (Address 0x44)<br>C <sub>IN</sub> 13 Gain Register (Address 0x45) | The contents are the same as those in the $C_{IN}0$ Gain Register. The contents are the same as those in the $C_{IN}0$ Gain Register. The value of $C_{IN}12$ Gain Register is valid in the differential input mode. |

Table 28. C<sub>IN</sub>0 CDAC OFFSET POS REGISTER

|         | Bit  | 7 | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|---------|------|---|---------|---------|---------|---------|---------|---------|---------|

| Address | Name | - | C0ADOP6 | C0ADOP5 | C0ADOP4 | C0ADOP3 | C0ADOP2 | C0ADOP1 | C0ADOP0 |

| 0x46    | W/R  | ı | RW      |

This register is used to perform offset adjustment for the parasitic capacitance of the sensor pattern using the on-chip capacitance DA converter. The contents of this register are automatically updated by the static offset calibration command. Offset adjustment range: 62.5 fF/LSB

Table 29. CINO CDAC OFFSET NEG REGISTER

|         | Bit  | 7 | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|---------|------|---|---------|---------|---------|---------|---------|---------|---------|

| Address | Name | - | C0ADON6 | C0ADON5 | C0ADON4 | C0ADON3 | C0ADON2 | C0ADON1 | C0ADON0 |

| 0x47    | W/R  | - | RW      |

This register is used to perform offset adjustment for the parasitic capacitance of the sensor pattern using the on-chip capacitance DA converter. The contents of the register are automatically updated by the static offset calibration command. Offset adjustment range: 62.5 fF/LSB

| C <sub>IN</sub> 1 CDAC Offset Pos Register (Address 0x48) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Pos Register. |

|-----------------------------------------------------------|----|-------------------------------------------------------------------------------|

| C <sub>IN</sub> 1 CDAC Offset Neg Register (Address 0x49) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Neg Register. |

| C <sub>IN</sub> 2 CDAC Offset Pos Register (Address 0x4A) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Pos Register. |

| C <sub>IN</sub> 2 CDAC Offset Neg Register (Address 0x4B) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Neg Register. |

| C <sub>IN</sub> 3 CDAC Offset Pos Register (Address 0x4C) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Pos Register. |

| C <sub>IN</sub> 3 CDAC Offset Neg Register (Address 0x4D) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Neg Register. |

| C <sub>IN</sub> 4 CDAC Offset Pos Register (Address 0x4E) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Pos Register. |

| C <sub>IN</sub> 4 CDAC Offset Neg Register (Address 0x4F) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Neg Register. |

| C <sub>IN</sub> 5 CDAC Offset Pos Register (Address 0x50) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Pos Register. |

| C <sub>IN</sub> 5 CDAC Offset Neg Register (Address 0x51) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Neg Register. |

| C <sub>IN</sub> 6 CDAC Offset Pos Register (Address 0x52) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Pos Register. |

| C <sub>IN</sub> 6 CDAC Offset Neg Register (Address 0x53) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Neg Register. |

| C <sub>IN</sub> 7 CDAC Offset Pos Register (Address 0x54)  | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Pos Register. |

|------------------------------------------------------------|----|-------------------------------------------------------------------------------|

| C <sub>IN</sub> 7 CDAC Offset Neg Register (Address 0x55)  | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Neg Register. |

| C <sub>IN</sub> 8 CDAC Offset Pos Register (Address 0x56)  | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Pos Register. |

| C <sub>IN</sub> 8 CDAC Offset Neg Register (Address 0x57)  | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Neg Register. |

| C <sub>IN</sub> 9 CDAC Offset Pos Register (Address 0x58)  | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Pos Register. |

| C <sub>IN</sub> 9 CDAC Offset Neg Register (Address 0x59)  | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Neg Register. |

| C <sub>IN</sub> 10 CDAC Offset Pos Register (Address 0x5A) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Pos Register. |

| C <sub>IN</sub> 10 CDAC Offset Neg Register (Address 0x5B) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Neg Register. |

| C <sub>IN</sub> 11 CDAC Offset Pos Register (Address 0x5C) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Pos Register. |

| C <sub>IN</sub> 11 CDAC Offset Neg Register (Address 0x5D) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Neg Register. |

| C <sub>IN</sub> 12 CDAC Offset Pos Register (Address 0x5E) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Pos Register. |

| C <sub>IN</sub> 12 CDAC Offset Neg Register (Address 0x5F) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Neg Register. |

| C <sub>IN</sub> 13 CDAC Offset Pos Register (Address 0x60) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Pos Register. |

| C <sub>IN</sub> 13 CDAC Offset Neg Register (Address 0x61) | => | The contents are the same as those in the $C_{IN}0$ CDAC Offset Neg Register. |

Table 30.  $C_{\rm IN}$ 0 STATIC OFFSET REGISTER

|         | Bit  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|------|--------|--------|--------|--------|--------|--------|--------|--------|

| Address | Name | C0SOF7 | C0SOF6 | C0SOF5 | C0SOF4 | C0SOF3 | C0SOF2 | C0SOF1 | C0SOF0 |

| 0x62    | W/R  | RW     |

The resister is used to perform offset compensation by computation for the portion which cannot be compensated by the offset adjustment that uses the on-chip capacitance D/A converter. (two's complement)

The contents of this register are automatically updated by the static offset calibration command.

| C0SOF7-0 | Added Value (Two's Complement) |

|----------|--------------------------------|

| 0x7F     | +16256 (0x3F80)                |

| 0x7E     | +16128 (0x3F00)                |

| 0x7D     | +16000 (0x3E80)                |

|          | I                              |

| 0x01     | +128 (0x0080)                  |

| 0x00     | 0 (0x0000)                     |

| 0xFF     | -128 (0xFFFF)                  |

|          | 1                              |

| 0x82     | -16128 (0xC17F)                |

| 0x81     | -16256 (0xC0FF)                |

| 0x80     | -16384 (0xC07F)                |

| C <sub>IN</sub> 1 Static Offset Register (Address 0x63) =>                                                              | The contents are the same as those in the $C_{IN}0$ Static Offset Register. The value of $C_{IN}0$ Static Offset Register is valid in the differential input mode.                                                                              |

|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C <sub>IN</sub> 2 Static Offset Register (Address 0x64) => C <sub>IN</sub> 3 Static Offset Register (Address 0x65) =>   | The contents are the same as those in the $C_{IN}0$ Static Offset Register. The contents are the same as those in the $C_{IN}0$ Static Offset Register. The value of $C_{IN}2$ Static Offset Register is valid in the differential input mode.  |

|                                                                                                                         | The contents are the same as those in the $C_{IN}0$ Static Offset Register. The contents are the same as those in the $C_{IN}0$ Static Offset Register. The value of $C_{IN}4$ Static Offset Register is valid in the differential input mode.  |

|                                                                                                                         | The contents are the same as those in the $C_{IN}0$ Static Offset Register. The contents are the same as those in the $C_{IN}0$ Static Offset Register. The value of $C_{IN}6$ Static Offset Register is valid in the differential input mode.  |

|                                                                                                                         | The contents are the same as those in the $C_{IN}0$ Static Offset Register. The contents are the same as those in the $C_{IN}0$ Static Offset Register. The value of $C_{IN}8$ Static Offset Register is valid in the differential input mode.  |

| $C_{IN}10$ Static Offset Register (Address 0x6C) => $C_{IN}11$ Static Offset Register (Address 0x6D) =>                 |                                                                                                                                                                                                                                                 |

| C <sub>IN</sub> 12 Static Offset Register (Address 0x6E) => C <sub>IN</sub> 13 Static Offset Register (Address 0x6F) => | The contents are the same as those in the $C_{IN}0$ Static Offset Register. The contents are the same as those in the $C_{IN}0$ Static Offset Register. The value of $C_{IN}12$ Static Offset Register is valid in the differential input mode. |

Table 31. C<sub>IN</sub>0 DYNAMIC OFFSET REGISTER

|         | Bit  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|------|--------|--------|--------|--------|--------|--------|--------|--------|

| Address | Name | C0DOF7 | C0DOF6 | C0DOF5 | C0DOF4 | C0DOF3 | C0DOF2 | C0DOF1 | C0DOF0 |