## 1A Ultra-Low Noise Wide-Bandwidth High PSRR Low-Dropout Linear Regulator

## Features

- Input Voltage Range: 2.6V to 6.5V

- Output Voltage Range: 0.8V to 6V

- Low Quiescent Current: 210uA (TYP)

- Ultra-Low Output Noise: 6 $\mu$ V<sub>RMS</sub> Typical (100Hz to 100kHz) at 1A Load

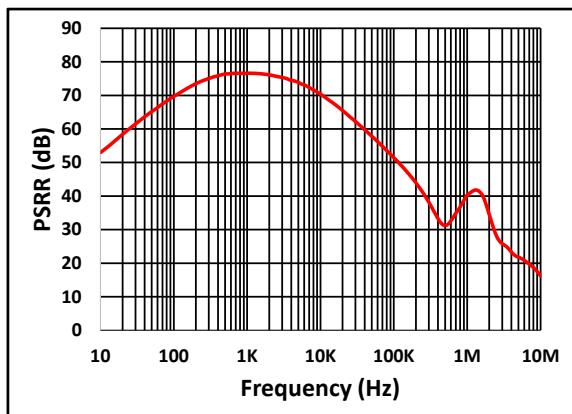

- High PSRR: Over 70dB at 1kHz and 40dB at 1MHz

- 2.0% Accuracy Over Line, Load and Temperature

- Very Low Dropout: 160mV (TYP) at 1A Load

- Excellent Transient Response

- Thermal Shutdown and Over-Current Protection

- Stable with a 22 $\mu$ F or larger ceramic capacitor

- Operating Junction Temperature: -40 $^{\circ}$ C to +125 $^{\circ}$ C

- Available packages: VSON-8-EP(3x3)

## Description

The device is an ultra-low noise (6 $\mu$ V<sub>RMS</sub>), high PSRR, low dropout voltage regulator capable of sourcing 1A current. The output is adjustable with external resistors from 0.8V to 6V. The device has a wide input voltage range from 2.6V to 6.5V

The device is designed to power noise-sensitive components such as found in high-speed communications, video, medical, or test and measurement applications. The very low output noise and wideband PSRR minimizes phase noise and clock jitter for devices ranging from VCOs, ADCs, DACs, to high-end processors and FPGAs.

## Applications

- High Performance Analog: VCO, ADC, DAC, LVDS

- Communication: CPU, ASIC, FPGA, CPLD, DSP

- Noise Sensitive Imaging: CMOC Sensors, Video ASICs

- Instrumentation, Medical, and Audio

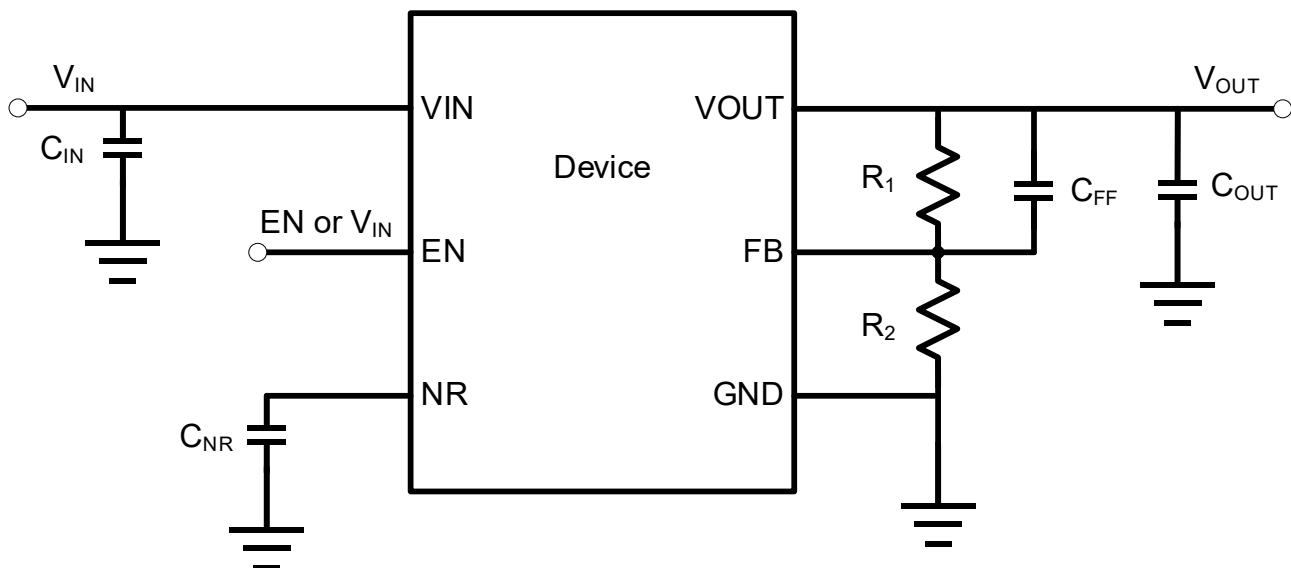

## Typical Application Circuit

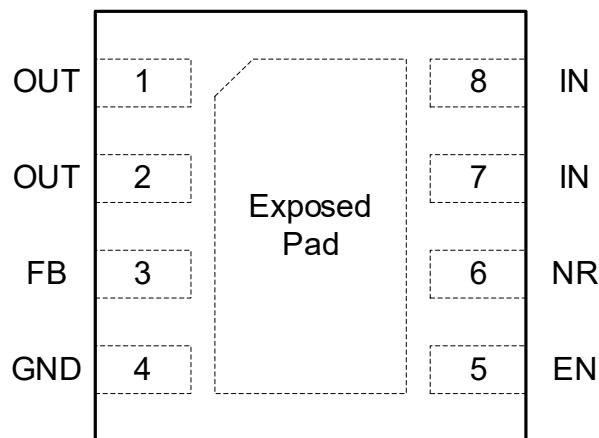

## Pin Configuration and Functions

### 8-Pin SON with Exposed Thermal Pad Top View

## Pin Descriptions

| PIN Number | PIN Name    | I/O | Function                                                                                                                                                                                                 |

|------------|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2       | OUT         | O   | Regulator output voltage pin. A 22µF or larger ceramic capacitor from OUT to ground is required to ensure regulator stability.                                                                           |

| 3          | FB          | I   | Output voltage feedback pin. Connect to an external resistor divider to adjust the output voltage. A 10nF feed-forward capacitor from FB to OUT is recommended to maximize the regulator ac performance. |

| 4          | GND         | -   | Device ground pin.                                                                                                                                                                                       |

| 5          | EN          | I   | Enable pin. Drive EN high to turn on the LDO and drive the EN low to turn off the LDO. The EN pin can be connected to IN for automatic startup                                                           |

| 6          | NR          | O   | Noise reduction pin. A 100nF or larger capacitor from NR to GND is recommended to maximize the performance                                                                                               |

| 7, 8       | IN          | I   | Input voltage pin. A 10µF capacitor from IN to GND is recommended                                                                                                                                        |

| -          | Exposed Pad | -   | Exposed Pad must be connected to a large-area ground plane to get maximum electrical and thermal performance.                                                                                            |

## Package/Ordering Information

| DEVICE        | PACKAGE TYPE   | MARKING | PACKING OPTION      |

|---------------|----------------|---------|---------------------|

| TPS7A8101DRBR | VSON-8-EP(3x3) | SAU     | Tape and Reel, 3000 |

## Electrical Specifications

### Absolute Maximum Ratings

| Parameter                 | Symbol    | Value                  | Unit |

|---------------------------|-----------|------------------------|------|

| IN and EN Pins            | IN, EN    | -0.3 to 7              | V    |

| OUT Pin                   | OUT       | -0.3 to $V_{IN} + 0.3$ | V    |

| NR and FB Pins            | NR, FB    | -0.3 to $V_{IN} + 0.3$ | V    |

| Storage temperature range | $T_{STG}$ | -65 to +150            | °C   |

| Output current            | $I_{OUT}$ | 1                      | A    |

#### Notes:

1. Exposure of the device under conditions beyond the limits specified by Maximum Ratings for extended periods may cause permanent damage to the device and affect product reliability. These conditions represent a stress rating only, and functional operations of the device at these or any other conditions above the operational limits noted in this specification is not implied.

### ESD Ratings

|           |                         | Value                     | Unit |

|-----------|-------------------------|---------------------------|------|

| $V_{ESD}$ | Electrostatic Discharge | HBM (Human Body Model)    | 3000 |

|           |                         | CDM (Charge Device Model) | 1000 |

### Recommended Operation Conditions

Over operating temperature range unless otherwise noted

| Parameter                      | Symbol    | Min | Max | Unit |

|--------------------------------|-----------|-----|-----|------|

| Input Voltage                  | $V_{IN}$  | 2.6 | 6.5 | V    |

| Output Voltage                 | $V_{OUT}$ | 0.8 | 6.0 | V    |

| Output Capacitance             | $C_{OUT}$ | 22  |     | μF   |

| Output Current                 | $I_{OUT}$ | 0   | 1   | A    |

| Operating Junction Temperature | $T_J$     | -40 | 125 | °C   |

### Thermal Information

| Package       | $R_{θJA}$ | $R_{θJC}$ | Unit |

|---------------|-----------|-----------|------|

| SON-8-EP(3x3) | 55        | 21        | °C/W |

## Electrical Characteristics

$V_{IN} = 2.6V$  or  $V_{IN} = V_{OUT} + 0.5V$  (whichever is greater),  $V_{EN} = V_{IN}$ ,  $C_{IN} = 10\mu F$ ,  $C_{OUT} = 22\mu F$ ,  $C_{NR} = 1\mu F$ ,  $C_{FF} = \text{open}$ ,  $T_A = -40$  to  $+125^\circ C$  unless otherwise noted

| Parameter                                        | Symbol                           | Conditions                                                                                                                                | Rating       |       |     | Unit          |

|--------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|-----|---------------|

|                                                  |                                  |                                                                                                                                           | Min          | Typ   | Max |               |

| Input Voltage                                    | $V_{IN}$                         |                                                                                                                                           | 2.6          | -     | 6.5 | V             |

| Reference Voltage                                | $V_{REF}$                        |                                                                                                                                           |              | 0.8   |     | V             |

| UVLO Threshold                                   | $V_{UVLO}$                       | $V_{IN}$ rising                                                                                                                           |              |       | 2.5 | V             |

| UVLO Hysteresis                                  | $\Delta V_{UVLO}$                |                                                                                                                                           |              | 215   |     | mV            |

| Output Voltage Accuracy                          |                                  | $5mA \leq I_{OUT} \leq 2A$                                                                                                                | -2.0         | 0     | 2.0 | %             |

| GND Pin Current                                  | $I_{GND}$                        | $V_{IN} = 6.5V$ , $I_{OUT} = 1mA$                                                                                                         |              | 210   | 0.3 | $\mu A$       |

| Shutdown Current                                 | $I_{SHDN}$                       |                                                                                                                                           |              | 0.2   | 0.9 | $\mu A$       |

| Dropout Voltage                                  | $V_{DO}$                         | $V_{IN} = 3.3V$ , $I_{OUT} = 1A$                                                                                                          |              | 160   |     | mV            |

| Over Current Limit                               | $I_{LIM}$                        | $V_{IN} = 2.6 - 6.5V$                                                                                                                     | 1            |       |     | A             |

| Line Regulation                                  | $\Delta V_{OUT(\Delta V_{IN})}$  | $V_{IN} = 2.6 - 6.5V$                                                                                                                     |              | 0.008 |     | %/V           |

| Load Regulation                                  | $\Delta V_{OUT(\Delta I_{OUT})}$ | $I_{OUT} = 5mA$ to $2A$                                                                                                                   |              | 0.07  |     | %/A           |

| EN pin low-level input voltage (device disabled) | $V_{IL(EN)}$                     |                                                                                                                                           | 0            |       | 0.4 | V             |

| EN pin high-level input voltage (device enabled) | $V_{IH(EN)}$                     |                                                                                                                                           | 1.35         |       | 6.5 | V             |

| EN PIN Leakage Current                           | $I_{EN}$                         | $V_{IN} = 6.5V$ , $0V \leq V_{EN} \leq 6.5V$                                                                                              | -0.2         |       | 0.2 | $\mu A$       |

| FB PIN Leakage Current                           | $I_{FB}$                         | $V_{IN} = 6.5V$ , $V_{FB} = 0.8V$                                                                                                         | -0.2         |       | 0.2 | $\mu A$       |

| Power Supply Rejection Ratio                     | PSRR                             | $V_{IN} = 5V$ , $V_{OUT} = 3.3V$ , $I_{OUT} = 1A$ , $C_{OUT} = 22\mu F$ , $C_{NR} = 1\mu F$ , $C_{FF} = 10nF$                             | $f = 1kHz$   | 75    |     | dB            |

|                                                  |                                  |                                                                                                                                           | $f = 100kHz$ | 52    |     |               |

|                                                  |                                  |                                                                                                                                           | $f = 1MHz$   | 41    |     |               |

| Output Noise Voltage                             | $V_N$                            | $BW = 100Hz$ to $100kHz$ , $V_{IN} = 5V$ , $V_{OUT} = 3.3V$ , $I_{OUT} = 1A$ , $C_{OUT} = 22\mu F$ , $C_{NR} = 1\mu F$ , $C_{FF} = 100nF$ |              | 6.0   |     | $\mu V_{RMS}$ |

| Thermal Shutdown Temperature                     | TSD                              |                                                                                                                                           |              | 160   |     | $^\circ C$    |

**DYW**

**TPS7A8101**

|                                |           |  |  |    |  |             |

|--------------------------------|-----------|--|--|----|--|-------------|

| Thermal Shutdown<br>Hysteresis | $T_{HYS}$ |  |  | 20 |  | $^{\circ}C$ |

|--------------------------------|-----------|--|--|----|--|-------------|

## Typical Characteristics

$V_{IN} = 2.6V$  or  $V_{IN} = V_{OUT} + 0.4V$  (whichever is greater), OUT connected to  $50\Omega$  to GND,  $V_{EN} = V_{IN}$ ,  $C_{IN} = 10\mu F$ ,  $C_{OUT} = 22\mu F$ ,  $C_{NR} = 1\mu F$ ,  $C_{FF} = \text{open}$ ,  $T_A = -40$  to  $+125^\circ C$  unless otherwise noted

$V_{IN} = 4V$ ,  $V_{OUT} = 3.3V$ ,  $I_{OUT} = 1A$ ,  $C_{OUT} = 22\mu F$ ,

$C_{NR} = 1\mu F$ ,  $C_{FF} = \text{open}$

Fig. 1 PSRR

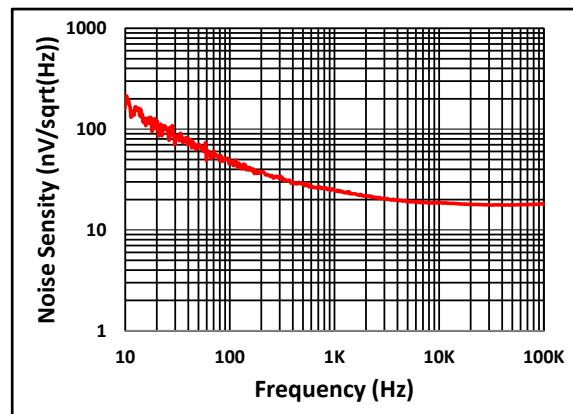

$V_{IN} = 4V$ ,  $V_{OUT} = 3.3V$ ,  $I_{OUT} = 1A$ ,  $C_{OUT} = 22\mu F$ ,

$C_{NR} = 1\mu F$ ,  $C_{FF} = \text{open}$

Fig. 2 Output Noise Density

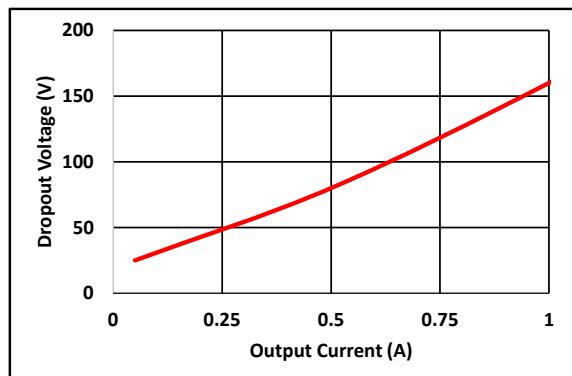

$V_{IN} = 3.3V$ ,  $V_{EN} = 3.3V$

Fig. 3 Dropout Voltage

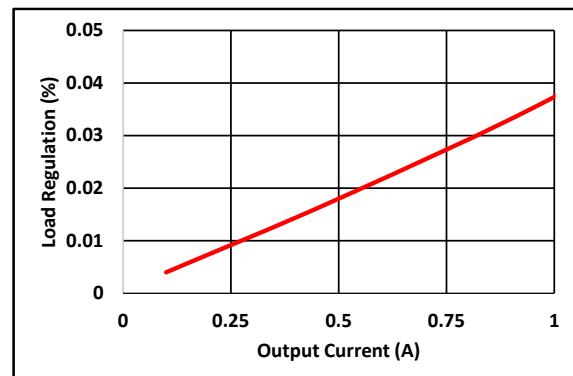

$V_{IN} = 4V$ ,  $V_{OUT} = 3.3V$ ,  $C_{OUT} = 22\mu F$

Fig. 4 Load Regulation

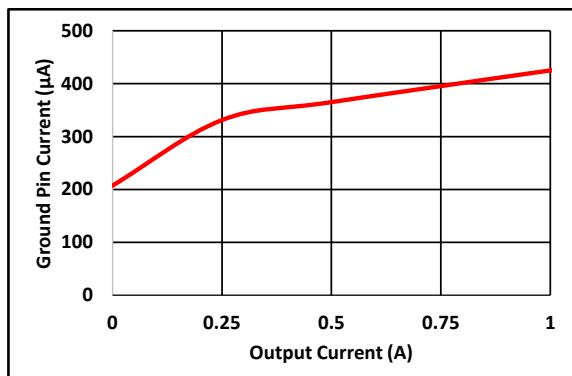

$V_{IN} = 4V$ ,  $V_{OUT} = 3.3V$ ,  $C_{OUT} = 22\mu F$

Fig. 5 Ground Current vs Output Current

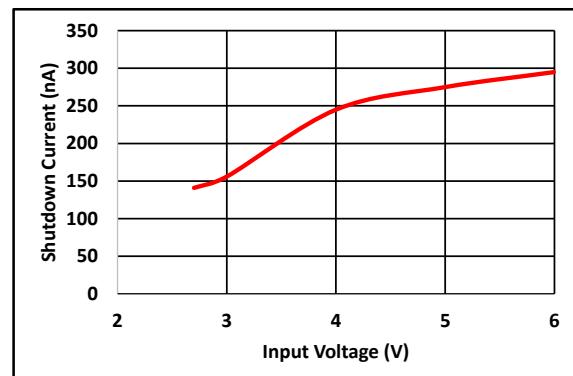

$V_{EN} = 0V$

Fig. 6 Power Down Current vs Input Voltage

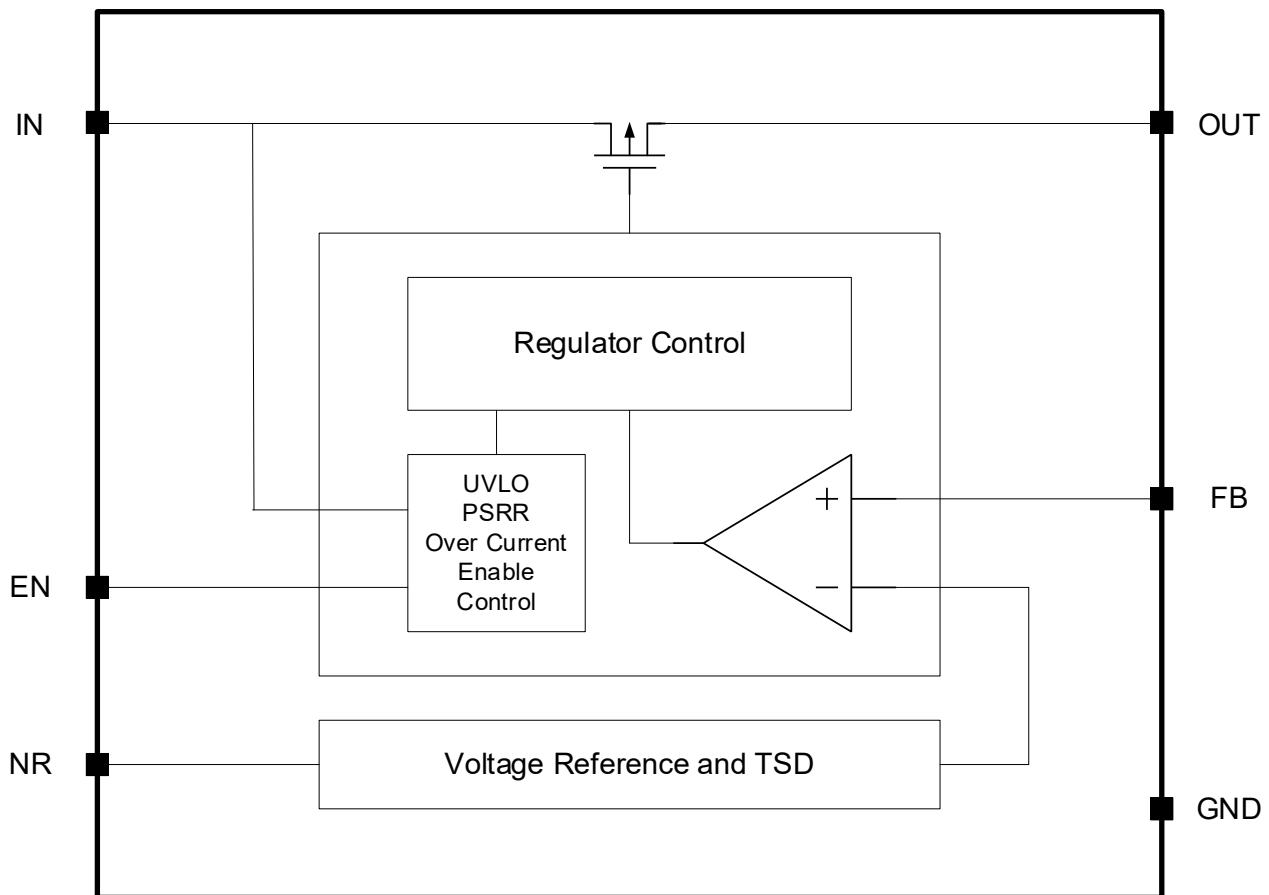

## Functional Description

The device is a low-noise, high PSRR low dropout (LDO) regulator capable of sourcing a 1A load current with 160mV (typical) dropout voltage. The device can operate down to 2.6V input voltage and a 0.8V output voltage. This combination of low-noise, high PSRR, and low dropout voltage makes the device an ideal LDO to power a multitude of load from noise-sensitive communication components in high-speed communications applications to high-end microprocessors or field-programmable gate arrays (FPGAs). The device also features internal protection circuitry such as UVLO (under-voltage lockout) and current limit.

## Functional Block Diagram

## Feature Description

### ***Enable***

The enable pin for the device is active high. The device is enabled when the enable pin voltage is greater than  $V_{IH(EN)}$  and disabled with the enable pin voltage less than  $V_{IL(EN)}$ . If independent control of chip enable is not needed, then connect the enable pin to the input. The device has an internal pulldown MOSFET that connects a discharge resistor from VOUT to ground when the device is disabled to actively discharge the output voltage.

### ***Dropout voltage***

Dropout voltage ( $V_{DO}$ ) is defined as the  $VIN - VOUT$  voltage at the rated current of 1A, where the pass transistor is fully on and in the linear region of operation.  $V_{DO}$  indirectly specifies a minimum input voltage above the nominal programmed output voltage at which the output voltage is expected to remain in regulation. If the input falls below the nominal output regulation, then the output follows the input.

### ***Output Voltage Accuracy***

Output voltage accuracy specifies minimum and maximum output voltage error, relative to the expected nominal output voltage stated as a percent. The device features an output voltage accuracy of 2% that includes the errors introduced by the internal reference, load regulation, and line regulation variance across the full range of rated load and the line operating conditions over temperature.

### ***Undervoltage Lockout (UVLO)***

The device uses an undervoltage lockout circuit to keep the output shut off until the internal circuitry is operating properly.

### ***Internal Current Limit***

The internal current-limit circuit is used to protect the LDO against transient high-load faults or shorting events. For reliable operation, the device should not be operated in a current limit state.

### ***Thermal Protection***

The device contains a thermal shutdown protection circuit to turn off the output current when excessive heat is dissipated in the LDO.

## Application Information

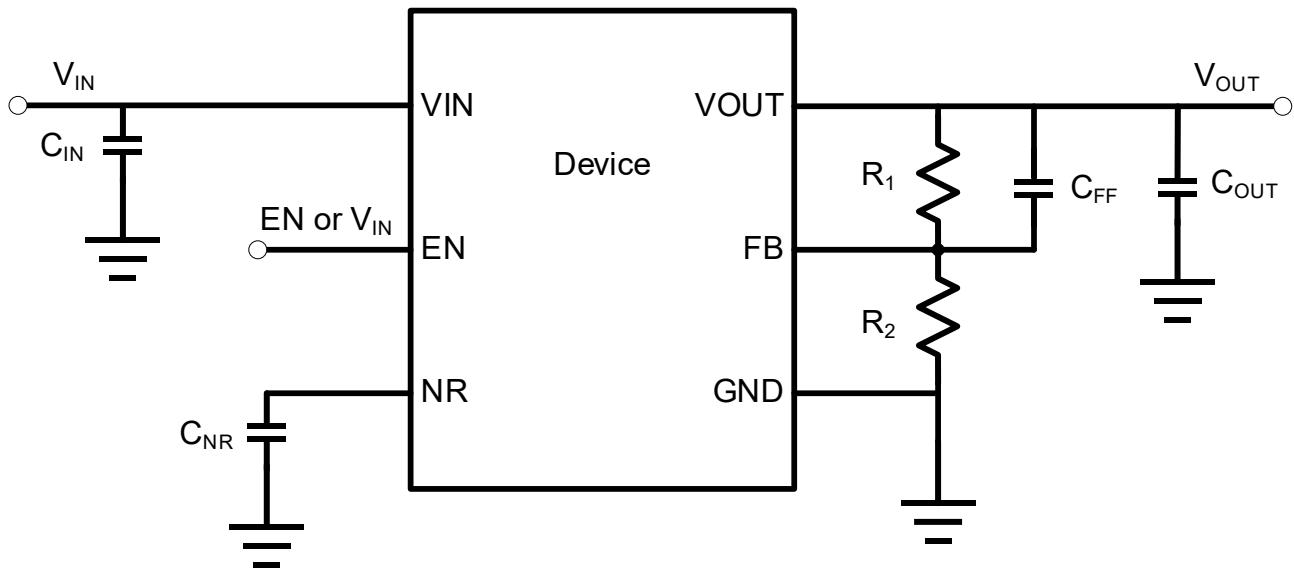

## Typical Application

The diagram above shows a typical application circuit.

## Input Capacitor and Output Capacitor

The device is designed and characterized for operation with ceramic capacitors of  $10\mu F$  or greater at the input and  $22\mu F$  or greater at the output. Locate the input and output capacitors as near as practical to the input and output pins to minimize the trace inductance from the capacitor to the device.

Feed-Forward Capacitor ( $C_{FF}$ )

Although a feed-forward capacitor ( $C_{FF}$ ), from the FB pin to the OUT pin is not required to achieve stability, a  $10nF$ , feed-forward capacitor improves noise and PSRR performance.

## Adjustable Output

The output voltage can be adjusted from  $0.8V$  to  $6V$  by using a resistor network as shown in the typical application diagram. The table below lists the resistor combination required to achieve a few of the most common rails using commercially available,  $0.1\%-tolerance$  resistors.

| V <sub>OUT(TARGET)</sub> (V) | FEEDBACK RESISTOR VALUES     |                              | CALCULATED OUTPUT VOLTAGE (V) |

|------------------------------|------------------------------|------------------------------|-------------------------------|

|                              | R <sub>1</sub> (k $\Omega$ ) | R <sub>2</sub> (k $\Omega$ ) |                               |

| 0.8                          | Short                        | Open                         | 0.800                         |

|      |      |      |       |

|------|------|------|-------|

| 1.00 | 2.55 | 10.2 | 1.000 |

| 1.20 | 5.9  | 11.8 | 1,200 |

| 1.50 | 9.31 | 10.7 | 1.496 |

| 1.80 | 1.87 | 1.5  | 1.797 |

| 2.50 | 2.43 | 1.15 | 2.490 |

| 3.00 | 3.16 | 1.15 | 2.998 |

| 3.30 | 3.57 | 1.15 | 3.283 |

| 5.00 | 10.5 | 2    | 5.00  |

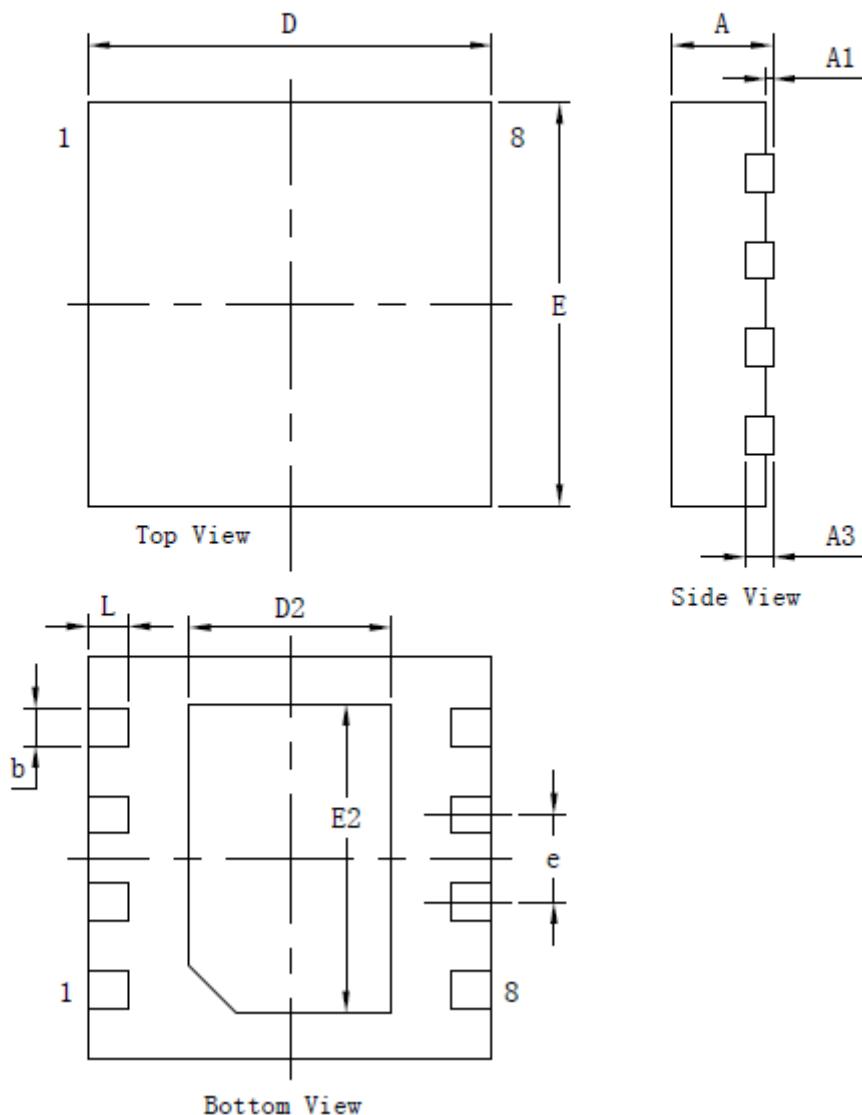

## Package Outline Dimensions

SON-8-EP(3x3)

| 尺寸<br>标注 | 最小 (mm) | 标准 (mm)   | 最大 (mm) | 尺寸<br>标注 | 最小 (mm) | 标准 (mm)  | 最大 (mm) |

|----------|---------|-----------|---------|----------|---------|----------|---------|

| A        | 0.70    | 0.75      | 0.80    | E        | 2.90    | 3.00     | 3.10    |

| A1       | -       | -         | 0.05    | D2       | 1.40    | 1.50     | 1.60    |

| A3       |         | 0.203 REF |         | E2       | 2.20    | 2.30     | 2.40    |

| b        | 0.23    | 0.28      | 0.33    | e        |         | 0.65 TYP |         |

| D        | 2.90    | 3.00      | 3.10    | L        | 0.25    | 0.30     | 0.35    |