## Product Overview

The NCA9534B is a 16-pin device that provides 8 bits of General Purpose parallel Input/Output (GPIO) expansion for the two-line bidirectional I2C bus applications. The device can operate with a power supply voltage (VDD) range from 1.65 V to 5.5 V. It provides a simple solution when additional I/Os are needed for ACPI power switches, sensors, push buttons, LEDs, fans, etc.

The NCA9534B consists of an 8-bit Configuration (Input or Output selection); Input, Output and Polarity Inversion (active HIGH or active LOW operation) registers. The system master can enable the I/Os as either inputs or outputs by writing to the I/O configuration bits. The data for each Input or Output is kept in the corresponding Input or Output register. The polarity of the read register can be inverted with the Polarity Inversion register. All registers can be read by the system master.

The NCA9534B open-drain interrupt output is activated when any input state differs from its corresponding input port register state and is used to indicate to the system master that an input state has changed. The power-on reset sets the registers to their default values and initializes the device state machine.

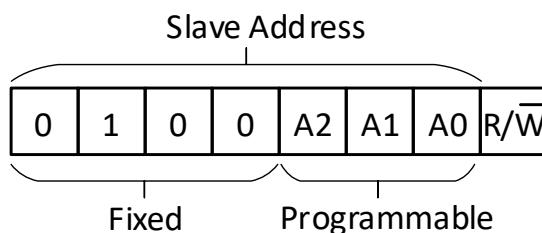

Three hardware pins (A0, A1, A2) vary the fixed I2C-bus address and allow up to eight devices to share the same I2C-bus.

## Key Features

- I2C to Parallel Port Expander

- Operating power supply voltage range of 1.65V to 5.5 V

- Low standby current

- Open-drain active-low interrupt output

- 5.5V tolerant, 8 I/O ports which default to input mode

- Compatible with most microcontrollers

- Up to 400 kHz clock frequency

- Noise filter on SCL/SDA inputs

- Polarity Inversion register

- Internal power-on reset

- No glitch on power-up

- Address by three hardware address pins for use of up to eight devices

- Latched outputs with high-current drive capability for directly driving LEDs

- Latch-up performance exceeds 100 mA per JESD 78, class II

- ESD protection exceeds JESD 22: 2000 V HBM, 200 V MM, and 1000 V CDM

## Applications

- GPIO expansion for I2C-bus applications

- Servers, personal computers, personal electronics

- Routers (Telecom Switching Equipment)

- Products with GPIO-Limited processors

## Device Information

| Part Number    | Package | Body Size      |

|----------------|---------|----------------|

| NCA9534B-DTSPR | TSSOP16 | 5.00mm*4.40mm  |

| NCA9534B-DSWR  | SOW16   | 10.30mm*7.50mm |

## Pinout

Figure 1. NCA9534B Pinout

## INDEX

|                                                                  |           |

|------------------------------------------------------------------|-----------|

| <b>1. PIN CONFIGURATION AND FUNCTIONS .....</b>                  | <b>3</b>  |

| <b>2. ABSOLUTE MAXIMUM RATINGS .....</b>                         | <b>4</b>  |

| <b>3. ESD RATINGS (ELECTROSTATIC DISCHARGE PROTECTION) .....</b> | <b>4</b>  |

| <b>4. RECOMMENDED OPERATING CONDITIONS .....</b>                 | <b>4</b>  |

| <b>5. THERMAL CHARACTERISTICS .....</b>                          | <b>5</b>  |

| <b>6. SPECIFICATIONS .....</b>                                   | <b>6</b>  |

| <b>6.1. ELECTRICAL CHARACTERISTICS .....</b>                     | <b>6</b>  |

| <b>6.2. DYNAMIC CHARACTERISTICS .....</b>                        | <b>9</b>  |

| <b>6.3. PARAMETER MEASUREMENT INFORMATION .....</b>              | <b>10</b> |

| <b>7. DETAILED DESCRIPTION .....</b>                             | <b>11</b> |

| <b>7.1. FUNCTIONAL BLOCK DIAGRAM .....</b>                       | <b>11</b> |

| <b>7.2. FEATURE DESCRIPTION .....</b>                            | <b>12</b> |

| <b>7.2.1. I/O port .....</b>                                     | <b>12</b> |

| <b>7.2.2. Interrupt (INT<sub>1</sub>) Output .....</b>           | <b>12</b> |

| <b>7.3. DEVICE FUNCTIONAL MODES .....</b>                        | <b>13</b> |

| <b>7.3.1. Power-On Reset .....</b>                               | <b>13</b> |

| <b>7.4. PROGRAMMING .....</b>                                    | <b>13</b> |

| <b>7.4.1. I<sub>2</sub>C Interface .....</b>                     | <b>13</b> |

| <b>7.4.2. Start and Stop Conditions .....</b>                    | <b>13</b> |

| <b>7.4.3. Bit Transfer .....</b>                                 | <b>14</b> |

| <b>7.4.4. System Configuration .....</b>                         | <b>14</b> |

| <b>7.4.5. Acknowledge .....</b>                                  | <b>15</b> |

| <b>7.5. REGISTER MAPS .....</b>                                  | <b>15</b> |

| <b>7.5.1. Device Address .....</b>                               | <b>15</b> |

| <b>7.5.2. Control Register and Command Byte .....</b>            | <b>16</b> |

| <b>7.5.3. Registers 0: Input port register .....</b>             | <b>16</b> |

| <b>7.5.4. Registers 1: Output port register .....</b>            | <b>17</b> |

| <b>7.5.5. Registers 2: Polarity inversion register .....</b>     | <b>17</b> |

| <b>7.5.6. Registers 3: Configuration register .....</b>          | <b>17</b> |

| <b>7.6. BUS TRANSACTIONS .....</b>                               | <b>17</b> |

| <b>7.6.1. Writing to the Port Registers .....</b>                | <b>17</b> |

| <b>7.6.2. Reading the Port Registers .....</b>                   | <b>18</b> |

| <b>8. APPLICATION DESIGN-IN INFORMATION .....</b>                | <b>20</b> |

| <b>8.1. APPLICATION INFORMATION .....</b>                        | <b>20</b> |

| <b>8.2. TYPICAL APPLICATION .....</b>                            | <b>20</b> |

| <b>9. ORDER INFORMATION .....</b>                                | <b>21</b> |

| <b>10. DOCUMENTATION SUPPORT .....</b>                           | <b>21</b> |

| <b>11. PACKAGE INFORMATION .....</b>                             | <b>22</b> |

| <b>12. TAPE AND REEL INFORMATION .....</b>                       | <b>24</b> |

| <b>13. REVISION HISTORY .....</b>                                | <b>25</b> |

## 1. Pin Configuration and Functions

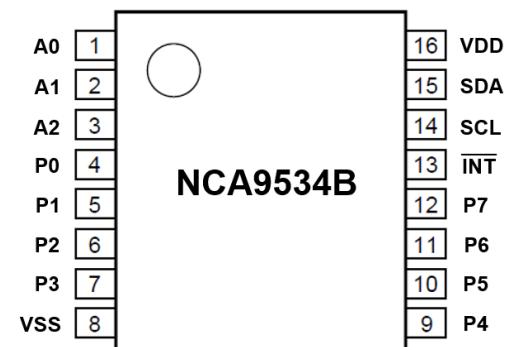

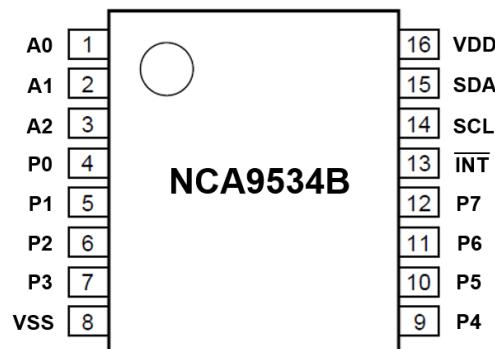

Figure 1-1. NCA9534B Package

Table 1-1. NCA9534B Pin Configuration and Description

| SYMBOL | PIN NO. | FUNCTION                                                               |

|--------|---------|------------------------------------------------------------------------|

| A0     | 1       | Address input 0. Connect directly to VDD or ground                     |

| A1     | 2       | Address input 1. Connect directly to VDD or ground                     |

| A2     | 3       | Address input 2. Connect directly to VDD or ground                     |

| P0     | 4       | Input/output port. At power-on, the port is configured as an input     |

| P1     | 5       |                                                                        |

| P2     | 6       |                                                                        |

| P3     | 7       |                                                                        |

| VSS    | 8       | Ground                                                                 |

| P4     | 9       | Input/output port. At power-on, the port is configured as an input     |

| P5     | 10      |                                                                        |

| P6     | 11      |                                                                        |

| P7     | 12      |                                                                        |

| INT\   | 13      | Interrupt open-drain output. Connect to VDD through a pull-up resistor |

| SCL    | 14      | Serial clock bus. Connect to VDD through a pull-up resistor            |

| SDA    | 15      | Serial data bus. Connect to VDD through a pull-up resistor             |

| VDD    | 16      | Supply voltage                                                         |

## 2. Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>[1]</sup>.

| Parameters                     | Symbol           | Min  | Max | Unit | Comments |

|--------------------------------|------------------|------|-----|------|----------|

| Supply voltage                 | V <sub>DD</sub>  | -0.5 | 6.0 | V    |          |

| Voltage on an input/output pin | V <sub>I/O</sub> | -0.5 | 6.0 | V    |          |

| Output current                 | I <sub>O</sub>   | -    | ±50 | mA   |          |

| Input current                  | I <sub>I</sub>   | -    | ±20 | mA   |          |

| Supply current                 | I <sub>DD</sub>  | -    | 160 | mA   |          |

| Ground supply current          | I <sub>SS</sub>  | -    | 200 | mA   |          |

| Total power dissipation        | P <sub>tot</sub> | -    | 200 | mW   |          |

| Junction temperature           | T <sub>J</sub>   | -    | 135 | °C   |          |

| Storage temperature            | T <sub>stg</sub> | -65  | 150 | °C   |          |

<sup>[1]</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to Absolute Maximum Rating condition for extended periods may affect device reliability.

## 3. ESD Ratings (Electrostatic Discharge Protection)

| Parameters | Conditions           | Value    | Unit | Comments |                                      |

|------------|----------------------|----------|------|----------|--------------------------------------|

| HBM        | Human Body Model     | All pins | ±6   | kV       | According to ANSI/ESDA/ JEDEC JS-001 |

| CDM        | Charged Device Model | All pins | ±2   | kV       | According to ANSI/ESDA/ JEDEC JS-002 |

| MM         | Machine Model        | All pins | ±300 | V        | According to JESD22-A115C            |

## 4. Recommended Operating Conditions

| Parameters                          | Symbol          | Min                 | Max                 | Unit |

|-------------------------------------|-----------------|---------------------|---------------------|------|

| Supply voltage                      | V <sub>DD</sub> | 1.65                | 5.5                 | V    |

| High-level input voltage            | V <sub>IH</sub> | 0.7*V <sub>DD</sub> | 5.5                 | V    |

| Low-level input voltage             | V <sub>IL</sub> | -0.5                | 0.3*V <sub>DD</sub> | V    |

| High-level output current (IO port) | I <sub>OH</sub> |                     | -10                 | mA   |

| Low-level output current (IO port)  | I <sub>OL</sub> |                     | 10                  | mA   |

|                                      |          |     |     |    |

|--------------------------------------|----------|-----|-----|----|

| Low-level output current (INT\, SDA) | $I_{OL}$ |     | 3.5 | mA |

| Operating free-air temperature       | $T_A$    | -40 | 125 | °C |

## 5. Thermal Characteristics

| Parameters                                | Symbol                    | TSSOP16 | SOW16 | Unit |

|-------------------------------------------|---------------------------|---------|-------|------|

| IC Junction-to-Air Thermal Resistance     | $\theta_{JA}$             | 122     | 92.2  | °C/W |

| Junction-to-case (top) thermal resistance | $\theta_{JC(\text{top})}$ | 56.4    | 53.8  | °C/W |

| Junction-to-board thermal resistance      | $\theta_{JB}$             | 67.1    | 56.9  | °C/W |

## 6. Specifications

### 6.1. Electrical Characteristics

$V_{DD}$ = 1.65V to 5.5V;  $T_{amb}$  = -40°C to 125°C;  $V_i$  is the voltage on I/O port; unless otherwise noted.

| Parameters                           | Symbol     | Min  | Typ  | Max | Unit          | Conditions                                                                                                 |

|--------------------------------------|------------|------|------|-----|---------------|------------------------------------------------------------------------------------------------------------|

| Input diode clamp voltage            | $V_{IK}$   | -1.2 | -    | -   | V             | $I_i = -18\text{mA}$                                                                                       |

| <b>Supplies</b>                      |            |      |      |     |               |                                                                                                            |

| Supply voltage Range                 | $V_{DD}$   | 1.65 | -    | 5.5 | V             |                                                                                                            |

| Supply current                       | $I_{DD}$   | -    | 26   | 40  | $\mu\text{A}$ | Operating mode; $V_{DD} = 5.5\text{ V}$ ; I/O=input; $V_i = V_{DD}$ ; no load; $f_{SCL} = 400\text{ kHz}$  |

|                                      |            | -    | 12   | 30  | $\mu\text{A}$ | Operating mode; $V_{DD} = 3.6\text{ V}$ ; I/O=input; $V_i = V_{DD}$ ; no load; $f_{SCL} = 400\text{ kHz}$  |

|                                      |            | -    | 7.5  | 19  | $\mu\text{A}$ | Operating mode; $V_{DD} = 2.7\text{ V}$ ; I/O=input; $V_i = V_{DD}$ ; no load; $f_{SCL} = 400\text{ kHz}$  |

|                                      |            | -    | 4.5  | 11  | $\mu\text{A}$ | Operating mode; $V_{DD} = 1.95\text{ V}$ ; I/O=input; $V_i = V_{DD}$ ; no load; $f_{SCL} = 400\text{ kHz}$ |

| Standby current                      | $I_{stb}$  | -    | 0.30 | 8.7 | $\mu\text{A}$ | Standby mode; $V_{DD} = 5.5\text{ V}$ ; I/O=input; $V_i = V_{DD}$ ; no load; $f_{SCL} = 0\text{ kHz}$      |

|                                      |            | -    | 0.15 | 4   | $\mu\text{A}$ | Standby mode; $V_{DD} = 3.6\text{ V}$ ; I/O=input; $V_i = V_{DD}$ ; no load; $f_{SCL} = 0\text{ kHz}$      |

|                                      |            | -    | 0.12 | 3   | $\mu\text{A}$ | Standby mode; $V_{DD} = 2.7\text{ V}$ ; I/O=input; $V_i = V_{DD}$ ; no load; $f_{SCL} = 0\text{ kHz}$      |

|                                      |            | -    | 0.09 | 2.2 | $\mu\text{A}$ | Standby mode; $V_{DD} = 1.95\text{ V}$ ; I/O=input; $V_i = V_{DD}$ ; no load; $f_{SCL} = 0\text{ kHz}$     |

|                                      |            | -    | 0.21 | 3.9 | $\mu\text{A}$ | Standby mode; $V_{DD} = 5.5\text{ V}$ ; I/O=input; $V_i = V_{SS}$ ; no load; $f_{SCL} = 0\text{ kHz}$      |

|                                      |            | -    | 0.14 | 2.2 | $\mu\text{A}$ | Standby mode; $V_{DD} = 3.6\text{ V}$ ; I/O=input; $V_i = V_{SS}$ ; no load; $f_{SCL} = 0\text{ kHz}$      |

|                                      |            | -    | 0.10 | 1.8 | $\mu\text{A}$ | Standby mode; $V_{DD} = 2.7\text{ V}$ ; I/O=input; $V_i = V_{SS}$ ; no load; $f_{SCL} = 0\text{ kHz}$      |

|                                      |            | -    | 0.08 | 1.5 | $\mu\text{A}$ | Standby mode; $V_{DD} = 1.95\text{ V}$ ; I/O=input; $V_i = V_{SS}$ ; no load; $f_{SCL} = 0\text{ kHz}$     |

| Power On Reset Rising <sup>[1]</sup> | $V_{PORR}$ | 0.75 | 1.17 | 1.5 | V             | no load; $V_i = V_{DD}$ or $V_{SS}$                                                                        |

|                                               |            |              |      |              |         |                                                              |

|-----------------------------------------------|------------|--------------|------|--------------|---------|--------------------------------------------------------------|

| Power On Reset Falling <sup>[1]</sup>         | $V_{PORF}$ | 0.75         | 1.06 | 1.5          | V       | no load; $V_I = V_{DD}$ or $V_{SS}$                          |

| <b><i>Input SCL; Input and Output SDA</i></b> |            |              |      |              |         |                                                              |

| LOW-level input voltage                       | $V_{IL}$   | -0.5         | -    | $0.3*V_{DD}$ | V       |                                                              |

| HIGH-level input voltage                      | $V_{IH}$   | $0.7*V_{DD}$ | -    | 5.5          | V       |                                                              |

| LOW-level output current                      | $I_{OL}$   | 3            | -    | -            | mA      | $V_{DD} = 1.65$ V to 5.5 V; $V_{OL} = 0.4$ V                 |

| Input leakage current                         | $I_L$      | -1           | -    | 1            | $\mu A$ | $V_{DD} = 1.65$ V to 5.5 V; $V_I = V_{DD}$ or $V_{SS}$       |

| Input capacitance                             | $C_i$      | -            | 6    | 10           | pF      | $V_I = V_{SS}$                                               |

| <b><i>I/Os</i></b>                            |            |              |      |              |         |                                                              |

| LOW-level input voltage                       | $V_{IL}$   | -0.5         | -    | $0.3*V_{DD}$ | V       |                                                              |

| HIGH-level input voltage                      | $V_{IH}$   | $0.7*V_{DD}$ | -    | 5.5          | V       |                                                              |

| LOW-level output current                      | $I_{OL}$   | 8            | -    | -            | mA      | $V_{DD} = 1.65$ V to 5.5 V; $V_{OL} = 0.3$ V <sup>[2]</sup>  |

|                                               |            | 10           | -    | -            | mA      | $V_{DD} = 1.65$ V to 5.5 V; $V_{OL} = 0.35$ V <sup>[2]</sup> |

| HIGH-level output voltage                     | $V_{OH}$   | 1.2          | -    | -            | V       | $I_{OH} = -8$ mA; $V_{DD} = 1.65$ V <sup>[3]</sup>           |

|                                               |            | 1.0          | -    | -            | V       | $I_{OH} = -10$ mA; $V_{DD} = 1.65$ V <sup>[3]</sup>          |

|                                               |            | 1.8          | -    | -            | V       | $I_{OH} = -8$ mA; $V_{DD} = 2.3$ V <sup>[3]</sup>            |

|                                               |            | 1.7          | -    | -            | V       | $I_{OH} = -10$ mA; $V_{DD} = 2.3$ V <sup>[3]</sup>           |

|                                               |            | 2.6          | -    | -            | V       | $I_{OH} = -8$ mA; $V_{DD} = 3.0$ V <sup>[3]</sup>            |

|                                               |            | 2.5          | -    | -            | V       | $I_{OH} = -10$ mA; $V_{DD} = 3.0$ V <sup>[3]</sup>           |

|                                               |            | 4.1          | -    | -            | V       | $I_{OH} = -8$ mA; $V_{DD} = 4.75$ V <sup>[3]</sup>           |

|                                               |            | 4.0          | -    | -            | V       | $I_{OH} = -10$ mA; $V_{DD} = 4.75$ V <sup>[3]</sup>          |

| HIGH-level input leakage current              | $I_{LIH}$  | -            | -    | 1            | $\mu A$ | $V_{DD} = 5.5$ V; $V_I = V_{DD}$                             |

| LOW-level input leakage current               | $I_{LIL}$  | -            | -    | -1           | $\mu A$ | $V_{DD} = 5.5$ V; $V_I = V_{SS}$                             |

| Input capacitance                             | $C_i$      | -            | 3.7  | 5            | pF      |                                                              |

|                                        |          |              |     |              |               |                                                                              |

|----------------------------------------|----------|--------------|-----|--------------|---------------|------------------------------------------------------------------------------|

| Output capacitance                     | $C_o$    | -            | 3.7 | 5            | pF            |                                                                              |

| <b><i>Interrupt INT</i></b>            |          |              |     |              |               |                                                                              |

| LOW-level output current               | $I_{OL}$ | 3            | -   | -            | mA            | $V_{DD} = 1.65 \text{ V to } 5.5 \text{ V}; V_{OL} = 0.4\text{V}$            |

| <b><i>Select Inputs A0, A1, A2</i></b> |          |              |     |              |               |                                                                              |

| LOW-level input voltage                | $V_{IL}$ | -0.5         | -   | $0.3*V_{DD}$ | V             |                                                                              |

| HIGH-level input voltage               | $V_{IH}$ | $0.7*V_{DD}$ | -   | 5.5          | V             |                                                                              |

| Input leakage current                  | $I_{IU}$ | -1           | -   | 1            | $\mu\text{A}$ | $V_{DD} = 1.65 \text{ V to } 5.5 \text{ V}; V_I = V_{DD} \text{ or } V_{SS}$ |

[1]  $V_{DD}$  must be lowered to 0.2V for at least 50 $\mu\text{s}$  in order to reset part.

[2] Each I/O must be externally limited to a maximum of 25 mA and the device must be limited to a maximum current of 100 mA.

[3] The total current sourced by all I/Os must be limited to 85 mA.

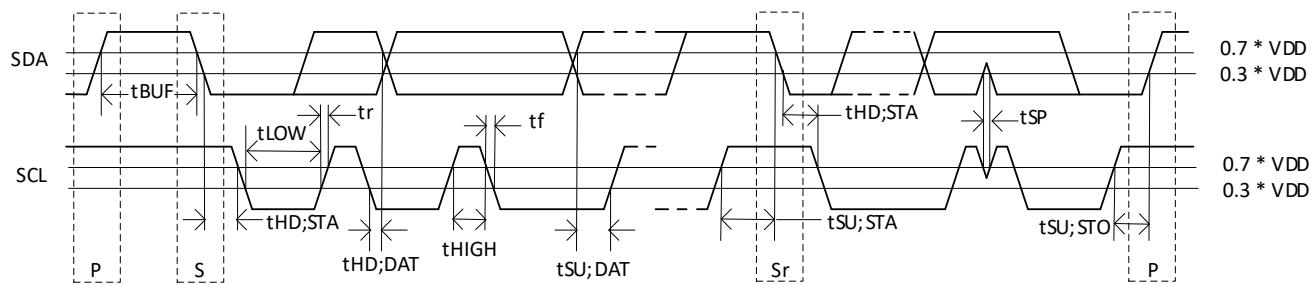

## 6.2. Dynamic Characteristics

VDD = 1.65V to 5.5V; Tamb = -40°C to +125°C; unless otherwise noted.

| Parameters                                                        | Symbol                  | Standard-mode I2C-bus |      | Fast-mode I2C-bus   |     | Unit |

|-------------------------------------------------------------------|-------------------------|-----------------------|------|---------------------|-----|------|

|                                                                   |                         | Min                   | Max  | Min                 | Max |      |

| SCL clock frequency                                               | $f_{SCL}$               | 0                     | 100  | 0                   | 400 | kHz  |

| Bus free time between a STOP and START condition                  | $t_{BUF}$               | 4.7                   | -    | 1.3                 | -   | μs   |

| Hold time (repeated) START condition                              | $t_{HD;STA}$            | 4.0                   | -    | 0.6                 | -   | μs   |

| Set-up time for a repeated START condition                        | $t_{SU;STA}$            | 4.7                   | -    | 0.6                 | -   | μs   |

| Set-up time for STOP condition                                    | $t_{SU;STO}$            | 4.0                   | -    | 0.6                 | -   | μs   |

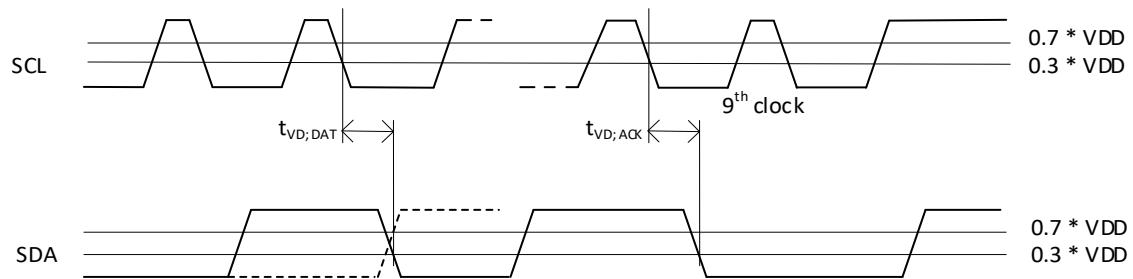

| Data valid acknowledge time                                       | $t_{VD;ACK}^{[1]}$      | 0.3                   | 3.45 | 0.1                 | 0.9 | μs   |

| Data hold time                                                    | $t_{HD;DAT}$            | 0                     | -    | 0                   | -   | ns   |

| Data valid time                                                   | $t_{VD;DAT}^{[2]}$      | 300                   | -    | 50                  | -   | ns   |

| Data set-up time                                                  | $t_{SU;DAT}$            | 250                   | -    | 100                 | -   | ns   |

| LOW period of the SCL clock                                       | $t_{LOW}$               | 4.7                   | -    | 1.3                 | -   | μs   |

| HIGH period of the SCL clock                                      | $t_{HIGH}$              | 4.0                   | -    | 0.6                 | -   | μs   |

| Fall time of both SDA and SCL signals                             | $t_f$                   | -                     | 300  | $20 + 0.1C_b^{[3]}$ | 300 | ns   |

| Rise time of both SDA and SCL signals                             | $t_r$                   | -                     | 1000 | $20 + 0.1C_b^{[3]}$ | 300 | ns   |

| Pulse width of spikes that must be suppressed by the input filter | $t_{SP}$                | -                     | 50   | -                   | 50  | ns   |

| Data output valid time                                            | $t_{V(Q)}$              | -                     | 200  | -                   | 200 | ns   |

| Data input set-up time                                            | $t_{su(D)}$             | 150                   | -    | 150                 | -   | ns   |

| Data input hold time                                              | $t_{h(D)}$              | 1                     | -    | 1                   | -   | μs   |

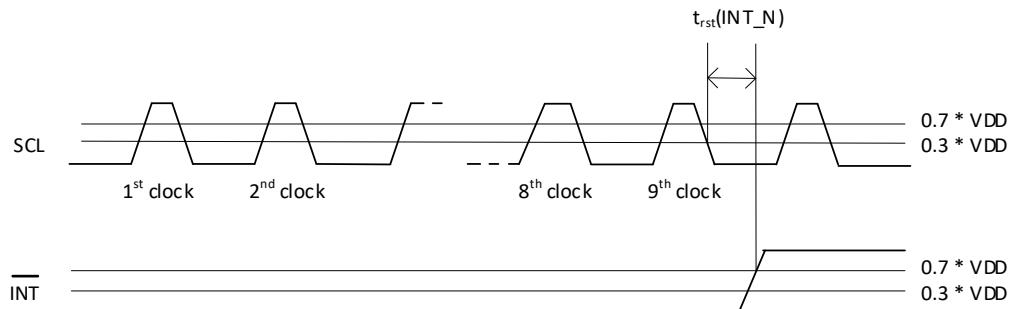

| Valid time on pin INT\                                            | $t_{V(INT\_N)}^{[4]}$   | -                     | 4    | -                   | 4   | μs   |

| Reset time on pin INT\                                            | $t_{rst(INT\_N)}^{[5]}$ | -                     | 4    | -                   | 4   | μs   |

1.  $t_{VD;ACK}$  = time for acknowledgement signal from SCL LOW to SDA (out) LOW, see Figure 6-2.

2.  $t_{VD;DAT}$  = minimum time for SDA data out to be valid following SCL LOW, see Figure 6-2.

3.  $C_b$  = total capacitance of one bus line in pF.

4.  $t_{V(INT\_N)}$  is measured from 0.5\*VDD input to 0.3\*VDD on INT\.

5.  $t_{rst(INT\_N)}$  is measured from 0.3\*VDD on SCL to 0.7\*VDD on INT\.

### 6.3. Parameter Measurement Information

Figure 6-1. Definition of timing on I<sup>2</sup>C-busFigure 6-2. Parameter Measurement Waveform:  $t_{VD;DAT}$  &  $t_{VD;ACK}$ Figure 6-3. Parameter Measurement Waveform:  $t_{rst(INT\_N)}$

## 7. Detailed Description

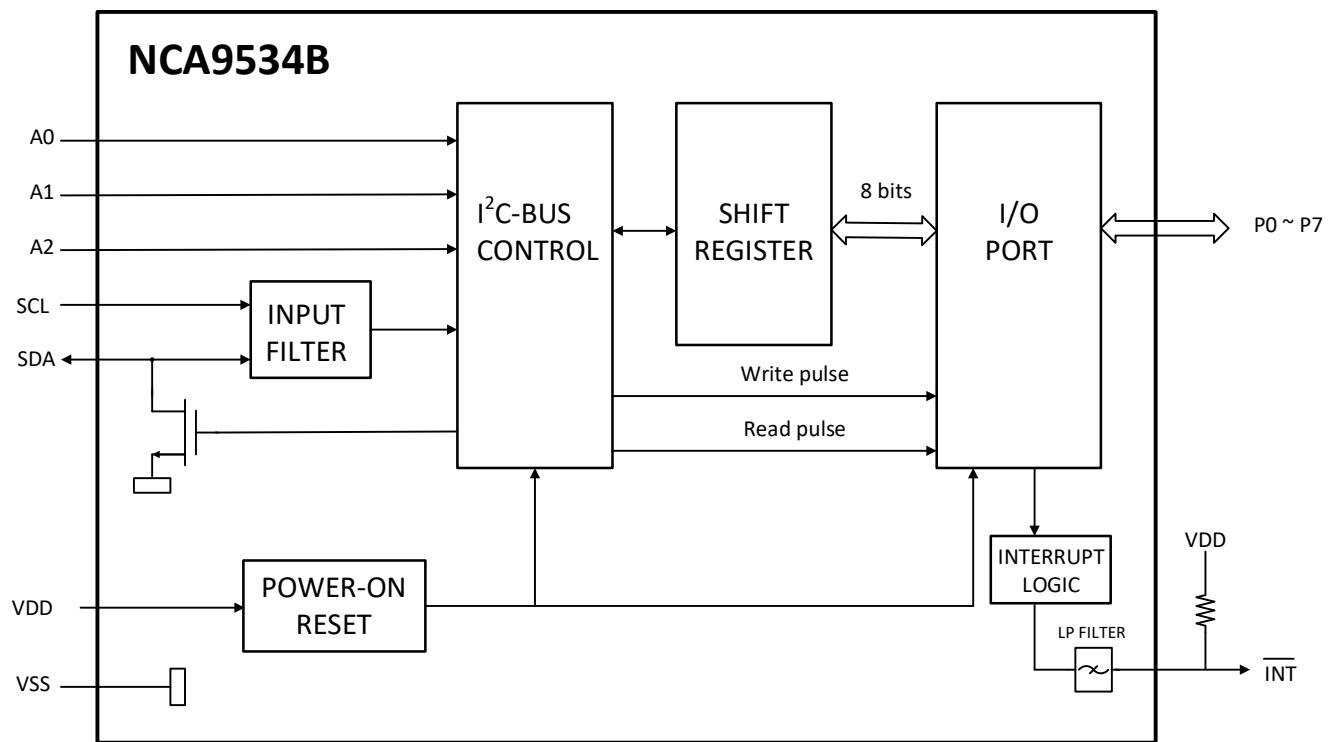

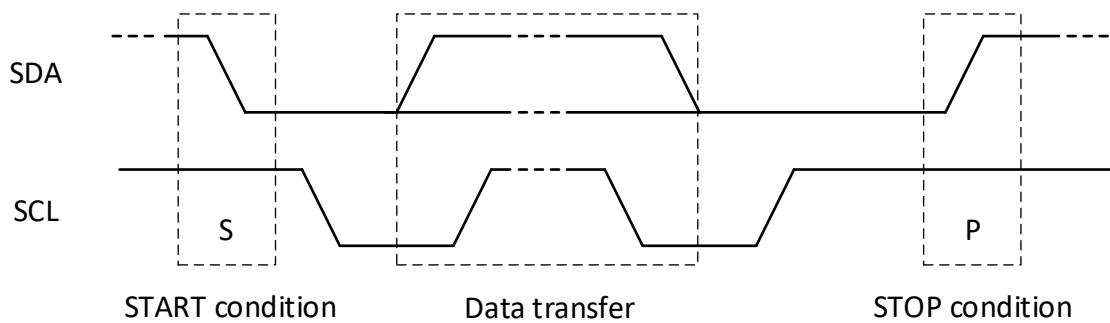

### 7.1. Functional Block Diagram

Figure 7-1. Block Diagram of NCA9534B

Figure 7-2. Simplified schematic of I/Os

## 7.2. Feature description

### 7.2.1. I/O port

When an I/O is configured as an input, FETs Q1 and Q2 are off, creating a high-impedance input. The input voltage may be raised above  $V_{DD}$  to a maximum of 5.5 V.

If the I/O is configured as an output, then either Q1 or Q2 is on, depending on the state of the Output Port register. Care should be exercised if an external voltage is applied to an I/O configured as an output because of the low-impedance path that exists between the pin and either  $V_{DD}$  or  $V_{SS}$ .

### 7.2.2. Interrupt (INT\ ) Output

An interrupt is activated at any rising or falling edge of the port inputs changing state in the input mode. After time,  $t_{V(INT\_N)}$ , the signal  $INT\$  is valid. The interrupt is deactivated when data on the port is changed to the original setting or data is read from the port that generated the interrupt. Resetting occurs in the read mode at the acknowledge (ACK) bit after the rising edge of the SCL signal. Each change of the I/Os after resetting is detected and is transmitted as  $INT\$ .

Reading from or writing to another device does not affect the interrupt circuit, and a pin configured as an output cannot cause an interrupt. Changing an I/O from an output to an input may cause a false interrupt to occur if the state of the pin does not match the contents of the Input Port register.

INT\ has an open-drain structure and requires a pull-up resistor to VDD.

### 7.3. Device functional modes

#### 7.3.1. Power-On Reset

When power is applied to VDD, an internal power-on reset holds the NCA9534B in a reset condition until VDD has reached  $V_{PORR}$ . At that point, the reset condition is released and the NCA9534B registers and I2C state machine will initialize to their default states. The power-on reset typically completes the reset and enables the part by the time the power supply is above  $V_{PORR}$ . However, when it is required to reset the part, it is necessary to lower power supply below 0.2 V for at least 50 $\mu$ s.

### 7.4. Programming

#### 7.4.1. I2C Interface

The NCA9534B has a standard bidirectional I2C interface that is controlled by a master device in order to be configured or read the status of this device.

The I2C-bus is for 2-way, 2-line communication between different ICs or modules. The two lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. The size of the pull-up resistor is determined by the amount of capacitance on the I2C lines. Data transfer may be initiated only when the bus is idle.

Each slave on the I2C bus has a specific device address to differentiate between other slave devices that are on the same I2C bus. Many slave devices require configuration upon startup to set the behavior of the device. This is typically done when the master accesses internal register maps of the slave, which have unique register addresses. A device can have one or multiple registers where data is stored, written, or read.

The general procedure for a master to access a slave device is as below.

1. If a master wants to send data to a slave:

- Master-transmitter sends a START condition and addresses the slave-receiver.

- Master-transmitter sends data to slave-receiver.

- Master-transmitter terminates the transfer with a STOP condition.

2. If a master wants to receive or read data from a slave:

- Master-receiver sends a START condition and addresses the slave-transmitter.

- Master-receiver sends the requested register to read to slave-transmitter.

- Master-receiver receives data from the slave-transmitter.

- Master-receiver terminates the transfer with a STOP condition.

Note: MSB first in data transfer.

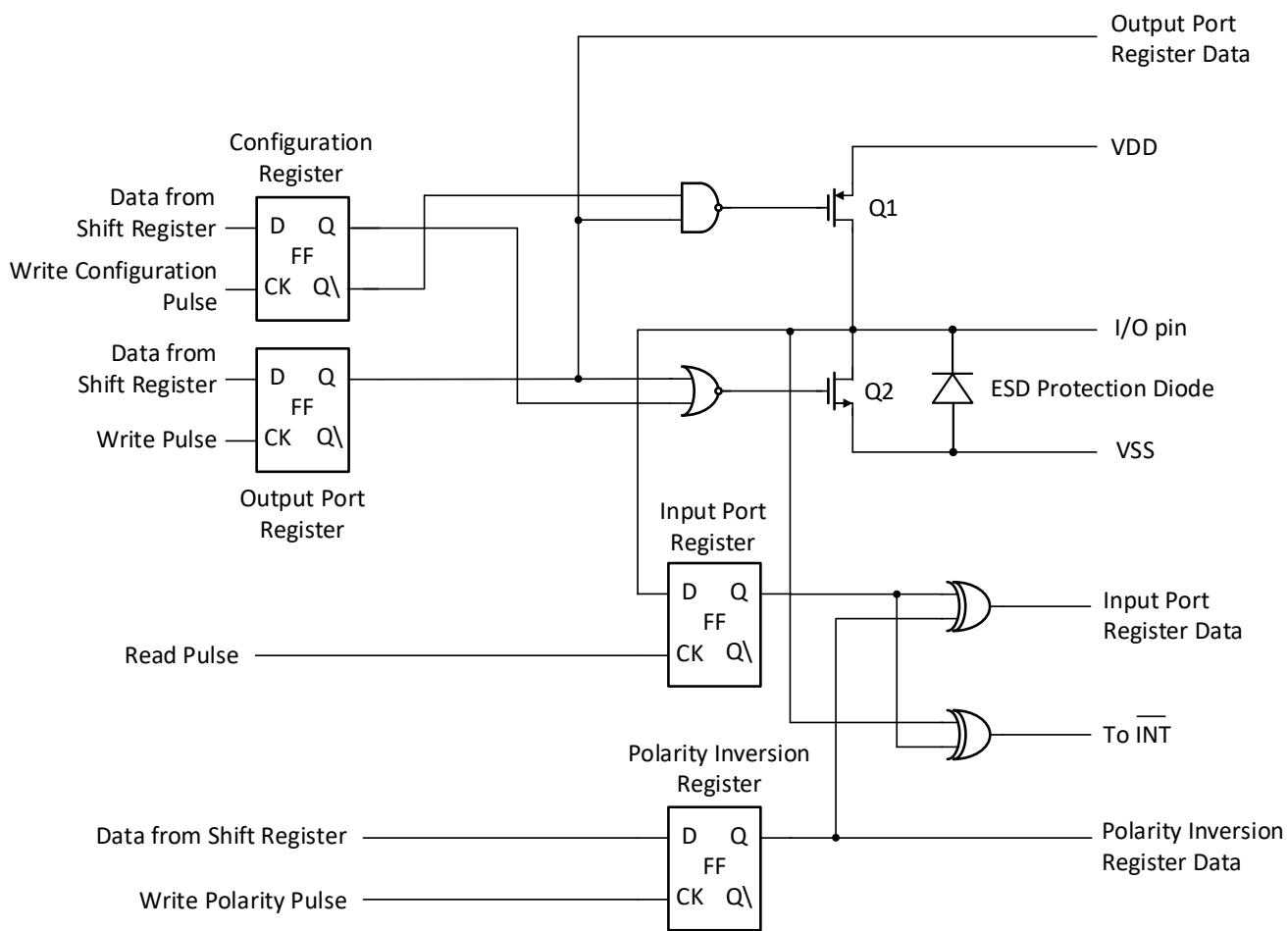

#### 7.4.2. Start and Stop Conditions

A HIGH-to-LOW transition of the data line while the clock is HIGH is defined as the START condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the STOP condition (P). A bus is considered idle if both SDA and SCL lines are high after a STOP condition.

Figure 7-3. Definition of START and STOP conditions

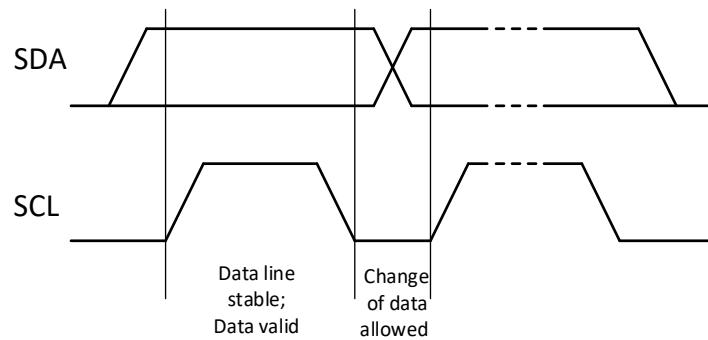

#### 7.4.3. Bit Transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse as changes in the data line at this time will be interpreted as control signals.

Figure 7-4. Bit transfer

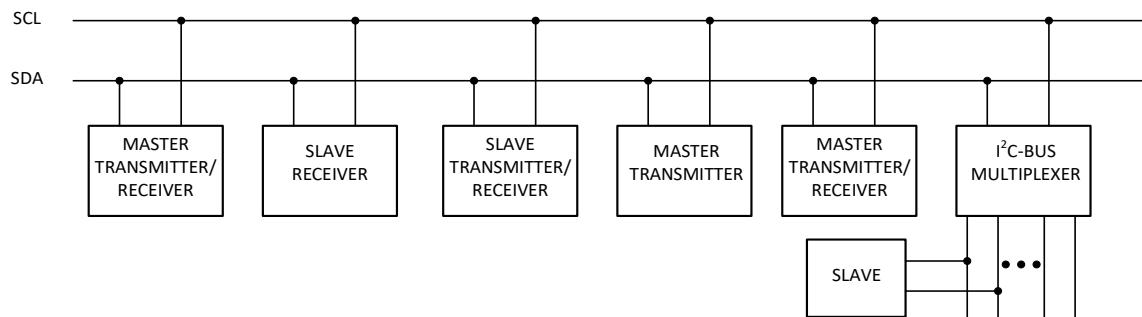

#### 7.4.4. System Configuration

A device generating a message is a ‘transmitter’; a device receiving is the ‘receiver’. The device that controls the message is the ‘master’ and the devices which are controlled by the master are the ‘slaves’ (see Figure 7-5).

Figure 7-5. System configuration

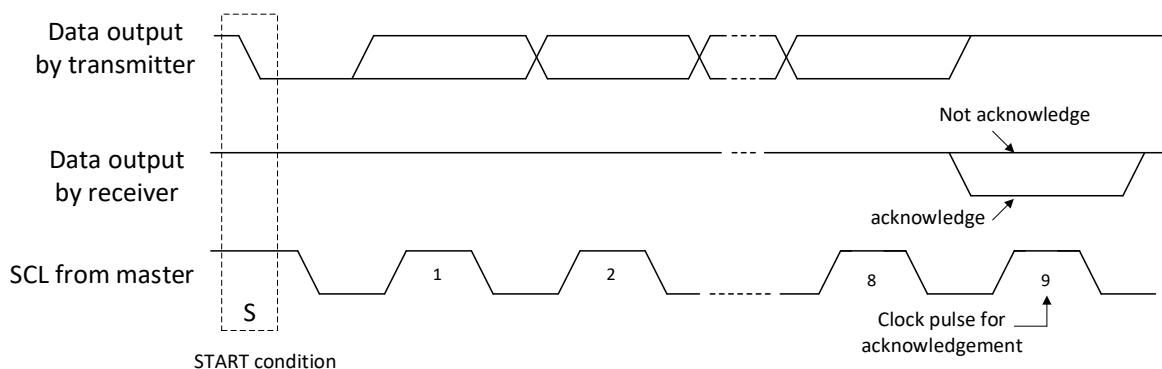

#### 7.4.5. Acknowledge

The number of data bytes transferred between the START and the STOP conditions from transmitter to receiver is not limited. Each byte of eight bits is followed by one acknowledge bit. The acknowledge bit is a HIGH level put on the bus by the transmitter, whereas the master generates an extra acknowledge related clock pulse.

A slave receiver which is addressed must generate an acknowledge after the reception of each byte. In the same way, a master must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges must pull down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse; set-up time and hold time must be taken into account.

A master receiver must signal an end of data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event, the transmitter must leave the data line HIGH to enable the master to generate a STOP condition.

Figure 7-6. Acknowledgement on I<sup>2</sup>C-bus

#### 7.5. Register Maps

The four registers within the NCA9534B are Input Ports, Output Ports, Polarity Inversion Ports, and Configuration Ports.

##### 7.5.1. Device Address

Figure 7-7 shows the address byte of the NCA9534B. The last bit of the target address defines the operation (read or write) to be performed. A HIGH (1) selects a read operation, while a LOW (0) selects a write operation.

Figure 7-7. NCA9534B device address

Table 7-1 shows the address reference of the NCA9534B.

Table 7-1. Address Reference

| Inputs |    |    | I2C Bus Slave Address         |

|--------|----|----|-------------------------------|

| A2     | A1 | A0 |                               |

| L      | L  | L  | 32(decimal), 20h(hexadecimal) |

| L      | L  | H  | 33(decimal), 21h(hexadecimal) |

| L      | H  | L  | 34(decimal), 22h(hexadecimal) |

| L      | H  | H  | 35(decimal), 23h(hexadecimal) |

| H      | L  | L  | 36(decimal), 24h(hexadecimal) |

| H      | L  | H  | 37(decimal), 25h(hexadecimal) |

| H      | H  | L  | 38(decimal), 26h(hexadecimal) |

| H      | H  | H  | 39(decimal), 27h(hexadecimal) |

### 7.5.2. Control Register and Command Byte

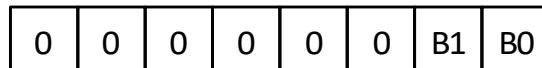

Following the successful acknowledgment of the address byte, the bus controller sends a command byte shown in Table 7-2 that is stored in the write-only control register in the NCA9534B. Three bits of this data byte state the operation (read or write) and the internal register (input, output, Polarity Inversion or Configuration) that is affected. The command byte is sent only during a write transmission. Figure 7-8 shows the control register bits.

Figure 7-8. NCA9534B control register bits

Table 7-2. Command byte

| Control Register Bits | Command Byte Hex | Register | Protocol                | Power-up Default |

|-----------------------|------------------|----------|-------------------------|------------------|

| B1                    | B0               |          |                         |                  |

| 0                     | 0                | 00h      | Input port              | Read byte        |

| 0                     | 1                | 01h      | Output port             | Read/write byte  |

| 1                     | 0                | 02h      | Polarity inversion port | Read/write byte  |

| 1                     | 1                | 03h      | Configuration port      | Read/write byte  |

### 7.5.3. Registers 0: Input port register

This register is an input-only port. It reflects the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output by Registers 3. Writing to this register has no effect.

Table 7-3. Input Port Register

| Bit     | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|---------|----|----|----|----|----|----|----|----|

| Symbol  | I7 | I6 | I5 | I4 | I3 | I2 | I1 | I0 |

| Default | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

#### 7.5.4. Registers 1: Output port register

This register is an output-only port. It reflects the outgoing logic levels of the pins defined as outputs by Registers 3. Bit values in this register have no effect on pins defined as inputs. In turn, reading from this register reflects the value that is in the flip-flop controlling the output selection, not the actual pin value.

Table 7-4. Output Port Register

| Bit     | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|---------|----|----|----|----|----|----|----|----|

| Symbol  | O7 | O6 | O5 | O4 | O3 | O2 | O1 | O0 |

| Default | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

#### 7.5.5. Registers 2: Polarity inversion register

This register allows the user to invert the polarity of the Input port register data. If a bit in this register is set (written with 1), the corresponding input port pin's polarity is inverted. If a bit in this register is cleared (written with 0), the corresponding input port pin's original polarity is retained.

Table 7-5. Polarity Inversion Port Register

| Bit     | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|---------|----|----|----|----|----|----|----|----|

| Symbol  | N7 | N6 | N5 | N4 | N3 | N2 | N1 | N0 |

| Default | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

#### 7.5.6. Registers 3: Configuration register

This register configures the directions of the I/O pins. If a bit in this register is set (written with 1), the corresponding port pin is enabled as an input with high-impedance output driver. If a bit in this register is cleared (written with 0), the corresponding port pin is enabled as an output.

Table 7-6. Configuration Port Register

| Bit     | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|---------|----|----|----|----|----|----|----|----|

| Symbol  | C7 | C6 | C5 | C4 | C3 | C2 | C1 | C0 |

| Default | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

### 7.6. Bus Transactions

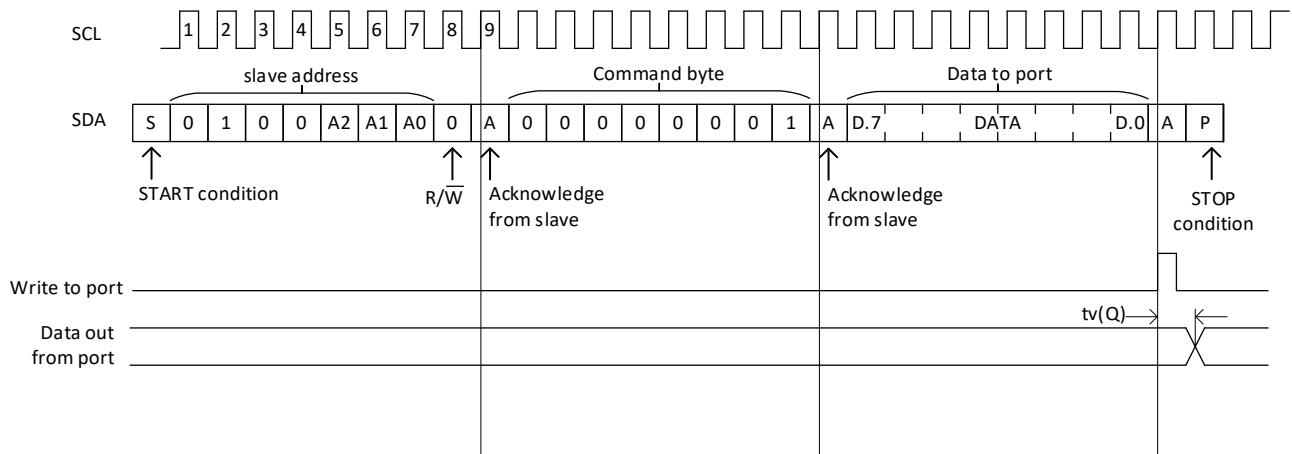

#### 7.6.1. Writing to the Port Registers

Data is transmitted to the NCA9534B by sending the device address and setting the least significant bit to a logic 0 (see Figure 7-7). The command byte is sent after the address and determines which register will receive the data following the command byte.

NCA9534B does not implement an auto-increment function, so once a command byte has been sent, the register which was addressed will continue to be accessed by reads until a new command byte has been sent.

Figure 7-9. Write to output port registers

Figure 7-10. Write to config registers

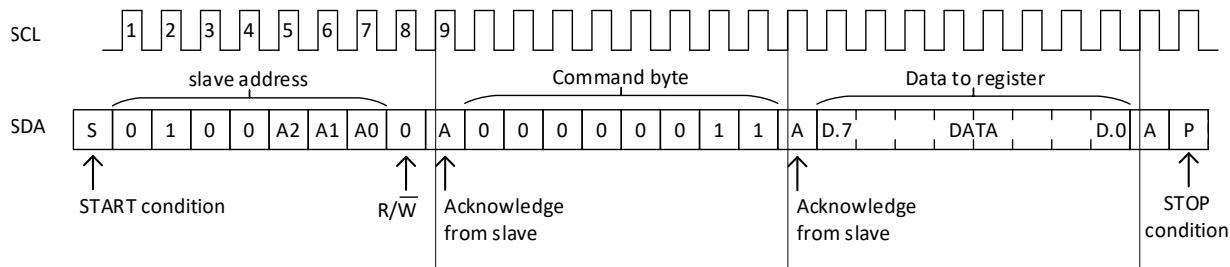

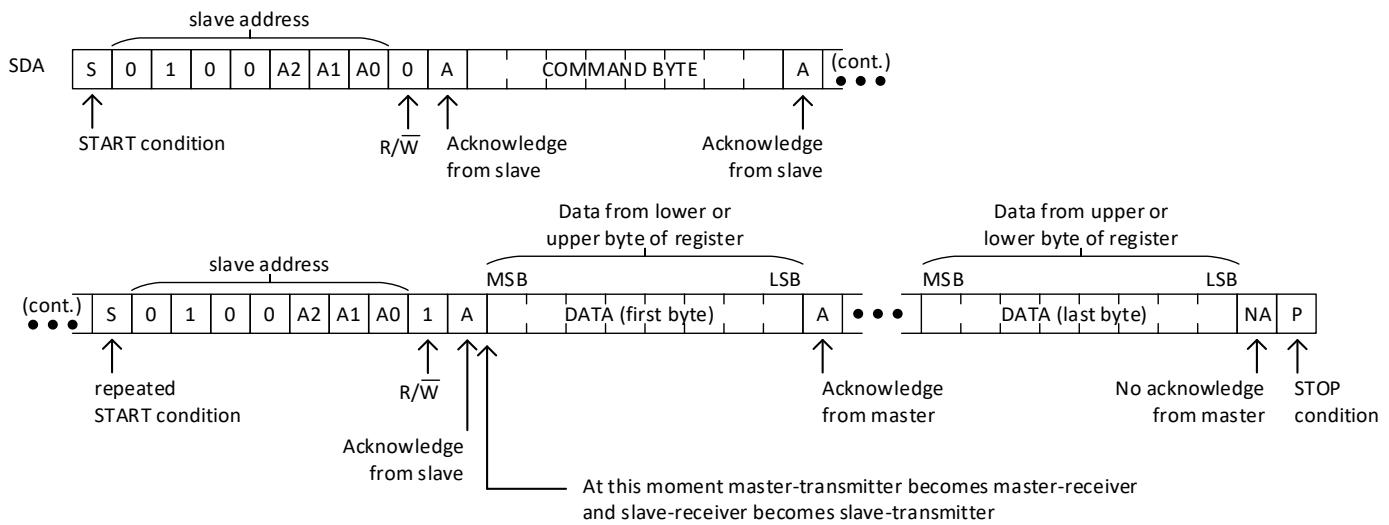

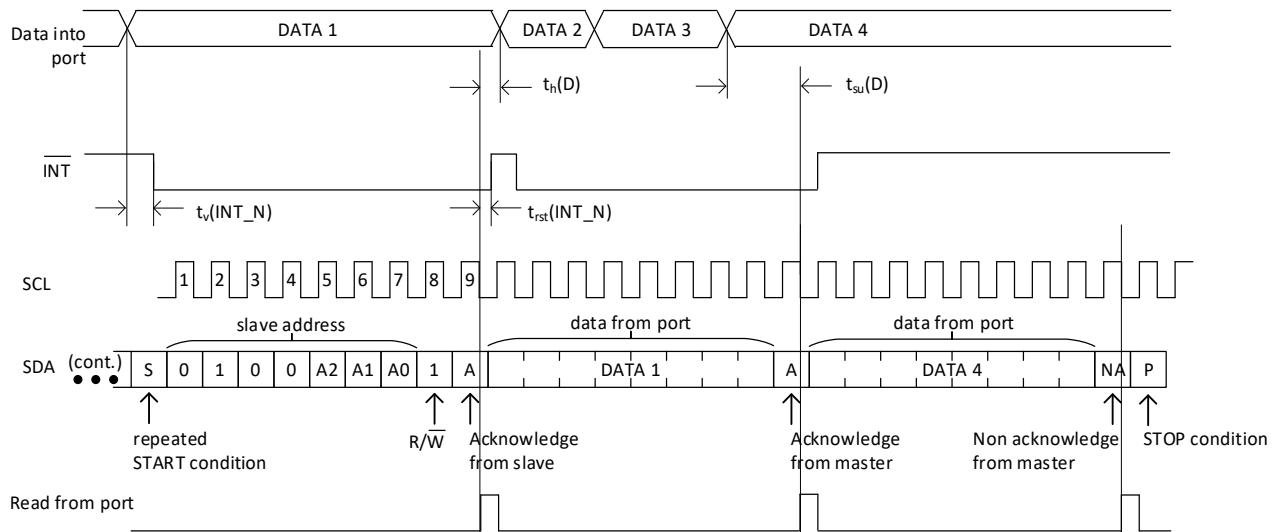

### 7.6.2. Reading the Port Registers

In order to read data from the NCA9534B, the bus master must first send the NCA9534B address with the least significant bit set to a logic 0 (see Figure 7-7). The command byte is sent after the address and determines which register will be accessed. After a restart, the device address is sent again, but this time the least significant bit is set to a logic 1. Data from the register defined by the command byte will then be sent by the NCA9534B (see Figure 7-11, Figure 7-12). Data is clocked into the register on the rising edge of the acknowledge clock pulse. There is no limitation on the number of data bytes received in one read transmission, but the final byte received, the bus master must not acknowledge the data.

**Remark:** Transfer of data can be stopped at any moment by a STOP condition.

Figure 7-11. Read from registers

**Remark:** Transfer of data can be stopped at any moment by a STOP condition. When this occurs, data present at the latest acknowledge phase is valid (output mode). It is assumed that the command byte has previously been set to '00' (read Input Port register).

Figure 7-12. Read input port registers

## 8. Application Design-In Information

### 8.1. Application Information

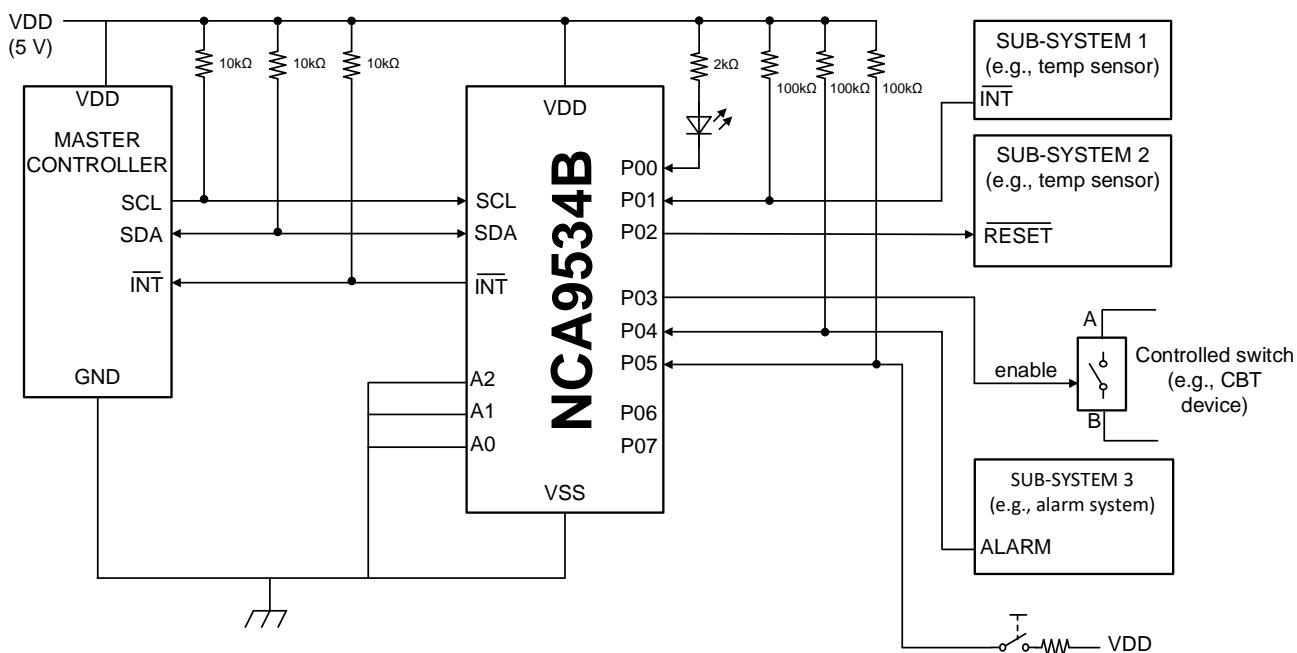

In applications of the NCA9534B, the device is connected as a slave to an I2C controller (processor), and the I2C bus may contain any number of other slave devices. The NCA9534B is typically in a remote location from the master, placed close to the GPIOs to which the master needs to monitor or control.

IO Expanders such as the NCA9534B are typically used for controlling LEDs (for feedback or status lights), controlling enable or reset signals of other devices, and even reading the outputs of other devices or buttons.

### 8.2. Typical Application

Figure 8-1. Typical Application

## 9. Order Information

| Part No.       | Temperature  | MSL Level | Package Type | Package Drawing | Package Qty |

|----------------|--------------|-----------|--------------|-----------------|-------------|

| NCA9534B-DTSPR | -40 to 125°C | 1         | TSSOP16      | TSSOP16         | 2500        |

| NCA9534B-DSWR  | -40 to 125°C | 2         | SOW16        | SOW16           | 1000        |

NOTE: All packages are RoHS-compliant with peak reflow temperatures of 260 °C according to the JEDEC industry standard classifications and peak solder temperatures.

## 10. Documentation Support

| Part Number | Product Folder             | Datasheet                  | Technical Documents        |

|-------------|----------------------------|----------------------------|----------------------------|

| NCA9534B    | <a href="#">Click here</a> | <a href="#">Click here</a> | <a href="#">Click here</a> |

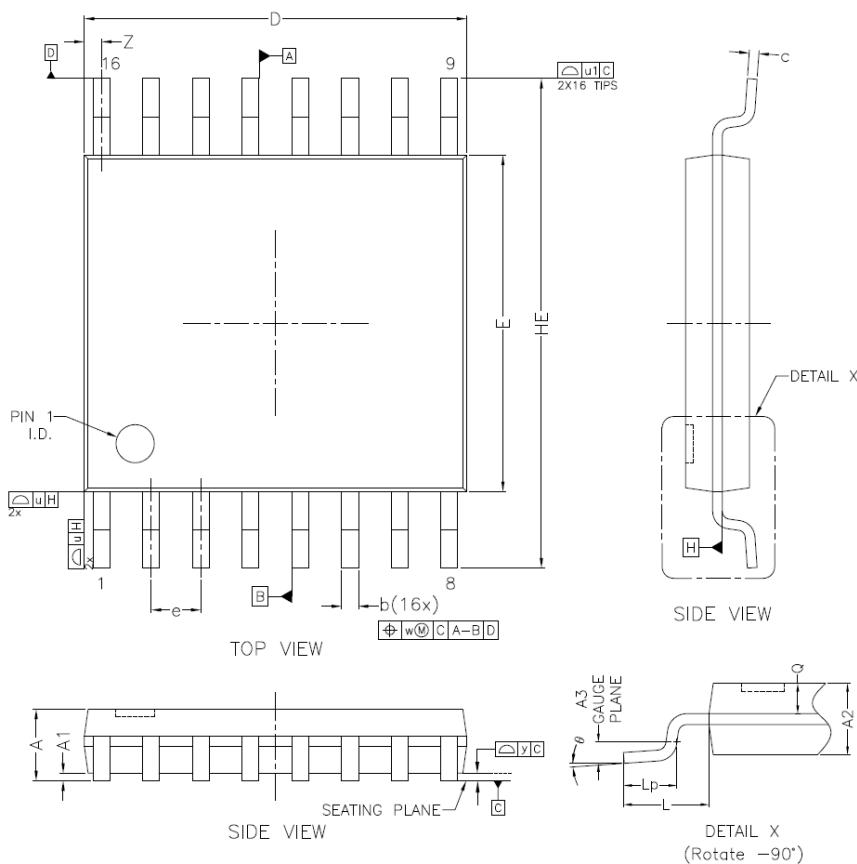

## 11. Package Information

\* CONTROLLING DIMENSION : MM

| SYMBOL | MM       |      |      |

|--------|----------|------|------|

|        | MIN.     | NOM. | MAX. |

| A      | --       | --   | 1.10 |

| A1     | 0.05     | --   | 0.15 |

| A2     | 0.80     | --   | 0.95 |

| b      | 0.19     | --   | 0.30 |

| c      | 0.10     | --   | 0.20 |

| D      | 4.90     | 5.00 | 5.10 |

| E      | 4.30     | 4.40 | 4.50 |

| HE     | 6.20     | --   | 6.60 |

| Q      | 0.30     | --   | 0.40 |

| e      | 0.65 BSC |      |      |

| A3     | 0.25 REF |      |      |

| L      | 1.00 REF |      |      |

| Lp     | 0.50     | --   | 0.75 |

| w      | 0.13     |      |      |

| y      | 0.10     |      |      |

| u      | 0.10     |      |      |

| u1     | 0.20     |      |      |

| Z      | 0.225    |      |      |

| θ      | 0°       | --   | 8°   |

NOTES:

1.0 COPLANARITY APPLIES TO LEADS, CORNER LEADS AND

DIE ATTACH PAD.

2.0 PLASTIC OR METAL PROTRUSIONS OF 0.15MM

MAXIMUM PER SIDE ARE NOT INCLUDED

Figure 11-1. TSSOP16 Footprint Shape and Dimension in millimeters

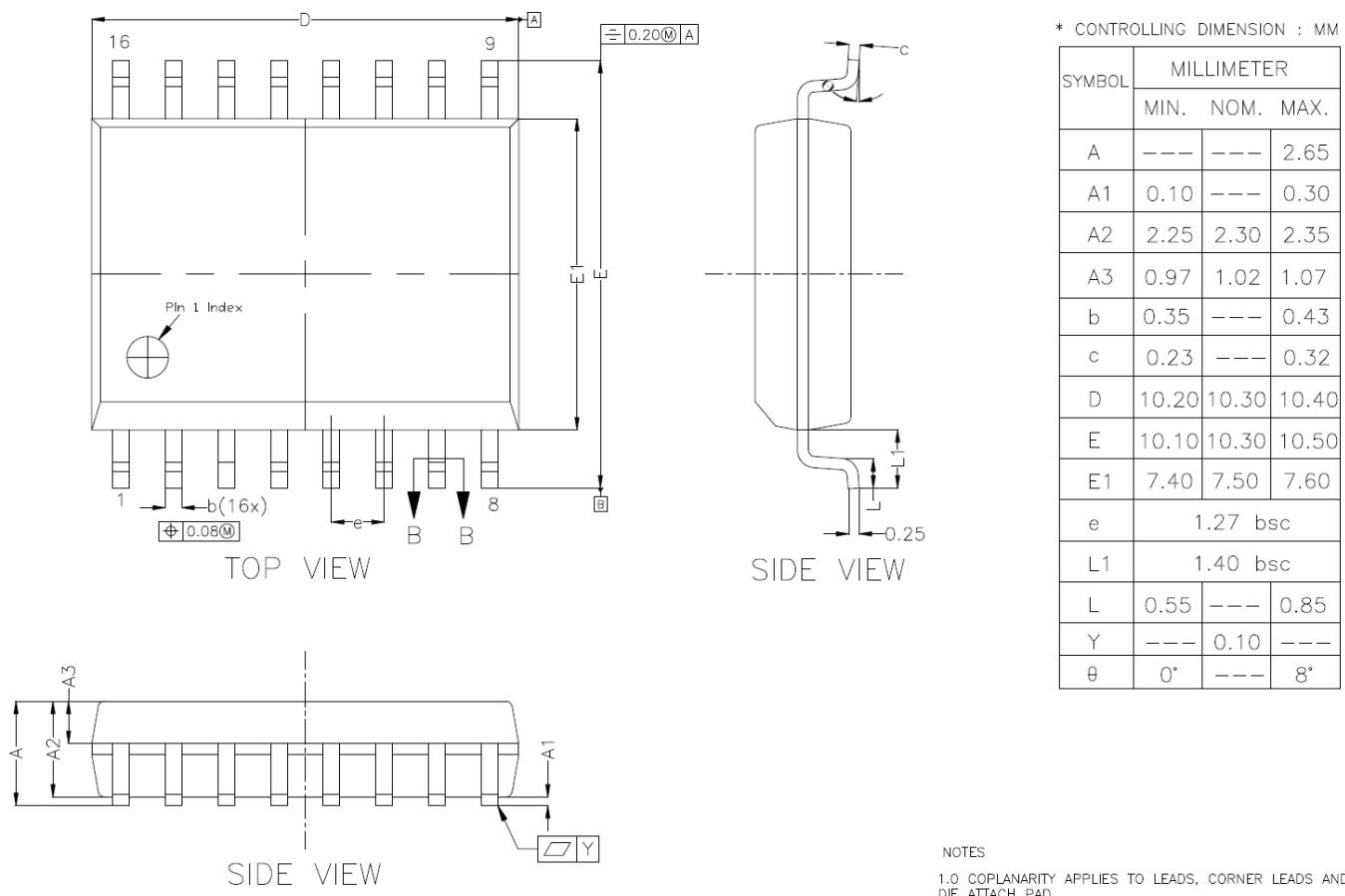

Figure 11-2. SOW16 Package Shape and Dimension in millimeters

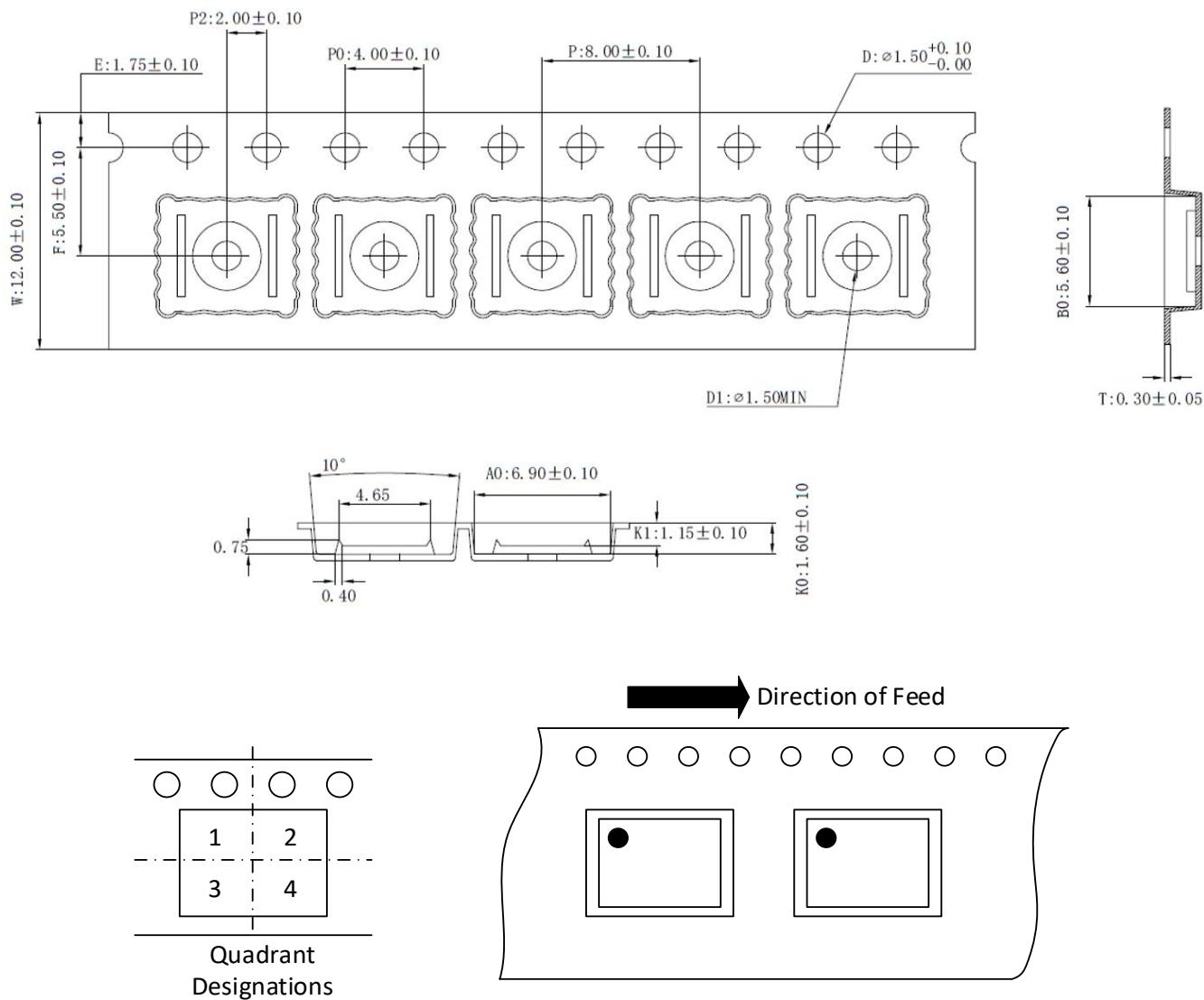

## 12. Tape and Reel Information

Figure 12-1. Tape and reel information for TSSOP16

1. 10 sprocket hole pitch cumulative tolerance  $\pm 0.20$  .

2. Carrier camber is within 1 mm in 250 mm.

3. Material : Black Conductive Polystyrene Alloy .

4. All dimensions meet EIA-481 requirements.

5. Thickness :  $0.30\pm 0.05$ mm.

6. Packing length per 22" reel : 378 Meters.

7. Component load per 13" reel : 1000 pcs.

8. Surface resistivity :  $10^5 \sim 10^{10} \Omega$

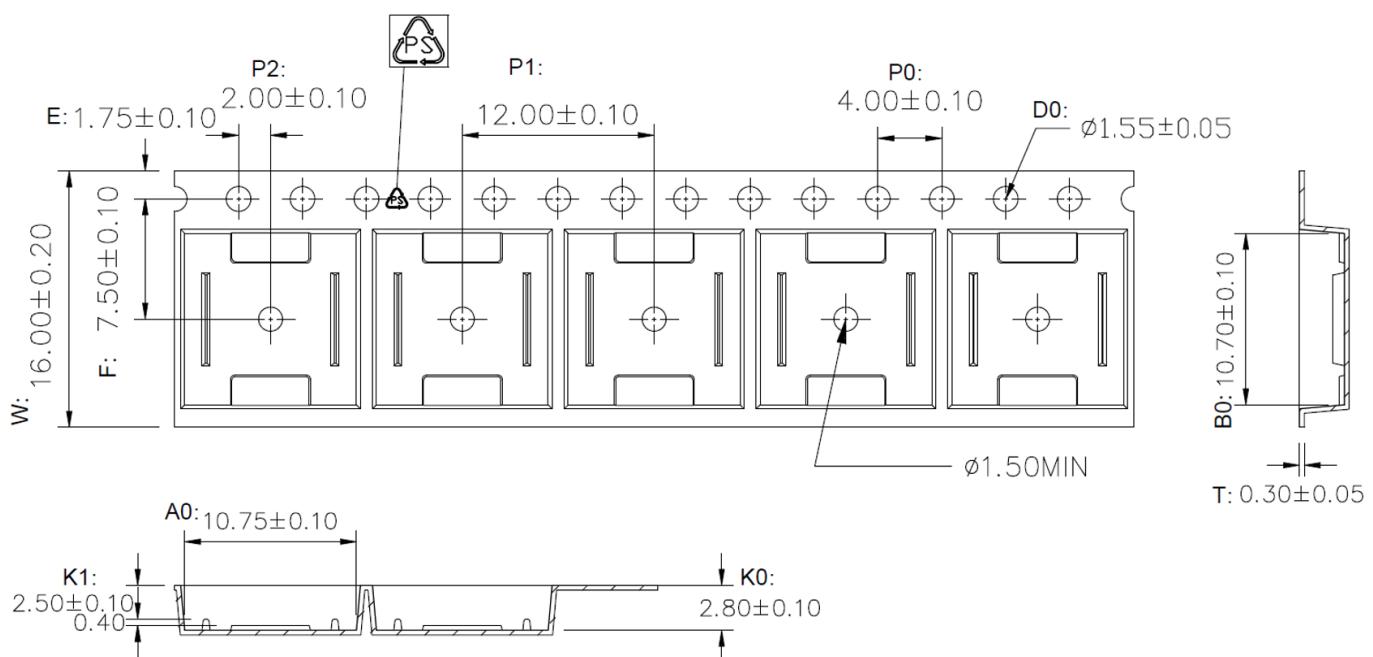

|    |            |

|----|------------|

| W  | 16.00±0.20 |

| A0 | 10.75±0.10 |

| B0 | 10.70±0.10 |

| K0 | 2.80±0.10  |

| K1 | 2.50±0.10  |

Figure 12-2. Tape and reel information for SOW16

### 13. Revision History

| Revision | Description                                                                            | Date       |

|----------|----------------------------------------------------------------------------------------|------------|

| 1.0      | Initial version                                                                        | 2022/12/28 |

| 1.1      | Package update; added ESD information; figure update; tape and reel information update | 2023/10/13 |

## **IMPORTANT NOTICE**

The information given in this document (the “Document”) shall in no event be regarded as any warranty or authorization of, express or implied, including but not limited to accuracy, completeness, merchantability, fitness for a particular purpose or infringement of any third party’s intellectual property rights.

Users of this Document shall be solely responsible for the use of NOVOSENSE’s products and applications, and for the safety thereof. Users shall comply with all laws, regulations and requirements related to NOVOSENSE’s products and applications, although information or support related to any application may still be provided by NOVOSENSE.

This Document is provided on an “AS-IS” basis and is intended only for skilled developers designing with NOVOSENSE’ products. NOVOSENSE reserves the rights to make corrections, modifications, enhancements, improvements or other changes to the products and services provided without notice. NOVOSENSE authorizes users to use this Document exclusively for the development of relevant applications or systems designed to integrate NOVOSENSE’s products. No license to any intellectual property rights of NOVOSENSE is granted by implication or otherwise. Using this Document for any other purpose, or any unauthorized reproduction or display of this Document is strictly prohibited. In no event shall NOVOSENSE be liable for any claims, damages, costs, losses or liabilities arising out of or in connection with this Document or the use of this Document.

For further information on applications, products and technologies, please contact NOVOSENSE ([www.novosns.com](http://www.novosns.com)).

**Suzhou NOVOSENSE Microelectronics Co., Ltd**