## 产品规格书

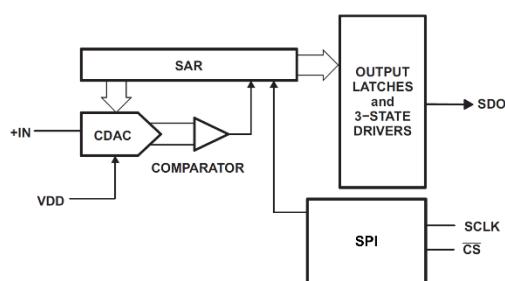

XC7886E 是一款 12 位的 ADC (Analog-to-Digital Converter) 芯片，即模拟数字转换器，具有高分辨率、高速率、低功耗、小尺寸、单极性的基本特征。

XC7886E 版本采用 3.3 V - 4.8 V 单电源供电，采样率最高可达 1000 KSPS。

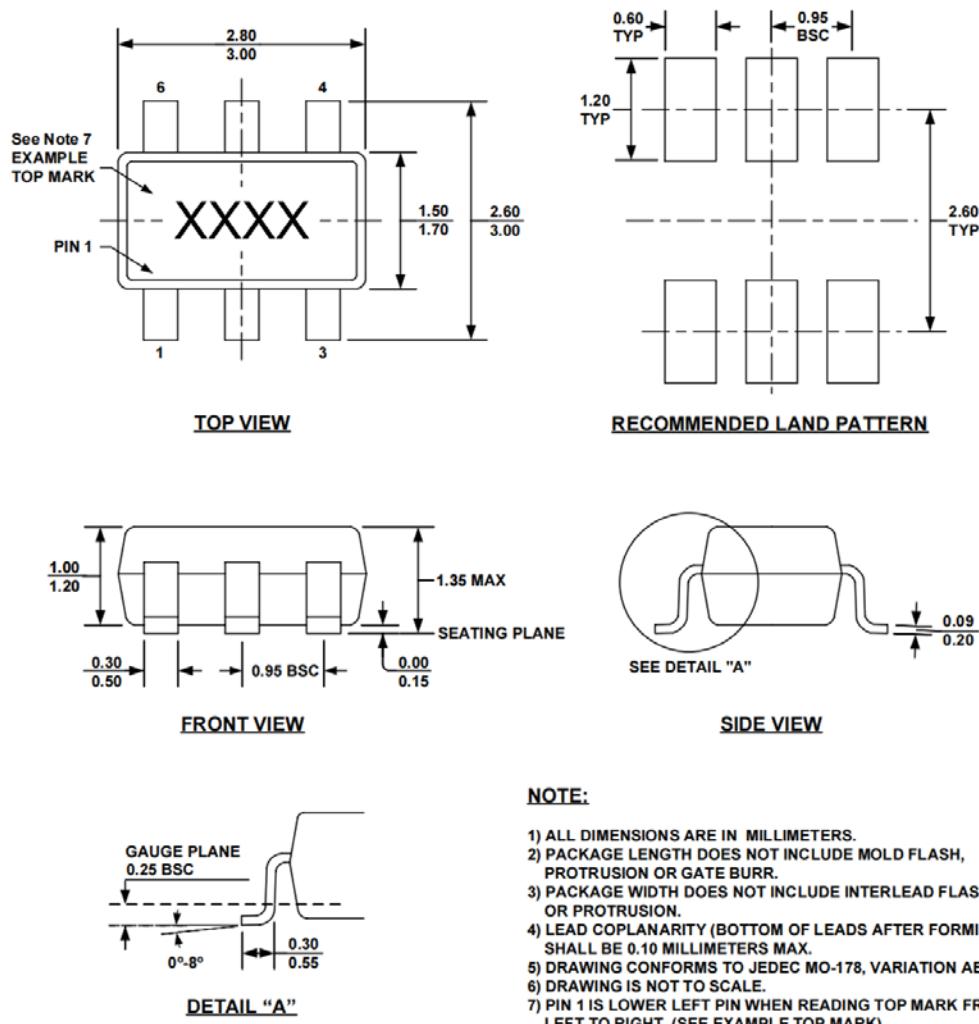

采用 6 引脚 SOT-23 封装，工作温度范围为 -40°C 至 85°C。

XC7886E 可 pin-to-pin 替代 ADS7886。

### 主要特征

- XC7886E 最高采样率：1000 KSPS

- 3.3 V—4.8 V 单电源供电

- 12 位分辨率

- 最高可达 20MHz 串行接口

- 低功耗（典型值）

2.40mW (3.3V, 1000 KSPS)

10.0mW (4.5V, 1000 KSPS)

- 最大误差  $\pm 1.5\text{LSB}$  INL,  $\pm 1.25\text{LSB}$  DNL

- 省电模式

- 6 引脚 SOT-23 封装

### 应用领域

- 无线通信中的基带转换器

- 数字驱动器中的电机电流和总线电压传感器

- 光网络（基于 DWDM、MEMS 的开关）

- 光学传感器

- 电池供电系统

- 医疗仪器

- 高速数据采集系统

- 高速闭环系统

原理图

封装效果图

## 1. 主要技术参数

- 3.3 V—4.8 V 单电源供电

- 12 位分辨率，无失码

- 微分非线性误差(DNL):  $\pm 1.25\text{LSB}$

- 积分非线性误差(INL):  $\pm 1.5\text{LSB}$

- 信噪比失真(SNR): 72.5dB @100 KHz

- 总谐波失真(THD): -84.5dB @100 KHz

- XC7886E 最高采样率: 1000 KSPS

- 最高可达 20MHz SPI 串行接口

- 无流水线周期延迟

- 省电模式

- 单极单通道输入, 0 V 至  $V_{DD}$  范围

- 6 引脚 SOT-23 封装

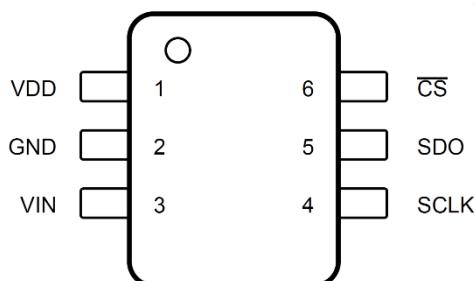

## 2. 引脚配置

引脚图

| 引脚   |    | 描述                          |

|------|----|-----------------------------|

| 名称   | 序号 |                             |

| VDD  | 1  | 电源输入也类似于 ADC 的基准电压。         |

| GND  | 2  | 模拟输入信号接地。所有模拟和数字信号都以此引脚为基准。 |

| VIN  | 3  | 模拟信号输入。                     |

| SCLK | 4  | 串行时钟输入。                     |

| SDO  | 5  | 串行数据输出。                     |

| CS   | 6  | 片选信号, 低电平有效。                |

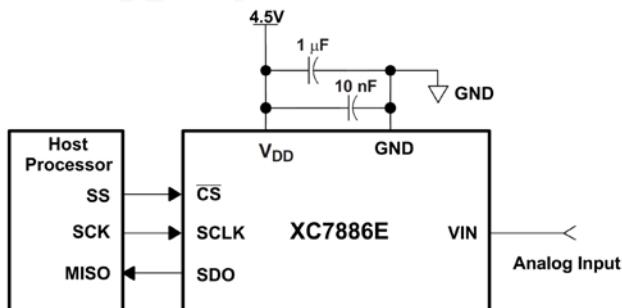

## 3. 典型连接

XC7886E 的典型连接电路, 请参见下图。电源应来自稳定的供电设备, 如 LDO。1 $\mu\text{F}$  和 10nF 耦合电容应尽可能靠近 XC7886E 引脚。始终将 VDD 电源设置为大于或等于最大 VIN 输入信号, 以避免最大转换码饱和。

电路连接图

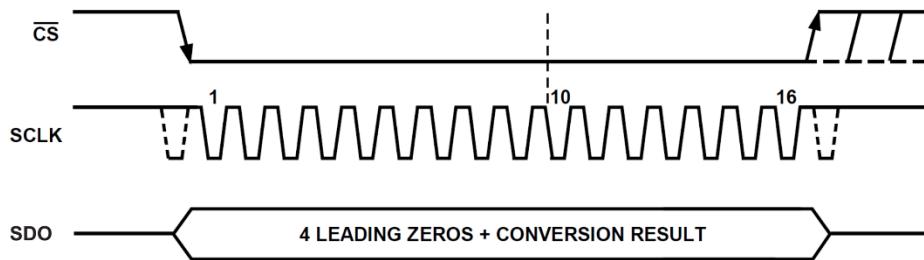

## 4.时序图

时序图

在 $\overline{CS}$ 引脚降低时并提供串行时钟 SCLK 信号，XC7886E 即可启动一个转换周期，如图所示。设备在转换过程中输出数据，数据都是 MSB 格式，在 4 个前导零后输出 12 位转换后的数据。在 SCLK 的第 16 个下降沿，SDO 进入三态，转换周期结束。

$\overline{CS}$ 在 16 个时钟 SCLK 过后拉高，直到 SDO 进入三态后的时间结束，再次将 $\overline{CS}$ 拉低即可开始下一次转换。

## 5.省电模式

XC7886E 系列具有自动断电功能。在关闭所有电路之后，转换器在这种模式下通常只消耗很小的电流。当出现 $\overline{CS}$ 下降沿时，设备自动唤醒。然而，只有当 SCLK 的第三个下降沿出现，所有的功能块才完全启动。经过 XC7886E 的 SCLK 的第 16 个下降沿，设备检测到转换结束，设备就会又自动断电。如果 $\overline{CS}$ 在 10 个 SCLK 之前被拉高，XC7886E 就会中止正在进行的数据转换过程，转换器将强迫进入断电模式，并且在接下来的一次转换中没有有效数据。

SCLK 的频率越高，转换器在固定吞吐率下消耗的功耗就越低，因为在固定的时间段内转换时间越短，即转换器在每个转换周期中更多地处于自动断电模式。对于特定的 SCLK 频率，采样时间（ $\overline{CS}$ 下降沿到 SCLK 的第三个下降沿）和转换时间（四个前导零加上 12 个 SCLK 周期）是固定的，所以较低的吞吐量时（即总的转换周期延长）增加了断电所占的时间比例，从而使功耗降低。

## 6.封装示意图

## 7.注意事项

1. 拆封的IC、管装IC等必须放在干燥柜内储存，干燥柜内湿度<20% R.H。

2. 存取后都以静电包装防护袋保存元件。

3. 防静电损伤：器件为静电敏感器件，传输、装配、测试过程中应采取充分的防静电措施。

4. 用户在使用前应进行外观检查，电路底部、侧面、四周光亮方可进行焊接。如出现氧化可采去氧化手段对电路进行处理，处理完成电路必须在12小时内完成焊接。