# 高速 MOS 驱动电路设计和应用指南

## 摘要

本篇论文的主要目的是来论证一种为高速开关应用而设计高性能栅极驱动电路的系统研究方法。它是对“一站买齐”主题信息的收集，用来解决设计中最常见的挑战。因此，各级的电力电子工程师对它都应该感兴趣。

对最流行电路解决方案和他们的性能进行了分析，这包括寄生部分的影响、瞬态的和极限的工作情况。整篇文章开始于对 MOSFET 技术和开关工作的概述，随后进行简单的讨论然后再到复杂问题的分析。仔细描述了设计过程中关于接地和高边栅极驱动电路、AC 耦合和变压器隔离的解决方案。其中一个章节专门来解决同步整流器应用中栅极驱动对 MOSFET 的要求。

另外，文章中还有一些一步一步的参数分析设计实例。

## 简介

MOSFET 是 Metal Oxide Semiconductor Field Effect Transistor 的首字母缩写，它在电子工业高频、高效率开关应用中是一种重要的元件。或许人们会感到不可思议，但是 FET 是在 1930 年，大约比双极晶体管早 20 年被发明出来。第一个信号电平 FET 晶体管制成于二十世纪 60 年代末期，而功率 MOSFET 是在二十世纪 80 年代开始被运用的。如今，成千上万的 MOSFET 晶体管集成在现代电子元件，从微型的到“离散”功率晶体管。

本课题的研究重点是在各种开关模型功率转换应用中栅极驱动对功率 MOSFET 的要求。

## 场效应晶体管技术

双极晶体管和场效应晶体管有着相同的工作原理。从根本上说，两种类型晶体管均是电荷控制元件，即它们的输出电流和控制极半导体内的电荷量成比例。当这些器件被用作开关时，两者必须和低阻抗源极的拉电流和灌电流分开，用以为控制极电荷提供快速的注入和释放。从这点看，MOS-FET 在不断的开关，当速度可以和双极晶体管相比拟时，它被驱动的将十分的‘激烈’。理论上讲，双极晶体管和 MOSFET 的开关速度是基本相同的，这取决于载流子穿过半导体所需的时间。在功率器件的典型值为 20 ~ 200 皮秒，但这个时间和器件的尺寸大小

有关。与双极结型晶体管相比，MOSFET 在数字技术应用和功率应用上的普及和发展得益于它的两个优点。优点之一就是在高频率开关应用中 MOSFET 使用比较方便。MOSFET 更加容易被驱动，这是因为它的控制极和电流传导区是隔离开的，因此不需要一个持续的电流来控制。一旦 MOSFET 导通后，它的驱动电流几乎为 0。另外，在 MOSFET 中，控制电荷的积累和存留时间也大大的减小了。这基本解决了设计中导通电压降（和多余的控制电荷成反比）和关断时间之间的矛盾。因此，MOSFET 技术以其更加简单的、高效的驱动电路使它比晶体管设备具有更大的经济效益。

此外，有必要突出强调下，尤其是在电源应用上，MOSFET 本身具有阻抗特性。MOSFET 漏源端的电压降和流经半导体的电流成线性关系。这种线性关系，以 MOSFET 的  $R_{DS(on)}$  表现出来，即导通阻抗。对于一个给定的栅源电压和温度的器件，其导通阻抗是恒定的。和 p-n 结  $-2.2\text{mV}/^\circ\text{C}$  的温度系数相反，MOSFET 有一个正的温度系数，约为  $0.7\% /^\circ\text{C}$  到  $1\% /^\circ\text{C}$ 。MOSFET 的这一正温度系数使得它成为在大功率电源应用的并联工作（由于使用一个器件是不实际或不可能的）上的理想选择。由于 MOSFET 较好的温度系数，串联的管子通常是均分电流。电流的均分是自动实现的，这是因为它的温度系数作为一个缓慢的负反馈系统。当电流较大时设备温度将会升高，但是不要忘记源漏极间的电压是不变的，温度升高将会使源漏极间电阻变大，增大的电阻又会使电流减小，因此管子的温度又会下降。最后，会达到一个动态平衡，并联的管子都通过相同的电流。在电流分配中，源漏极导通电阻的初始值和有不同温度特性的结电阻在均分电流时将会引起较大的误差，最高可达 30%。

## 器件类型

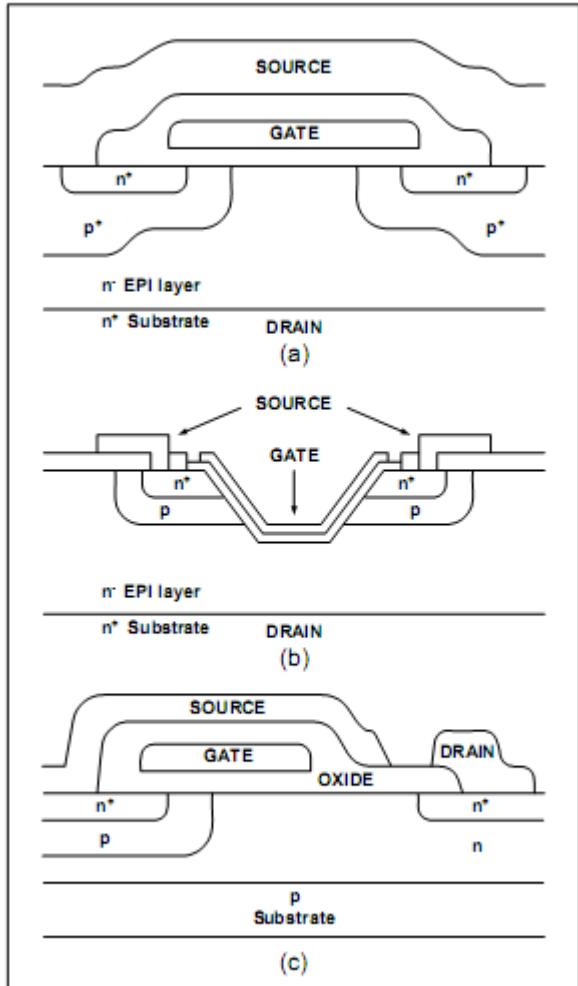

几乎所有的 MOSFET 制造厂商都有制造最佳管子的独特制造技术，但所有这些在市场上的管子都可分为基本的三类，如图 1 所示。

Figure 1. Power MOSFET device types

双扩散型晶体管在 1970 年开始应用于电源方面并在以后的时间里不断的发展。使用多晶硅闸门结构和自动调整过程，使高密度的集成和电容迅速的减小成为可能。

下一个重大的进步是在功率 MOSFET 器件上 V 沟槽技术或者称为沟渠技术，使集成度进一步的提高。更好的性能和更高的集成度并不是由你随便就能得来的，这是因为这将导致 MOS 器件沟渠

更难制造。

在这里第三个器件类型是横向功率 MOSFET。该器件的电压、电流是受限制的，这是由于其对芯片形状的低效利用。然而，他们能在低电压应用上提供很大的效益，如在微型电源或在隔离转换同步整流器中。由于横向功率 MOSFET 有着相当小的电容，因此他们的开关速度可以很快而且栅极驱动损耗也比较小。

## 场效应晶体管模型

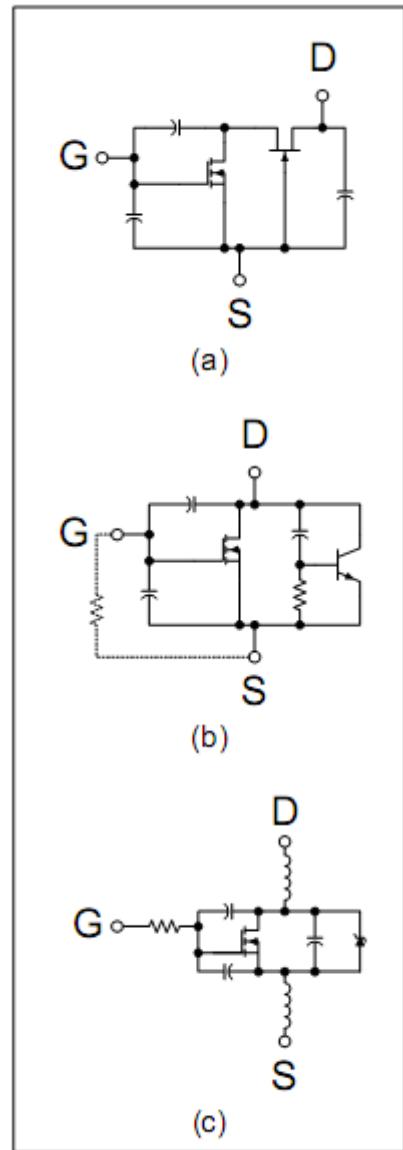

有很多的模型来说明 MOSFET 如何工作，然而找到正确的适合的模型是比较困难的。大多数 MOSFET 制造商为他们的器件提供普通或者军用（Spice and/or Saber）模型，但是这些模型很少告诉使用者在实际使用中的陷阱。他们甚至很少提供在使用中最常见的最普通问题的解决方案。一个真正有用的 MOSFET 模型会从应用的角度描述器件所有重要的性质，这使得其模型可能会相当复杂。另一方面，如果我们把模型限制在某一问题领域，那么我们可以得到十分简单并有意义的 MOSFET 模型。在图 2 中第一个模型是基于 MOSFET 器件的实际结构，它主要用于直流的分析。它表示出了沟道阻抗和 JFET（相当于外延层的阻抗）。外延层的厚度（决定外延层的阻抗）是器件额定电压的函数，而高电压的 MOSFET 需要一个厚的外延层。

图 2b 可以非常好的展示 MOSFET 的  $dv/dt$  引发的击穿特性。它主要展现了两种击穿机制，即诱发寄生晶体管（所有的管子均有）的导通和  $dv/dt$  根据栅极阻抗诱发沟道导通。现代的功率 MOSFET 由于生产工艺的提高减小了基极和发射极的电阻，因此，实际上对  $dv/dt$  诱发寄生 npn 晶体管导通是有免疫的。必须指出的是，寄生性双极晶体管还扮演着另一个重要的角色。它的基集结就是有名的 MOSFET 的体二极管。

图 2c 是场效应晶体管的开关模型。影响开关性能的最重要的寄生部分都展现在这个模型中。它们对器件的开关过程的影响将在下一章中讨论。

## MOSFET 的重要参数

当 MOSFET 工作在开关状态下，目标是在可能的最短时间内实现器件在最

Figure 2. Power MOSFET models

低阻抗和最高阻抗之间的切换。由于 MOSFET 实际的开关时间（10ns—60ns）至少比理论开关时间（50ps—200ps）大 2~3 个数量级，因此有必要了解其差异。参考图 2 中 MOSFET 的模型，可以发现所有的模型在器件的三端之间都连有一个等效电容。毫无疑问，开关速度和性能决定于这三个电容上电压变化的快慢。

因此，在高速开关应用中，器件的寄生电容是一个重要的参数。电容  $C_{GS}$  和电容  $C_{GD}$  与器件的实际几何尺寸有关，而电容  $C_{DS}$  是寄生在双集晶体管的基集二极管间的电容。

电容  $C_{GS}$  是由于源极和栅极形成的沟道区域的重叠形成的。它的值由器件实际的区域几何尺寸决定而且在不同的工作条件下保持不变。电容  $C_{GD}$  由两个因素决定。一是耗尽层（是非线性的）的电容；二是 JFET 区域和栅极的重叠。等效电容  $C_{GD}$  是器件漏源极电压的函数，大致可用下面公式计算得到：

$$C_{GD} \approx \frac{C_{GD,0}}{1 + K_1 \cdot \sqrt{V_{DS}}}$$

电容  $C_{DS}$  也是非线性的，这是由于它是体二极管的结电容。它和电压间关系为：

$$C_{DS} \approx \frac{C_{DS,0}}{K_2 \cdot \sqrt{V_{DS}}}$$

不幸的是，上述的所有电容在器件的资料表中均未涉及和说明。它们的值由  $C_{iss}$ （栅短路共源输入电容）、 $C_{rss}$ （栅短路共源反向传输电容）、 $C_{oss}$ （栅短路共源输出电容）间接给出，而且必须用下列公式计算：

$$C_{GD} = C_{RSS}$$

$$C_{GS} = C_{ISS} - C_{RSS}$$

$$C_{DS} = C_{OSS} - C_{RSS}$$

在开关应用中，电容  $C_{GD}$  会引起其他复杂问题，这是由于它处于器件输入与输出间的反馈回路中。因此，它在开关应用中有效值可能会很大，它的值取决于

MOSFET 的漏源极电压。这种现象被称为“Miller”效应，而且可以用下式表示：

$$C_{GD,eqv} = (1 + g_{fs} \cdot R_L) \cdot C_{GD}$$

由于电容  $C_{GD}$  和  $C_{GS}$  是和电压有关的，因此只有把测试条件列出来时，那些资料中的数据才是有效的。对于一个确定的应用，有关的平均电容值必须由计算得来，而计算是基于建立于实际电压所需要的电荷。对于大多数的功率 MOSFET 来说，下面公式将会十分有用：

$$C_{GD,ave} = 2 \cdot C_{RSS,spec} \cdot \sqrt{\frac{V_{DS,spec}}{V_{DS,off}}}$$

$$C_{OSS,ave} = 2 \cdot C_{OSS,spec} \cdot \sqrt{\frac{V_{DS,spec}}{V_{DS,off}}}$$

下一个将要谈及的重要的参数是栅极网格阻抗， $R_{g,I}$ 。这个寄生阻抗描述了器件内部栅极信号分配与阻抗之间的联系。在高速开关应用中它的重要性尤为突出，因为它介于驱动和器件输入电容之间，直接影响 MOSFET 的开关时间和  $dv/dt$  能力。在工业生产中已经意识到这个问题，实际中的高速 MOSFET 器件如 RF MOSFET 在栅极信号分配中使用金属栅极用来代替高阻抗的硅栅极。在资料表中阻抗  $R_{g,I}$  并没有指明，但在实际的应用中它可能是器件一个十分重要的特性。在这篇文章的后面，附录 A4 展示了通过使用阻抗电桥采用一种典型的测量装置来确定栅极内部阻抗值。

很明显，栅极阈值电压也是一个临界特性。有必要注意一下，在器件资料表中  $V_{TH}$ (开启电压)的值是指在 25°C，而且在漏极电流很小的情况下，电流典型值是 250uA。因此，它并不等同于被大家公认的栅极开关波形的 Miller 平坦区。关于开启电压  $V_{TH}$  的另一个很少提到的是约为 -7mV/°C 的温度系数，在 MOSFET 逻辑电平栅极电路驱动中它有着尤为重要的意义，它的开启电压  $V_{TH}$  比在正常的测试条件下已经变低了。由于 MOSFET 工作在较高的温度，栅极驱动设计必须中适当的考虑到在截止时较低的开启电压， $dv/dt$  免疫能力的计算见附录 A 和

F。场效应晶体管的跨导是线性工作区中小信号的增益。有必要指出在管子每次导通或截止时，都要必须经过线性工作区，此时的电流取决于栅源电压。正向跨导  $g_{fs}$ ，反映了漏极电流和栅源电压之间的小信号关系，具体关系如下：

$$g_{fs} = \frac{dI_D}{dV_{GS}}$$

因此，MOSFET 在线性区的最大电流公式为：

$$I_D = (V_{GS} - V_{th}) \cdot g_{fs}$$

变换  $V_{GS}$ , Miller 平坦区电压可近似写成漏极电流的函数：

$$V_{GS, Miller} = V_{th} + \frac{I_D}{g_{fs}}$$

其他重要的参数如  $L_D$ ---漏极电感和  $L_s$ ---源极电感在开关性能中也有显著的限制。典型的  $L_D$  和  $L_s$  值会在器件资料单中列出，而且他们的值主要和器件的封装类型有关。它们的影响通常可以和外部寄生元件（通常和布局和外电路因素如漏电感、检测电阻等等）一同分析。

完整的，外部系列栅极电阻和 MOSFET 的输出阻抗在高速栅极驱动设计中是决定性的因素，因为它们在开关速度和最终开关损耗上有着深远的意义。

## 开关应用

现在，所有的角色都讨论完了，让我们来研究下 MOSFET 的真实开关行为。为了更好的理解其基本过程，电路中的寄生电感将会被忽略掉。随后，它们在基本工作中各自的影响将会单独的分析。此外，下面的说明和钳位感应开关有关，这因为大多数被用于电源模式的 MOSFET 晶体管和高速门驱动电路工作于那个模式。

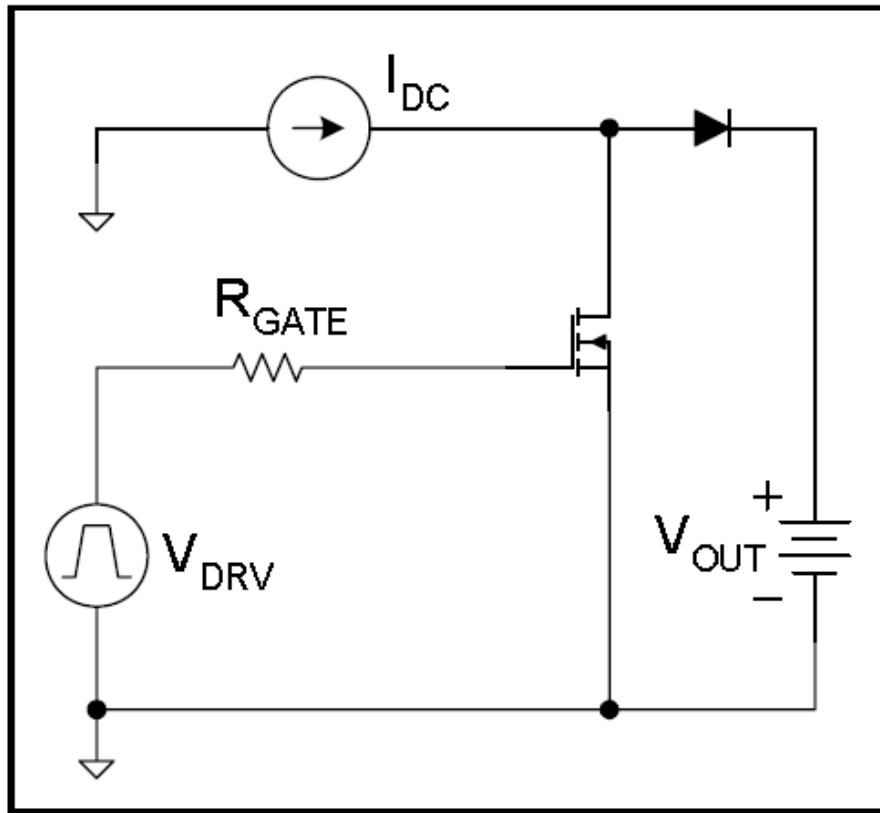

*Figure 3. Simplified clamped inductive switching model*

一个最简单的钳位感应开关模型如图三 (Figure) 所示, 直流电流源代表感应器。在开关间隔比较小的情况下, 它的电流可看作是连续的。在 MOSFET 截止期间二极管为电流提供了一个回路, 设备的漏极终端用一个电池来象征表示。

### 导通过程

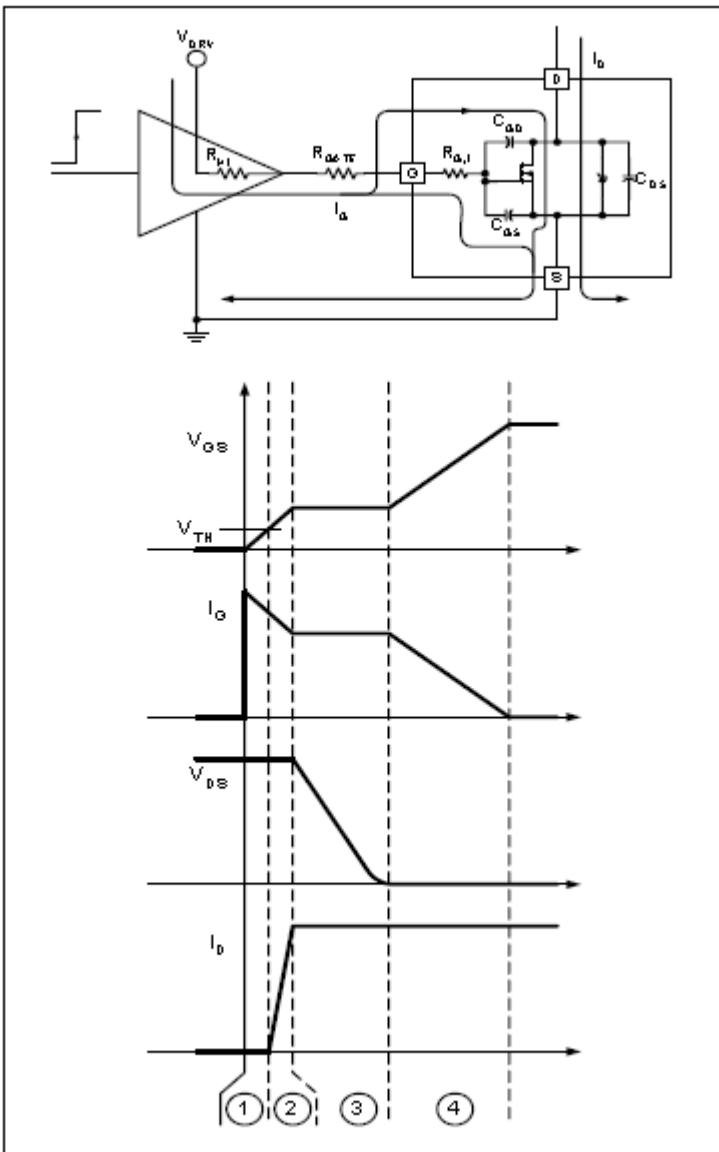

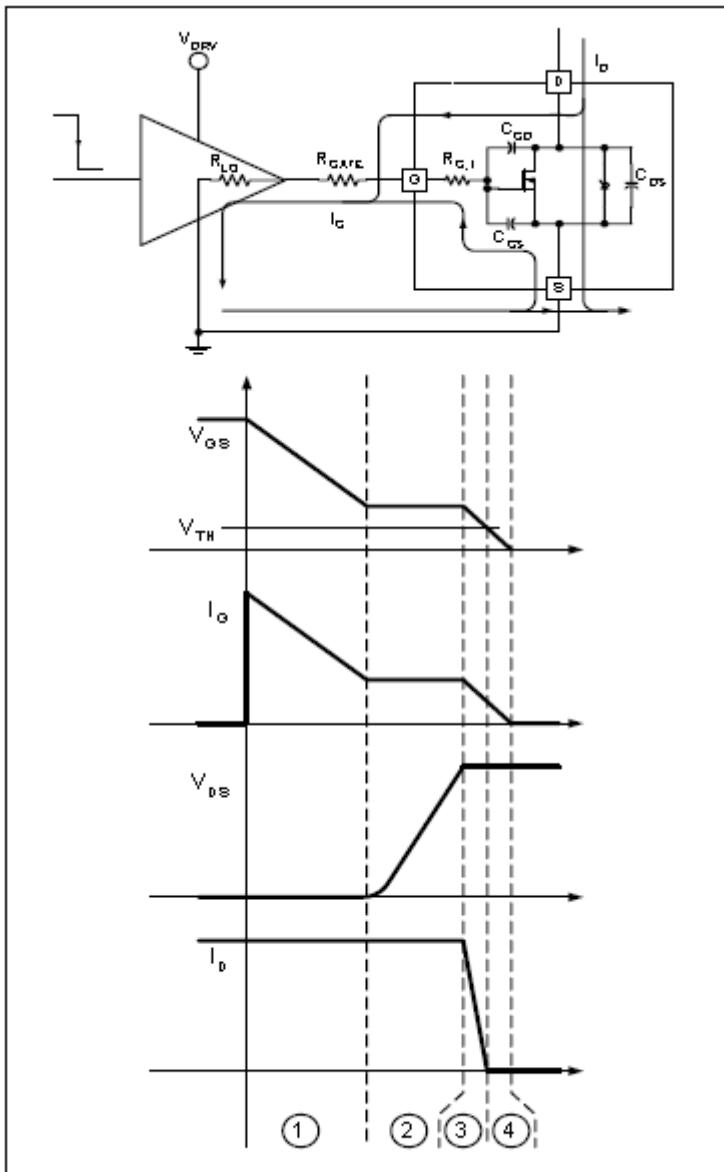

MOSFET 的导过过程可分为如图 4 (即 Figure4) 所示的四个阶段。

Figure 4. MOSFET turn-on time intervals

第一个阶段：输入电容从 0 开始充电到  $V_{th}$ , 在这个过程，栅极绝大部分电流都用来给电容  $C_{GS}$  充电，也有很小的电流流过电容  $C_{GS}$ 。当电容  $C_{GS}$  的电压增加到门的极限时，它的电压就会有稍微的减小。这个过程称为导通延迟，这是因为此时器件的漏极电流和漏极电压均未发生变化。

当栅极电压达到开启电压时，MOSFET 处于微导通状态。在第二个阶段，栅极电压从  $V_{th}$  上升到 Miller 平坦区，即  $V_{GS,Miller}$ 。这是器件的线性工作区，电流和栅极电压成正比。在栅极的一侧，电流如第一阶段一样流入电容  $C_{GS}$  和  $C_{GD}$ ，电容  $V_{GS}$  的电压将会不断升高。在器件的输出端，漏极电流也不断变大，但

是漏源电压基本不变，保持先前水平( $V_{DS,OFF}$ )。这从图 3 的原理图可以看出来。

当所有电流都流入 MOSFET 而且二极管完全截止（pn 结能承受反向电压）后，漏极电压必须保持在输出电压水平。

进入导通过程的第三个阶段，栅极电压 ( $V_{GS,Miller}$ ) 已经足够使漏极电流全部通过，而且整流二极管处于完全截止状态。现在允许漏极电压下降。在器件漏极电压下降过程中，栅源电压保持不变。这就是栅极电压波形的 Miller 平坦区。从驱动得到的可用的所有栅极电流通过电容  $C_{GD}$  放电，这将加快漏源电压变化。而漏极电流几乎不变，这是由于此刻它受外部电路（即直流电流源）限制。

最后一个阶段 MOSFET 沟道增强，处于完全导通状态，这得益于栅极的电压已经足够高。最终的  $V_{GS}$  电压幅度将决定器件最终导通阻抗。因此，在第四个阶段，电压  $V_{GS}$  从 Miller 平坦区增大到其最大值  $V_{DRV}$ 。这由于电容  $C_{GS}$  和  $C_{GD}$  的充电完成，因此栅极电流被分成这两部分。在这两个电容充电过程中，漏极电流保持不变，漏源电压也随着导通阻抗的减小而慢慢的减小。

## 关断过程

MOSFET 的关断过程恰好和它的导通过程相反。电压  $V_{GS}$  从图 3 的  $V_{DRV}$  开始，电流从图 3 的最大负载电流  $I_{DC}$  开始。漏源电压由 MOSFET 的电流  $I_{DC}$  和导通阻抗决定。图 5 完整的显示了关断的四个阶段。

Figure 5. MOSFET turn-off time intervals

第一个阶段是关断延迟，这阶段需要电容  $C_{iss}$  从最初值电压放电到 Miller 平坦区水平。这期间栅极电流由电容  $C_{iss}$  提供，而且它流入 MOSFET 的电容  $C_{gs}$  和  $C_{gd}$ 。器件的漏极电压随着过载电压的减小而略微的增大。此阶段漏极电流几乎不变。

在第二个阶段，管子的漏源电压从  $I_{DC} \cdot R_{DS(on)}$  增加到最终值 ( $V_{DS(off)}$ )，由图 3 的原理图可知它是由整流二极管强制决定的。在这一阶段，即相当于栅极电压波形的 Miller 平坦区，栅极电流完全是电容  $C_{gd}$  的充电电流因为栅源电压是不变的。这个电流由电源级的旁路电容提供而且它是从漏极电流减掉的。总的漏极电

流仍然等于负载电流，也就是图 3 直流电源表示的感应电流。

二极管的导通预示着第三个阶段的开始，二极管给负载电流提供另一通路。栅极电压从  $V_{GS,Miller}$  降到  $V_{th}$ 。大部分的栅极电流来自于电容  $C_{GS}$ ，因为事实上电容  $C_{GD}$  在前一个阶段是充满电的。MOSFET 处于线性工作区，而且栅源电压的降低将会导致漏极电流的减小，在这个阶段的最后漏极电流几乎达到 0。与此同时，由于整流二极管的正向偏置漏极电压将维持在  $V_{DS(off)}$ 。

截止过程的最后一个阶段是器件的输入电容完全放电。电压  $V_{GS}$  进一步减小到 0。占栅极电流较大比例部分的电流，和截止过程的第三阶段一样，由电容  $C_{GS}$  提供。器件的漏极电流和漏极电压保持不变。

综合上述结论，可以总结为：在四个阶段（无论是导通还是关断）里，场效应晶体管可在最大阻抗和最小阻抗间变换。四个阶段的时间是寄生电容、所需电压变化、栅极驱动电流的函数。这就突出了在高速、高频开关应用设计中器件选择部分和栅极最适合工作条件的重要性。

MOSFET 典型的开启延迟时间、关断延迟时间、上升沿时间、下降沿时间会在资料表中列出。不幸的是，这些数据适用于特殊的测试条件而对于有阻抗的负载，不同厂家的产品使得比较变得困难。而且，实际开关应用中呈感性的负载的数据和资料表上给的又是有很大差别。

## 功率损耗

MOSFET 在电源应用中作为开关用时将会导致一些不可避免的损耗，这些损耗可以分为两类。

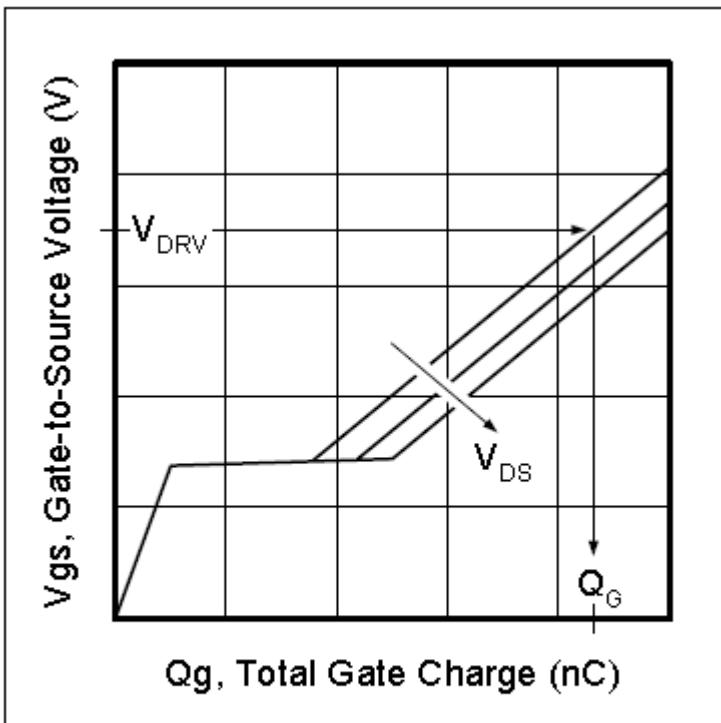

这两类中较为简单的是器件栅极驱动损耗。如前所述，MOSFET 的导通和截止过程包括电容  $C_{iss}$  的充电和放电。当电容上的电压发生变化时，一定量的电荷就会发生转移。需要一定量的电荷使栅极电压在 0 和  $V_{DRV}$  之间变化，这在资料表中的栅极电压----电荷曲线表现出来。图 6 (Figure6) 是一个示例。

Figure 6. Typical gate charge vs. gate-to-source voltage

这个图表曲线给出了一个栅极电荷与栅极驱动电压成函数关系的在最恶劣条件下相对精确的估计。常用来生成这些曲线的参数是器件漏源截止电压。 $V_{DS(off)}$  影响 Miller 电荷（曲线中平坦曲线下面部分），也即，在整个开关周期中所需的总电荷。在图 6 中一旦得到了栅极总电荷，那么栅极电荷损耗就可用下面公式计算：

$$P_{GATE} = V_{DRV} \cdot Q_G \cdot f_{DRV}$$

式中  $V_{DRV}$  是栅极驱动波形的幅度， $f_{DRV}$  是栅极驱动的频率（这个频率通常情况等于开关频率）。值得注意在这个公式中的  $Q_G \cdot f_{DRV}$  项，它给出了驱动栅极所需的平均偏置电流。驱动 MOSFET 的栅极损耗在了栅极的驱动电路上。参看图 4 和图 5，损耗部分可被认为是栅极驱动回路中一系列的电阻的组合。在每个开关循环中，所需要的电荷必须流经输出驱动阻抗、外部栅极电阻和内部栅极网格阻抗。这样的结果是，功率损耗并不取决于电荷流经阻抗元件的快慢。使用图 4 和图 5 的指定电阻，驱动功率损耗可表示为：

$$P_{DRV,ON} = \frac{1}{2} \cdot \frac{R_{HI} \cdot V_{DRV} \cdot Q_G \cdot f_{DRV}}{R_{HI} + R_{GATE} + R_{G,I}}$$

$$P_{DRV,OFF} = \frac{1}{2} \cdot \frac{R_{LO} \cdot V_{DRV} \cdot Q_G \cdot f_{DRV}}{R_{LO} + R_{GATE} + R_{G,I}}$$

$$P_{DRV} = P_{DRV,ON} + P_{DRV,OFF}$$

在上面的方程式中，栅极驱动电路用有阻抗的输出代替，但这个假设对于金属半导体的栅极驱动是无效的。当双极性晶体管在栅极电路驱动中被用到时，输出阻抗变为非线性的，而且公式将得不到正确的结果。为保险起见，假定栅极阻抗很小 ( $<5\Omega$ ) 而且大部分损耗浪费在驱动电路中。假如  $R_{gate}$  足够大，足以使  $I_G$  低于驱动双极型的能力，那么绝大部分的栅极功率损耗浪费在  $R_{gate}$  上。

除了栅极驱动功率损耗外，还有由于大电流和大电压在较短的时间内同时出现造成传统意义上的开关损耗。为了保证开关损耗最小，这个持续的时间间隔必须尽量的小。观察 MOSFET 的导通和截止过程，应该减小开关过程中第 2 和第 3 个阶段的时间（无论是导通过程还是截止过程）。这个间隔是 MOSFET 的线性工作区间，此刻栅极电压介于  $V_{TH}$  和  $V_{GS,Miller}$ 。漏极电压在开关间转换时，将会引起器件电流变化而且到达 Miller 平坦区。

在高速门驱动电路设计中领悟这点是十分重要的。它强调突出这样的事实：门驱动最主要的特性就是它在 Miller 平坦区电压附近的拉电流和灌电流能力。峰值电流能力，是在有输出阻抗时最大电压  $V_{DRV}$  条件下测得的，和 MOSFET 的实际开关性能有很少联系。真正决定器件开关时间的是在栅源电压，也就是，在输出为 5V 的情况下（MOSFET 的逻辑电平是 2.5V）时栅极驱动电流的能力。

MOSFET 的开关损耗的粗略估计可使用在开关期间第 2 和第 3 个阶段关于门驱动电流、漏极驱动电流、漏极驱动电压的简单线性近似。首先必须确定门驱动电流，分别为第 2 和第三阶段作准备：

$$I_{G2} = \frac{V_{DRV} - 0.5 \cdot (V_{GS,Miller} + V_{TH})}{R_{HI} + R_{GATE} + R_{GI}}$$

$$I_{G3} = \frac{V_{DRV} - V_{GS,Miller}}{R_{HI} + R_{GATE} + R_{GI}}$$

假设  $I_{G2}$  为器件的输入电容充电电流，在电压从  $V_{TH}$  变到  $V_{GS,Miller}$ ;  $I_{G3}$  是电容  $C_{RSS}$  的放电电流，在漏极电压从  $V_{DS(off)}$  变到 0 时，大致的开关时间为：

$$t2 = C_{ISS} \cdot \frac{V_{GS,Miller} - V_{TH}}{I_{G2}}$$

$$t3 = C_{RSS} \cdot \frac{V_{DS,off}}{I_{G3}}$$

在  $t2$  时间内，漏极电压是  $V_{DS(off)}$ ，电流从 0 倾斜的变化到负载电流  $I_L$ ，而在  $t3$  时间内漏极电压从  $V_{DS(off)}$  变到 0。再次使用波形的线性近似，各自时间内的功率损耗近似为：

$$P2 = \frac{t2}{T} \cdot V_{DS,off} \cdot \frac{I_L}{2}$$

$$P3 = \frac{t3}{T} \cdot \frac{V_{DS,off}}{2} \cdot I_L$$

式中的  $T$  是开关周期。总的开关损耗是两部分的和，由此可得出下列表达式：

$$P_{SW} = \frac{V_{DS(off)} \cdot I_L}{2} \cdot \frac{t2 + t3}{T}$$

即使较好的理解了开关的过程，但是要精确的计算开关损耗几乎是不可能的。原因是寄生感性分量将会显著的影响电流和电压波形，也会影响开关过程的开关时间。考虑到实际电路中不同的漏极和源极感应的影响，将会导出一个二阶微分方程来描述电路中的实际波形。由于那些变量，包括开启电压、MOSFET 电容值、驱动输出部分等等，有很大的误差，上述的线性近似对于 MOSFET 开关损耗的估算是否可行的，是比较合理的。

## 寄生部分的影响

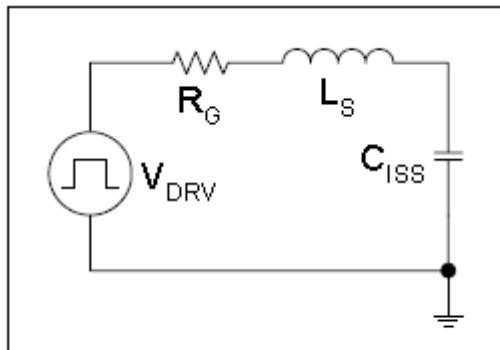

对开关性能最有深远的影响是源极电感系数。在一个典型的电路中，寄生电感有两个来源，一是 MOSFET 封装时的封装接线；二是在源极端和共地端的印刷电路板线的电感。当高频滤波电容的负极和门驱动的旁路电容在功率级时通常要考虑这些。在源极的一系列电流检测电阻也会对前两部分电路增加额外的电感。

开关过程中有两个机制，这包括源极电感。在开关转换的开始，栅极电流慢慢增大（由图 4 和图 5 可得知）。这个电流必须流经源极电感，而且会变慢，这取决于电感值。因此，MOSFET 的输入电容的充放电时间将会变长，这主要会影响导通延迟和截止延迟（第一阶段）。此外，源极电感和电容  $C_{iss}$  组成共振电路，如图 7 所示。

Figure 7. Gate drive resonant circuit components

震荡电路随着门驱动电压波形的陡峭边沿而消失，而且他是门驱动电路中导致可观察到的毛刺波形的基本原因。幸运的是，源极电感和电容  $C_{iss}$  之间较大的 Q 值将会使震荡衰减，另外，回路中的一系列的电阻（包括输出驱动部分、外部栅极电阻、内部栅极网格电阻）也会使震荡衰减。使用者唯一可以调节的电阻， $R_{GATE}$  可以为达到最佳状态而计算出来：

$$R_{GATE,OPT} = 2 \cdot \sqrt{\frac{L_s}{C_{iss}}} - (R_{DRV} + R_{G,I})$$

小一点的阻值电阻将会导致门驱动电压波形的一个毛刺，但也会加快开启速度。大点阻值的电阻对震荡不会衰减而且会加大开关时间，这对门驱动设计没有任何的帮助。

源极电感的第二个影响是器件漏极电流迅速变化时的一个负反馈。这个影响在导通过程的第 2 个阶段和截止过程的第 3 个阶段会出现。在这些阶段中，门电压介于  $V_{TH}$  和  $V_{GS,Miller}$  之间，而门电流由驱动部分电压决定 ( $V_{DRV} \sim V_{GS}$ )。为了使漏极电流增加的快些，源极电感上必须加上必要的电压。这个电压减少了可用的驱动电压，这将会降低漏极电流变化率。较低的漏极电流变化率使得源极电感需要的电压变小。由此会建立一个由源极电感负反馈导致的栅极电流和漏极电流变化率之间的微妙的平衡。

在开关网络中的另外一个寄生电感是漏极电感，它也由几部分组成。它们是封装电感、所有的互联电感、在孤立电源中变压器的漏电感。它们的影响可以合并到一块，因为他们之间是相互连接的。它们在 MOSFET 中作为导通阻尼器。在导通期间，它们限制漏极电流变化而且通过公式  $L_D \cdot di/dt$  来减小器件上漏源极电压。事实上， $L_D$  可以减小导通时的开关损耗。虽然较大的  $L_D$  对导通过程有用，但是会在截止时（当漏极电流必须快速下降时）产生相当大的问题。为了使截止时漏极电流能迅速减小，关于导通时的一个反方向电压必须加到电感  $L_D$  上。这个电压比  $V_{DS(off)}$  要高，这将会引起漏源电压的一个毛刺，而且会增加截止开关损耗。

精确的关于完整开关过程机制的分析包括寄生电感的影响可见相应文献，但这些点超出了本篇论文的范围。

## 接地门电路驱动

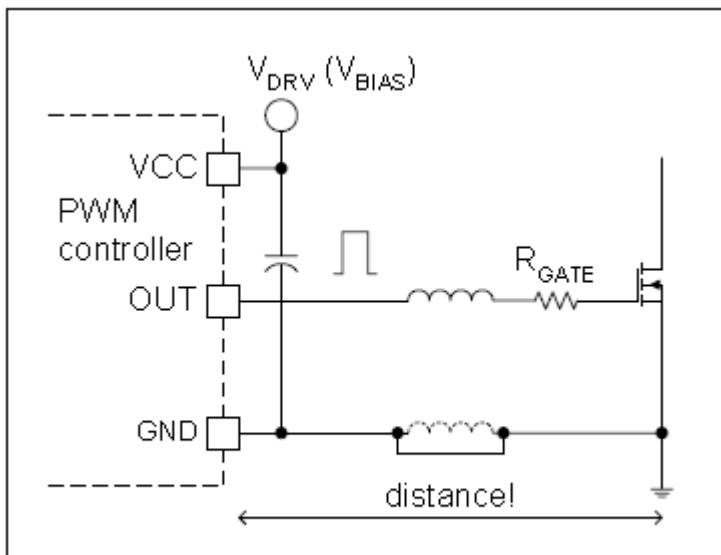

### PWM 直接驱动

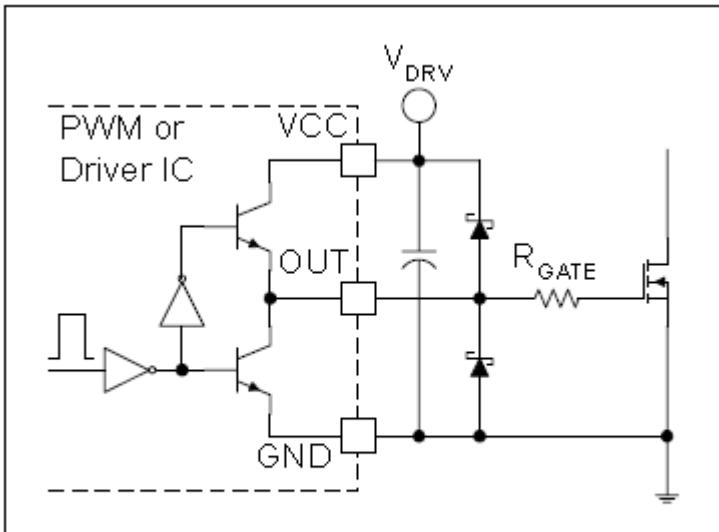

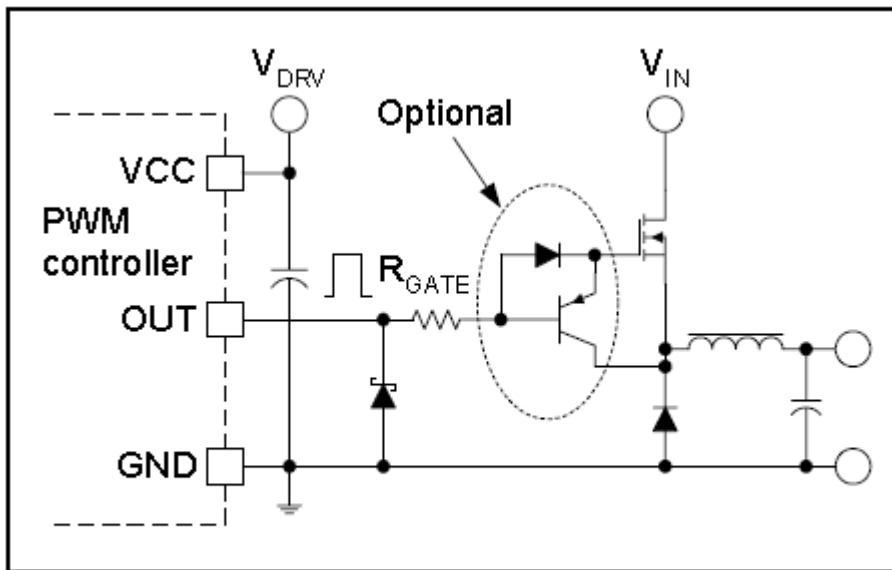

在电源供给应用中，驱动门开关晶体管最简单的方法就是利用 PWM 控制器，如图 8 所示。

Figure 8. Direct gate drive circuit

在直接驱动中最困难的是如何使电路布线最优化。如图 8 所示，在 PWM 和 MOSFET 间有相当大的距离。这段距离会引起由门驱动和地之间回路造成的寄生电感，这将会降低开关速度和引起在 MOSFET 驱动波形中的噪声。即使使用地线层，寄生电感也不能被消除，因为地线层仅比地回路的寄生电感小些而已。为了减小门驱动连线的寄生电感，一个比较宽的 PCB 布线是必须的。直接驱动的另一个问题是 PWM 控制器的电流驱动能力。这将限制由 PWM 控制器驱动的在最佳工作状态的芯片的最大尺寸。使用 PWM 直接驱动 MOSFET 的另一个限制因素是驱动器内部的功率损耗。如前所讨论的，一个外接栅极电阻可以解决这个问题。当直接驱动电路需要考虑空间限制或者成本限制时，这就需要对控制器的布线进行仔细的考虑和分析。驱动 MOSFET 的电流过高可能会破坏 PWM 内部敏感的模拟电路。随着 MOSFET 的尺寸的变大，对应的栅极驱动电荷也会增加。旁路电容的选择也需要比原来的选择 0.1uF 或 1uF 的旁路电容更加科学的方法。

## 旁路电容的选择

在这一章将要分析论证 MOSFET 旁路电容的选择。这个电容和直接驱动应用电路中的 PWM 控制器的旁路电容一样，因为在导通时它提供栅极驱动电流。假如在一个孤立的驱动电路中，无论是一个 IC 还是孤立的元件的门驱动，这个电容必须放得很近，直接接在偏置端和地线间更好。

这里有两部分电流需要考虑。一个是静态电流（即无信号输入电流），它可能变化 10 倍多，在一些集成电路的输入状态下。它本身就会在旁路电容上产生一些纹波，计算公式为：

$$\Delta V_Q = \frac{I_{Q,HI} \cdot D_{MAX}}{C_{DRV} \cdot f_{DRV}}$$

这是假设静态电流在比较大的情况下得到的。

另一个波动成分是栅极电流。尽管大多数情况下不知道实际电流振幅，但是由栅极电荷量可得知旁路电容产生的电压纹波值。在导通期间，旁路电容放电给栅极提供电荷，而且最后转移到 MOSFET 的输入电容上。因此有纹波如下公式：

$$\Delta V_{QG} = \frac{Q_G}{C_{DRV}}$$

使用叠加原理和这些公式，旁路电容  $C_{DRV}$  在允许范围内的电容值的公式为：

$$C_{DRV} = \frac{I_{Q,HI} \cdot \frac{D_{MAX}}{f_{DRV}} + Q_G}{\Delta V}$$

式中  $I_{Q,HI}$  是最大静态电流， $D_{MAX}$  是最大占空比， $f_{DRV}$  是工作频率， $Q_G$  是栅极总电荷，这些是建立在门驱动电压幅值和漏源电压为 0 的状态下。

## 驱动保护

在使用双极型晶体管作为输出级和直接驱动的另一个需要做的事情是为双极型晶体管的输出提供适当的保护，这主要是针对反向电流的。如图 9 简化图解，集成电路的输出级是使用 npn 晶体管，这是由于他们的高效区和比较好的性能。

*Figure 9. Gate drive with integrated bipolar transistors*

图中的每个 npn 晶体管只能控制一个电流方向。上面那个可以控制拉电流但不能控制灌电流，下面那个恰好相反。在 MOSFET 的导通和截止时源极电感和 MOSFET 的输入电容之间不可避免的波动迫使电流输出时要向两个方向流动。为了给反向电流提供一个回路，就需要一个正向导通压降低的肖特基二极管来保护输出电路。这个二极管必须与输出端和驱动的旁路电容端放的很近。有必要指出，二极管仅保护驱动电路，对控制栅源电压噪声无效，尤其是直接驱动中芯片和 MOSFET 的栅源终端离得比较远的情况。

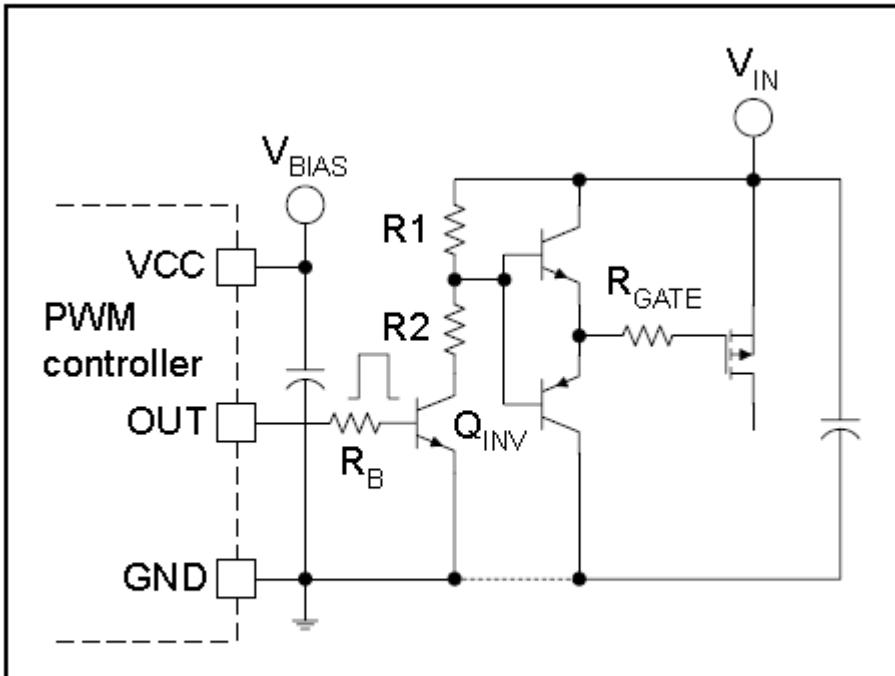

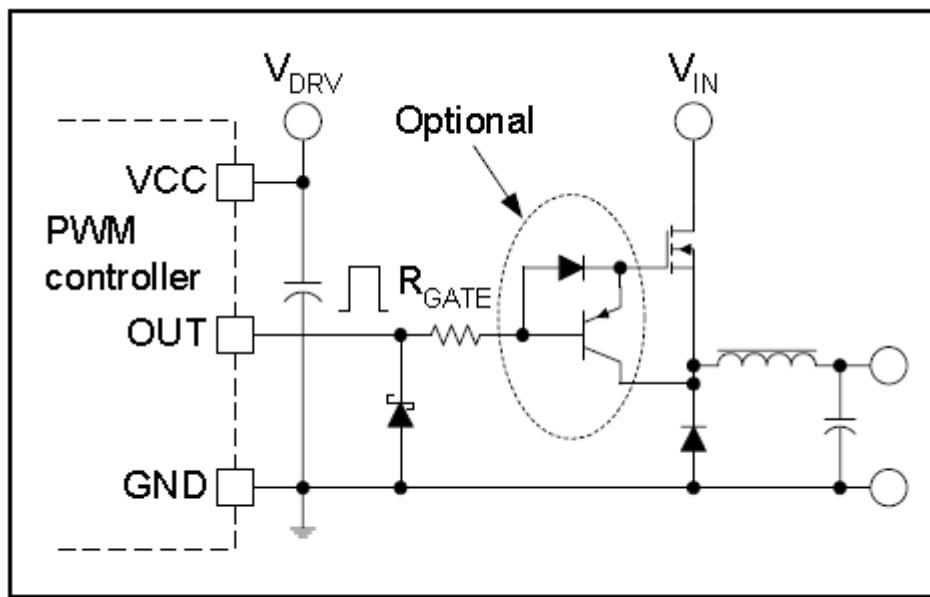

## 双极型晶体管推拉式驱动

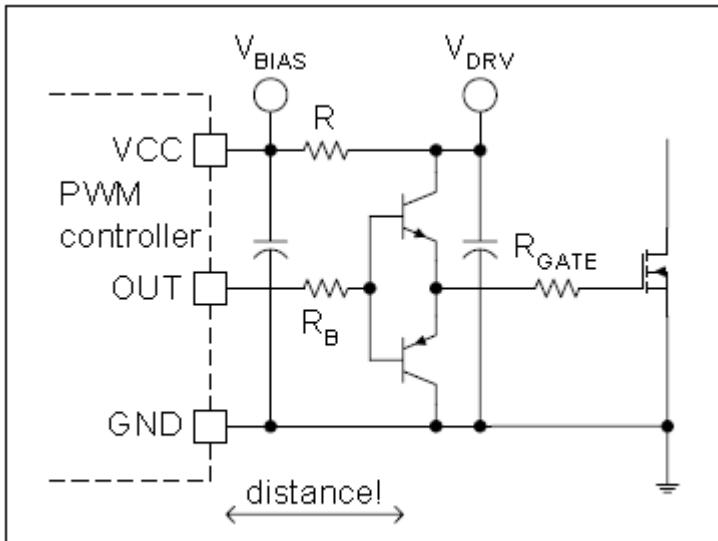

MOSFET 驱动最流行的和最划算的就是晶体管同相的推拉式驱动，如图 10.

Figure 10. Bipolar totem-pole MOSFET driver

像所有的外部驱动一样，这种电路对控制电流毛刺、功率损耗有效，这对 PWM 控制更有利。当然，它们可以而且应该紧挨所驱动的功率 MOSFET 放置。这样使得驱动栅极的电流变化在一个小的范围内，减小了寄生电感的值。即使驱动由分立元件组成，也需要把旁路电容放置在上部 npn 管子和下部 pnp 管子之间。理想情况下，在驱动的旁路电容和 PWM 控制器的旁路电容之间可以放置一个滤波电阻或电感，这可增加电路抗干扰能力。图 10 中 RGATE 是可选的，RB 可以由驱动晶体管的放大倍数而计算得来，以此来提供所需的栅极阻抗。

推拉式三极管驱动有个有趣的性能，那就是两个基射结可以相互保护，防止反向击穿。此外，假设回路区域比较小，RGATE 可以被忽略，那么使用基射三极管就可以把栅极电压锁定在  $V_{BIAS}+V_{BE}$  和  $GND-V_{BE}$  之间。这种解决方案的另一个好处是：在同样的锁定机制下，npn-pnp 推拉式驱动不需要任何肖特基二极管保护来防止反向电流。

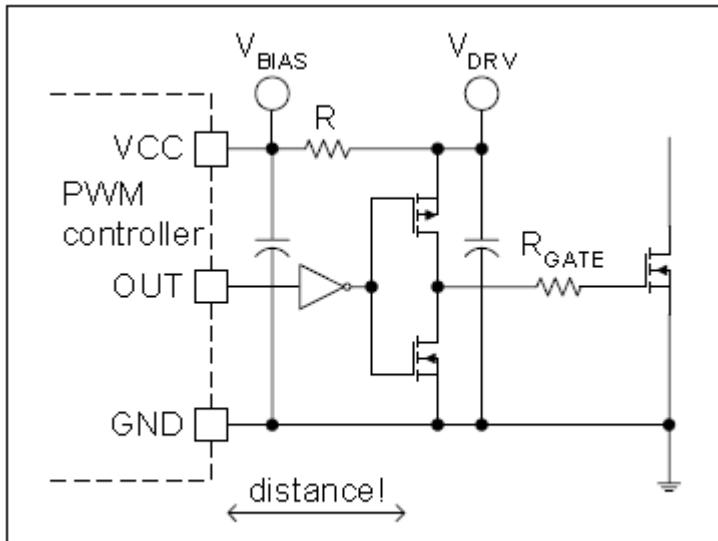

## MOSFET 推拉式驱动

使用 MOSFET 电路和使用晶体管是等价的，如图 11 所示。

Figure 11. MOSFET based totem-pole driver

不幸的是，这个电路和晶体管推拉式电路相比有一些缺点，这就解释了为什么它很少被分散的使用。图 11 所示为一个反向驱动，因此 PWM 控制器的信号也必须反向一下。此外，合适的 MOSFET 要比晶体管贵很多，而且当他们的栅极电压在转变时会有很大的电流流过它们。这个问题可以通过增加额外的逻辑或者定时电路来避免，这些技术在 IC 中被广泛的使用。

## 提速电路

当提到提速电路，设计者唯一的能想到的电路就是加快 MOSFET 关断过程的电路。原因是导通速度通常受关断速度限制，或者说是受电源中整流器部分反向恢复速度限制。在图 3 的电感箝紧模型的讨论中，MOSFET 的导通和整流二极管的截止是相符合的。因此，快速的开关决定于二极管的反向恢复特性，而不是驱动电路的能力。在一个最优的设计中，栅极导通的驱动速度和二极管开关特性相符的。另外，考虑 Miller 平坦区是更加靠近 GND 而不是栅极最终驱动电压  $V_{DRV}$ ，输出阻抗和栅极阻抗上可以得到一个更高的电压。通常情况下所获得的导通速度足够来驱动 MOSFET 了。

在关断上情况就大大的不一样了。理论上，MOSFET 的关断速度仅仅依赖于栅极驱动电路。一个关断时电流比较大的电路能够使输入电容放电更快些，提供更短的截止时间和更小的截止损耗。大的放电电流可以通过低输出阻抗的

MOSFET 或者一个 n 沟道负的截止电压的器件来实现。虽然较快的开关速度可以降低开关损耗，但是加速电路会增加波形的噪声，这是由 MOSFET 关断时较大的电压变化率和电流变化率引起。这在选择合适的额定电压和电磁干扰防范上需要考虑的。

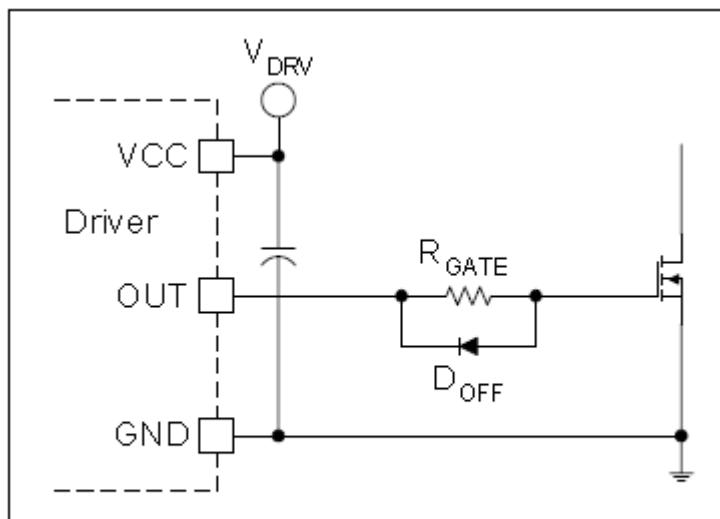

## 截止二极管

下述的关于截止二极管电路的例子是在简单的以地位参考的栅极驱动电路中论证的，但也适用于论文后面的电路。最简单的是反向并联二极管技术，如图 12 所示。

Figure 12. Simple turn-off speed enhancement circuit

在这个电路中，RGATE 可以调节 MOSFET 的开启速度。在关断期间，反向二极管分流。仅当栅极电流高于下式值时，

$$I_G > \frac{V_{D,FWD}}{R_{GATE}}$$

D<sub>OFF</sub>开始工作。1N4148 的典型值约为 150mA，BAS40，反向肖特基二极管的为 300mA 左右。因此，当栅源电压接近 0 时，二极管的作用越来越小。最终结果是，这个电路会显著的减小截止时间的延迟，但仅是在开关时间和 dv/dt 能力上有所帮

助而已。另一个缺点是栅极关断电流仍然必须流经驱动的输出阻抗。

## Pnp 关断电路

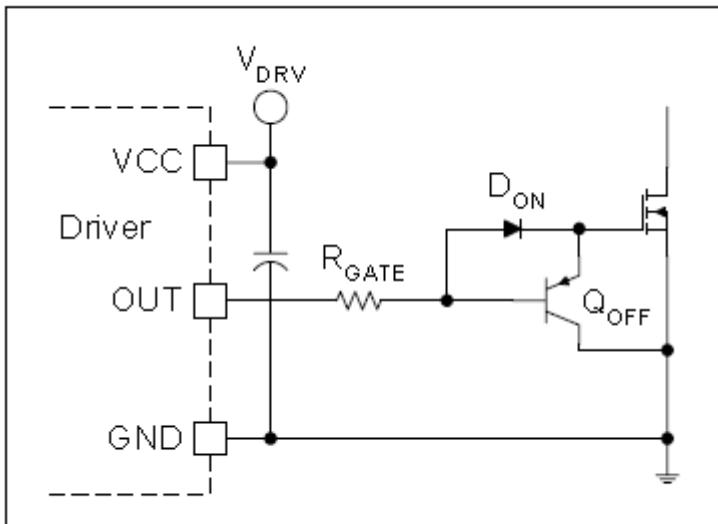

毋庸置疑的，快速关断电路中最流行的设置就是使用局部 pnp 关断电路，如图 13 所示。

Figure 13. Local pnp turn-off circuit

在  $Q_{OFF}$  的帮助下，MOSFET 关断时栅极和源极局部短路。 $R_{GATE}$  限制开关速度，而  $D_{ON}$  为导通电流提供回路。另外， $D_{ON}$  在开始导通时还为三极管  $Q_{OFF}$  的基射结提供保护，防止被反向击穿。

这个方案最大的好处是 MOSFET 输入电容的放电峰值电流被限制在最小的可能的回路（两个晶体管的栅源连接和集射连接）中。关断电流不再流入驱动器中，它不会再引起接地反弹问题，而且驱动的功率损耗也会减小 1/2。关断三极管的分流包括栅极驱动环形电感、电流采样电阻、和驱动输出阻抗。此外， $Q_{OFF}$  从不饱和，这对迅速的开关是十分的重要的。仔细观察电路，可发现这个解决方案是一个简单的推拉式驱动，其中上拉 npn 晶体管被一个二极管代替。和推拉式驱动相似，MOSFET 栅极电压被关断电路近似的锁定在  $V_{DRV}+0.7$  和  $GND-0.7$  之间，消除了栅极多余电压的危险。电路的唯一的缺点是由于  $Q_{OFF}$  的结压降使得

栅极电压不能达到 0。

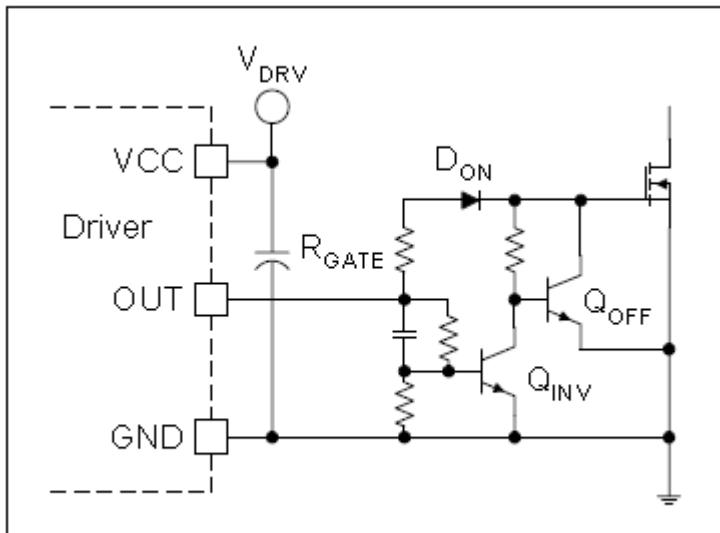

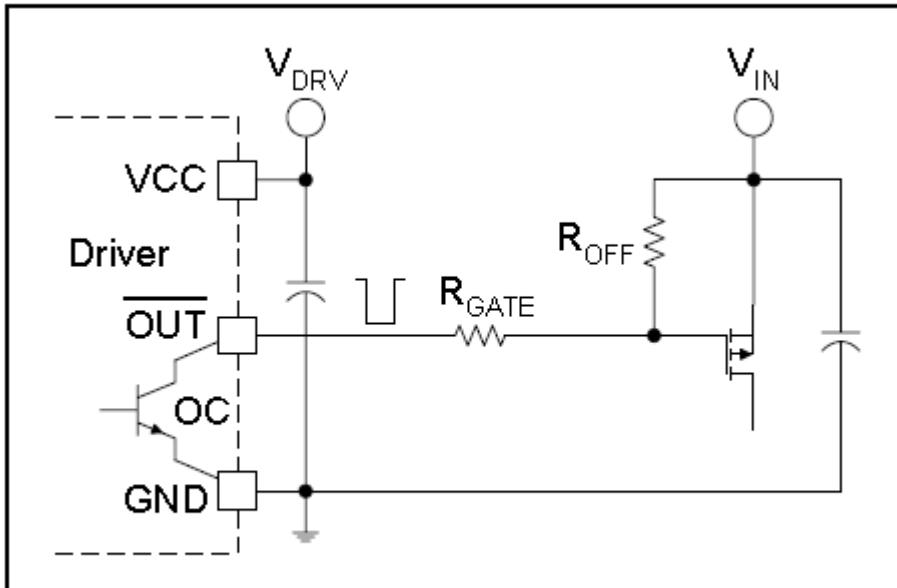

## Npn 关断电路

要分析的下一个电路是 npn 局部关断电路，如图 14 所示。

Figure 14. Local npn selfbiasing turn-off circuit

和 pnp 方案类似，栅极放电电流也是被限制在局部的。Npn 晶体管比 pnp 晶体管更靠近地端。而且，这样放置可以提供一个自给偏压使在加电时 MOSFET 仍为截止的。

不幸的是，这种电路有一些重大的缺点。Npn 关断晶体管  $Q_{OFF}$  是反向状态，这就需要通过  $Q_{INV}$  来提供一个反向的 PWM 信号。在 MOSFET 导通时，反相器从驱动中分走一部分电流，这降低了电路的效率。此外， $Q_{INV}$  的饱和在门驱动时将会使关断延迟变大。

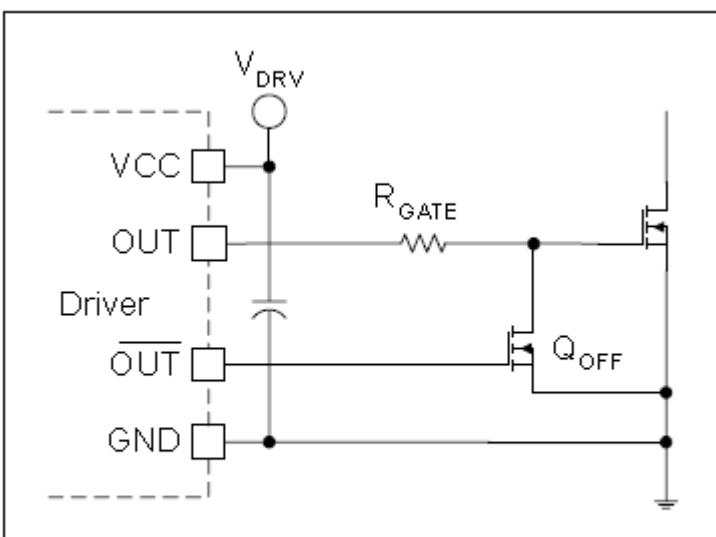

## Nmos 关断电路

这是一个改进，遵循较少元件原则，如图 15 所示，使用一个双驱动为一个小的 n 沟道晶体管提供 PWM 信号。

Figure 15. Improved N-channel MOS based turn-off circuit

这个电路的开关速度很快，而且可以使栅极电压降到0V。和前面一样  $R_{GATE}$  可以开关的速度，但它也用来防止在两个驱动之间毛刺电流的产生。另一个需要考虑的事实是  $Q_{OFF}$  的电容  $C_{oss}$  和功率 MOSFET 的电容  $C_{iss}$  相并联。这将增加驱动所提供的栅极总电荷量。还要考虑，主 MOSFET 的栅极在智能 IC 驱动加电时是不固定的。

## dv/dt 保护

这里有两种保护 MOSFET 防止  $dv/dt$  触发导通的情况。一是在加电过程中，器件栅极和源极端的电阻通常可以提供这种保护。在加电时，下拉电阻的值是在  $dv/dt$  最糟糕的情况下来的，公式如下：

$$R_{GS} < \frac{V_{TH}}{C_{GD}} \cdot \left( \frac{dt}{dv} \right)_{TURN-OFF}$$

在这个公式中，最大的挑战就是找到加电过程中出现大的最大的  $dv/dt$ ，然后对此进行保护。

第二种情况是在正常工作时，当漏源端时截止而  $dv/dt$  强制加到这两端。这种情况比最初预料的更普遍。所有的同步整流开关都工作在这种模式，这随后将

会讨论。大多数软启动开关转换器都能够在主开关刚截止后把  $dv/dt$  强制加到它们上，由电源震荡部分所驱动。由于这些  $dv/dt$  在加电时相当大，而且开启电压  $V_{TH}$  由于结工作温度比较高而更低，因此必须由门驱动电路的输出阻抗提供相应保护。

第一个任务就是确定在最糟糕情况下  $dv/dt$  的最大值。下一步就是在估计一个特定器件的合适性时计算它的正常  $dv/dt$  范围，这由 MOSFET 内部栅极阻抗和电容  $C_{GD}$  决定。假定在理想情况即外部驱动阻抗为 0 时，器件自身  $dv/dt$  限制为：

$$\frac{dv}{dt}_{LIMIT} = \frac{V_{TH} - 0.007 \cdot (T_J - 25)}{R_{G,I} \cdot C_{GD}}$$

式中  $V_{TH}$  是在  $25^{\circ}\text{C}$  时的开启电压，-0.007 是  $V_{TH}$  的温度系数， $R_{G,I}$  是栅极内部网格阻抗， $C_{GD}$  是栅源电容。假如 MOSFET 的自身  $dv/dt$  比共振电路的  $dv/dt$  低，或者另一个不同的管子或者一个负的栅极偏压，那么久必须考虑这些了。假如结果对器件是有利的，那么最大栅极阻抗可以重新计算，而且由下式可以解出这个方程式：

$$R_{MAX} = \frac{V_{TH} - 0.007 \cdot (T_J - 25)}{C_{GD}} \cdot \left( \frac{dt}{dv} \right)_{MAX}$$

where  $R_{MAX} = R_{LO} + R_{GATE} + R_{G,I}$ .

一旦给出最大下拉电阻值，那么栅极驱动设计就可以进行了。还应该考虑到驱动的下拉电阻的阻抗也是和温度有关的。在较高的温度下，用 IC 电路驱动的 MOSFET 表现出比在通常  $25^{\circ}\text{C}$  情况下更大输出阻抗。

关断加速电路同样也可以用于 MOSFET 的  $dv/dt$  抑制上，因为在关断时可以和  $R_{GATE}$  分流，在器件截止状态也可以。例如，图 13 中简单的 pnp 关断电路，就可以增大 MOSFET 最大  $dv/dt$  值。由于晶体管的放大倍数的作用等式增加的  $dv/dt$  值为：

$$\frac{dv}{dt} = \frac{V_{TH} - 0.007 \cdot (T_J - 25)}{\left( R_{G,I} + \frac{R_{GATE} + R_{LO}}{\beta} \right) \cdot C_{GD}}$$

在  $dv/dt$  的计算中, MOSFET 内部栅极阻抗在任何资料表中都没有明确给出。如前所指出的, 这个阻抗由栅极用于分配电流的材料、芯片大小、和芯片内部半导体的设计决定。

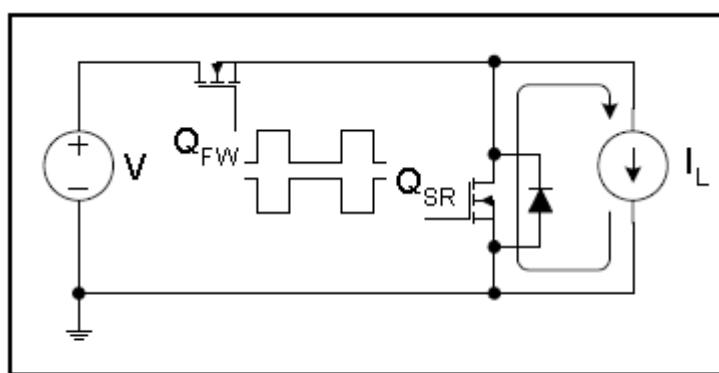

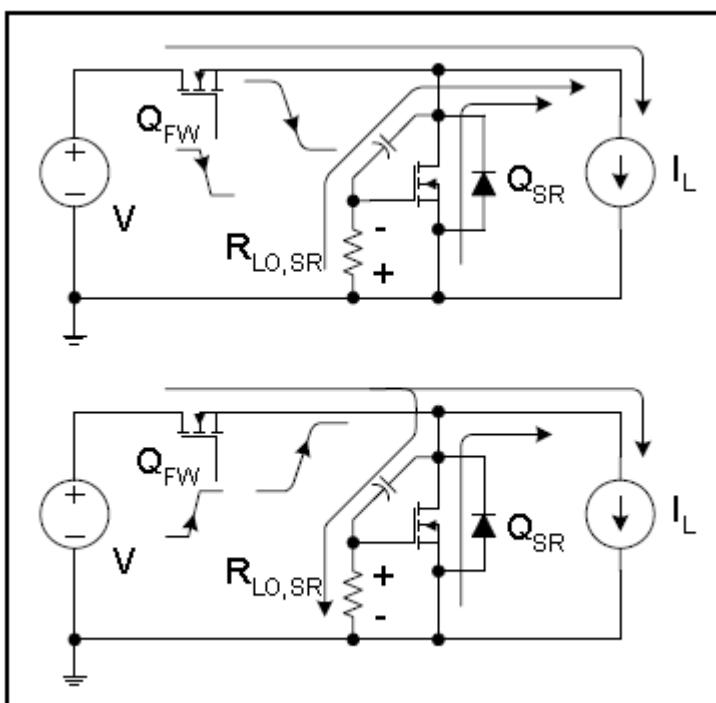

## 同步整流器驱动

MOSFET 同步整流器是以地位参考开关的一个特例。这些器件是在传统应用中完全一样的 N 沟道 MOSFET, 但是是应用于低电压输出电源中而不是用在整流二极管中。它们通常工作在限制十分严格的漏源电压范围内, 因此, 它们的电容  $C_{GS}$  和  $C_{DS}$  表现出很大的电容值。此外, 它们的应用是独特的, 因为他们工作在他们 V-I 波形的第四象限。电流由源极流向漏极。这使得栅极驱动信号仿佛是不相干的。假定这种情况, 同步开关锁需的各个器件都有, 电流将会流过这些器件, 或者流过有阻抗的沟道, 或者是流经 MOSFET 的寄生二极管。检验 MOSFET 同步整流开关的最简单模型就是一个简化了的 buck 功率级电路, 其中整流二极管被晶体管  $Q_{SR}$  所代替, 如图 16 所示。

*Figure 16. Simplified synchronous rectification model*

在这个电路中第一个要确认的事是同步整流 MOSFET 的工作决定于电路中的另一个控制开关, 即前置开关  $Q_{FW}$ 。两个门驱动波形不是独立的, 而且它们特定的时间标准必须一致。信号的重叠将会使致命的, 因为这两个 MOSFET 将会使源

极电压短路，而在此回路中没有任何限流元件。理想情况是两个开关同时导通和截止，这可防止 MOSFET Q<sub>SR</sub> 体二极管的导通。不幸的是，避免体二极管导通的机会太小了。若需要精确的、时间自适的开关速度快的，使用传统技术通常是做不到的。因此，在很多情况下，一个简单的周期（从 20ns 到 80ns）体二极管要比同步整流器先导通，后截止。

## 栅极电荷

在体二极管导通期间，器件中建立满载电流，而且漏源电压和体二极管正向导通压降相同。在这些条件下，来使器件导通、截止所需的栅极电荷和传统的在工作区四分之一周期的电荷不一样。当栅极导通时，漏源电压几乎为 0，而且电容 C<sub>GD</sub> 和 C<sub>DG</sub> 已经放电完毕。而且，Miller 效应也不会出现，在漏极和栅极端没有反馈。因此，所需的栅极电荷和使栅源电容、栅漏电容从 0 充电到 V<sub>DRV</sub> 所需的电荷相等。精确的，在 0 到 V<sub>DRV</sub> 的低电压下，电容 C<sub>GD</sub> 的平均值由下式决定：

$$C_{GD,SR} = 2 \cdot C_{RSS,SPEC} \cdot \sqrt{\frac{V_{DS,SPEC}}{0.5 \cdot V_{DRV}}}$$

下式用来计算同步 MOSFET 整流器的总的栅极电荷：

$$Q_{Q,SR} = (C_{GS} + C_{GD,SR}) \cdot V_{DRV}$$

这个值明显的比器件资料表中给出的总电荷值要小。同样的管子、同样的整流电路，如果它工作在它的第一象限工作区，那么它可以更快的开和关。不幸的是，这个优点无法实现，这是由于器件的 R<sub>D(on)</sub> 比较低，而在同步整流器中由于器件尺寸较大而导致的输入电容和输出电容比较大。在功率损耗中里一个重要的点是，我们需要考虑资料表中总的栅极电荷值。尽管栅极在导通期间从驱动上得到的实际电荷量要比资料表中给出的小，但资料表中的值包括了流如输出阻抗的那一部分。在导通前，漏源地电压变化时，由功率级提供的 Miller 电荷必须流经同步 MOSFET 驱动，这就导致了额外的功率损耗。这种现象从图 17 可看到，它也是下节要讨论的 dv/dt 注意事项的一部分。

同步 MOSFET 的截止过程和导通过程遵循相同的原则，因此前面的关于栅极电荷的讨论同样适用。

## dv/dt 注意事项

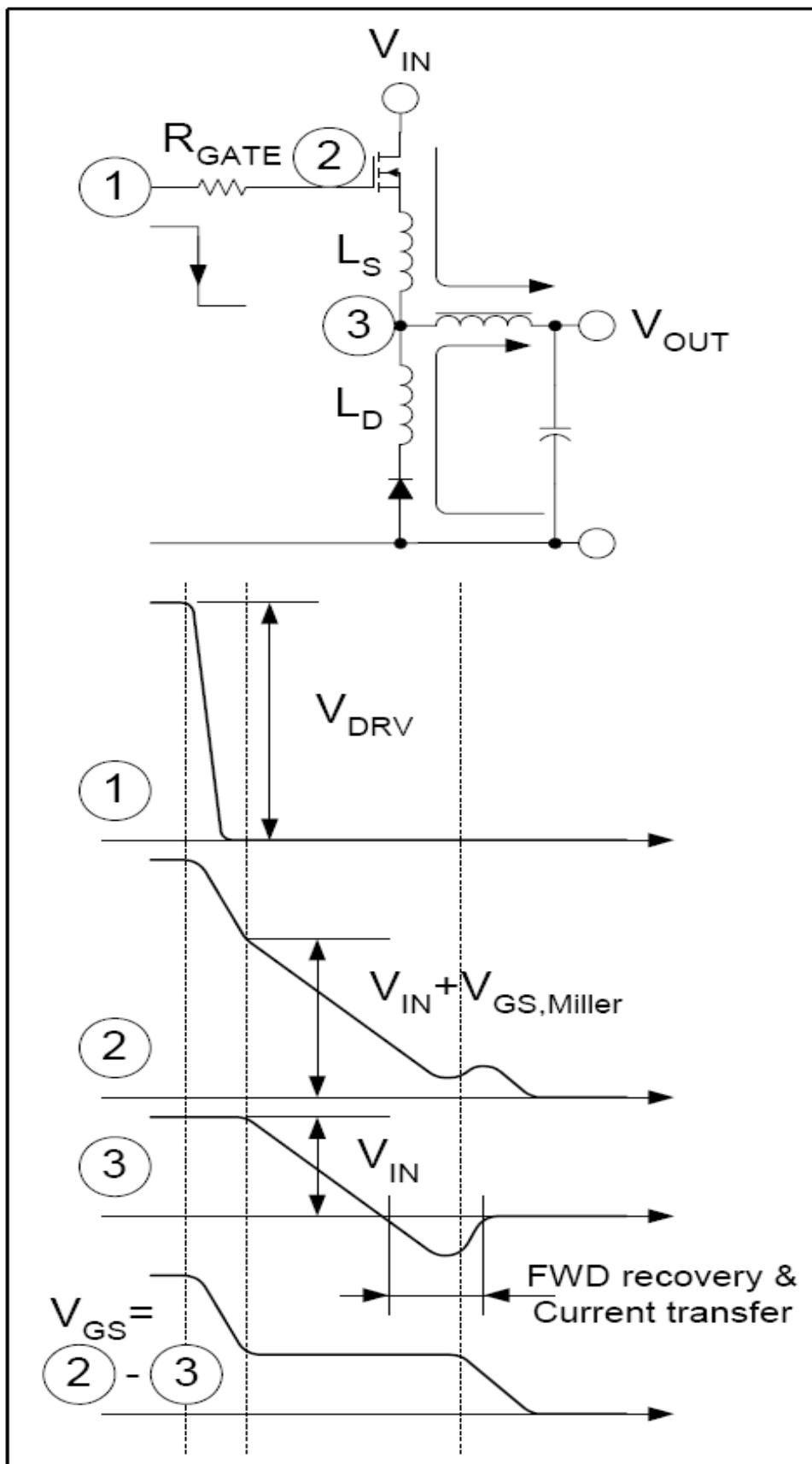

图 17 展示了  $Q_{SR}$  导通和截止时最重要的电路和电流组成。实际上，更精确的说是， $Q_{FW}$  上的开关动作强制使  $Q_{SR}$  导通和截止，而与它本身栅极信号驱动无关。

Figure 17. Synchronous switching model

$Q_{SR}$  的导通开始于  $Q_{FW}$  的截止。当  $Q_{FW}$  的栅极驱动信号从高变到低时，开关点的电压从输入的电压水平变到 GND。电流停留在前级开关，直到电容  $C_{RSS}$  放完电， $Q_{SR}$  的体二极管为正向偏压。在那一瞬间，同步 MOSFET 接收电流， $Q_{FW}$  完全截止。在一个小的延迟后（由控制器的电容控制）， $Q_{SR}$  的栅极信号开始起作用，然后 MOSFET 导通。在那时，电流从体二极管上转移到沟道上。

在  $Q_{SR}$  的导通要结束时，MOSFET 必须截止。这个过程从同步开关的栅极撤掉驱动信号开始。这个事件的本身不会引起器件的截止。与之相反，它会强制使电流流入体二极管而不是沟道。电路的运行并不在乎这个变化。当前级开关电压

从低变到高时，电流开始从  $Q_{SR}$  转移到  $Q_{FW}$  上。一旦  $Q_{FW}$  上得电流达到满载电流，体二极管就完全恢复，开关点电压从 GND 变到输入电压水平。在这个转变过程中， $Q_{SR}$  的电容  $C_{RSS}$  开始充电，而且同步 MOSFET 易受导通时  $dv/dt$  的影响。总结这个 MOSFET 的独特的工作过程和它的栅极驱动，最重要的结论是同步 MOSFET 的导通和截止电压变化强加到器件上，这是由前级开关的特性（也就是开关速度）决定的。因此，两个栅极驱动电路应一同设计，以此来保证在任何工作条件下它们各自的速度和电压变化匹配。遵循下式可保证这一点：

$$\frac{dv}{dt}_{TURN-ON(FW)} = \frac{V_{DRV} - V_{GS,PLATEAU(FW)}}{(R_{HI(FW)} + R_{GATE(FW)} + R_{G,I(FW)}) \cdot C_{RSS(FW)}}$$

$$\frac{dv}{dt}_{MAX(SR)} = \frac{V_{TH(SR)}}{(R_{LO(SR)} + R_{GATE(SR)} + R_{G,I(SR)}) \cdot C_{RSS(SR)}}$$

$$\frac{dv}{dt}_{TURN-ON(FW)} < \frac{dv}{dt}_{MAX(SR)}$$

假设  $Q_{SR}$  和  $Q_{FW}$  的管子一样，没有外接栅极电阻，而且内部栅极阻抗和驱动输出阻抗相比是微不足道的，那么，驱动输出阻抗的比例约为：

$$\frac{R_{LO(SR)}}{R_{HI(FW)}} \leq \frac{V_{TH(SR)}}{V_{DRV} - V_{GS,PLATEAU(FW)}}$$

一个典型的例子，逻辑电平的 MOSFET 被一个 10V 的驱动信号驱动，那么此时的比率为 0.417，这意味着  $Q_{SR}$  的下拉驱动电阻必须低于  $Q_{FW}$  上拉电阻的 42%。当应用这些计算时，在设计中记住每个参数除了电压  $V_{DRV}$  是温度相关的外它们的值必须适应最糟糕的工作条件。

## 高边非隔离栅极驱动

高边非隔离栅极驱动电路可以按所驱动器件类型分类，或者按所包含的驱动电路分类。因此，它们是有差别的，无论是使用的 P 沟道还是 N 沟道的管子或

者是否为直接驱动、电位移驱动、还是自举驱动。无论怎样，高边栅极驱动需要更多注意，下面涵盖了涉及中所有方面的表可能很有帮助：

- 效率

- 偏置/电源电压

- 速度限制

- 最大频宽比限制

- $dv/dt$  影响

- 启动条件

- 瞬态工作情况

- 旁路电容大小

- 布线、接地注意事项

## P 沟道器件的高边驱动

在这组电路中，P 沟道 MOSFET 开关的栅极端和输入正极相连。对于栅极器件，驱动器提供一个低电平导通信号给栅极。这意味着 PWM 控制器的输出必须进行反向而且为正极输入电路提供参考。由于输入电压可看做是一个直流电压源，因此，高边 P 沟道驱动器在开关频率基础上不会来回波动，但是他们必须工作在电压波动范围内。此外，由于栅极的低交流输入阻抗，驱动还得参考 AC 接地电位。

### P 沟道直接驱动

P 沟道高边驱动的最简单的情况就是直接驱动，如果最大输入电压比栅源击穿电压低，那么就可采用此种驱动。一个典型的应用领域就是使用 P 沟道 MOSFET12V 的 DC/DC 转换，和图 18 原理图类似。注意图中反向的 PWM 输出

信号，这在一些专用的 P 沟道驱动控制器中是很容易实现的。

Figure 18. Direct drive for P-channel MOSFET

器件的工作和 N 沟道接地直接驱动相类似。最大的不同就是栅极驱动电流的路径，此种电路中它从不流入地。相反的，栅极比较大的充电和放电电流由正极互连网络导电。以此，为使栅极环形电感最小，正极输入使用比较宽的线或一个层是比较令人满意的。

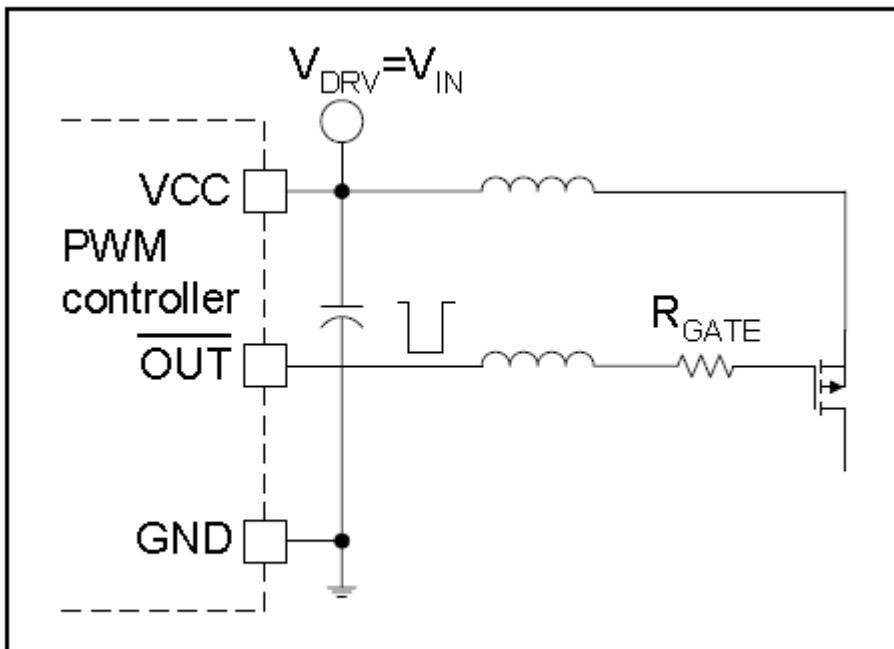

## P 沟道电位移驱动

对于输入电压超过栅源电压范围的管子来说，多电平栅极驱动是必要的。最简单的栅极驱动技术是使用一个集电极开路的驱动，如图 19 所示。不幸的是，集电极开路电位移驱动器在高速应用直接驱动 MOSFET 是不合适的。

*Figure 19. Open collector drive for PMOS device*

在一定的输入电压范围，这样连接会产生许多问题，这是由于集电极开路晶体管的额定电压。但是最大的抑制障碍就是大的驱动阻抗。两个电阻， $R_{OFF}$  和  $R_{GATE}$  的阻抗必须足够高以此来抑制在开关导通时驱动的恒流。此外，栅极驱动幅度取决于分压电阻和输入电压。开关速度和电压变化受到严重限制，这使得这个电路与开关应用无缘。然而，这个简单的位移驱动可以用于涌入电流受限制或不需要考虑速度的开关驱动。

图 20 展示了一个栅极位移驱动电路，它对高速应用是适合的而且使用常见的 PWM 控制器就可顺利的工作。集电极开路位移电路的工作原理在推拉式驱动级中是很简单的。在这个连接电路中电位移器有两个作用，使 PWM 信号反向和给输入提供 PWM 信号参考。

电路的开关速度很快，由  $R_{GATE}$  和  $R_2$  决定的。在开关导通时间，有很小的电流流入电位移器，以此来使驱动在正常偏置下。栅极驱动的能量和位移器的电流都是功率级的正向输入提供，这部分通常是忽略的。

*Figure 20. Level shifted P-channel MOSFET driver*

驱动的能量功耗和频率部分相关（这是建立在主开关栅极电荷上）、和频宽比有关、和输入电压有关（这是由于电流流入位移器）。

$$P_{DRIVE} = Q_G \cdot V_{DRV} \cdot f_{DRV} + \frac{V_{IN} \cdot D_{MAX}}{R1 + R2}$$

这个电路的一个缺点是电压 V<sub>DRV</sub> 是输入电压的函数，这是由于电阻 R<sub>1</sub> 和 R<sub>2</sub> 的分压。在大部分情况下，保护电路是用来阻止栅源端电压过高。另一个困难是 npn 位移器的饱和，这会增加截止时间（除了由 R<sub>1</sub> 和 R<sub>GATE</sub> 决定外）。幸运的是，这两个缺点可以通过把 R<sub>2</sub> 移动到 Q<sub>INV</sub> 的发射极和 GND 之间而解决。最终电路在导通和截止时将会提供恒定的栅极电压和快速的、稳定的开关速度。驱动原理图中的 dv/dt 的抑制主要由电阻 R<sub>1</sub> 设置。一个低的阻抗可以提高防止 dv/dt 触发导通的能力但是这也增大了位移器的功率损耗。同时，注意这个解决方案在加电时有内部自给偏压装置。当 PWM 控制器还未工作时，Q<sub>INV</sub> 是截止的，主 MOSFET 的栅极电压低于开启电压（这由 R<sub>1</sub> 和推拉驱动电路的上一个 npn 晶体管决定）。尤其要注意的是飞速变化的电压变化，因为在 MOSFET 直接的状态下它可能引起 dv/dt 诱发导通。

总之，直流电位移器的效率相当的低，而且在高于一定输入电压时功耗较大。最根本的权衡就是平衡开关速度和位移器的功率损耗，以此来满足在整个输入电压范围内的需要。

## N 沟道器件的高边直接驱动

在大多数的开关电源应用中都是采用 N 沟道 MOSFET 作为主功率开关，这是由于他们的较低的价格低、较快的速度、和较低的导通阻抗。使用 N 沟道器件作为高边开关成为当提到栅极 MOSFET 的栅极驱动的必需。驱动器必需能够承受在开关切换时猛烈的电压波动和能够驱动栅极电压在电源正极电压高的 MOSFET。在大多数情况下，栅极驱动电压必须高于电路中直流电源可能的最高电压。所有的这些困难使得高边驱动成为一个有挑战性的任务。

### N 沟道 MOSFET 高边直接驱动

在最简单的 MOSFET 高边直接驱动应用中，它可以直接由 PWM 控制器驱动或者是一个接地的驱动器。两种情况必须符合下面这个要求：

$$V_{DRV} < V_{GS,MAX}$$

$$V_{IN} < V_{DRV} - V_{GS,Miller}$$

一个典型的应用电路原理图如图 21 所示，使用一个可选择的 pnp 关断电路。

*Figure 21. Direct drive of N-channel MOSFET*

看着电路的基本运行,现在忽略 pnp 晶体管的断开,这个结构与以地为参考的原理图相比有两个主要的差异。因为漏极和直流输入端相连,开关动作发生在器件的源极端。它仍是一样的具有相同开关时间间隔的感应开关,但是从栅极驱动设计的观点看,它是一个完全不同的回路。注意栅极驱动电流不能回到源极的地端,相反,它必须经过负载,与器件的源极相连。在不间断的电感电流模式下,栅极充电电流必须经过输出电感和负载;而在连续电感电流模式下,回路却可以通过控制整流二极管的 pn 结被打断。在断开时候,栅极放电电流通过连接地和 MOSFET 的源极的整流管。在所有的工作模式中,电容  $C_{gd}$  的充放电电流都流过功率级的高频旁路电容。

这些差异的最终结果是由于栅极驱动系统中有了更多的组件和更大的环路区域而造成的更大的源极自感应系数。像前面提到的,源极电感对栅极驱动电路有不良的反馈效果,使电路的开关动作慢了下来。

高边直接去驱动的另外一个显著性差异是电路的开关节点——源极的动作。注意看 MOSFET 截止期间的源极的波形,可以看到一个非常大的负电压。图 22 介 绍 了 这 个 复 杂 的 开 关 行 动 。

Figure 22. Turn-off of high side N-channel MOSFET

由于栅极和地的相连使 MOSFET 截止, MOSFET 的输入电容通过放电很快就被调节到了 Miller 平衡电压。这个器件仍在工作,整个负载电流流过漏极和源极, 电压降很小。其次,在 Miller 区,MOSFET 作为源极的跟随器。

源极和栅极同时下降, 当  $V_{ds}$  增大时,  $V_{gs}$  固定在 Miler 水平。栅极驱动阻抗和器件的  $C_{gd}$  电容限制了  $dv/dt$  的大小。一旦源极电压下降了 0.7V 或者是 -0.7V, 整流二极管使开关节点固定到接近地的位置。

事实上,源极电压会短时间内降到低于地,直到整流二极管经过了它的恢复过程,电流克服了现有的寄生电感效果。在负载电流完全从 MOSFET 转移到二极管后, 开关节点可以回到它的最终的电压状态, 低于地一个二极管的电压。

这种源极电压负漂移表现了一种典型的栅极驱动电路的问题。缓慢的二极管、高寄生电感值会导致对 MOSFET 的源极过多的负反馈电压, 也可以使驱动器的输出端低于地端。为了保护驱动, 低压降肖特基二极管可以连接输出和地端, 像图 21 标示的那样。

*Figure 21. Direct drive of N-channel MOSFET*

另一个要考虑的方面是当栅极电压为 0 时, 栅极的放电电流也会为 0.如果进一步对栅极进行作用, 那么场效应晶体管就开始逆转。最后这个系统会达到一个非常微妙的平衡点, 那就是栅极的放电电流和通过寄生电感的电压降在器件中形成了同样大小的  $di/dt$ 。

当电路处在负电压的时候，即使是图 21 所示的随意的断开提速电路也不能提供有效地帮助。当栅极的电压降到  $V_{BE}$  的时候，pnp 晶体管会处于截止状态，而场效应晶体管会处在负电压暂态中。另外，在主开关处于截止状态的时候要注意容许的噪声的上限。源极电压要低于地几百毫伏，而栅极则保持在大约 0.7 伏。这种和源极有关的通过栅极的电压很危险的接近于阈值电压，尤其对于处于高温的逻辑级设备来说。

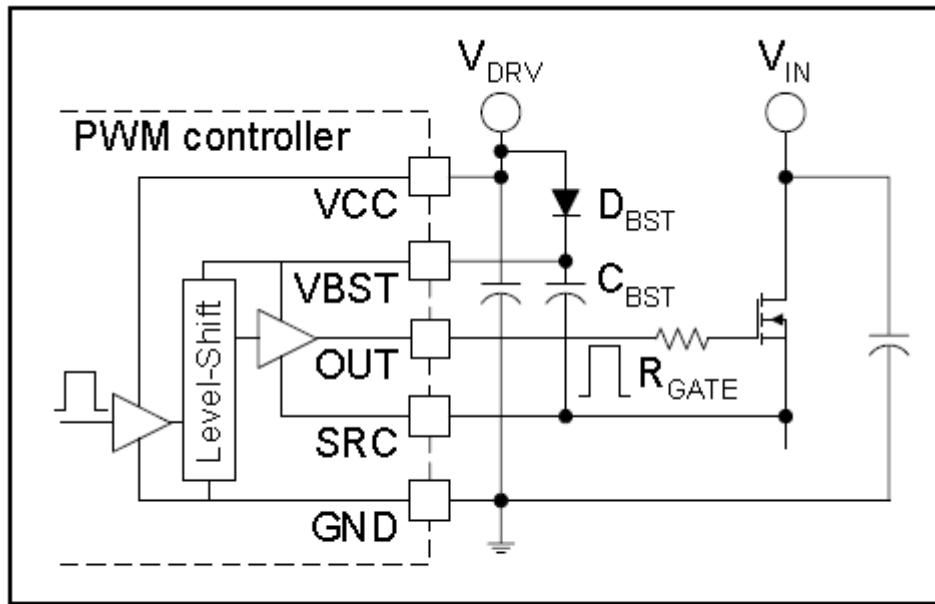

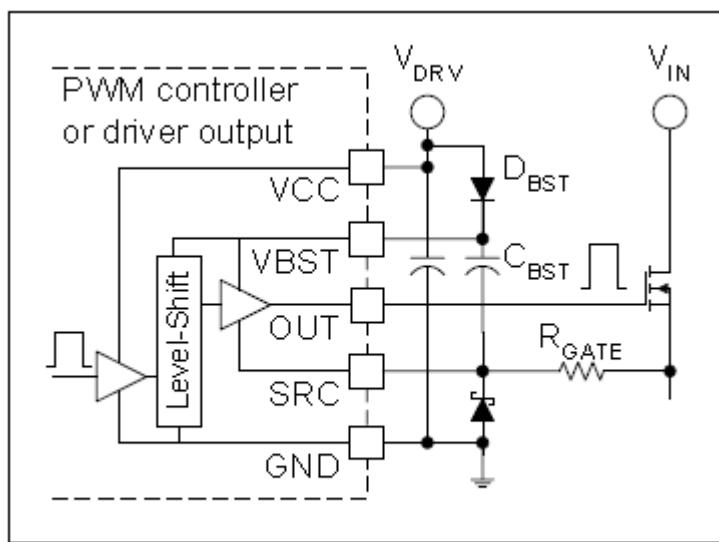

## 自举栅极驱动技术

在输入电压禁止高边 N 沟道场效应晶体管的直接栅极驱动电路使用的地方，可以考虑使用自举栅极驱动技术。这种技术采用了一个栅极驱动和跟随偏置电路，它们以主场效应晶体管的源极为参考。驱动电路和偏置电路以及器件的源极一起在两个输入电压之间波动。但是，驱动器和它的变化的偏差可以被低电压提供，因为输入电压没有在它们上面消耗。驱动器和参考地控制的信号通过一个电位移电路连接了起来，这个电路必须承受高压差以及变动的高边和以地为参考的低边电路之间的可观的电容式开关电流。

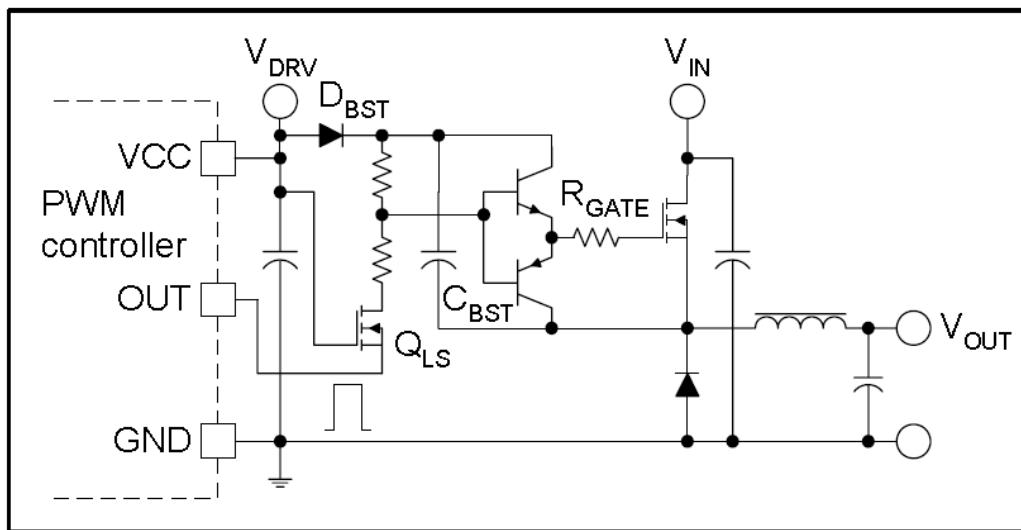

### 离散高性能变动的驱动器

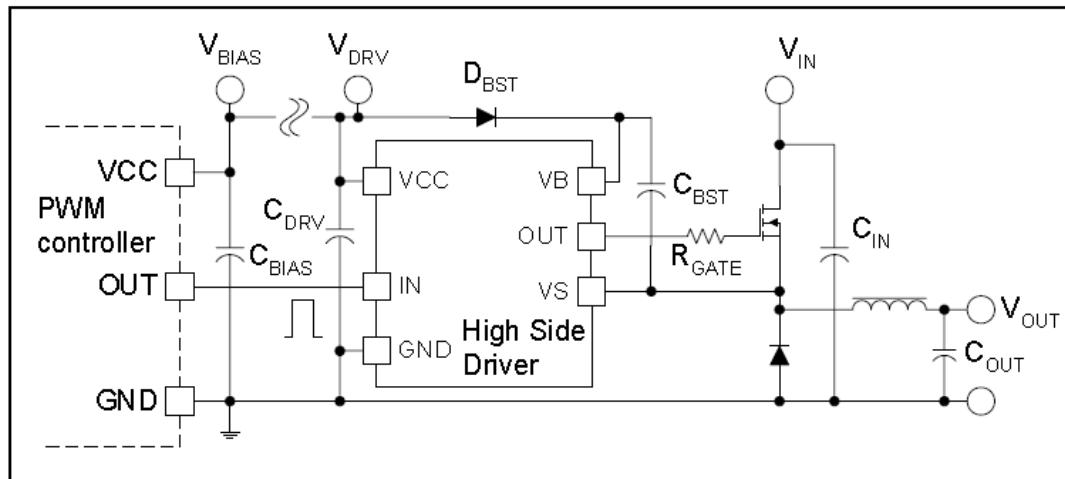

图 23 展示了一个很典型的自举原则的实施实例。

Figure 23. Integrated bootstrap driver

旁路电容和输出引脚可以代表以地为参考的 PWM 控制器和场效应晶体管驱动器。自举栅极驱动电路的基本电路组成很容易看出来。这个变动的电路由自举二极管  $Q_{BST}$ 、 $R_1$ 、 $R_2$  和电位移晶体管  $Q_{LS}$  组成。自举电容  $C_{BST}$ ，一个有两极

的推拉输出电路的驱动器和普通的栅极电阻就是自举解决方案的变动的以源极为参考的部分。这个特殊的器件可以很有效的运用到 12 到大约 24 伏的运用没有变动的驱动的简单的低功耗的 PWM 控制器的系统中。这个是有益的，因为芯片的额定电压不限制输入的电压的大小。另外这个电位移电路是一个在主场效应晶体管导通期间不会从自举电容器得到电流的源极会变动的 NMOS 晶体管。这是一种重要的功能，它可以保持电位移器的高效率性，还可以延长主开关的最大导通时间。这个动作过程可归纳如下:当 PWM 输出升高就会使主 MOSFET 导通，水平位移晶体管截止。R1 将基极电流提供给上面的推拉输出电路驱动的 npn 晶体管，主 MOSFET 就导通了。栅极电荷从自举电容器， $C_{bst}$  获取。当开关接通，它的源极就接通到输入支路上去。自举二极管和限制了向驱动提供电压和能量的晶体管通过自举电容器提供能量。在截止的时候，PWM 降低就使电位移晶体管导通。

电流开始从 R1 和 R2 流向地，下面的推拉输出电路的晶体管开始导通。因为主场效应晶体管的栅极开始放电，漏极到源极的电压开始增大，源极向地过度，允许整流器导通。在主开关闭合期间，自举电容器再次通过自举二极管放电到  $V_{DRV}$  水平。这个电流是由以地为参考的电路的  $C_{DRV}$  旁路电容提供，它穿过了  $D_{bst}$ 、 $C_{bst}$  和整流部分，这就是自举技术的基本运行原理。

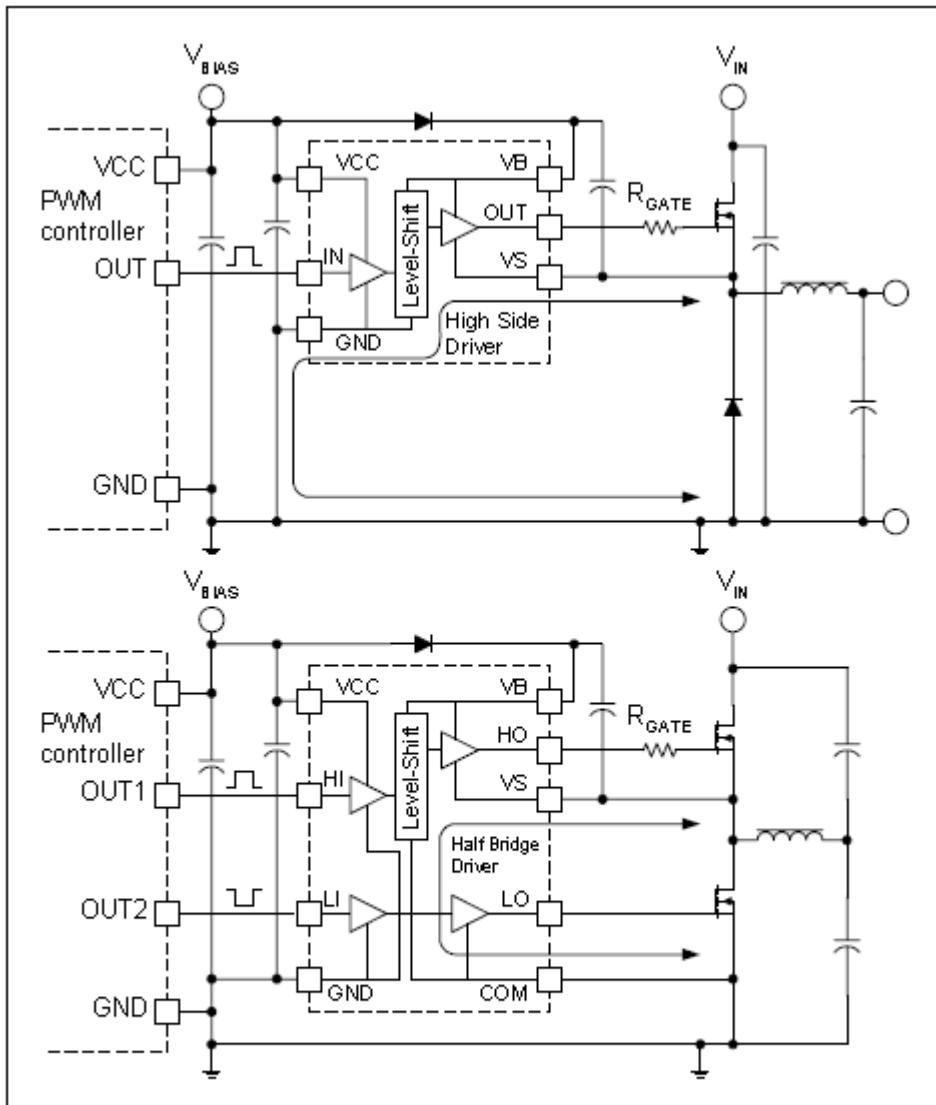

## 集成自举驱动器

在中等输入电压,主要 24V 或 48V 的应用电信系统中,大部分的自举部件可以集成到 PWM 控制器中如图 24 中示意的那样。

*Figure 24. Integrated bootstrap driver*

甚至对于更高的电压来说,专用的驱动集成电路也可以用高达 600V 的电压来使自举栅极驱动的设计变得简单。这些高电压集成电路是由它们独特的电位移设计来区分的,为了维持高效率和可控的能耗,这些电位移器在主开关导通期间不应该分走任何电流,即使 1mA 的电流作用在电位移晶体管上,就有可能在驱动集成电路上消耗 0.5W 的功率。

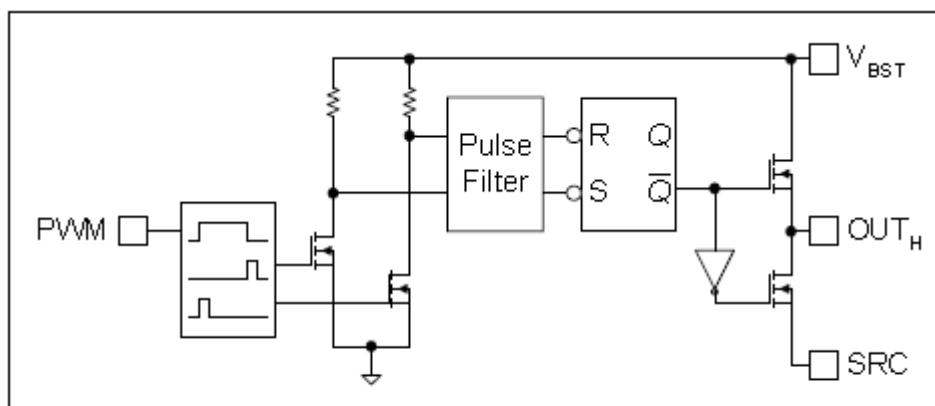

这些应用程序的一种被广泛使用的技术叫做脉冲锁存电平转换器,如图 25 所示的那样。

*Figure 25. Typical level shifter in high voltage driver IC*

如图所示,输入的 PWM 信号被转换成了开关命令。在上升和下降沿产生的

短脉冲驱动了和高边电路连接的电位移晶体管对。因此，驱动器的变动部分也得到改进。电位移控制信号也必须同噪声区别开来，并为适当的功能锁存起来。

这种动作因为在电位移器上的电流持续了很短时间，所以功耗低；但是因为控制信号不能持续保持在驱动器的输入端，导致了较低的抗干扰能力。一个额定 600V 的脉冲锁存电平转换器的典型脉冲宽度是 120 纳秒左右，这个时间间隔使驱动的本来间隔时间增加，表现为动作时开关动作的延迟，这在驱动的数据表中也可以看到。由于高于正常的时间间隔，高电压的栅极驱动集成电路的工作频率范围被限制在几百 KHz 以下。

一些低电压高边驱动器芯片（最高 100V）利用直流电位移电路来消除脉冲鉴频器的延迟，因此它们支持较高的工作频率。

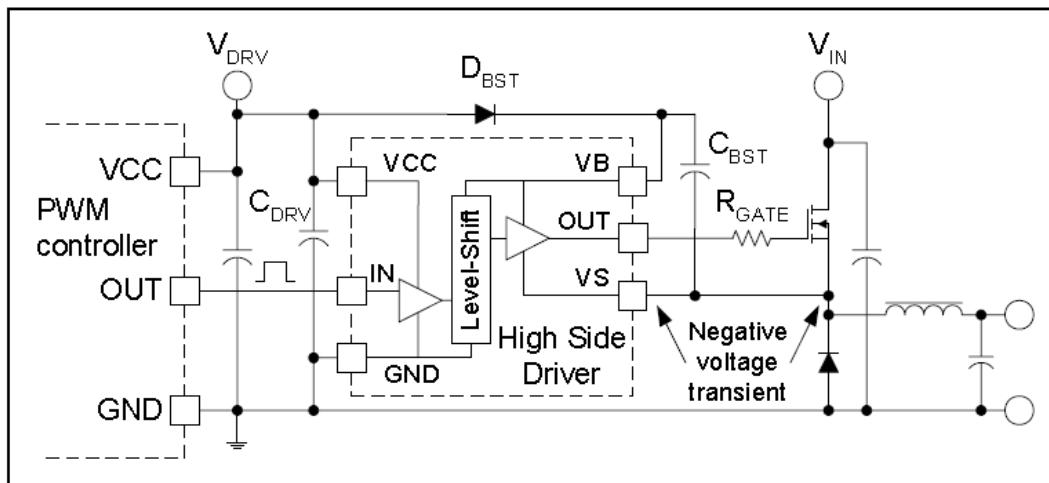

### 自举开关动作

如图 26 所示的是自举栅极驱动电路和高边 N 沟道场效应晶体管一起使用。这个高边开关的开关转换先前跟高边 N 沟道的直接驱动原理图一起探讨，它们同样适用于自举驱动。这个电路最大的困难之处在于当截止的时候器件的源极存在负电压。像前面展示的那样，负电压的振幅与连接主 MOSFET 与地的寄生电感成比例（包括与整流器相连的寄生电感），器件的闭合速度大部分由栅极驱动电阻  $R_{GATE}$  和输入电容  $C_{iss}$  决定。这个负电压可以给驱动器的输出级带来很大的麻烦，因为它可以直接影响驱动器或者 PMW 集成电路的源极引脚——经常被叫做 SRC 或者 VS 引脚，可能会使一些内部电路显著低于地。负电压暂态可能引起的另一个问题是可能在自举电容上产生过压。电容  $C_{BST}$  很快被  $D_{BST}$  从  $C_{DRV}$  处充满电，因为  $C_{DRV}$  是参考电压，自举电容上面的最大电压是  $V_{DRV}$  和源极端的负电压之和。给自举二极管串联一个小电阻就可以减轻这个问题，不幸的是，串联的电阻并不能提供一个可靠的解决过压的方案，而且它还使自举电容的充电速度变慢。

Figure 26. High voltage driver IC for bootstrap gate drive

如图 27 所示是一个给 SRC 引脚提供了非常有效地保护的电路。它包括把栅极电阻挪到驱动器和主要的 MOSFET 的源极之间，从地到驱动器的 SRC 引脚之间加了一个小的、低正向电压降的肖特基二极管。

Figure 27. Protecting the SRC pin

在这个电路中， $R_{GATE}$ 有两个作用，它设定了 MOSFET 的开关速度，而且在主开关的源极处于负电压暂态的时候为肖特基二极管提供限制的电流，现在，这个开关节点就可以不用打断驱动器的动作而达到负几伏。另外，与  $C_{BST}$  的两个引脚相连的两个二极管也可以保护自举电容使它不会处于过压状态。这个电路唯一的潜在威胁就是自举电容的充电电流必须经过  $R_{GATE}$ 。 $C_{BST}$  和  $R_{GATE}$  的时间常数会使重复充电过程慢下来，这或许是一个限制因素当 PWM 的占空比趋于一致时。

## 自举偏压、瞬态问题和启动

图 28 所示为一个典型的自举栅极驱动技术的典型应用图表。

Figure 28. Bootstrap bypassing example

图示中有 4 个重要的旁路电容。

从设计观点来看，自举电容  $C_{BST}$  是最重要的组成元件。因为当主 MOSFET 为源极参考变动电路提供偏置的时候，它需要过滤为主 MOSFET 栅极充电的高的峰值电流。在每一个开关周期正常运行时，自举电容提供全部的栅极电荷 ( $Q_G$ ) 来使 MOSFET 导通，逆向回收电荷和自举二极管的泄露电流、电位移器的静态电流和栅极驱动器、栅极和源极之间的泄露电流，包括可能的栅极到源极之间的电流消耗都使电阻变小。这其中的一些电流只在主开关导通期间存在，一些或许是零，它们都取决于驱动器和电位移器的实际动作。

假设稳态运行时，下面的公式可以计算在为了达到目标脉动电压时的自举电容值， $\Delta V_{BST}$ ：

$$C_{BST} = \frac{Q_G + Q_{RR} + I_{BST} \cdot \frac{D_{MAX}}{f_{DRV}}}{\Delta V_{BST}}$$

这里：

$$I_{BST} = I_{LK,D} + I_{Q,LS} + I_{Q,DRV} + I_{GS}$$

为了确定自举电容的值，两个条件都要考虑到。在负载暂态的时候，可能有必要使主开关保持在导通或者截止的状态几个开关周期。为了确保在这种条件下不间断的运行， $C_{BST}$ 必须储存足够的能量使变动的偏置电压保持在高边栅极驱动集成电路的下限电压之上一段更长的时间。

从低负荷到高负荷，合适的控制器可以使主开关保持导通状态直到输出电感电流达到负载的电流值。最大的导通时间通常用输出电感两端的电压差来定义，在这样的情况下，最大的自举电容值可以这样得到：

$$C_{BST,\text{MIN}} = \frac{Q_G + Q_{RR} + I_{BST} \cdot t_{ON,\text{MAX}}}{V_{BST} - V_{UVLO}}$$

这里  $V_{BST}$  是通过  $C_{BST}$  的自举偏压的初始值， $V_{UVLO}$  是驱动器的下限电压。如果用离散的变动驱动器来驱动的话， $V_{UVLO}$  可以用最小的可靠的栅极驱动电压替换。

当 MOSFET 停止工作几个开关周期的时候，任何其他方向负载瞬态都需要脉冲瞬变。当输出电感的电流变为 0 时，主开关的源极就定位在输出电压水平。自举电容必须提供所有的放电电流，也必须储存足够的能量以便在闲置段结束的时候使开关导通。类似于先前的瞬态模式，电容的最小值可以这样计算：

$$C_{BST,\text{MIN}} = \frac{Q_G + (I_{LK,D} + I_{Q,LS} + I_{Q,DRV}) \cdot t_{OFF,\text{MAX}}}{V_{BST} - V_{UVLO}}$$

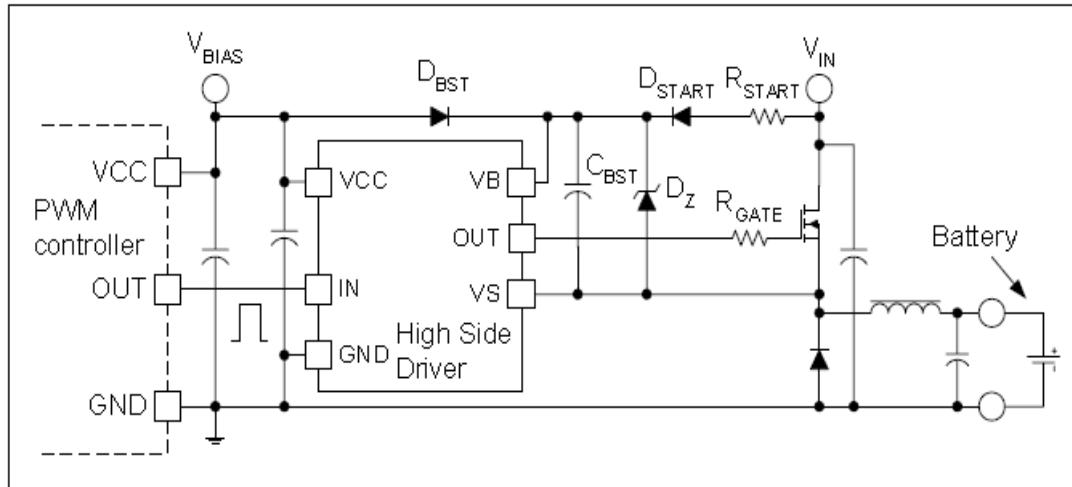

在某些应用，如在充电器中，输出电压要早于输入能源应用于整流器。这些情况下，主 MOSFET 的源极和  $C_{BST}$  的负极连接在输出电压上，自举二极管可能在启动的时候反向偏置。给自举电容提供初始的电荷或许是不可能的，这取决于偏置和输出电压电位之间的电位差。假如输入和输出之间有足够的电压差，如图 29 所示的由电阻  $R_{START}$ 、二极管  $D_{START}$ 、稳压二极管  $D_Z$  组成的简单的电路可以解决启动问题。

Figure 29. Bootstrap start-up circuit

在这个启动电路中， $D_{START}$ 作为第二个自举二极管用来在加电的时候给自举电容充电。 $C_{BST}$ 经过充电之后将会达到比正常情况下的驱动器的偏置电压高的齐纳电压  $D_z$ 。自举电容电流和齐纳电流都被启动电阻限制。为了达到高效率，选择的电阻应该可以使电流限制在一个很小的值，因为第二个通过启动二极管的自举线路将会一直存在于电路中。

### 接地注意事项

关于自举栅极驱动和高边 N 沟道 MOSFET 有 3 个接地问题需要解决。图 28 即可用来识别最关键的高强度电流在一个循环中的典型应用。

第一个焦点就是需要限制栅极的峰值电流在一个比较小的范围内，考虑到栅极电流必须经过的线路，这可能是一个很具有挑战性的任务。导通时，这个路线包括自举电容，驱动器导通的晶体管、栅极电阻、栅极端，最终，这个循环在主 MOSFET 的源极也就是以  $C_{GST}$  为参考的地方结束。截止过程更为复杂，因为栅极电流有两个独立的部分。电容  $C_{GS}$  的放电电流被很好的定位，它流经栅极电阻、驱动器截止的晶体管，从功率场效应管的源极流向栅极。另一方面，电容  $C_{GD}$  的电流必须流经电阻  $R_{GATE}$ 、驱动器截止的晶体管、输出滤波器，最终流经功率级的输入电容 ( $C_{IN}$ )。这三个载有栅极驱动电流的环路都必须缩小到印刷电路板上。

第二条高强度电流路线包括自举电容、自举二极管、以地为参考的驱动器的旁路电容以及功率级的整流二极管或者晶体管。 $C_{GST}$  从以地为参考的驱动器电

容  $C_{DRV}$  通过自举二极管再次充电，使  $D_{BST}$  的正极和地连接起来。这种再充电过程发生在很短的时间内，其中还有峰值电流。因此这个高边驱动器必须局部绕道到它自己的输入上面。根据经验， $C_{DRV}$  需要比  $C_{BST}$  大几个数量级。为了保证可靠性，将循环线路缩小到印刷电路板上面也同样重要。

这个电路的第三个难题就是保持寄生电容电流流经电源和地，而且流经的环路阻抗要低。目标就是控制这部分电流远离敏感的模拟电路的地端。如图 30 展示了两个高边驱动集成电路中的寄生电容电流的线路。

单独的高边驱动集成电路常常只有一个公共的地端。因为电容电流必须回到能级的地面电位，集成电路的低边部分需要以激励地线为参考。这是与直觉相违背的，因为驱动器的控制信号是以信号地线为参考。然而想要消除模拟和激励地线之间的电容电流还需要使两者地之间的可能的差异性最小。

如果用既有低边部分又有高边部分的一般意义上的桥式驱动器，这个情况会得到很大的改善。这些环路有两种地经常被标成 GND 和 COM，在设计上提供了更多的便利。为了使电容电流经过最短的路线回到激励地线，可以把 COM 的引脚直接与激励地线相连。而 GND 的引脚可以与控制器的信号地线相连，这样就可以达到最大的抗干扰能力。为了完整性，PWM 控制器的旁路电容也应该被提到，它接在芯片的 VCC 和 GND 的引脚的附近。再一次提到图 2-8，相对于  $C_{BST}$  和  $C_{DRV}$  而言， $C_{BIAS}$  是一个比较小的电容，因为它仅仅提供高频通路而不是栅极驱动的组成部分。

*Figure 30. Capacitive currents in high side applications*

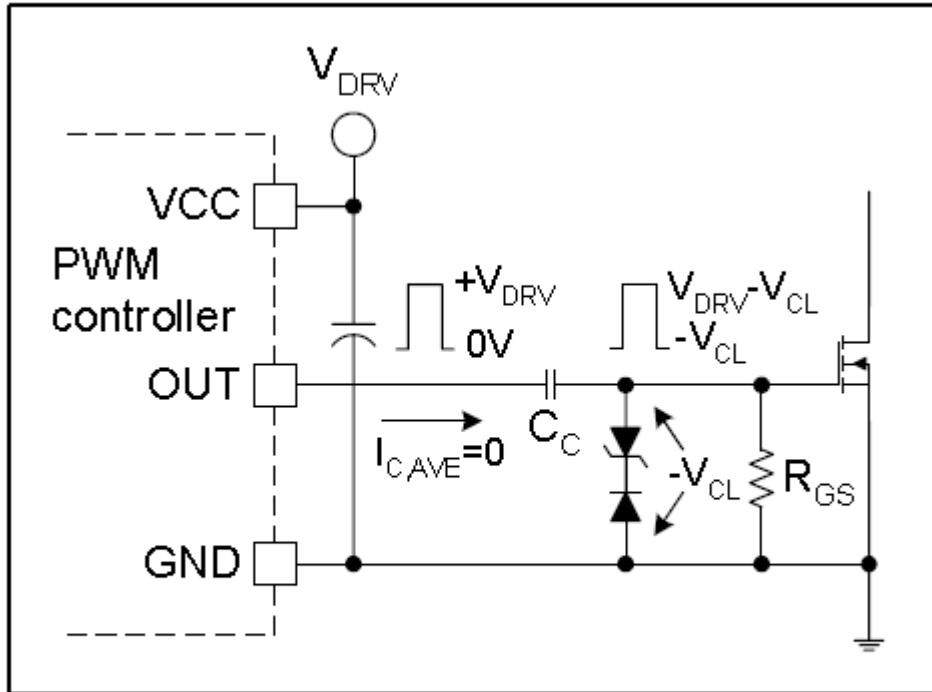

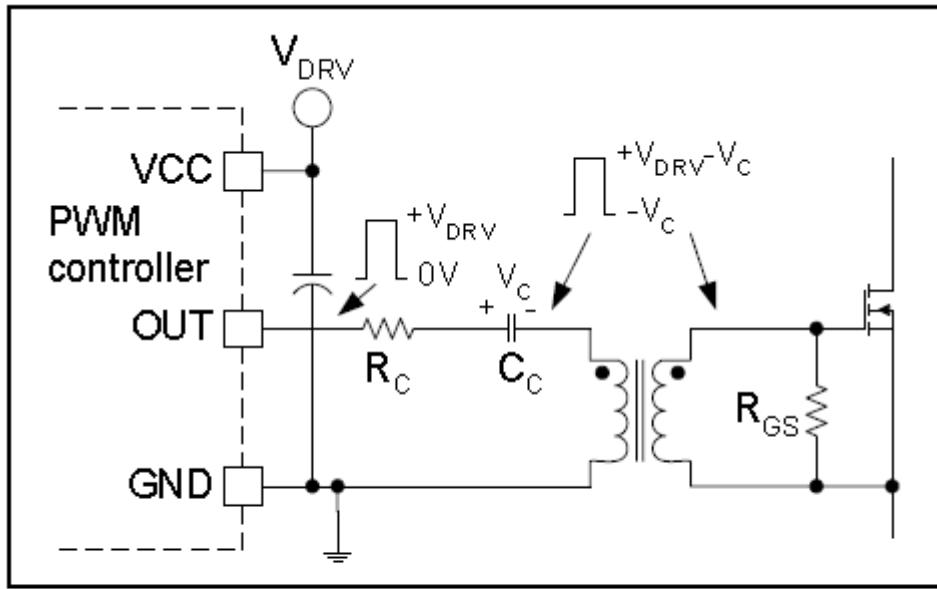

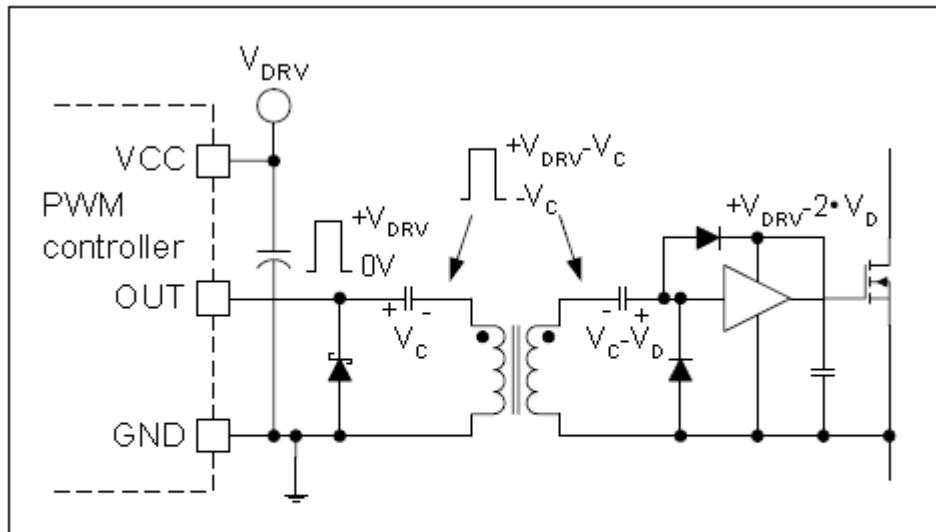

### 交流耦合栅极驱动电路

在栅极驱动中交流耦合仅仅为栅极驱动信号提供了简单的幅度变动。交流耦合的主要目的是参照高边栅极驱动器为主MOSFET修正开启和闭合电压，其中的关键是桥接大的可能的差异性。如图3-1所示的以地为参考的例子中，栅极不是被原始的驱动器的输出电压，0V到 $V_{DRV}$ 驱动，而是被 $-V_{CL}$ 到 $V_{DRV}-V_{CL}$ 驱动。电压 $V_{CL}$ 由被二极管固定的网络决定，它是穿过耦合电容的时候产生的。这种技术的好处在于以一种简单的方法在截止期间为栅极提供了负偏压，使得在开关断开的时候提高了断开的速度以及对MOSFET的dv/dt的免疫能力。作为交换，降低了闭合的速度，以及因为降低了的正驱动电压而可能需要提高阻

值的 $R_{DS(on)}$ 。交流耦合的基本成分由耦合电容 $C_c$ 和栅极到源极的负载电阻 $R_{GS}$ 组成。

*Figure 31. Capacitively coupled MOSFET gate drive*

电阻在加电的时候起到了拉低栅极电位的最重要作用，启动时保持MOSFET闭合的原理是位于驱动的输出端和器件的栅极之间的耦合电容的阻挡作用。另外， $R_{GS}$ 为流经耦合电容的电流提供了线路。如果没有这个电流成分，或许通过 $C_c$ 就不能产生电压。理论上，在每个开关周期中，都会产生同样数量的栅极电荷然后通过电容运输，而通过 $C_c$ 的静电荷为0。同样的原理也适用于稳态时来确定通过电路中的耦合电容和 $R_{GS}$ 的直流电压。假设没有钳位电路，一个固定的 $V_c$ 电压通过电容，一个固定的循环周期D， $R_{GS}$ 的电流可以看成是通过 $C_c$ 的附加成分。因此，在导通期间以及MOSFET的持续导通时间内通过耦合电容的电荷是：

$$Q_{C,ON} = Q_G + \frac{V_{DRV} - V_c}{R_{GS}} \cdot \frac{D}{f_{DRV}}$$

同理，在截止期间以及持续截止时间通过的电荷是：

$$Q_{C,OFF} = Q_G + \frac{V_C}{R_{GS}} \cdot \frac{1-D}{f_{DRV}}$$

在稳态工作时，这两个电荷必须相等。

解  $V_C$  的方程式就可以得到通过耦合电容的电压值：

$$V_C = V_{DRV} \cdot D$$

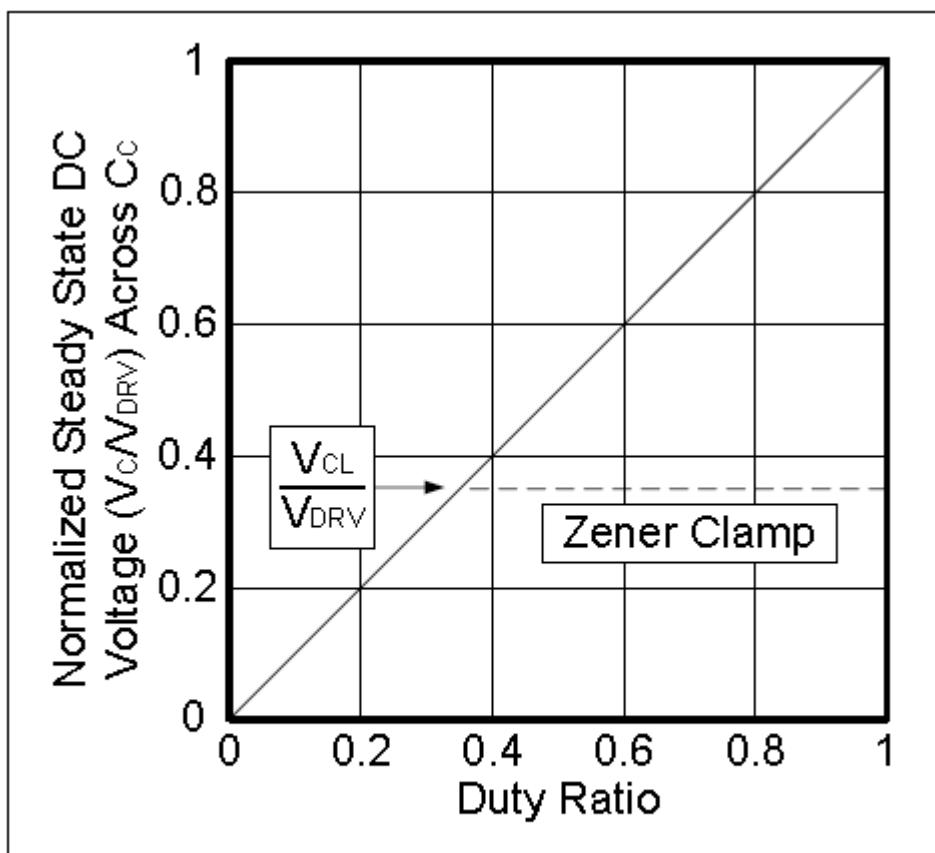

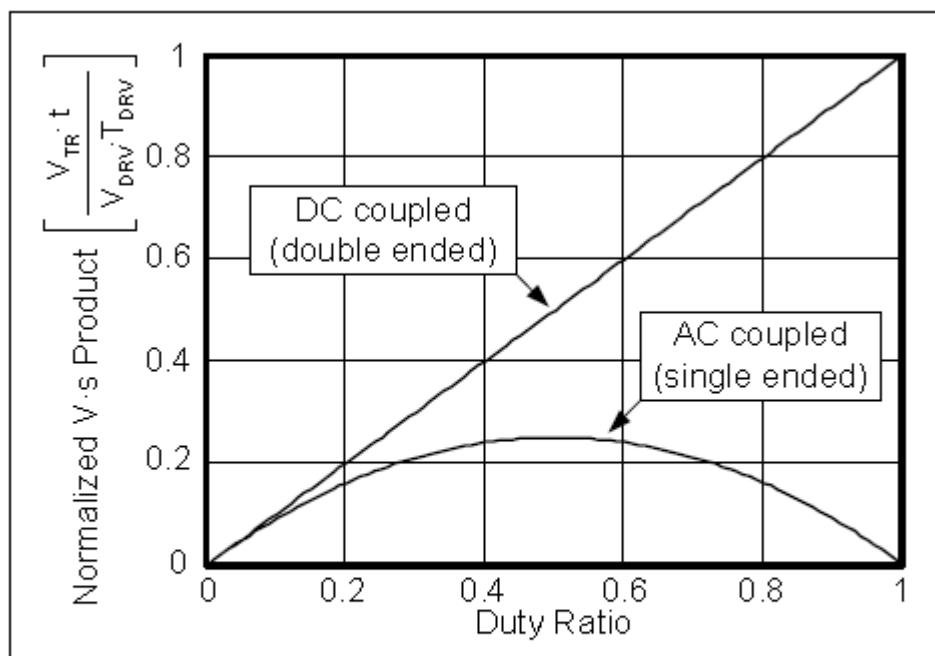

这个被广泛了解的关系强调了耦合电容电压的占空比的依赖性。当占空度变化的时候， $V_C$  也跟着变化，MOSFET 的开关电压因此也跟着调节。如图 3 2 所示，当占空比较低时，截止时的负偏压减小，当占空比较高时，导通电压显得有些不足。

Figure 32. Normalized coupling capacitor voltage as a function of duty ratio

这种在比较大的占空比情况下不适当的导通电压可以通过像图 3 1 展示的那样给  $R_{GS}$  并联一个钳位电路的方法来解决。它对耦合电容电压的影响在图 3 2 中也表示了出来。因为耦合电容的电压被钳位电压限制了，栅极的最大负偏压也确定

了下来。因为栅极驱动的幅度不被交流耦合电路影响，因此可以保证一个占空比幅度内的最小的启动电压。

## 耦合电容的计算

在每个开关周期中，通过  $C_c$  的电荷量都在开关频率的基础上引起了通过耦合电容的交流波动。很明显，这个电压波动与驱动电压的幅度相比应该尽可能的小。

这个波动电压可以根据前面计算的电荷量来计算：

$$\Delta V_c = \frac{Q_G}{C_c} + \frac{(V_{DRV} - V_c) \cdot D}{C_c \cdot R_{GS} \cdot f_{DRV}}$$

因为  $V_c = D \cdot V_{DRV}$ ，因此这个式子整理之后可以得到  $C_c$  的值：

$$C_c = \frac{Q_G}{\Delta V_c} + \frac{V_{DRV} \cdot (1 - D) \cdot D}{\Delta V_c \cdot R_{GS} \cdot f_{DRV}}$$

当  $D=0.5$  的时候，这个式子取最大值。好的情况下应当限制最大的交流波纹振幅在  $V_{DRV}$  的 10%。

## 耦合电容的启动瞬态

在计算最小的耦合电容之前，有一个参数需要先定义一下。 $R_{GS}$  的值应该首先被确定，为了做出适当的决定，应该首先检查交流耦合电路的启动瞬态。

在加电的时候， $C_c$  的初始电压为 0，驱动器的输出开始通过耦合电容使直流电压逐渐增大直到达到它的稳态电压值， $V_c$ 。通过  $C_c$  形成  $V_c$  的时间决定于由  $C_c$  和  $V_c$  同时决定的时间常数。因此，为了同时达到既定的启动瞬态时间和耦合电容的波动电压，这两个参数必须同时计算。幸运的是，这里有这两个未知量的计算公式：

$$C_c = \frac{Q_G}{\Delta V_c} + \frac{V_{DRV} \cdot (1 - D) \cdot D}{\Delta V_c \cdot R_{GS} \cdot f_{DRV}}$$

$$\tau = R_{GS} \cdot C_C \rightarrow R_{GS} = \frac{\tau}{C_C}$$

通过它们两个可以得出唯一的方案。

取代第二个表达式中的  $R_{GS}$  的表达式，最差的情况下， $D = 0.5$ ，又  $\Delta V_c = 0.1 \cdot V_{DRV}$ ，第一个方程就得到了解决，简化后的电容值表达式为：

$$C_{C,MIN} = \frac{20 \cdot Q_G \cdot \tau \cdot f_{DRV}}{V_{DRV} \cdot (2 \cdot \tau \cdot f_{DRV} - 5)}$$

p a g e 3 0

一旦  $C_{C,MIN}$  得值计算出来，它的值和需要的启动时间常数共同决定了下拉电阻的值。交流耦合驱动作为交换，平衡了效率和瞬态时间常数。为了在不同的占空比的时候耦合电容电压值可以得到更快的调节，栅极到源极之间的电阻应该可以承受更大的电流。

## 变压器耦合栅极驱动

在高电压栅极驱动芯片出现之前，唯一的可行的解决方法就是用一个栅极驱动变压器来驱动离散或者相似的高电压电路中的高边开关。这两种方案今天都还在使用，它们都有自己的优缺点，可以用在不同的应用中。集成的高边驱动电路很方便，它们用了更小的电路板区域，但是它们也有了明显的闭合和断开延迟。合适的耦合变压方案只有可以忽略的延迟，而且它可以在即使更高的势差下工作。通常它需要更多的元件，对变压器的设计有要求或者至少要理解工作原理和它的规格。

聚焦在栅极驱动电路之前，复习一下变压器设计的基本问题以及它们与栅极驱动的联系。

1. 变压器至少有 2 个线圈，一个主线圈，一个次级线圈，它们都应该有良好的绝缘性。两者之间的匝数比应该可以使电压有一定的缩放比例。对于栅极驱动变压器来说，可以不必要使电压有一定的缩放比例，但是一定要有良好的绝缘性。

2. 理想的变压器不会存储能量，被称作反激式变压器的实际上就是耦合

线圈。但是，实际上的变压器都在线圈和磁芯的两部分合到一块的地方的空气之间的非磁性区域都储存着少量的能量，泄露以及自感表明了这种储能。在电源变压器中，减少泄露的电感对于减少储存的能量以及提高效率非常重要。栅极驱动变压器掌握了很低的平均功率，但是在导通或者截止的时候它产生了高电流峰值。为了避免栅极驱动中的时间延迟，比较低的漏电流还是很有必要。

3. 法拉第定律要求一段时间之内变压器线圈上的平均电压为 0，即使是一点直流分量都可以使工作状态不稳定以及使磁芯达到磁饱和。这个定律对于单端电流模式 PWM 控制的变压器耦合栅极驱动电路的设计有很大的影响。

4. 磁芯的磁饱和限制了伏秒数积通过线圈，变压器的设计必须考虑到包括最大占空比时以及同时最大输入电压时的最坏情况下的瞬态的所有条件下的最大的伏秒数积。栅极驱动变压器的最大的优点在于不变的供给电压。

5. 开关部分的一个非常重要的部分就是在单端电流模式的应用（仅仅在 B-H 曲线的第一象限工作）比如说快速整流器中需要保留对主电源变压器的磁芯的复位。复位时间限制了变压器的工作占空比。这即使是在单端电流模式栅极驱动变压器设计中也是一个很少见的问题，因为它们必须交流耦合，这样它们才可以双向磁化工作。

## 单端变压器耦合栅极驱动电路

这些栅极驱动电路和单一输出 PWM 控制器相互协调，共同驱动高边开关，如图 33 所示就是一个基本的电路。

耦合电容必须和栅极驱动变压器的初级线圈串联来为磁化的磁芯提供复位电压。如果没有这个电容，就会有一个取决于通过线圈的直流电压的占空比，变压器也会变得饱和。

*Figure 33. Single ended transformer coupled gate drive*

$C_c$  的直流电压像交流耦合直接驱动中展示的那样生成，耦合电容电压的稳态值是：

$$V_C = D \cdot V_{DRV}$$

像交流耦合直接驱动一样，实际的栅极驱动电压  $V_C$  随着占空比而变化。另外，突然地占空比变化会在栅极驱动变压器和耦合电容旁边产生 L-C 谐振回路。大多数情况下，这个 L-C 谐振可以通过给  $C_c$  串联一个小电阻  $R_c$  就可以得到缓解。 $R_c$  的阻值由谐振回路的特性阻抗决定，给出计算公式如下：

$$R_c \geq 2 \cdot \sqrt{\frac{L_M}{C_c}}$$

记住上面的公式中  $R_c$  的值等价于包括 PWM 驱动器的输出阻抗的串联电阻。此外，要考虑到耦合电容电压中的准确的衰减反馈或许需要不合理的阻值。这可能会限制栅极电流，最终导致主开关的开关速度受到限制。另一方面，欠阻尼的反馈可能会导致谐振期间不可接受的通过栅极和源极端的电压。

这个电流的产物  $V_C$  有两种成分，变压器的磁化电流以及流通在连接栅极和主 MOSFET 的源极的电阻中的电流。因此，启动和瞬态时间常数支配着耦合电

容电压的调节速度，这反映了栅极驱动变压器的磁化部分的影响，可以被下面的公式估算出：

$$\tau = \frac{2 \cdot \pi \cdot f_{DRV} \cdot L_M \cdot R_{GS} \cdot C_C}{2 \cdot \pi \cdot f_{DRV} \cdot L_M + R_{GS}}$$

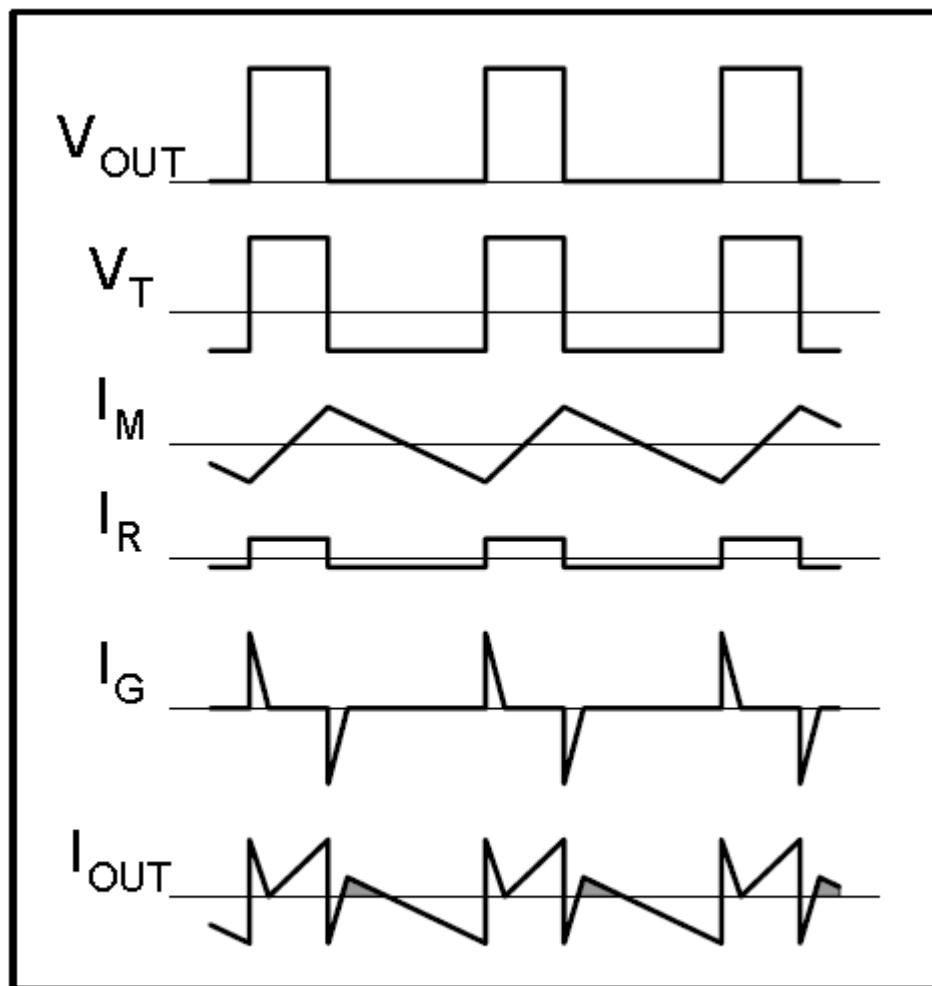

磁化部分对驱动器的网络电流以及方向有另外一个重大的影响。图 34 展示了电路中的不同的电流成分，以及这些电流成分的和， $I_{OUT}$ ，它必须由驱动器提供。

*Figure 34. Driver output current with transformer coupled gate drive*

注意输出电流波形的阴影区域，输出驱动器在它的低状态，这意味着它支持反向电流。但是因为磁化电流成分，驱动器确实在产生电流，因此输出必须控制变压器耦合栅极驱动的双向电流。如果驱动器没有在双向上携带电流的能力，或许需

要额外的二极管。双极 MOSFET 驱动器就是一个经典的例子，因为这个时候肖特基二极管必须连接地和输出引脚。在不同的占空比以及电流值时的驱动器处于高态的时候相同的情况也会发生。

解决这个问题，避免驱动器的输出上的二极管的出现的一个简单的补救方法就是增加阻抗电流来抵消磁化电流的影响。

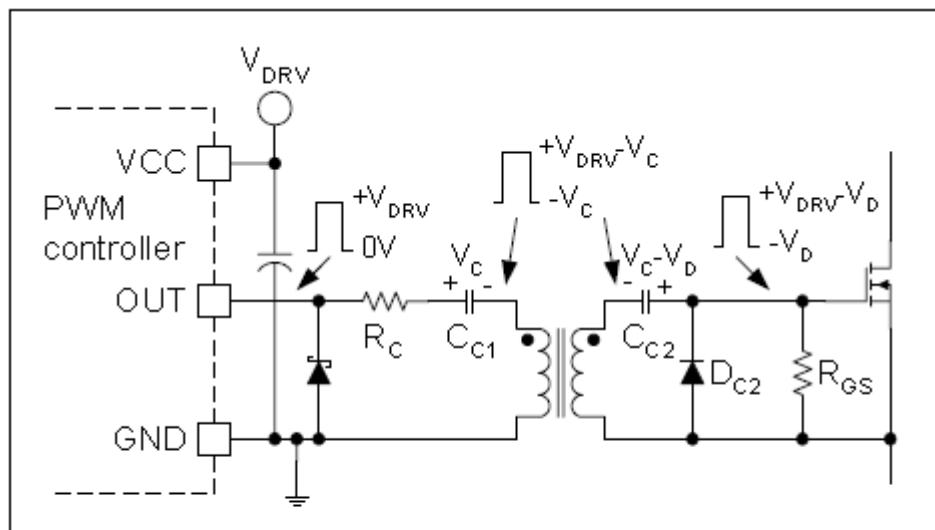

宽的占空比，像整流器中的那样，图 33 中的电路没有提供足够的栅极驱动电压，耦合电容电压与占空比成比例增加。相应的，截止期间的负偏压也增加，但是导通电压下降了。在栅极驱动变压器的次级线圈后加两个小元件就可以解决这个问题，图 35 展示了使栅极激励脉冲保持原先的电压水平的常用的技术。

*Figure 35. DC restore circuit in transformer coupled gate drive*

这里用了另外一个耦合电容和一个简单的二极管来使变压器的次级线圈恢复到原来的栅极驱动电压水平。如果截止期间主开关需要一个更大的负偏压，可以像图 31 所示的关于交流耦合直接驱动的解决方案那样给这个二极管串联一个齐纳二极管。

### 耦合电容的计算

耦合电容值的计算是建立在最大的波动电压和先前交流耦合电路描述的稳态工作时通过电容的电荷量的基础上的， $C_{C2}$ 的方程式跟直接耦合栅极驱动电路中的那个计算类似。波动有两种成分，一种跟主 MOSFET 的栅极电荷有关，另一个是与栅极下拉电阻中的电流有关：

$$C_{C2} = \frac{Q_G}{\Delta V_{C2}} + \frac{(V_{DRV} - V_{DC2,FW}) \cdot D_{MAX}}{\Delta V_{C2} \cdot R_{GS} \cdot f_{DRV}}$$

当开关有最大的导通时间的时候，它也有了最大值，也就是在最大占空比的时候取最大值。在初级线圈部分，栅极驱动变压器的耦合电容磁化电流产生了另外的波动成分。它的影响反应在下面的方程式上，这个方程式也可以用来计算初级线圈的耦合电容：

$$C_{C1} = \frac{Q_G}{\Delta V_{C1}} + \frac{(V_{DRV} - V_{DC2,FW}) \cdot D}{\Delta V_{C1} \cdot R_{GS} \cdot f_{DRV}} + \frac{V_{DRV} \cdot (D^2 - D^3)}{\Delta V_{C1} \cdot 4 \cdot L_M \cdot f_{DRV}^2}$$

可以保证在各种条件下保持在目标波动电压之下的最小的电容值可以通过确定上面表达式的最大值来得到。不幸的是，不同占空比下的最大值取决于实际的设计参数以及元件值。大多数情况下，它会下降到  $D=0.6$  到  $D=0.8$  范围内。

另外还要注意出现在主 MOSFET 晶体管栅极的总的波动电压， $\Delta V_{C1} + \Delta V_{C2}$ 。当需要特定的波动电压和栅极压降的时候，它必须分离到两个耦合电容之间。

### 栅极驱动变压器的设计

栅极驱动变压器的作用是用来传递以地为参考的栅极激励脉冲，使它通过比较大的势差来调解变动的驱动。像所有的变压器一样，它也可以缩放电压，尽管它很少这样被要求。它操控很低的能量但是很高的峰值电流来驱动功率场效应晶体管的栅极。栅极驱动变压器被像 PWM 占空比功能的可变的脉冲宽度来驱动，振幅的固定或者是变动取决于电路排布。在单端电流模式电路中栅极驱动变压器是交流耦合，磁化部分产生了振幅可变的脉冲。双端引线安排，像半桥式应用中，用振幅固定的信号来驱动栅极驱动变压器。所有情况下，栅极驱动变压器在 B-H 曲线的第一个和第三象限都工作。

栅极驱动变压器的设计类似于电源变压器的设计，通常只有一种匝比，由于功耗而造成的温升通常可以忽略。因此，设计以磁芯的选择开始。栅极驱动变压器的磁芯形状可以包括环形、RM、P 或者类似的形状。磁芯材料是高透磁率的铁酸盐，这样可以使磁化电感值达到最大，同时磁化电流达到最小。经验丰富的

设计者可以通过经验来选择磁芯的尺寸,或许也可以像电源变压器设计中要求的那样根据产品的估计区域来选择。磁芯选择完成之后,初级线圈的匝数就可以通过下面的公式来计算:

$$N_p = \frac{V_{TR} \cdot t}{\Delta B \cdot A_e}$$

其中  $V_{TR}$  是通过初级线圈的电压,  $t$  是指脉冲的持续时间,  $\Delta B$  是指  $t$  时间内峰峰值的变化,  $A_e$  是指选出的磁芯的等效横截面。

首要的任务是找出分子中最大的伏秒积,图 36 展示了单端电流模式和双端引线的栅极驱动变压器的标准积与整流器占空度之间的关系。

*Figure 36. Gate drive transformer volt-second product vs. duty ratio*

对于一个交流耦合电路来说,最坏的情况就是  $D=0.5$ ,直接驱动达到了最大工作占空比的伏秒数峰值。有趣的是,交流耦合电路通过四个因素来抑制稳态时的最大的伏秒积,因为在较大的占空比的时候由于电压是通过耦合电容产生的,变压的的电压成比例地减小。

在  $N_p$  的方程式中列出  $\Delta B$  是比较困难的,原因是在暂态的时候不稳定的状态的变化。当输入电压和负载迅速变化的时候,占空比也通过 PWM 控制器而相

应的调节自己。想要推断出不稳定的变化的准确数值是相当困难的，它取决于控制回路的反馈，以及耦合网络存在时它的时间常数。通常，较慢的回路反馈以及更快的时间常数有使不稳定的变化变小的倾向。三分之一的饱和通量密度和最坏的稳态条件下的通量峰值之间的利润对于大多数设计来说，覆盖瞬态已经足够了。

下一步就是在磁芯的有效区域布线，像前面提到的那样，漏电流应当小点防止通过变压器的时候造成延迟，交流线阻也应该得到有效地控制。在环状磁芯上，线应当绕成双股的还是三股的取决于栅极驱动变压器的线数。在壶状磁芯上，每根线都应当保持单层。初级线圈应当尽量靠近中心，后面跟着低边区域的导线，如果需要用到高边部分的线，它应当尽量远离中心区域。壶状磁芯上的线的排布保证了最小的交流线阻以及可以接受的漏电流。此外，与电源地线直接相连的低边部分的导线提供了控制线圈以及变动部分和电源电线之间的天然的屏蔽。

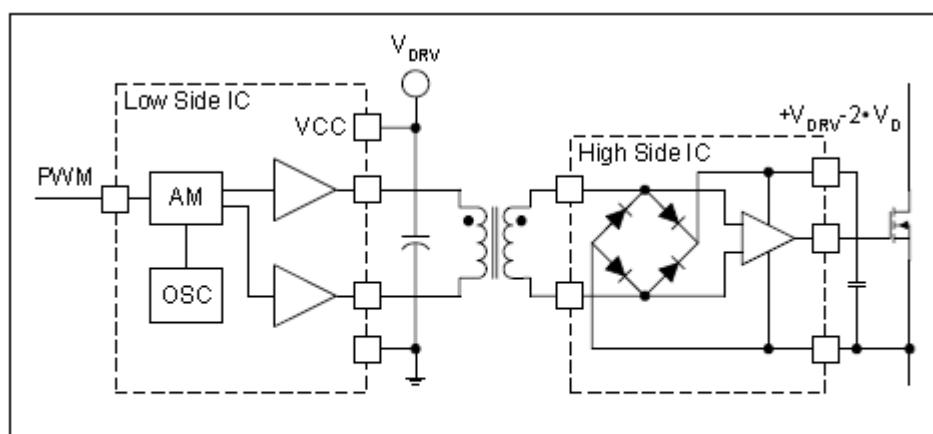

## 两种功能的变压器耦合电路

有低输出阻抗和高速栅极驱动芯片的短时间的传输延迟是必须的高边开关应用。

图 37 和图 38 展示了两种不同的解决方法，它们都可以既提供电源又提供控制给在一个变动的应用中只使用一个变压器的低压栅极驱动芯片。

图 37 中的电路用开关频率来携带控制信号以及能量送给驱动器，原理很简单。在主开关导通期间，变压器的次级线圈电压调节到最大值来给栅极驱动芯片供电。因为电压是从栅极激励脉冲产生，因此前面的几个激励脉冲需要首先对偏置电容进行充电。因此，为这个应用选择的驱动器芯片具有负压锁定功能，避免了栅极驱动欠压时的处理还是令人满意的。

*Figure 37. Power and control transmission with one transformer*

像电路图中展示的那样，直流复位电路必须为独立于运行占空比的驱动器提供偏压，D<sub>C2</sub>也保护了驱动器的输入免受变压器的次级线圈的负的复位电压的影响。这个电路的变压器的设计基本上和其他栅极驱动变压器的设计相同，功率级只被驱动器芯片的能量消耗增加了一点，与 MOSFET 的总的栅极电荷相关的能量亏损相比确实很小。变压器携带了很高的峰值电流，但是这些电流给偏置电容而不是 MOSFET 的输入电容充了电。所有的栅极电流都包括主要晶体管、驱动芯片和偏置电容的一部分电流。

*Figure 38. Power and control transmission with one transformer*

图 38 展示了另外一个利用同一个变压器来转换能量以及控制信号的方案。图 37 和图 38 的不同之处在于变压器的工作频率不同。这个方案运用了一个专用

的芯片对，高频载波被用来传送能量，幅度调制传输控制命令。为了有效地利用电路板区域，图 38 中的电路原理图可以划分成两部分。因为运用了高频，因此这里用到的变压器要小于传统上的栅极驱动变压器。这种解决方案的另外一个优点在于可以独立于栅极驱动命令把变动的驱动器的偏压确定下来，这样驱动就没有前面的方案中的开启延迟了。

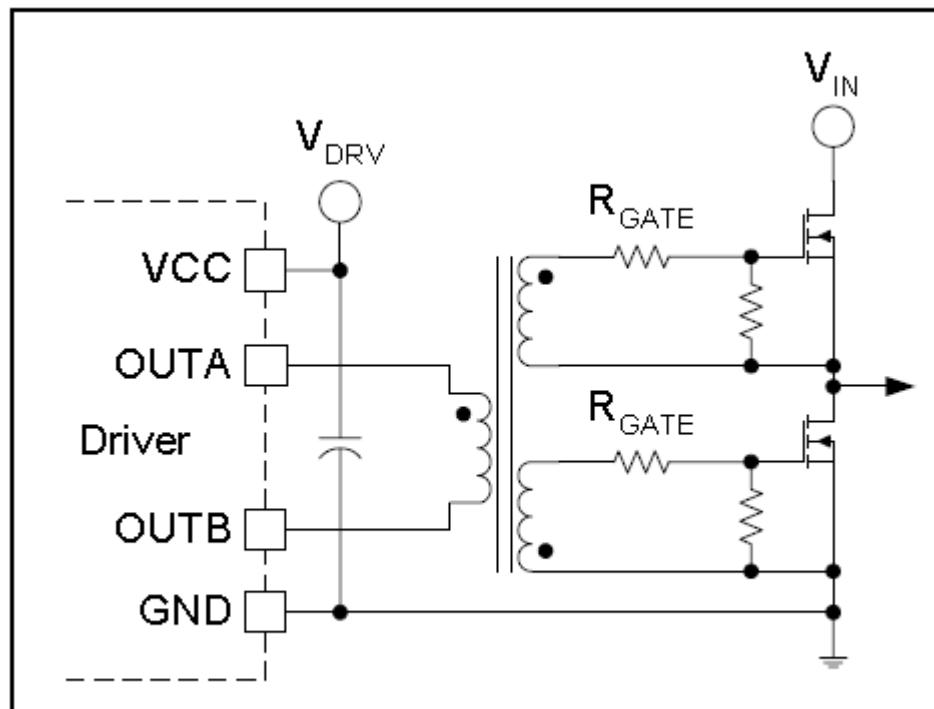

## 双端变压器耦合栅极驱动

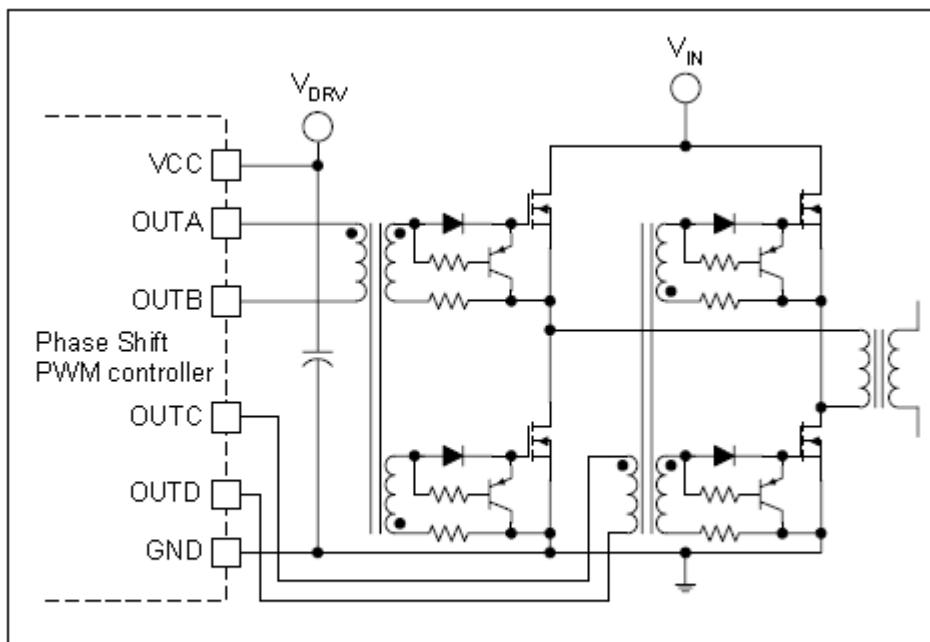

在高能量半桥式以及桥式转换器中，驱动两个或者更多的 MOSFET 的需求由推挽式或者被叫做双端 PWM 控制器控制着，如图 39 所示即为这种栅极驱动电路的简化的原理图。

在这些应用中，两极对称的栅极驱动电压很有效，在第一个时钟周期中，**OUTA**是导通的，迫使通过栅极驱动变压器的初级线圈产生了一个正压。在下一个时钟周期中，**OUTB**导通了一段时间（稳态时间），通过磁化电感产生了一个极性相反的电压。在任意两个时钟周期中，通过变压器初级线圈的平均电压为 0V。

*Figure 39. Push-pull type half-bridge gate drive*

因此在推挽式栅极驱动电路中不需要交流耦合。

设计者们总是担心任何可能由元件容差产生、在控制器中抵消的不平衡成

分，这些小的偏差可以很容易地被驱动器的输出阻抗或者跟变压器的初级线圈串联的一个小电阻补偿掉。不均衡的工作周期会产生一个可以产生通过驱动电路的等效电阻的平衡电压的电流，假设 PWM 控制器的两种输出占空比  $D_A$  和  $D_B$ ，磁化电感的直流电流值定义如下：

$$I_{DC} = \frac{V_{DRV}}{2 \cdot R_{EQV}} \cdot (D_A - D_B)$$

为了表现这个问题的繁琐，我们假设  $D_A=0.33$ ,  $D_B=0.31$  (百分之六的占空比不同)， $V_{DRV}=12V$ ,  $R_{EQV}=5\Omega$ ，是高边和低边的输出阻抗之和，直流电流的结果值是 24mA，额外的功耗仅为 3mW。

栅极驱动器的设计应该遵循的规则和程序和这一章介绍过的规则和程序是一样的，最大的伏秒积由  $V_{DRV}$  和开关周期决定，因为通常推挽式的电路没有占空比限制。

最差条件下的通量密度的峰值与饱和时的通量密度的比值应当适当(大约为 3:1)。

图 40 展示的是栅极驱动变压器控制满桥式调相整流器的四个功率晶体管的特殊的应用。

*Figure 40. Push-pull type half-bridge gate drive*

根据调相技术，这个功率级用了四个 50% 占空比的栅极驱动信号。每个腿的

两个 MOSFET 都需要可以由同一个栅极驱动变压器的两个输出绕组提供的补充驱动波形，尽管稳态的占空比通常为 0.5，改变两个补充的脉冲序列之间的相位关系会使占空比出现不对称现象。因此，瞬态的时候 PWM 输出为栅极驱动变压器提供的不是原先的占空比 50% 的信号。因此，应当在变压器中建立一个安全系数来覆盖暂态时候不平均的占空比。

另一个需要指出的有趣的事是局部的断开电路可以很容易就被合并，而且变压器的次级线圈很需要这种电路。栅极驱动变压器，准确的说是变压器的漏电感对快速变化的信号表现出了较高的阻抗。如果驱动器的下拉能力对于高边开关的应用不是很适合的话，电源电路的闭合速度以及  $dv/dt$  免疫力就会受到很严重的影响。

## 最终的评论，概要

像所有的书一样，这篇文章应该从头读到尾来了解整个故事。早先对于开关速度、 $dv/dt$  的免疫力、绕路规则等等的考虑的描述对于所有的包括变压器耦合栅极驱动电路在内的所有电路都适用。像那些互相依赖的话题一样，只有特别的独特的、新的性能才突出表现了出来。

这篇文章介绍了为高边开关应用电路设计高性能栅极驱动电路时的一个系统性的观点，这些程序可以用下面的分步的清单来总结概括：

1. 栅极驱动设计程序应在功率级设计好之后以及选好功率组件之后。

2. 收集所有的工作参数，特别是基于应用要求的功率 MOSFET 的电流和电压，工作点温度、跟功率 MOSFET 周围的电路有关的  $dv/dt$  以及  $di/dt$  的限制，通常由功率级的不同的阻尼或者共振电路决定。

3. 估量实际应用电路中的描述功率半导体元件的寄生组件值的所有的器件参数，数据表中的数值都是为了室温下不实际的测试条件而列出的，因此它们都应该做出相应的修改。这些数据包括器件电容值、总的栅极电荷、 $R_{DS(on)}$ 、阈值电压、米勒稳定电压、栅极内阻等等。

4. 把要求按照优先顺序排好：性能、印刷电路板尺寸、预计花费等等。然后选择跟功率级的拓扑结构吻合的栅极驱动电路。

5. 建立将要用来激励栅极驱动电路的偏置电压电平，检查是否有足够的电压来减小 MOSFET 的  $R_{DS(on)}$ 。

6. 选择驱动芯片，栅极到源极的电阻，根据作为目标的升高的  $dv/dt$  串联的栅极电阻  $R_{DS(on)}$ ，想要的开关速度。

7. 如果需要设计（或者选择）一个栅极驱动变压器。

8. 计算出交流耦合情况下的耦合电容值。

9. 检查启动或者瞬态运行条件，特别是在交流耦合栅极驱动电路中。

10. 估计驱动器的  $dv/dt$  和  $di/dt$  的能力，并和功率级决定的值比较一下。

11. 如果需要增加一个断开电路，计算它的组件的值来达到  $dv/dt$  和  $di/dt$  的要求。

12. 检查驱动电路中所有的功耗。

13. 计算出旁路电容值。

14. 优化印刷电路板的布局使寄生电感达到最小。

15. 为了过多的铃声，在栅极-源极端和驱动芯片的输出端经常检测最终的印刷版上的栅极驱动波形。

16. 需要的时候通过改变栅极驱动电阻来增加保护或者调节共振电路。

在一个可靠的设计中，这些步骤应该在最坏的条件，比如高温，高瞬态电压，比较高的电流等可以改变驱动器工作状态，最终影响功率 MOSFET 的条件下检测。

当然还有更多的栅极驱动的应用，这里就不再论述了。我们希望这里讲述的原则和方法可以帮助读者去理解和分析其他的方案。对于那些想要在告诉栅极驱动设计方案中快速找到答案的人，附录 A 到 E 提供了不同计算的经典实例，附录 F 则提供了一个有变动的栅极驱动电路的整流器的完整的，一步接着一步的栅极驱动设计例子。

## REFERENCES

- [1] V. Barkhordarian, “Power MOSFET Basics”, International Rectifier, Technical Paper

- [2] S. Clemente, et al., “Understanding HEXFET® Switching Performance”, International Rectifier, Application Note 947

- [3] B. R. Pelly, “A New Gate Charge Factor Leads to Easy Drive Design for Power MOSFET Circuits”, International Rectifier, Application Note 944A

- [4] “Understanding MOSFET Data”, Supertex, DMOS Application Note AN-D15

- [5] K. Dierberger, “Gate Drive Design For Large Die MOSFETs”, PCIM ‘93, reprinted as Advanced Power Technology, Application Note APT9302

- [6] D. Gillooly, “TC4426/27/28 System Design Practice”, TelCom Semiconductor, Application Note 25

- [7] “Gate Drive Characteristics and Requirements for HEXFET®s”, International Rectifier, Application Note AN-937

- [8] “TK75050 Smart MOSFET Driver Datasheet”, TOKO Power Conversion ICs Databook, Application Information Section

- [9] Adams, “Bootstrap Component Selection For Control IC’s”, International Rectifier, Design Tip DT 98-2

- [10] “HV Floating MOS-Gate Driver ICs”, International Rectifier, Application Note INT978

- [11] C. Chey, J. Parry, “Managing Transients in Control IC Driven Power Stages” International Rectifier, Design Tip DT 97-3

- [12] “HIP408X Level Shifter Types”, Harris Semiconductor

- [13] “IR2110 High and Low Side Driver” International Rectifier, Data Sheet No. PD-6.011E

- [14] “Transformer-Isolated Gate Driver

Provides Very Large Duty Cycle Ratios”,

International Rectifier, Application Note

AN-950B

[15] W. Andreycak, “Practical Considerations in Troubleshooting and Optimizing Power Supply Control Circuits and PCB Layout”, Unitrode Corporation, Power Supply Design Seminar, SEM-1200, Topic 4

[16] L. Spaziani, “A Study of MOSFET Performance in Processor Targeted Buck and Synchronous Buck Converters”, HFPC Power Conversion Conference, 1996, pp 123-137

[17] W. Andreycak, “Practical Considerations In High Performance MOSFET, IGBT and MCT Gate Drive Circuits”, Unitrode Corporation, Application Note U-137

[18] J. O’Connor, “Unique Chip Pair Simplifies Isolated High Side Switch Drive” Unitrode Corporation, Application Note U-127

[19] D. Dalal, “Design Considerations for Active Clamp and Reset Technique”, Unitrode Corporation, Power Supply Design Seminar SEM1100, Topic 3

[20] E. Wittenbreder, “Zero voltage switching pulse width modulated power converters”, U.S. Patent No. 5402329.

[21] R. Erickson, “Lecture 20, The Transistor as a Switching Device”, Power Electronics ECE579 Course Notes, Fall 1987, pg. 20-4 through 20-16.

[22] R. Severns, J. Armijos, “MOSFET Electrical Characteristics,” MOSPOWER Applications Handbook, Siliconix, Inc., 1984, pg. 3-1 through 3-8.

[23] J. Bliss, “The MOSFET Turn-Off Device - A New Circuit Building Block,” Motorola Semiconductor, Engineering Bulletin

EB142, 1990