ANSG08

# 8-Ch Auto Sensitivity Calibration Capacitive Touch Sensor

# **SPECIFICATION V1.3**

| 작성 | 검토 | 팀장 | Marketing | Q A | Approval |

|----|----|----|-----------|-----|----------|

|    |    |    |           |     |          |

|    |    |    |           |     |          |

|    |    |    |           |     |          |

July, 2011 AD Semiconductor

# Revision History

| Rev. | Description of change                | Date     | Originator |

|------|--------------------------------------|----------|------------|

| 1.0  | First creation                       | 11.07.11 | KD PARK    |

| 1.1  | LDO output pin removal               | 11.08.16 | EW LEE     |

| 1.2  | Adding the packages (24 SOP, 16 SOP) | 11.09.17 | KD PARK    |

| 1.3  | Adding I2C Timing Diagram            | 11.11.17 | KD PARK    |

# 1. Specification

#### 1.1 General Feature

- 8-Channel capacitive sensor with auto sensitivity calibration

- Available LED PWM drive up to 8

- Multi interface I<sup>2</sup>C serial interface / Parallel outputs

- Selectable output operation mode (Single output / Multi output)

- Adjustable 256 steps sensitivity

- Almost no external component needed

- Low current consumption

- Embedded common and normal noise elimination circuit

- RoHS compliant 24 QFN / 24 SOP / 16 SOP packages

- Moisture sensitivity level 2 (MSL2)

### 1.2 Application

- Home appliances (TV, Monitor keypads)

- Mobile applications (PMP, MP3, Car navigation)

- Membrane switch replacement

- Sealed control panels, keypads

- Touch screen replacement application

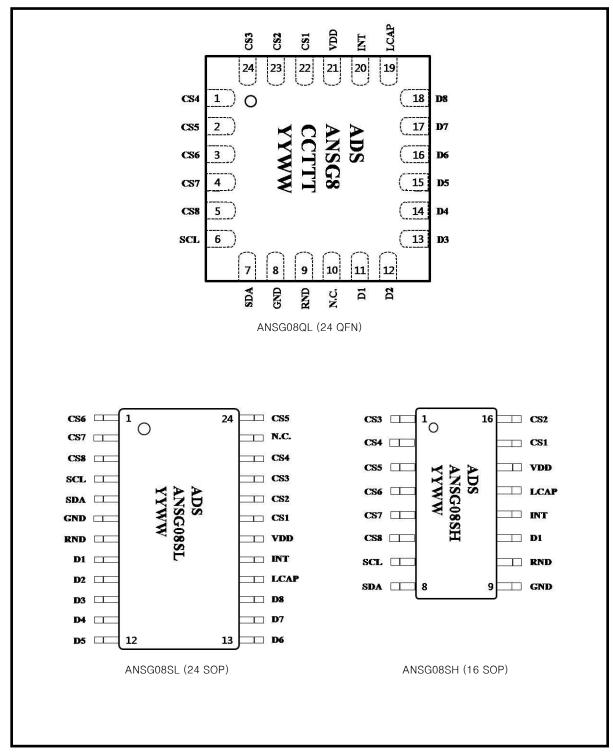

#### 1.3 **Packages**

\* Drawings not to scale

# 2 Pin Description

#### VDD, GND

Supply voltage and ground pin.

#### R.N.D

Radio frequency Noise Detection pin. Normally, R.N.D pin does not connect to anywhere. But, in radio frequency noise environment, this pin must form a pattern line on PCB.

#### CS1 ~ CS8

Capacitive sensor input pins.

#### LCAP

Internal LDO output port.

#### D1 ~ D8

Parallel output ports of CS1~CS8 respectively / LED PWM drive output ports. The structure of these parallel output ports is open drain NMOS for active low output level operation.

#### SCL, SDA

SCL is  $I^2C$  clock input pin and SDA is  $I^2C$  data input-output pin. These ports have internal pull-up resistor. In case of not use, this pin must be not connected to any circuitry.

#### INT

Touch sensing interrupt output pin.

# ANSG08QL (24 QFN package)

| Pin No. | Name  | I/O                       | Description                                                                  | Protection |

|---------|-------|---------------------------|------------------------------------------------------------------------------|------------|

| 1       | CS4   | Analog Input              | Capacitive sensor input 4                                                    | VDD/GND    |

| 2       | CS5   | Analog Input              | Capacitive sensor input 5                                                    | VDD/GND    |

| 3       | CS6   | Analog Input              | Capacitive sensor input 6                                                    | VDD/GND    |

| 4       | CS7   | Analog Input              | Capacitive sensor input 7                                                    | VDD/GND    |

| 5       | CS8   | Analog Input              | Capacitive sensor input 8                                                    | VDD/GND    |

| 6       | SCL   | Digital Input             | I <sup>2</sup> C clock input                                                 | VDD/GND    |

| 7       | SDA   | Digital<br>Input / Output | I <sup>2</sup> C data input-output<br>Open drain NMOS structure              | VDD/GND    |

| 8       | GND   | Ground                    | Supply ground                                                                | VDD        |

| 9       | R.N.D | Analog Input              | Radio frequency Noise Detection pin                                          | VDD/GND    |

| 10      | N.C   | _                         | _                                                                            | _          |

| 11      | D1    | Digital Output            | Parallel output of CS1<br>LED PWM drive output1<br>Open drain NMOS structure | VDD/GND    |

| 12      | D2    | Digital Output            | Parallel output of CS2<br>LED PWM drive output2<br>Open drain NMOS structure | VDD/GND    |

| 13      | D3    | Digital Output            | Parallel output of CS3<br>LED PWM drive output3<br>Open drain NMOS structure | VDD/GND    |

| 14      | D4    | Digital Output            | Parallel output of CS4 LED PWM drive output4 Open drain NMOS structure       | VDD/GND    |

| 15      | D5    | Digital Output            | Parallel output of CS5 LED PWM drive output5 Open drain NMOS structure       | VDD/GND    |

| 16      | D6    | Digital Output            | Parallel output of CS6<br>LED PWM drive output6<br>Open drain NMOS structure | VDD/GND    |

| 17      | D7    | Digital Output            | Parallel output of CS7<br>LED PWM drive output7<br>Open drain NMOS structure | VDD/GND    |

| 18      | D8    | Digital Output            | Parallel output of CS8 LED PWM drive output8 Open drain NMOS structure       | VDD/GND    |

| 19      | LCAP  | Analog Output             | Internal LDO Output                                                          | VDD/GND    |

| 20      | INT   | Digital Output            | Touch sensing interrupt output Open drain NMOS structure                     | VDD/GND    |

| 21      | VDD   | Power                     | Power (3.0V~5.5V)                                                            | GND        |

| 22      | CS1   | Analog Input              | Capacitive sensor input 1                                                    | VDD/GND    |

| 23      | CS2   | Analog Input              | Capacitive sensor input 2                                                    | VDD/GND    |

| 24      | CS3   | Analog Input              | Capacitive sensor input 3                                                    | VDD/GND    |

# 2.2 ANSG08SL (24 SOP package)

| Pin No. | Name | I/O                       | Description                                                                  | Protection |

|---------|------|---------------------------|------------------------------------------------------------------------------|------------|

| 1       | CS6  | Analog Input              | Capacitive sensor input 6                                                    | VDD/GND    |

| 2       | CS7  | Analog Input              | Capacitive sensor input 7                                                    | VDD/GND    |

| 3       | CS8  | Analog Input              | Capacitive sensor input 8                                                    | VDD/GND    |

| 4       | SCL  | Digital Input             | I <sup>2</sup> C clock input                                                 | VDD/GND    |

| 5       | SDA  | Digital<br>Input / Output | I <sup>2</sup> C data input-output<br>Open drain NMOS structure              | VDD/GND    |

| 6       | GND  | Ground                    | Supply ground                                                                | VDD        |

| 7       | RND  | Analog Input              | Radio frequency Noise Detection pin                                          | VDD/GND    |

| 8       | D1   | Digital Output            | Parallel output of CS1<br>LED PWM drive output1<br>Open drain NMOS structure | VDD/GND    |

| 9       | D2   | Digital Output            | Parallel output of CS2<br>LED PWM drive output2<br>Open drain NMOS structure | VDD/GND    |

| 10      | D3   | Digital Output            | Parallel output of CS3<br>LED PWM drive output3<br>Open drain NMOS structure | VDD/GND    |

| 11      | D4   | Digital Output            | Parallel output of CS4<br>LED PWM drive output4<br>Open drain NMOS structure | VDD/GND    |

| 12      | D5   | Digital Output            | Parallel output of CS5<br>LED PWM drive output5<br>Open drain NMOS structure | VDD/GND    |

| 13      | D6   | Digital Output            | Parallel output of CS6<br>LED PWM drive output6<br>Open drain NMOS structure | VDD/GND    |

| 14      | D7   | Digital Output            | Parallel output of CS7<br>LED PWM drive output7<br>Open drain NMOS structure | VDD/GND    |

| 15      | D8   | Digital Output            | Parallel output of CS8 LED PWM drive output8 Open drain NMOS structure       | VDD/GND    |

| 16      | LCAP | Analog Output             | Internal LDO Output                                                          | VDD/GND    |

| 17      | INT  | Digital Output            | Touch sensing interrupt output Open drain NMOS structure                     | VDD/GND    |

| 18      | VDD  | Power                     | Power (3.0V~5.5V)                                                            | GND        |

| 19      | CS1  | Analog Input              | Capacitive sensor input 1                                                    | VDD/GND    |

| 20      | CS2  | Analog Input              | Capacitive sensor input 2                                                    | VDD/GND    |

| 21      | CS3  | Analog Input              | Capacitive sensor input 3                                                    | VDD/GND    |

| 22      | CS4  | Analog Input              | Capacitive sensor input 4                                                    | VDD/GND    |

| 23      | N.C. | _                         | -                                                                            | VDD/GND    |

| 24      | CS5  | Analog Input              | Capacitive sensor input 5                                                    | VDD/GND    |

#### 2.3 ANSG08SH (16 SOP package)

| Pin No. | Name  | I/O                       | Description                                                                  | Protection |

|---------|-------|---------------------------|------------------------------------------------------------------------------|------------|

| 1       | CS3   | Analog Input              | Capacitive sensor input 3                                                    | VDD/GND    |

| 2       | CS4   | Analog Input              | Capacitive sensor input 4                                                    | VDD/GND    |

| 3       | CS5   | Analog Input              | Capacitive sensor input 5                                                    | VDD/GND    |

| 4       | CS6   | Analog Input              | Capacitive sensor input 6                                                    | VDD/GND    |

| 5       | CS7   | Analog Input              | Capacitive sensor input 7                                                    | VDD/GND    |

| 6       | CS8   | Analog Input              | Capacitive sensor input 8                                                    | VDD/GND    |

| 7       | SCL   | Digital Input             | I <sup>2</sup> C clock input                                                 | VDD/GND    |

| 8       | SDA   | Digital<br>Input / Output | I <sup>2</sup> C data input-output<br>Open drain NMOS structure              | VDD/GND    |

| 9       | GND   | Ground                    | Supply ground                                                                | VDD        |

| 10      | R.N.D | Analog Input              | Radio frequency Noise Detection pin                                          | VDD/GND    |

| 11      | D1    | Digital Output            | Parallel output of CS1<br>LED PWM drive output1<br>Open drain NMOS structure | VDD/GND    |

| 12      | INT   | Digital Output            | Touch sensing interrupt output Open drain NMOS structure                     | VDD/GND    |

| 13      | VDD   | Power                     | Power (3.0V~5.5V)                                                            | GND        |

| 14      | LCAP  | Analog Output             | Internal LDO Output                                                          | VDD/GND    |

| 15      | CS1   | Analog Input              | Capacitive sensor input 1                                                    | VDD/GND    |

| 16      | CS2   | Analog Input              | Capacitive sensor input 2                                                    | VDD/GND    |

# 3 Absolute Maximum Rating

Battery supply voltage 6V

Maximum voltage on any pin VDD+0.3

Maximum current on any PAD 100mA

Power Dissipation 800mW

Storage Temperature  $-50 \sim 150^{\circ}$ C

Operating Temperature  $-20 \sim 75^{\circ}$ C

Junction Temperature 150°C

Note: Unless and 511

Note: Unless any other command is noted, all above are operated in normal temperature.

# 4 ESD & Latch-up Characteristics

#### 4.1 ESD Characteristics

| Mode  | Polarity  | Max                                      | Reference            |

|-------|-----------|------------------------------------------|----------------------|

|       |           | 7500V                                    | VDD                  |

| H.B.M | Pos / Neg | 7500V                                    | VSS                  |

|       |           | 7500V                                    | P to P               |

|       |           | 550V                                     | VDD                  |

| M.M   | Pos / Neg | 550V                                     | VSS                  |

|       |           | 7500V P to P 550V VDD Pos / Neg 550V VSS | P to P               |

| C.D.M | Pos / Neg | 1000V                                    | Field Induced Charge |

### 4.2 Latch-up Characteristics

| Mode               | Polarity | Max    | Reference |

|--------------------|----------|--------|-----------|

| l Test             | Positive | 100mA  |           |

| rrest              | Negative | -100mA | JESD78A   |

| V supply over 5.0V | Positive | 8.25V  |           |

# **Electrical Characteristics**

• Note:  $V_{DD}$ =3.3V, Typical system frequency (Unless otherwise noted),  $T_A$  = 25°C

| Characteristics                            | Symbol               | Test Condition                              |                                    | Min                  | Тур  | Max                  | Units |

|--------------------------------------------|----------------------|---------------------------------------------|------------------------------------|----------------------|------|----------------------|-------|

| Power supply requirement ar                | nd current c         | onsumpt                                     | ion                                |                      |      |                      |       |

| Operating voltage                          | $V_{DD}$             |                                             |                                    | 3.0                  |      | 5.5                  | V     |

| Current consumption                        | $I_{DD}$             | V <sub>DD</sub> = 3.3V Standby state @10MHz |                                    | -                    | 0.50 | _                    | mA    |

| Reset and input level                      |                      |                                             |                                    |                      |      |                      |       |

| Internal reset voltage                     | $V_{DD\_RST}$        | $T_A = 25$                                  | 5℃                                 | _                    | 2.6  | -                    | V     |

| Input high level                           | VIH                  |                                             | ≤ +5µA                             | V <sub>DD</sub> *0.6 |      | V <sub>DD</sub> +0.3 | V     |

| Input low level                            | VIL                  | <sub> L</sub>   ≤                           | ≤ +5µA                             | -0.3                 |      | V <sub>DD</sub> *0.3 | V     |

| Self calibration time after                |                      | Slow ca                                     | Slow calibration speed             |                      | 100  | _                    |       |

| •                                          | $T_CAL$              | Norma                                       | calibration speed                  | _                    | 80   | _                    | msec  |

| system reset                               |                      | Fast ca                                     | alibration speed                   | _                    | 60   | -                    |       |

| Internal Pull Up resister of SDA, SCL, INT | $R_{\text{P/U}}$     |                                             |                                    | -                    | 30   | _                    | kΩ    |

| Touch sensing performance                  |                      |                                             |                                    |                      |      | •                    |       |

| Minimum detective capacitance difference   | $\Delta C_{MIN}$     |                                             |                                    | 0.1                  | _    | _                    | pF    |

| Sense input capacitance range <sup>1</sup> | Cs                   |                                             |                                    | -                    | _    | 50                   | рF    |

| Output impedance                           | 7 -                  | $\Delta C > \Delta$                         | C <sub>MIN</sub>                   | _                    | 12   | -                    | 0     |

| (open drain)                               | Zo                   | $\Delta C < \Delta$                         | CMIN                               | _                    | 30M  | _                    | Ω     |

| System performance                         |                      |                                             |                                    |                      |      | •                    |       |

| Max. output current (LED drive current)    | I <sub>OUT</sub>     | Per uni                                     | t drive output port                | -                    | -    | 8.0                  | mA    |

| LED PWM control <sup>2</sup>               | N <sub>PWM</sub>     |                                             |                                    | _                    | 16   | _                    | step  |

| Sensitivity control <sup>3</sup>           |                      |                                             |                                    | -                    | 256  | _                    | step  |

|                                            |                      | _                                           |                                    | _                    |      |                      |       |

| Max. I <sup>2</sup> C SCL clock speed      | f <sub>SCL_MAX</sub> | Maxim                                       | um internal I <sup>2</sup> C clock | -                    | ı    | 2                    | MHz   |

| Touch expired time                         | T <sub>EX</sub>      | Norma                                       | calibration speed                  | _                    | 30   | -                    | sec   |

Refer to the chapter 8.2.10. Sensitivity register

The sensitivity can be decreased with higher parallel capacitance of CS pin including parasitic capacitance made by neighbor GND or other pattern. The series resistor(under  $1k\Omega$ ) of CS can be used in noisy condition to avoid mal-function Prom external surge and ESD.

Refer to the chapter 8.2.13. LED luminance control register

# 6 ANSG08 Implementation

### 6.1 Typical current consumption

ANSG08 uses internal bias circuit, so internal clock frequency and current consumption is fixed and no external bias circuit is needed. Internal clock frequency and calibration speed can be changed by I<sup>2</sup>C register setting<sup>4</sup>. Faster calibration speed needs more current consumption than normal or slower calibration speed. Slow calibration speed isn't recommended if it has not problem of current consumption.

Internal bias circuit can make the circuit design simple and reduce external components.

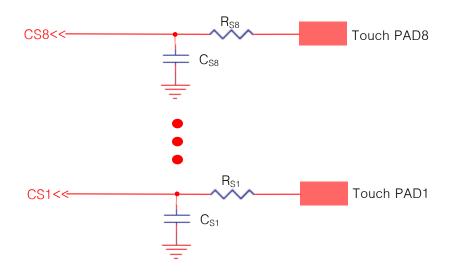

#### 6.2 CS implementation

ANSG08 has 256 step selections of sensitivity and internal surge protection resister. Sensitivity of each sensing channel (CS) can be independently controlled on others. External components of CS pin such as series resistor or parallel capacitor isn't necessary. The parallel parasitic capacitance of CS pins caused by touch line, touch pad and neighbor GND or other pattern may affect sensitivity. The sensitivity will be decreased when bigger parallel parasitic capacitance of CS pin is added.

Parallel capacitor ( $C_{S1\sim S8}$ ) of CS pin is useful in case of detail sensitivity mediation is required such as for complementation sensitivity difference between channels. Same as above parallel parasitic capacitance, sensitivity will be decreased when a big value of parallel capacitor ( $C_{S1\sim S8}$ ) is used. Under 50pF capacitor can be used as sensitivity meditation capacitor and a few pF is usually used. The  $R_S$ , serial connection resistor of CS pins, may be used to avoid mal-function from external surge and ESD. (It might be optional.) From 200 $\Omega$  to 1k $\Omega$  is recommended for  $R_S$ . Refer to below CS pins application figure.

<sup>&</sup>lt;sup>4</sup> Refer to 8.2.6 Clock control register.

The ANSG08 has eight independent touch sensor input from CS1 to CS8. The internal touch decision process of each channel is separated from others. Therefore eight channel touch key board application can be designed by using only one ANSG08 without coupling problems.

The size and shape of PAD might have influence on the sensitivity. The sensitivity will be optimal when the size of PAD is approximately an half of the first knuckle (it's about 10 mm x 7 mm). The connection line of CS to touch PAD is recommended to be routed as short as possible to prevent from abnormal touch detect caused by connection line. The unused CS pin should not be connected with the ground.

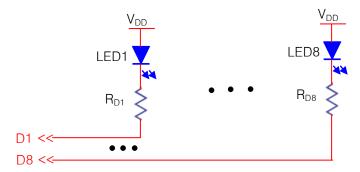

### 6.3 LED drive implementation

ANSG08 has a function to control the LED using D1~D8 ports. For using D1~D8 as LED driver ports, LEDs and resisters must be equipped as below figure, and write the 'port\_mode" register<sup>5</sup> as '1'. D1 ~ D8 ports can drive LEDs by 'PWM\_ctrlx' register<sup>6</sup> control. ANSG08 can drive up to 8 LED as below method.

#### 6.4 Parallel output

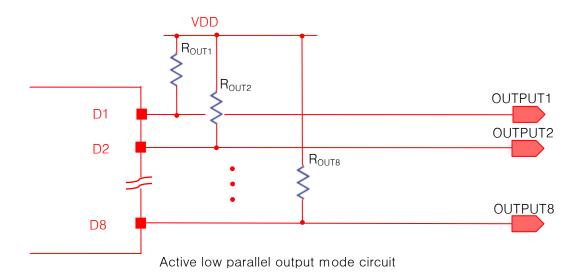

ANSG08 acts as active low parallel output mode. Parallel output ports (D1~D8) have an open drain NMOS structure. For this reason, the parallel output mode of ANSG08 needs  $R_{OUT}$  as below figures. The maximum output drive current is 8mA, so over a few  $k\Omega$  must be used as  $R_{OUT}$ . Normally  $10k\Omega$  is used as  $R_{OUT}$ .

<sup>&</sup>lt;sup>6</sup> Refer to the chapter 8.2.13. LED luminance control register

**AD Semiconductor Confidential**

<sup>&</sup>lt;sup>5</sup> Refer to the chapter 8.2.14. Port mode control register

# 6.5 INT (Interrupt output) Implementation

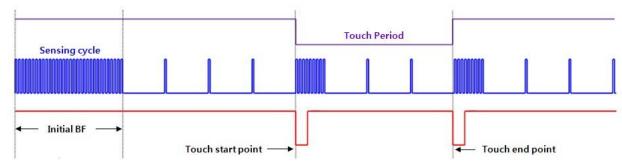

An INT pin is for the touch sensing interrupt output. The interrupt pulse is generated only during short period of every each channel touch start point and touch end point. Interrupt pulse has logical low level. INT has NMOS open drain structure and internal pull-up resister of which value is 30kΩ typical.

# 6.6 Change initial reset register values (EEPROM writing)

ANSG08 has an EEPROM.

So, initial reset register values can be rewritten.

The erase and write cycle endurance of the EEPROM is at least 300,000.

There are three operation modes about EEPROM read/write. These are automatically load operation mode, writing operation mode and reading operation mode.

#### Automatically load operation mode

After power reset, ANSG08 start to read the data of 00H and 7FH address in EEPROM.

ANSG08 automatically loads the data of the EEPROM when the data of 00H is 0xAA and the data of 7FH is 0x55. And then ANSG08 is starting to work with control register values that are loaded from EEPROM. ANSG08 is working with initial control register value when the data of 00H isn't 0xAA or the data of 7FH isn't 0x55.

#### Writing operation mode

EEPROM writing provides the flexible reset register values that control all the operation options of ANSG08. So, additional communication programs on MCU for operation option select or register value setting aren't required.

There is only one writing operation mode, all bytes writing mode.

The 'write\_all' bit of 'prom\_cmd' register' has to be '1' because all bytes writing mode is activated. And then user can write all registers frame data on EEPROM. Read or write command register is 'prom\_cmd' registers and user can start writing by 'wr\_start' bit of 'prom\_cmd' register setting as '1'. This 'wr\_start' bit of 'prom\_cmd' register is recovered as '0' at ending of writing.

#### Reading operation mode

When EEPROM data is required to be read, user can read all EEPROM date by reading operation. When the 'read\_all' bit of 'prom\_cmd' register is '0', user can read one byte data that is written on selected address of EEPROM.

When the 'read\_all' bit of 'prom\_cmd' register is '1', user can read all data on EEPROM.

EEPROM read start command bit is 'rd\_start' bit of 'prom\_cmd' register. When the 'rd\_start' bit of 'prom\_cmd' register is '1', ANSG08 starts to read. This 'rd\_start' bit of 'prom\_cmd' register is recovered as '0' at ending of reading.

#### 6.7 SCL. SDA implementation

SCL is  $I^2C$  clock input and SDA is  $I^2C$  data input-output. These ports have internal pull-up resistor. SCL has Schmitt trigger input structure to prevent clock signal from being broken. Maximum supported  $I^2C$  clock frequency is 2MHz. SDA has NMOS open drain structure and internal pull-up resister of which value is  $30k\Omega$  typical. So, according to communication speed a few  $k\Omega$  resister must be used as pull-up resister for proper data pulse rising time. For more details refer to 'Chapter 7.  $I^2C$  Interface'.

$<sup>^{7}</sup>$  Refer to the chapter 8.2.15. EEPROM control register.

**AD Semiconductor Confidential**

# 7 I<sup>2</sup>C Interface

# 7.1 I<sup>2</sup>C Enable / Disable

If the SDA or SCL signal goes to low, I<sup>2</sup>C control block is enabled automatically. And if the SDA and SCL signal maintain high during about 2 us, I<sup>2</sup>C control block is disabled automatically also.

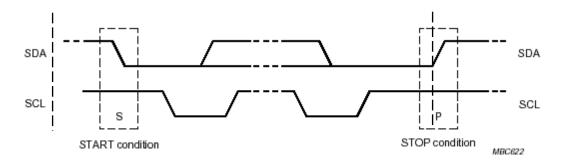

# 7.2 Start & stop condition

- Start Condition (S)

- Stop Condition (P)

- Repeated Start (Sr)

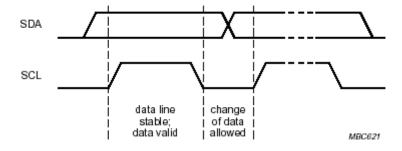

# 7.3 Data validity

The SDA should be stable when the SCL is high and the SDA can be changed when the SCL is low.

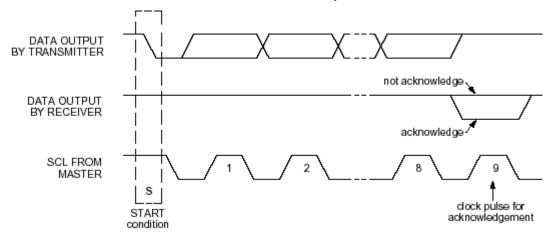

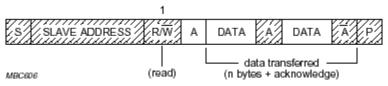

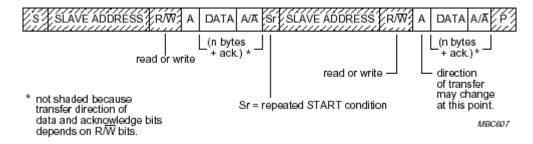

#### 7.4 Byte format

The byte structure is composed with 8Bit data and an acknowledge signal.

#### 7.5 Acknowledge

It is a check bit whether the receiver gets the data from the transmitter without error or not. The receiver will write '0' when it received the data successfully and '1' if not.

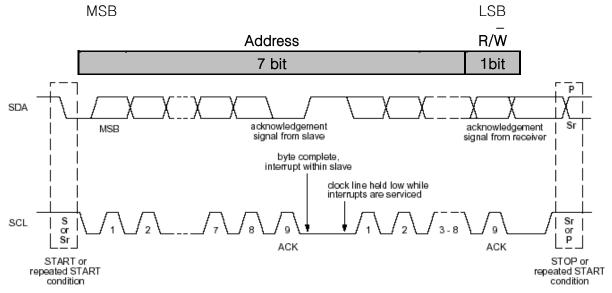

# 7.6 First byte

#### 7.6.1 Slave address

It is the first byte from the start condition. It is used to access the slave device. The initial chip address of ANSG08 is '48' hex number and the chip address is possible to change with "l<sup>2</sup>C Address of ANSG08" register<sup>8</sup>.

# 7.6.2 R/W

The direction of data is decided by the bit and it follows the address data.

$<sup>^{8}</sup>$  Refer to the chapter 8.2.4. I2C address of ANSG08.

# 7.7 Transferring data

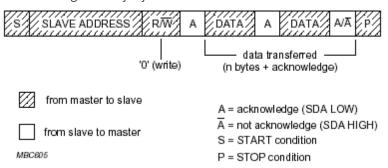

## 7.7.1 Write operation

The byte sequence is as follows:

- 1. The first byte gives the device address plus the direction bit (R/W = 0).

- 2. The second byte contains the internal address of the first register to be accessed.

- 3. The next byte is written in the internal register. Following bytes are written in successive internal registers.

- 4. The transfer lasts until stop conditions are encountered.

- 5. The ANSG08 acknowledges every byte transfer.

#### 7.7.2 Read operation

The address of the first register to read is programmed in a write operation without data, and terminated by the stop condition. Then, another start is followed by the device address and R/W= 1. All following bytes are now data to be read at successive positions starting from the initial address.

### 7.7.3 Read/Write Operation

# 7.8 I<sup>2</sup>C write and read operations in normal mode

The following figure represents the I<sup>2</sup>C normal mode write and read registers.

Write register 0x00 to 0x01 with data AA and BB

From Master to Slave

| Start | Device<br>Address 0x48 | ACK     | Register<br>Address 0x00 | ACK | Data AA      | ACK | Data BB | ACK | Stop |

|-------|------------------------|---------|--------------------------|-----|--------------|-----|---------|-----|------|

| Pood  | rogistor 0x00          | and Ove | 11                       |     |              |     |         |     |      |

| neau  | register 0x00          | and uxu | /                        |     |              |     |         |     |      |

| Start | Device<br>Address 0x48 | ACK     | Register<br>Address 0x00 | ACK | Stop         |     |         |     |      |

|       |                        |         |                          |     |              |     |         |     |      |

| Start | Device<br>Address 0x49 | ACK     | Data Read AA             | ACK | Data Read BB | ĀCK | Stop    |     |      |

|       | 1                      |         |                          |     |              |     |         |     |      |

From Slave to Master

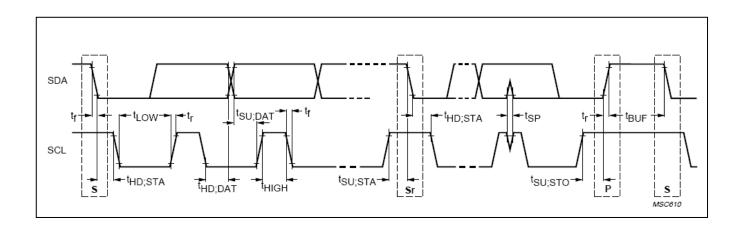

# 7.9 I<sup>2</sup>C Timing Diagram

| DADAMETED                                                | CVMDOI  | 1001   | kbps | 4001                 | kbps                 | TIMITE |

|----------------------------------------------------------|---------|--------|------|----------------------|----------------------|--------|

| PARAMETER                                                | SYMBOL  | MIN.   | MAX. | MIN.                 | MAX.                 | UNIT   |

| Hold time (repeated)START condition.                     | tHD;STA | 4.0    | -    | 0.6                  | -                    | us     |

| LOW period of the SCL clock                              | tLOW    | 4.7    | -    | 1.3                  | -                    | us     |

| HIGH period of the SCL clock                             | tHIGH   | 4.0    | -    | 0.6                  | -                    | us     |

| Set-up time for a repeated START condition               | tSU;STA | 4.7    | -    | 0.6                  | -                    | us     |

| Data hold time                                           | tHD;DAT | 1.0    | -    | -                    | -                    | us     |

| Data set-up time                                         | tSU;DAT | 250    | -    | 100                  | -                    | ns     |

| Rise time of both SDA and SCL signals                    | tr      | -      | 1000 | 20                   | 300                  | ns     |

| Fall time of both SDA and SCL signals                    | tf      | -      | 300  | 20                   | 300                  | ns     |

| Set-up time for STOP condition                           | tSU;STO | 4.0    | -    | 0.6                  | -                    | us     |

| Bus free time between a STOP and START condition         | tBUF    | 4.7    | -    | 1.3                  | -                    | us     |

| Noise margin at the LOW level for each connected device  | VnL     | 0.1VDD | -    | 0.1VDD               | -                    | V      |

| Noise margin at the HIGH level for each connected device | VnH     | 0.2VDD | -    | 0.2VDD               | -                    | V      |

| Input Low level                                          |         |        |      | 0                    | V <sub>DD</sub> *0.2 | V      |

| Input High level                                         |         |        |      | V <sub>DD</sub> *0.8 | $V_{DD}$             | V      |

# 8 ANSG08 Control Register List

- Note: The unused bits (defined as reserved) in I<sup>2</sup>C registers must be kept to zero.

- Note: The reset value of ANSG08 can be changed by EEPROM writing.

# 8.1 I<sup>2</sup>C Register Map

| Name                   | Addr. | Reset<br>Value |         |                   |           | Bit name of         | each bytes        |                |          |              |

|------------------------|-------|----------------|---------|-------------------|-----------|---------------------|-------------------|----------------|----------|--------------|

| Name                   | (Hex) | (Bin)          | Bit7    | Bit6              | Bit5      | Bit4                | Bit3              | Bit2           | Bit1     | Bit0         |

| prom_set1              | 00H   | 0000 0000      |         |                   |           | eepror              | m_set1            |                |          |              |

| ch_enable<br>/soft_rst | 01H   | 1111 1111      | ch8_en  | ch7_en            | ch6_en    | ch5_en ch4_en       |                   | ch3_en         | ch2_en   | ch1_en       |

| i2c_id                 | 06H   | 0100 1000      |         |                   |           | i2c_id              |                   |                |          | wr_bit       |

| output                 | 2AH   | 0000 0000      | o_ch8   | o_ch7             | o_ch6     | o_ch5               | o_ch4             | o_ch3          | o_ch2    | o_ch1        |

| clock_ctrl             | 34H   | 0000 0110      |         | init_cal_opt      |           | -                   | clk               | _sel           | rb       | _sel         |

| global_ctrl1           | 36H   | 0100 1100      |         | response_off_ctrl |           |                     | response_ctrl     |                | bf_mode  | software_rst |

| state_count            | 37H   | 0101 1111      | 0       | 1                 | 0         |                     |                   | cal_pre_scaler |          |              |

| global_ctrl2           | 38H   | 0001 1110      | imp_sel | sin_multi_mode    |           | cal_ho              | ld_time           |                | 1        | clk_off      |

| sensitivity1           | 39H   | 0001 1100      |         |                   |           | sensiti             | vity01            |                |          |              |

| sensitivity2           | 3AH   | 0001 1100      |         |                   |           | sensiti             | vity02            |                |          |              |

| sensitivity3           | 3BH   | 0001 1100      |         |                   |           | sensiti             | vity03            |                |          |              |

| sensitivity4           | 3CH   | 0001 1100      |         |                   |           | sensiti             | vity04            |                |          |              |

| sensitivity5           | 3DH   | 0001 1100      |         | sensitivity05     |           |                     |                   |                |          |              |

| sensitivity6           | 3EH   | 0001 1100      |         | sensitivity06     |           |                     |                   |                |          |              |

| sensitivity7           | 3FH   | 0001 1100      |         |                   |           | sensiti             | vity07            |                |          |              |

| sensitivity8           | 40H   | 0001 1100      |         |                   |           | sensiti             | vity08            |                |          |              |

| cal_speed              | 41H   | 0000 0000      | rnd_    | bf_up             | rnd_bf    | _down               | sen_b             | of_up          | sen_b    | f_down       |

| cal_BS_speed           | 42H   | 0000 0000      | rnd_    | bs_up             | rnd_bs    | _down               | sen_bs_up sen_bs_ |                |          | s_down       |

| PWM_ctrl1              | 43H   | 0000 0000      |         | pwm               | _d2       |                     |                   | pwn            | n_d1     |              |

| PWM_ctrl2              | 44H   | 0000 0000      |         | pwm               | _d4       |                     |                   | pwn            | n_d3     |              |

| PWM_ctrl3              | 45H   | 0000 0000      |         | pwm               | _d6       |                     |                   | pwn            | n_d5     |              |

| PWM_ctrl4              | 46H   | 0000 0000      |         | pwm               | _d8       |                     |                   | pwn            | n_d7     |              |

| port_mode              | 4FH   | 0000 0000      | pmod_d8 | pmod_d7           | pmod_d6   | pmod_d5             | pmod_d4           | pmod_d3        | pmod_d2  | pmod_d1      |

| rd_ch_H1               | 50H   | 0000 0000      |         |                   |           | rd_cl               | n_H1              |                |          |              |

| rd_ch_L1               | 51H   | 00             | =       | =                 | =         | -                   | =                 | =              | rd_c     | :h_L1        |

| Percent_H              | 52H   | 0000 0000      |         |                   |           | touch_perd          | ent[24:17]        |                |          |              |

| Percent_M              | 53H   | 0000 0000      |         |                   |           | touch_per           | cent[16:9]        |                |          |              |

| Percent_L              | 54H   | 0000 0000      |         |                   |           | touch_pe            | rcent[8:1]        |                |          |              |

| rd_ch_H2               | 56H   | 0000 0000      |         |                   |           | rd_cl               | n_H2              |                |          |              |

| rd_ch_L2               | 57H   | 0              | =       | =                 | =         | =                   | Ξ                 | T.             | rd_d     | :h_L2        |

| prom_cmd               | 5CH   | 0000           | =       | =                 | write_all | read_all            | Ξ                 | T.             | wr_start | rd_start     |

| prom_addr              | 5FH   | 0000 0000      | =       |                   |           |                     | eeprom_addr       |                |          |              |

| prom_wr_data           | 60H   | 0000 0000      |         |                   |           | eeprom_             | _wr_data          |                |          |              |

| prom_rd_data           | 61H   |                |         |                   |           | eeprom <sub>.</sub> | _rd_data          |                |          |              |

| prom_set2              | 7FH   | 0000 0000      |         |                   |           | eepror              | n_set2            |                |          |              |

#### 8.2 Details

#### 8.2.1 EEPROM Set 1

Type: R/W

| Address | Register Name | Bit7 | Bit6 | Bit5 | Bit4   | Bit3   | Bit2 | Bit1 | Bit0 |

|---------|---------------|------|------|------|--------|--------|------|------|------|

| 00h     | prom_set1     |      |      |      | eepror | m_set1 |      |      |      |

#### **Description**

The first flag byte for the valid data of EEPROM. If the data of this address isn't 0xAA on EEPROM, all data on EEPROM are invalid. So, the data of this address must be written by 0xAA if user wants to change the reset value using EEPROM.

| Bit name    | Reset value | Function                                                        |

|-------------|-------------|-----------------------------------------------------------------|

| eeprom_set1 | 00000000    | 10101010 : EEPROM data is valid others : EEPROM data is invalid |

### 8.2.2 Channel enable / reset register

Type: R/W

| Address | Register Name          | Bit7   | Bit6   | Bit5   | Bit4   | Bit3   | Bit2   | Bit1   | Bit0   |

|---------|------------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| 01h     | ch_enable<br>/soft_rst | ch8_en | ch7_en | ch6_en | ch5_en | ch4_en | ch3_en | ch2_en | ch1_en |

#### **Description**

Enable, disable and reset of each channel control register.

| Bit name | Reset value | Function                                                                                                                                              |

|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| chx_en   | 1           | Channel enable / disable and Channel reset (chx_en is control bit for CSx channel)  0 : Channel disable and sensing channel reset  1 : Channel enable |

# 8.2.3 I<sup>2</sup>C address of ANSG08

Type: R/W

| Address | Register Name | Bit7 | Bit6 | Bit5 | Bit4   | Bit3 | Bit2 | Bit1 | Bit0   |

|---------|---------------|------|------|------|--------|------|------|------|--------|

| 06h     | i2c_id        |      |      |      | i2c_id |      |      |      | wr_bit |

#### **Description**

Chip address of ANSG08 control register. User can change this address value with EEPROM write. During reset period EEPROM data is loaded to registers.

| Bit name | Reset value | Function                                                           |

|----------|-------------|--------------------------------------------------------------------|

| wr_bit   | 0           | Write/Read address selection - 0 : Write address, 1 : Read address |

| i2c_id   | 0100100     | Chip address of ANSG08.                                            |

# 8.2.4 Output data

Type: R

| Address | Register Name | Bit7  | Bit6  | Bit5  | Bit4  | Bit3  | Bit2  | Bit1  | Bit0  |

|---------|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 2Ah     | output        | o_ch8 | o_ch7 | o_ch6 | o_ch5 | o_ch4 | o_ch3 | o_ch2 | o_ch1 |

#### **Description**

The output data register from channel 1 to channel 8.

| Bit name | Reset value | Function                                                                         |

|----------|-------------|----------------------------------------------------------------------------------|

| o_chx    | 0           | o_chx is output bit for CSx channel  4 0: No touch detected  4 1: Touch detected |

#### 8.2.5 Clock control register

Type: R/W

| Address | Register Name | Bit7 | Bit6         | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------|---------------|------|--------------|------|------|------|------|------|------|

| 34h     | clock_ctrl    |      | init_cal_opt |      | -    | clk  | _sel | rb_  | _sel |

#### **Description**

This register controls the global options of ANSG08

| Bit name     | Reset value | Function                                                              |

|--------------|-------------|-----------------------------------------------------------------------|

|              |             | ANSG08 provides three internal calibration speeds with this register. |

| rb sel       | 10          | ↓ 00, 01 : Fast                                                       |

| 10_501       |             | ↓ 10 : Normal                                                         |

|              |             | <b>↓</b> 11 : Slow                                                    |

|              |             | ANSG08 provides four internal calibration speeds with this register.  |

|              |             | <b>♣</b> 00 : Fast                                                    |

| clk_sel      | 01          | ♣ 01 : Normal                                                         |

|              |             | <b>↓</b> 10 : Slow                                                    |

|              |             | ↓ 11 : Slowest                                                        |

| init cal ont | 000         | To control the initial BF time.                                       |

| init_cal_opt | 000         | ↓ init_cal_opt[2:0] * 5 + 5 (Seconds)                                 |

# 8.2.6 Global option control register 1

Type: R/W

| Address | Register Name | Bit7 | Bit6         | Bit5 | Bit4 | Bit3          | Bit2 | Bit1    | Bit0             |

|---------|---------------|------|--------------|------|------|---------------|------|---------|------------------|

| 36h     | global_ctrl1  | res  | sponse_off_c | etrl |      | response_ctrl |      | bf_mode | software<br>_rst |

#### **Description**

This register controls the global options of ANSG08

| Bit name          | Reset value | Function                                                                                                           |

|-------------------|-------------|--------------------------------------------------------------------------------------------------------------------|

| software_rst      | 0           | Software reset control bit. Reset the data of all sensing channel.  4 0: No reset 4 1: Reset                       |

| bf_mode           | 0           | Operation mode selection 0: Normal mode 1: BF mode                                                                 |

| response_ctrl     | 011         | Numbers of continuous touch detections for touch decision.  response_ctrl[2:0] + 1 (Maximum time : 7)              |

| response_off_ctrl | 010         | Numbers of continuous touch off detections for touch off decision.  response_off_ ctrl[2:0] + 1 (Maximum time : 7) |

## 8.2.7 State count control register

Type: R/W

| Address | Register Name | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2          | Bit1 | Bit0 |

|---------|---------------|------|------|------|------|------|---------------|------|------|

| 37h     | state_count   | 0    | 1    | 0    |      | (    | cal_pre_scale | er   |      |

#### **Description**

Register to set the pre-scaler for the calibration speed.

| Bit name       | Reset value | Function                                                                           |

|----------------|-------------|------------------------------------------------------------------------------------|

| cal_pre_scaler | 1 1111      | The pre-scaler for the calibration speed.    cal_pre_scaler[4:0] x 16ms (1-period) |

# 8.2.8 Global option control register 2

Type: R/W

| Address | Register Name | Bit7    | Bit6               | Bit5 | Bit4    | Bit3    | Bit2 | Bit1 | Bit0    |

|---------|---------------|---------|--------------------|------|---------|---------|------|------|---------|

| 38h     | global_ctrl2  | imp_sel | sin_mult<br>i_mode |      | cal_hol | ld_time |      | -    | clk_off |

#### **Description**

This register controls the global options of ANSG08.

| Bit name           | Reset value | Function                                                                                                                                                   |

|--------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk_off            | 0           | System clock off control bit.  4 0: Not clock off 4 1: Clock off                                                                                           |

| cal_hold_tim<br>e  | 0111        | Output expiration Time control.  cal_hold_time[3:0] x 4 ( seconds)  The output expiration time is infinite when the data of the "cal_hold_time" is "0000". |

| sin_multi_mo<br>de | 0           | Single/Multi output operation mode selection bit.  4 0: Single output mode  4 1: Multi output mode                                                         |

| imp_sel            | 0           | Impedance of the sensing wire of all channels control bit.  4 0: High impedance  4 1: Low impedance except sensing period.                                 |

# 8.2.9 Sensitivity register

Type: R/W

| Address | Register Name | Bit7 | Bit6          | Bit5 Bit4 Bit3 Bit2 Bit1 |         |        |  |  |  |  |  |

|---------|---------------|------|---------------|--------------------------|---------|--------|--|--|--|--|--|

| 39H     | sensitivity1  |      | sensitivity01 |                          |         |        |  |  |  |  |  |

| ЗАН     | sensitivity2  |      | sensitivity02 |                          |         |        |  |  |  |  |  |

| ЗВН     | sensitivity3  |      | sensitivity03 |                          |         |        |  |  |  |  |  |

| 3СН     | sensitivity4  |      |               |                          | sensiti | vity04 |  |  |  |  |  |

| 3DH     | sensitivity5  |      |               |                          | sensiti | vity05 |  |  |  |  |  |

| 3ЕН     | sensitivity6  |      |               |                          | sensiti | vity06 |  |  |  |  |  |

| 3FH     | sensitivity7  |      | sensitivity07 |                          |         |        |  |  |  |  |  |

| 40H     | sensitivity8  |      |               |                          | sensiti | vity08 |  |  |  |  |  |

#### **Description**

This register controls the global options of ANSG08.

| Bit name      | Reset value | Function                                                                                       |

|---------------|-------------|------------------------------------------------------------------------------------------------|

| sensitivity0x | 0001 1100   | Sensitivities of each channel. Sensitivity of CSx channel: {(sensitivity0x[7:0] x 0.025)} (%). |

# 8.2.10 Calibration speed control register

Type: R/W

| Address | Register Name | Bit7 | Bit6  | Bit5   | Bit4  | Bit3  | Bit2  | Bit1   | Bit0   |

|---------|---------------|------|-------|--------|-------|-------|-------|--------|--------|

| 41H     | cal_speed     | rnd_ | bf_up | rnd_bf | _down | sen_t | of_up | sen_bf | f_down |

#### **Description**

Calibration speed can be controlled by this 'cal\_speed' register at BF mode.

| Bit name    | Reset value | Function                                                                                                               |

|-------------|-------------|------------------------------------------------------------------------------------------------------------------------|

| sen_bf_down | 00          | Sense channel down calibration speed at BF mode control bits.  4 00 : Fastest  4 01 : Fast  4 10 : Normal  4 11 : Slow |

| sen_bf_up   | 00          | Sense channel up calibration speed at BF mode control bits.  4 00 : Fastest 4 01 : Fast 4 10 : Normal 4 11 : Slow      |

| rnd_bf_down | 00          | RND channel down calibration speed at BF mode control bits.  4 00 : Fastest 4 01 : Fast 4 10 : Normal 4 11 : Slow      |

| rnd_bf_up   | 00          | RND channel up calibration speed at BF mode control bits.  4 00 : Fastest  4 01 : Fast  4 10 : Normal  4 11 : Slow     |

# " Free from Common Mode Noise " ANSG08 (8-CH Auto Sensitivity Calibration Capacitive Touch Sensor)

# 8.2.11 Calibration speed control register at BS mode

Type: R/W

| Address | Register Name | Bit7  | Bit6  | Bit5   | Bit4  | Bit3  | Bit2  | Bit1   | Bit0   |

|---------|---------------|-------|-------|--------|-------|-------|-------|--------|--------|

| 42H     | cal_BS_speed  | rnd_l | bs_up | rnd_bs | _down | sen_l | os_up | sen_bs | s_down |

### **Description**

Calibration speed can be controlled by this 'cal\_BS\_speed' register at BS mode.

| Bit name    | Reset value | Function                                                                                                            |

|-------------|-------------|---------------------------------------------------------------------------------------------------------------------|

| sen_bs_down | 00          | Sense channel down calibration speed at BS mode control bits.  4 00 : Fastest 4 01 : Fast 4 10 : Normal 4 11 : Slow |

| sen_bs_up   | 00          | Sense channel up calibration speed at BS mode control bits.  4 00 : Fastest 4 01 : Fast 4 10 : Normal 4 11 : Slow   |

| rnd_bs_down | 00          | RND channel down calibration speed at BS mode control bits.  4 00 : Fastest 4 01 : Fast 4 10 : Normal 4 11 : Slow   |

| rnd_bs_up   | 00          | RND channel up calibration speed at BS mode control bits.  4 00 : Fastest 4 01 : Fast 4 10 : Normal 4 11 : Slow     |

# 8.2.12 LED luminance control register

Type: R/W

| Address | Register Name | Bit7 | Bit6          | Bit5 | Bit4 | Bit3   | Bit2 | Bit1 | Bit0 |  |

|---------|---------------|------|---------------|------|------|--------|------|------|------|--|

| 43h     | PWM_ctrl1     |      | pwn           | n_d2 |      | pwm_d1 |      |      |      |  |

| 44h     | PWM_ctrl2     |      | pwm_d4 pwm_d3 |      |      |        |      |      |      |  |

| 45h     | PWM_ctrl3     |      | pwn           | n_d6 |      | pwm_d5 |      |      |      |  |

| 46h     | PWM_ctrl4     |      | pwn           | n_d8 |      |        | pwn  | m_d7 |      |  |

#### **Description**

LED luminance can be controlled by "PWM\_ctrlx" register.

| Bit name | Reset value | Function                                                                                         |

|----------|-------------|--------------------------------------------------------------------------------------------------|

| pwm_dx   | 0000        | The LED PWM control bits of Dx port.  4 0000: The minimum low duty  4 1111: The maximum low duty |

# 8.2.13 Port mode control register

Type: R/W

| Address | Register Name | Bit7        | Bit6        | Bit5        | Bit4        | Bit3        | Bit2        | Bit1        | Bit0        |

|---------|---------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| 4Fh     | port_mode     | pmod_d<br>8 | pmod_d<br>7 | pmod_d<br>6 | pmod_d<br>5 | pmod_d<br>4 | pmod_d<br>3 | pmod_d<br>2 | pmod_d<br>1 |

#### Description

This register controls the mode of output port.

| Bit name | Reset value | Function                                                                                                |

|----------|-------------|---------------------------------------------------------------------------------------------------------|

| pmod_dx  | 0           | Select the output port operation mode of each channels.  4 0: Parallel output mode  4 1: LED drive mode |

# 8.2.14 Sense, reference count read register

Type: R

| Address | Register Name | Bit7     | Bit6                 | Bit5 | Bit4       | Bit3        | Bit2 | Bit1 | Bit0 |

|---------|---------------|----------|----------------------|------|------------|-------------|------|------|------|

| 50h     | rd_ch_H1      | rd_ch_H1 |                      |      |            |             |      |      |      |

| 51h     | rd_ch_L1      | -        | -                    | -    | -          | 1           | -    | rd_c | h_L1 |

| 52h     | Percent_H     |          | touch_percent[25:18] |      |            |             |      |      |      |

| 53h     | Percent_M     |          |                      |      | touch_pero | cent[17:10] |      |      |      |

| 54h     | Percent_L     |          |                      |      | touch_pe   | rcent[9:2]  |      |      |      |

| 56h     | rd_ch_H2      | rd_ch_H2 |                      |      |            |             |      |      |      |

| 57h     | rd_ch_L2      | -        | -                    | -    | -          | -           | -    | rd_c | h_L2 |

#### **Description**

ANSG08 provides the special function to read sense count of each channels or reference count.

| Bit name             | Reset value | Function                                                                                                                                                                                                                  |

|----------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rd_ch_H1             | Read only   | Read channel indication register.                                                                                                                                                                                         |

| rd_ch_Ll             | Read only   | Read channel indication register.  4 01 : CS7 channel  4 10 : CS8 channel                                                                                                                                                 |

| touch_percent[24:17] | Read only   | The percent data of RND channel and sense channels.  [25:18] bits of the touch percent data.                                                                                                                              |

| touch_percent[16:9]  | Read only   | The percent data of RND channel and sense channels.  ↓ [17:10] bits of the touch percent data.                                                                                                                            |

| touch_percent[8:1]   | Read only   | The percent data of RND channel and sense channels.  [9:2] bits of the touch percent data.                                                                                                                                |

| rd_ch_H2             | Read only   | Read channel indication register.    00000001: -   00000010: R.N.D channel   0000100: CS1 channel   00001000: CS2 channel   00010000: CS3 channel   00100000: CS4 channel   01000000: CS5 channel   10000000: CS5 channel |

| rd_ch_L2             | Read only   | Read channel indication register.  4 01 : CS7 channel  4 10 : CS8 channel                                                                                                                                                 |

# 8.2.15 EEPROM control register (EEPROM command)

Type: R/W

| Address | Register Name | Bit7 | Bit6 | Bit5      | Bit4     | Bit3 | Bit2 | Bit1     | Bit0     |

|---------|---------------|------|------|-----------|----------|------|------|----------|----------|

| 5Ch     | prom_cmd      | 0    | 0    | write_all | read_all | 0    | 0    | wr_start | rd_start |

#### Description

EEPROM commands to access.

| Bit name  | Reset value | Function                                                                                                    |

|-----------|-------------|-------------------------------------------------------------------------------------------------------------|

| rd_start  | 0           | Reading the EEPROM start command bit.  4 0: Don't start  4 1: Start to read                                 |

| wr_start  | 0           | Writing on the EEPROM start command bit.  4 0: Don't write 4 1: Start to write                              |

| read_all  | 0           | Unit of reading the EEPROM control bit.  4 0: 1-Byte reading 4 1: All bytes of the EEPROM reading           |

| write_all | 0           | Unit of writing on the EEPROM control bit.  4 0: No writing  4 1: All bytes of selected EEPROM cell writing |

# 8.2.16 EEPROM data address select register

Type: R/W

| Address | Register Name | Bit7 | Bit6 | Bit5 | Bit4 | Bit3        | Bit2 | Bit1 | Bit0 |

|---------|---------------|------|------|------|------|-------------|------|------|------|

| 5Fh     | prom_addr     | -    |      |      |      | eeprom_addı |      |      |      |

#### Description

Register for the specific address of the EEPROM.

User can read the EEPROM data of specific address by leaving 'read\_all' bit in the 'prom\_cmd' register '0'.

| Bit name  | Reset    | Function                                                       |

|-----------|----------|----------------------------------------------------------------|

| prom_addr | 00000000 | Select specific address of EEPROM.  deprom_addr[6:0] : Address |

#### 8.2.17 EEPROM data register to read

Type: R

| Address | Register Name | Bit7 | Bit6 | Bit5 | Bit4    | Bit3     | Bit2 | Bit1 | Bit0 |

|---------|---------------|------|------|------|---------|----------|------|------|------|

| 61h     | prom_rd_data  |      |      |      | eeprom_ | _rd_data |      |      |      |

#### Description

The data register for reading data from specific address of selected EEPROM cell.

| Bit name     | Reset | Function                                                                |

|--------------|-------|-------------------------------------------------------------------------|

| prom_rd_data |       | Data register for reading the EEPROM data.  deprom_rd_data [7:0] : Data |

#### 8.2.18 EEPROM Set 2

Type: R/W

| Address | Register Name | Bit7 | Bit6 | Bit5 | Bit4   | Bit3   | Bit2 | Bit1 | Bit0 |

|---------|---------------|------|------|------|--------|--------|------|------|------|

| 7Fh     | prom_set2     |      |      |      | eepror | n_set2 |      |      |      |

#### Description

The second flag byte for the valid data of EEPROM. If the data of this address isn't 0x55 on EEPROM, all data on EEPROM are invalid. So, the data of this address must be written by 0x55 if user wants to change the reset value using EEPROM.

| Bit name    | Reset value | Function                                                        |

|-------------|-------------|-----------------------------------------------------------------|

| eeprom_set2 | 00000000    | 01010101 : EEPROM data is valid others : EEPROM data is invalid |

# 9 Recommended Circuit Diagram

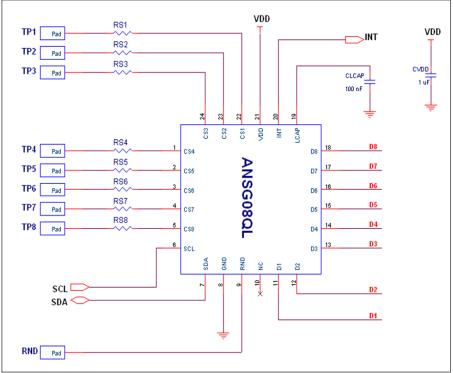

# 9.1 ANSG08QL (24 QFN)

ANSG08QL (24 QFN) Application Example Circuit

- 4 ANSG08QL is reset by internal reset circuit. VDD voltage rising time should be shorter than 100msec for proper operation.

- Normally, R.N.D pin dose not connection to anywhere. But, in radio frequency noise environment, R.N.D pin must form a pattern line on PCB.

- The VDD periodic voltage ripple over 50mV and the ripple frequency is lower than 10 kHz can cause wrong sensitivity calibration. To prevent above problem, power (VDD, GND) line of touch circuit should be separated from other circuit. Especially LED driver power line or digital switching circuit power line certainly should be treated to be separated from touch circuit.

- ♣ The CS patterns also should be routed as short as possible and the width of line might be about 0.25mm.

- Parallel capacitor of CS pin could be useful in case detail sensitivity mediation is required such as for complementation sensitivity difference between channels.

- Serial connection resistor of CS pins may be used to avoid mal-function from external surge and ESD.

- The capacitor that is between VDD and GND is an obligation. It should be located as close as possible from ANSG08OL.

- The CS pattern routing should be formed by bottom metal (opposite metal of touch PAD).

- ♣ The empty space of PCB must be filled with GND pattern to strengthen GND pattern and to prevent external noise from interfere with sensing frequency.

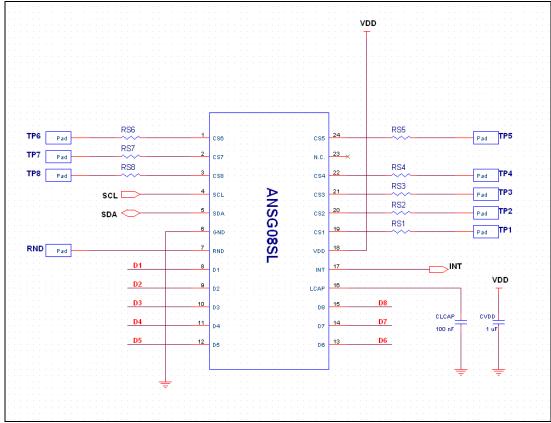

# 9.2 ANSG08SL (24 SOP)

ANSG08SL (24 SOP) Application Example Circuit

- ANSG08SL is reset by internal reset circuit. VDD voltage rising time should be shorter than 100msec for proper operation.

- Normally, R.N.D pin dose not connection to anywhere. But, in radio frequency noise environment, R.N.D pin must form a pattern line on PCB.

- The VDD periodic voltage ripple over 50mV and the ripple frequency is lower than 10 kHz can cause wrong sensitivity calibration. To prevent above problem, power (VDD, GND) line of touch circuit should be separated from other circuit. Especially LED driver power line or digital switching circuit power line certainly should be treated to be separated from touch circuit.

- The CS patterns also should be routed as short as possible and the width of line might be about 0.25mm.

- Parallel capacitor of CS pin could be useful in case detail sensitivity mediation is required such as for complementation sensitivity difference between channels.

- Serial connection resistor of CS pins may be used to avoid mal-function from external surge and ESD.

- The capacitor that is between VDD and GND is an obligation. It should be located as close as possible from ANSG08SL.

- The CS pattern routing should be formed by bottom metal (opposite metal of touch PAD).

- The empty space of PCB must be filled with GND pattern to strengthen GND pattern and to prevent external noise from interfere with sensing frequency.

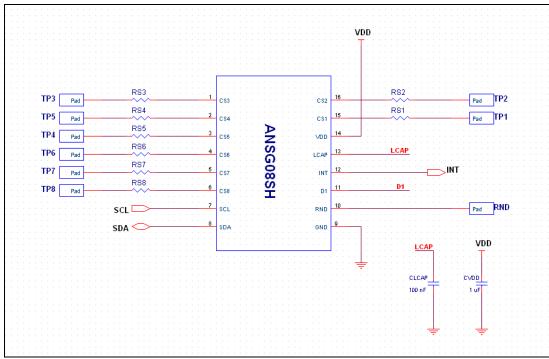

# 9.3 ANSG08SH (16 SOP)

ANSG08SH (16 SOP) Application Example Circuit

- ♣ ANSG08SH is reset by internal reset circuit. VDD voltage rising time should be shorter than 100msec for proper operation.

- Normally, R.N.D pin dose not connection to anywhere. But, in radio frequency noise environment, R.N.D pin must form a pattern line on PCB.

- The VDD periodic voltage ripple over 50mV and the ripple frequency is lower than 10 kHz can cause wrong sensitivity calibration. To prevent above problem, power (VDD, GND) line of touch circuit should be separated from other circuit. Especially LED driver power line or digital switching circuit power line certainly should be treated to be separated from touch circuit.

- ♣ The CS patterns also should be routed as short as possible and the width of line might be about 0.25mm.

- Parallel capacitor of CS pin could be useful in case detail sensitivity mediation is required such as for complementation sensitivity difference between channels.

- Serial connection resistor of CS pins may be used to avoid mal-function from external surge and ESD.

- ♣ The capacitor that is between VDD and GND is an obligation. It should be located as close as possible from ANSG08SH.

- ☐ The CS pattern routing should be formed by bottom metal (opposite metal of touch PAD).

- The empty space of PCB must be filled with GND pattern to strengthen GND pattern and to prevent external noise from interfere with sensing frequency.

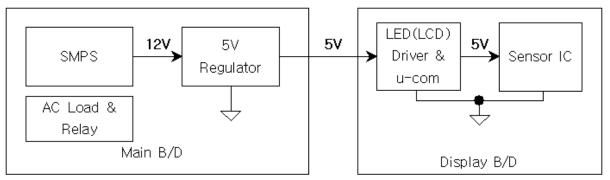

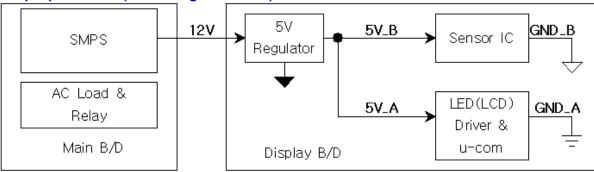

#### 9.4 Example – Power Line Split Strategy PCB Layout

#### A. Not split power Line (Bad power line design)

- ♣ The noise that is generated by AC load or relay can be loaded at 5V power line.

- ♣ A big inductance might be appeared in case of the connection line between main board and display board is too long, moreover the voltage ripple could be generated by LED (LCD) display driver at VDD (5V).

#### B. Split power Line (One 5V regulator used) - Recommended

## C. Split power Line (Separated 5V regulator used) – Strongly recommended

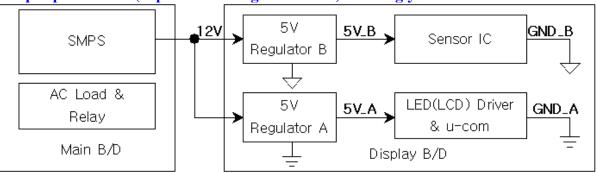

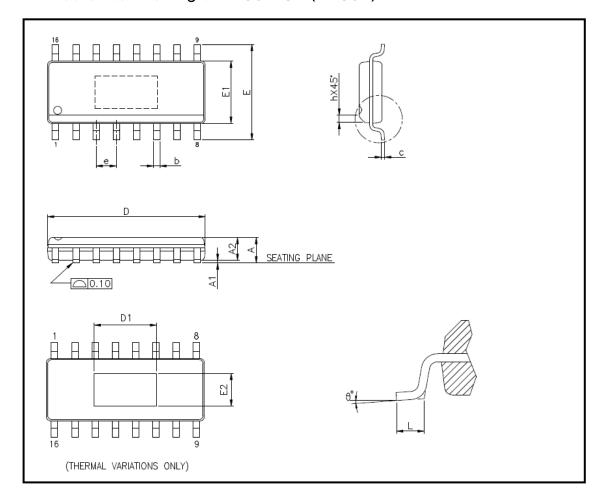

# 10 MECHANICAL DRAWING

# 10.1 Mechanical Drawing of ANSG08QL (24 QFN Full lead type)

| S     |        |           | CDM    | MDN             |       |       |  |

|-------|--------|-----------|--------|-----------------|-------|-------|--|

| S>M M | DIMENS | IONS MILL | IMETER | DIMENSIONS INCH |       |       |  |

| Ľ     | MIN.   | N□M.      | MAX.   | MIN.            | N□M.  | MAX.  |  |

| Α     |        | S         | EE VAR | IATION 4        | Ά*    |       |  |

| A3    | C      | .203 RE   | F      | 0.008 REF       |       |       |  |

| b     | 0.20   | 0.25      | 0.30   | 0.008           | 0.010 | 0.012 |  |

| D     | 3.925  | 4.00      | 4.075  | 0.154           | 0.157 | 0.160 |  |

| DS    | 2.30   | 2.40      | 2.50   | 0.090           | 0.094 | 0.098 |  |

| Ε     | 3.925  | 4.00      | 4.075  | 0.154           | 0.157 | 0.160 |  |

| E2    | 2.30   | 2.40      | 2.50   | 0.090           | 0.094 | 0.098 |  |

| е     |        | 0.500 BS  | С      | 0.020 B2C       |       |       |  |

| L     | 0.35   | 0.40      | 0.45   | 0.013           | 0.015 | 0.017 |  |

| Ş    | ∨ariation "a"         |      |      |                 |       |       |  |

|------|-----------------------|------|------|-----------------|-------|-------|--|

| B    | DIMENSIONS MILLIMETER |      |      | DIMENSIONS INCH |       |       |  |

| Ľ    | MIN.                  | N□M. | MAX. | MIN.            | N□M.  | MAX.  |  |

| QFN  | 0.85                  | 0.90 | 0.95 | 0.033           | 0.035 | 0.037 |  |

| TQFN | 0.70                  | 0.75 | 0.80 | 0.027           | 0.029 | 0.031 |  |

#### NOTES :

- 1. DIMENSION AND TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. CONTROLLING DIMENSIONS : MILLIMETER. CONVERTED INCH DIMENSION ARE NOT NECESSARILY EXACT.

- 3. DIMENSION & APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30 MM. FROM TERMINAL TIP.

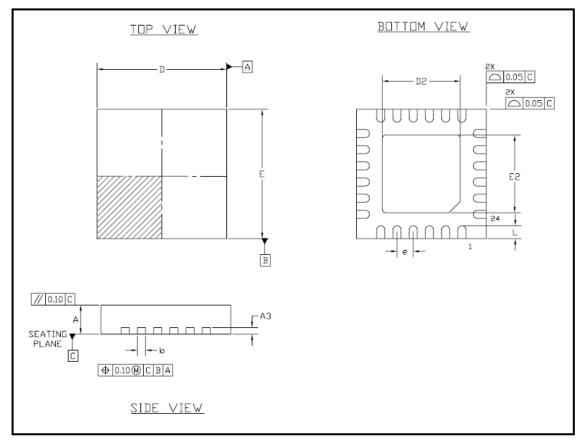

# 10.2 Mechanical Drawing of ANSG08SL (24 SOP)

|   | SYMBOLS | MIN.  | NOM   | MAX.       |

|---|---------|-------|-------|------------|

|   | А       | _     | _     | 2.64       |

|   | A1      | 0.10  | _     |            |

| A | D       | 15.24 | _     | 15.70      |

|   | Ē       | 7.42  | 7.52  | 7.59       |

|   | Н       | 10.29 | 10.46 | 10.64      |

|   | Ĺ       | 0.53  | 0.79  | 1.04       |

|   | θ°      | 0     | 4     | 8          |

|   |         |       |       | LINUT NINI |

UNIT: MM

#### NOTES:

▲1.JEDEC OUTLINE : N/A.

2.DIMENSIONS "D" DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.MOLD FLASH, PROTRUSIONS AND GATE BURRS SHALL NOT EXCEED .25mm (.010in) PER SIDE.

3.DIMENSIONS "E" DOES NOT INCLUDE INTER-LEAD FLASH, OR PROTRUSIONS. INTER-LEAD FLASH AND PROTRUSIONS SHALL NOT EXCEED .25mm (.010in) PER SIDE.

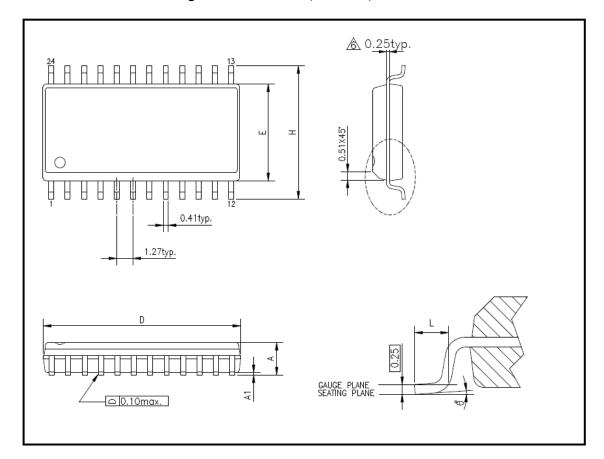

# 10.3 Mechanical Drawing of ANSG08SH (16 SOP)

|             | STANDARD |        | THERMAL  |      |  |

|-------------|----------|--------|----------|------|--|

| SYMBOLS     | MIN.     | MAX.   | MIN.     | MAX. |  |

| Α           | ı        | - 1.75 |          | 1.70 |  |

| A1          | 0.10     | 0.25   | 0.00     | 0.15 |  |

| A2          | 1.25     | _      | 1.25     | _    |  |

| ь           | 0.31     | 0.51   | 0.31     | 0.51 |  |

| С           | 0.10     | 0.25   | 0.10     | 0.25 |  |

| D           | 9.90 BSC |        | 9.90 BSC |      |  |

| E           | 6.00 BSC |        | 6.00 BSC |      |  |

| E1 3.90 BSC |          | BSC    | 3.90 BSC |      |  |

| е           | 1.27 BSC |        | 1.27 BSC |      |  |

| L           | 0.40     | 1.27   | 0.40     | 1.27 |  |

| h           | 0.25     | 0.50   | 0.25     | 0.50 |  |

| θ°          | 0        | 8      | 0        | 8    |  |

UNIT: mm

#### THERMALLY ENHANCED DIMENSIONS

| DAD 6175 | Е    | 2    | D1   |      |

|----------|------|------|------|------|

| PAD SIZE | MIN. | MAX. | MIN. | MAX. |

| 95X18E   | 1.68 | 2.41 | 3.86 | 4.57 |

UNIT: mm

#### NOTES:

1.JEDEC OUTLINE: MS-012 AC REV.F (STANDARD) MS-012 BC REV.F (THERMAL) 2.DIMENSIONS "D" DOES NOT INCLUDE MOLD FLASH,

PROTRUSIONS OR GATE BURRS.MOLD FLASH, PROTRUSIONS AND GATE BURRS SHALL NOT EXCEED 0.15mm. PER SIDE.

3.DIMENSIONS "E1" DOES NOT INCLUDE INTER-LEAD FLASH, OR PROTRUSIONS. INTER-LEAD FLASH AND PROTRUSIONS SHALL NOT EXCEED 0.25mm PER SIDE.

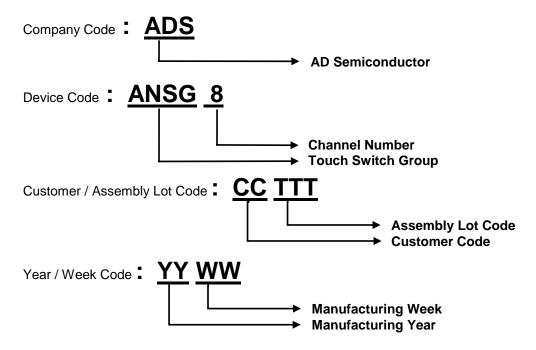

# 11 MARKING DESCRIPTION

# 11.1 Marking Description of ANSG08QL (24 QFN)

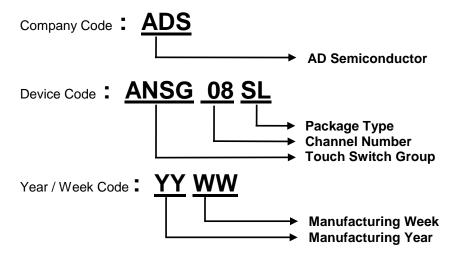

#### 11.2 Marking Description of ANSG08SL (24 SOP)

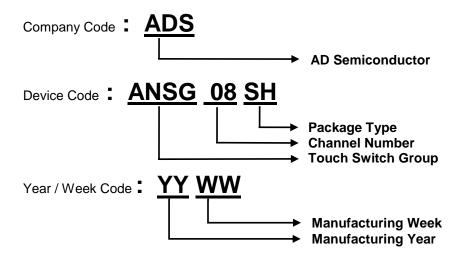

# 11.3 Marking Description of ANSG08SH (16 SOP)

NOTES:

#### LIFE SUPPORT POLICY

AD SEMICONDUCTOR'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF AD SEMICONDUCTOR CORPORATION

The ADS logo is a registered trademark of ADSemiconductor

© 2006 ADSemiconductor - All Rights Reserved

www.adsemicon.com www.adsemicon.co.kr