# **Operational Amplifier, Low Power, 1.2 MHz, 42 μA**

# NCS20081/2/4, NCV20081/2/4

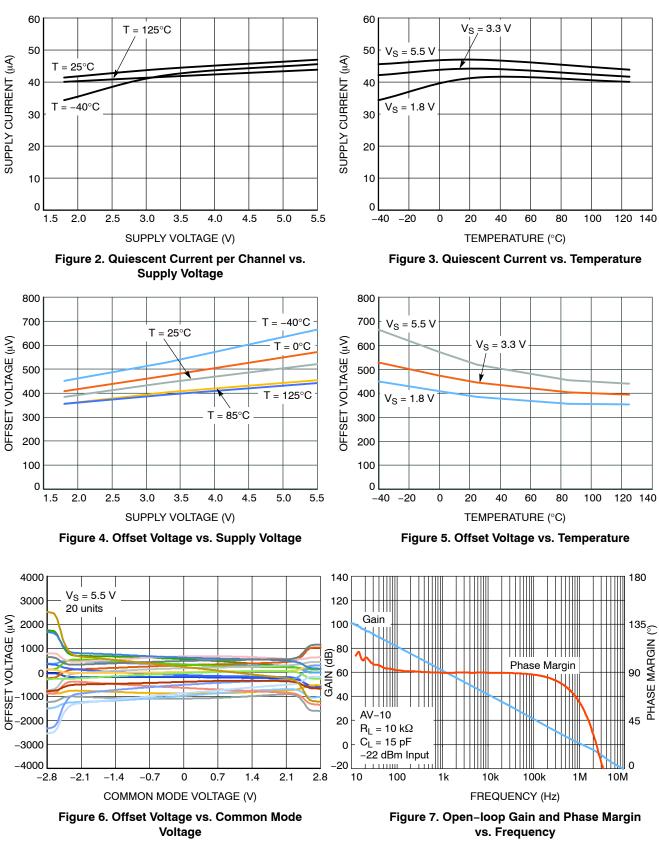

The NCS20081/2/4 is a family of single, dual and quad Operational Amplifiers (Op Amps) with 1.2 MHz of Gain–Bandwidth Product (GBWP) While consuming only 42  $\mu$ A of Quiescent current per opamp. The NCS2008x has Input Offset Voltage of 4 mV and operates from 1.8 V to 5.5 V supply voltage over a wide temperature range (-40°C to +125°C). The Rail–to–Rail In/Out operation allows the use of the entire supply voltage range while taking advantage of the 1.2 MHz GBWP. Thus, this family offers superior performance over many industry standard parts. These devices are AEC–Q100 qualified which is denoted by the NCV prefix.

NCS2008x's low current consumption and low supply voltage performance in space saving packages, makes them ideal for sensor signal conditioning and low voltage current sensing applications in Automotive, Consumer and Industrial markets.

#### Features

- Wide Bandwidth: 1.2 MHz

- Low Supply Current/ Channel:  $42 \mu A \text{ typ} (V_S = 1.8 \text{ V})$

- Low Input Offset Voltage: 4 mV max

- Wide Supply Range: 1.8 V to 5.5 V

- Wide Temperature Range: -40°C to +125°C

- Rail-to-Rail Input and Output

- Unity Gain Stable

- Available in Single, Dual and Quad Packages

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

#### Applications

- Automotive

- Battery Powered/ Portable

- Sensor Signal Conditioning

- Low Voltage Current Sensing

- Filter Circuits

- Unity Gain Buffer

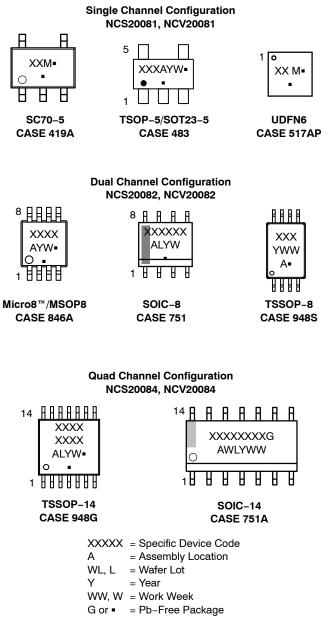

#### **DEVICE MARKING INFORMATION**

See general marking information in the device marking section on page 2 of this data sheet.

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 3 of this data sheet.

#### MARKING DIAGRAMS

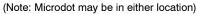

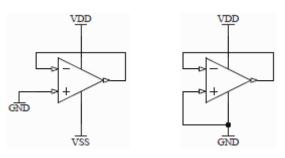

Figure 1. Pin Connections

#### **ORDERING INFORMATION**

| Device          | Configuration | Automotive | Marking  | Package        | Shipping <sup>†</sup>                              |

|-----------------|---------------|------------|----------|----------------|----------------------------------------------------|

| NCS20081SQ2T2G  |               |            | AAX      | SC70           |                                                    |

| NCS20081SQ3T2G  |               |            | AAP      | SC70           |                                                    |

| NCS20081SN2T1G  |               | No         | AER      | SOT23-5/TSOP-5 |                                                    |

| NCS20081SN3T1G  |               |            | AEU      | SOT23-5/TSOP-5 |                                                    |

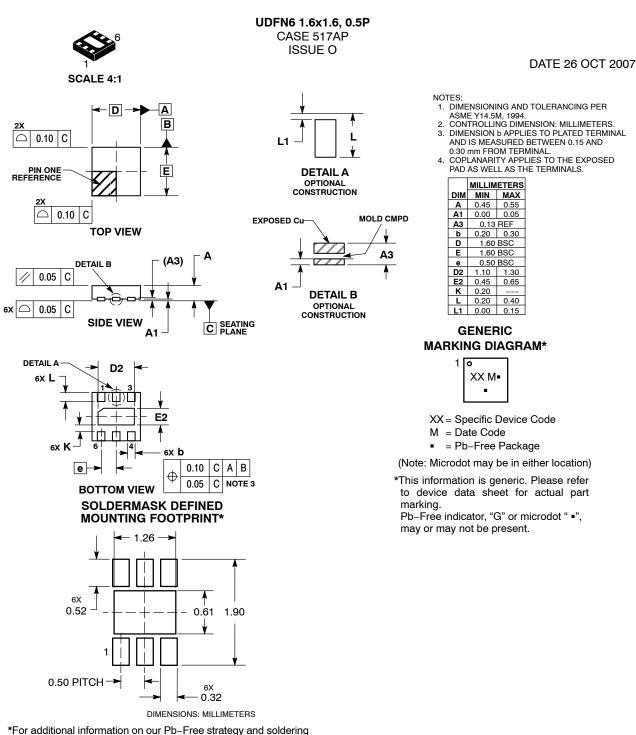

| NCS20081MUTAG   | Single        |            | AP       | UDFN6          |                                                    |

| NCV20081SQ2T2G* |               |            | AAX      | SC70           |                                                    |

| NCV20081SQ3T2G* | 1             | Mar        | AAP      | SC70           | 1                                                  |

| NCV20081SN2T1G* | 1             | Yes        | AER      | SOT23-5/TSOP-5 | 1                                                  |

| NCV20081SN3T1G* |               |            | AEU      | SOT23-5/TSOP-5 | 1                                                  |

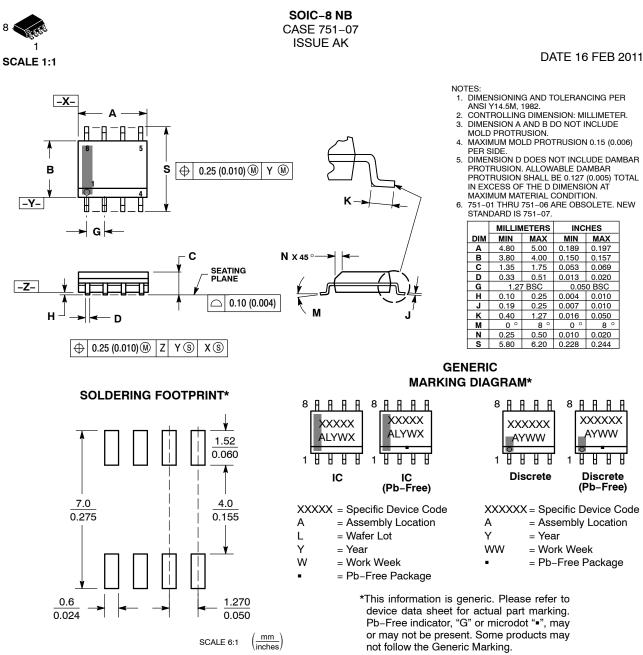

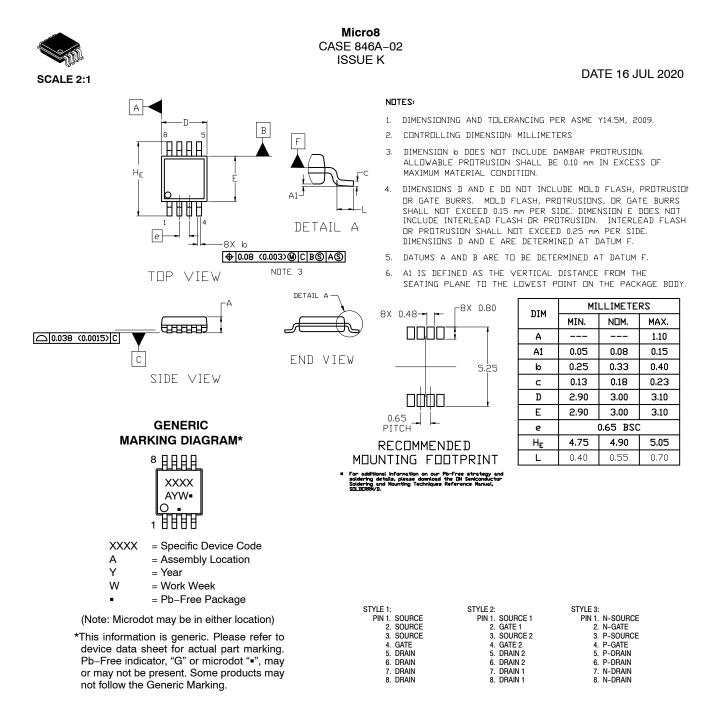

| NCS20082DMR2G   |               |            | 2K82     | Micro8/MSOP8   | Contact local sales office for<br>more information |

| NCS20082DR2G    |               | No         | NCS20082 | SOIC-8         | more mornation                                     |

| NCS20082DTBR2G  |               |            | K82      | TSSOP-8        |                                                    |

| NCV20082DMR2G*  | Dual          |            | 2K82     | Micro8/MSOP8   |                                                    |

| NCV20082DR2G*   | 1             | Yes        | NCS20082 | SOIC-8         | 1                                                  |

| NCV20082DTBR2G* | 1             |            | K82      | TSSOP-8        | 1                                                  |

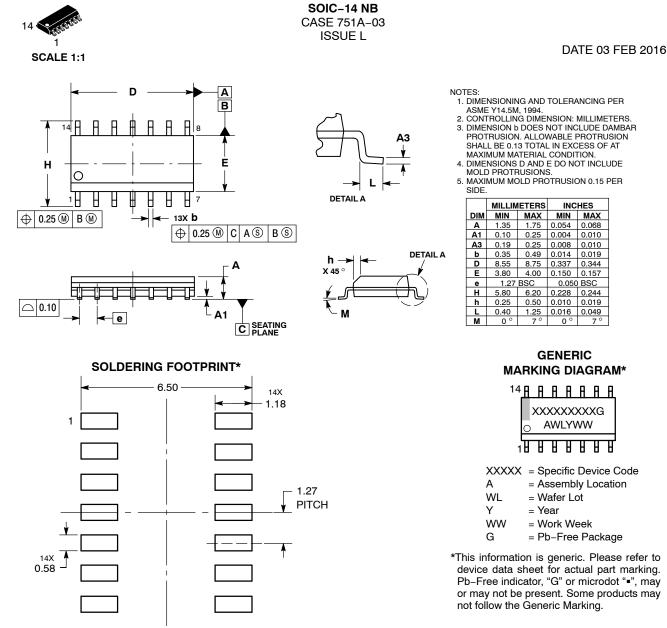

| NCS20084DR2G    |               | Ne         | 20084    | SOIC-14        | 1                                                  |

| NCS20084DTBR2G  |               | No         | 284      | TSSOP-14       |                                                    |

| NCV20084DR2G*   | Quad          |            | 20084    | SOIC-14        | 1                                                  |

| NCV20084DTBR2G* | 1             | Yes        | 284      | TSSOP-14       | 1                                                  |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D

\*NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable.

#### ABSOLUTE MAXIMUM RATINGS (Note 1)

| Rating                                                          | Symbol                                   | Limit                            | Unit |

|-----------------------------------------------------------------|------------------------------------------|----------------------------------|------|

| Supply Voltage ( $V_{DD} - V_{SS}$ ) (Note 2)                   | V <sub>S</sub>                           | 6                                | V    |

| Input Voltage                                                   | VI                                       | $V_{SS}$ – 0.5 to $V_{DD}$ + 0.5 | V    |

| Differential Input Voltage                                      | V <sub>ID</sub>                          | ±Vs                              | V    |

| Maximum Input Current                                           | lı                                       | ±10                              | mA   |

| Maximum Output Current                                          | Ι <sub>Ο</sub>                           | ±100                             | mA   |

| Continuous Total Power Dissipation (Note 2)                     | PD                                       | 200                              | mW   |

| Maximum Junction Temperature                                    | Т <sub>Ј</sub>                           | 150                              | °C   |

| Storage Temperature Range                                       | T <sub>STG</sub>                         | -65 to 150                       | °C   |

| Mounting Temperature (Infrared or Convection – 20 sec)          | T <sub>mount</sub>                       | 260                              | °C   |

| ESD Capability (Note 3) Human Body Model<br>Charge Device Model | ESD <sub>HBM</sub><br>ESD <sub>CDM</sub> | 2000<br>2000                     | V    |

| Latch-Up Current (Note 4)                                       | I <sub>LU</sub>                          | 100                              | mA   |

| Moisture Sensitivity Level (Note 5)                             | MSL                                      | Level 1                          |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Refer to ELECTRICAL CHARACTERISTICS for Safe Operating Area.

2. Continuous short circuit operation to ground at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C. Output currents in excess of the maximum output current rating over the long term may adversely affect reliability. Shorting output to either VDD or VSS will adversely affect reliability.

3. This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model tested per JEDEC standard Js-001-2017 (AEC-Q100-002) ESD Charged Device Model tested per JEDEC standard JS-002-2014 (AEC-Q100-011)

4. Latch-up Current tested per JEDEC standard JESD78E (AEC-Q100-004)

5. Moisture Sensitivity Level tested per IPC/JEDEC standard: J-STD-020A

#### THERMAL INFORMATION

| Parameter           | Symbol        | Channels | Package        | Single Layer<br>Board (Note 6) | Multi-Layer<br>Board (Note 7) | Unit  |     |     |  |

|---------------------|---------------|----------|----------------|--------------------------------|-------------------------------|-------|-----|-----|--|

|                     |               |          | SC-70          | 491                            | 444                           |       |     |     |  |

|                     |               | Single   | SOT23-5/TSOP-5 | 310                            | 247                           |       |     |     |  |

|                     |               |          |                |                                |                               | UDFN6 | 278 | 239 |  |

| Junction to Ambient | 0             |          | Micro8/MSOP8   | 236                            | 167                           |       |     |     |  |

| Thermal Resistance  | $\theta_{JA}$ | Dual     | SOIC-8         | 190                            | 131                           | °C/W  |     |     |  |

|                     |               |          | TSSOP-8        | 253                            | 194                           |       |     |     |  |

|                     |               |          | SOIC-14        | 130                            | 99                            |       |     |     |  |

|                     |               | Quad     | TSSOP-14       | 178                            | 140                           |       |     |     |  |

6. Value based on 1S standard PCB according to JEDEC51-3 with 1.0 oz copper and a 300 mm<sup>2</sup> copper area

7. Value based on 1S2P standard PCB according to JEDEC51-7 with 1.0 oz copper and a 100 mm<sup>2</sup> copper area

#### **OPERATING RANGES**

| Parameter                  | Symbol           | Min            | Max                   | Unit |

|----------------------------|------------------|----------------|-----------------------|------|

| Operating Supply Voltage   | V <sub>S</sub>   | 1.8            | 5.5                   | V    |

| Differential Input Voltage | V <sub>ID</sub>  |                | VS                    | V    |

| Input Common Mode Range    | V <sub>ICM</sub> | $V_{SS} - 0.2$ | V <sub>DD</sub> + 0.2 | V    |

| Ambient Temperature        | T <sub>A</sub>   | -40            | 125                   | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

**ELECTRICAL CHARACTERISTICS AT**  $V_{S} = 1.8 V$   $T_{A} = 25^{\circ}C; R_{L} \ge 10 k\Omega; V_{CM} = V_{OUT} = mid-supply unless otherwise noted.$  **Boldface** limits apply over the specified temperature range,  $T_{A} = -40^{\circ}C$  to 125°C. (Note 8)

| Parameter                            | Symbol                     | Cor                                       | nditions                       | Min | Тур                 | Мах  | Unit     |

|--------------------------------------|----------------------------|-------------------------------------------|--------------------------------|-----|---------------------|------|----------|

| INPUT CHARACTERISTICS                |                            |                                           |                                |     |                     |      |          |

| Input Offset Voltage                 | V <sub>OS</sub>            |                                           |                                |     | 0.5                 | 3.5  | mV       |

|                                      |                            |                                           |                                |     |                     | 4    | mV       |

| Offset Voltage Drift                 | $\Delta V_{OS} / \Delta T$ |                                           |                                |     | 1                   |      | μV/°C    |

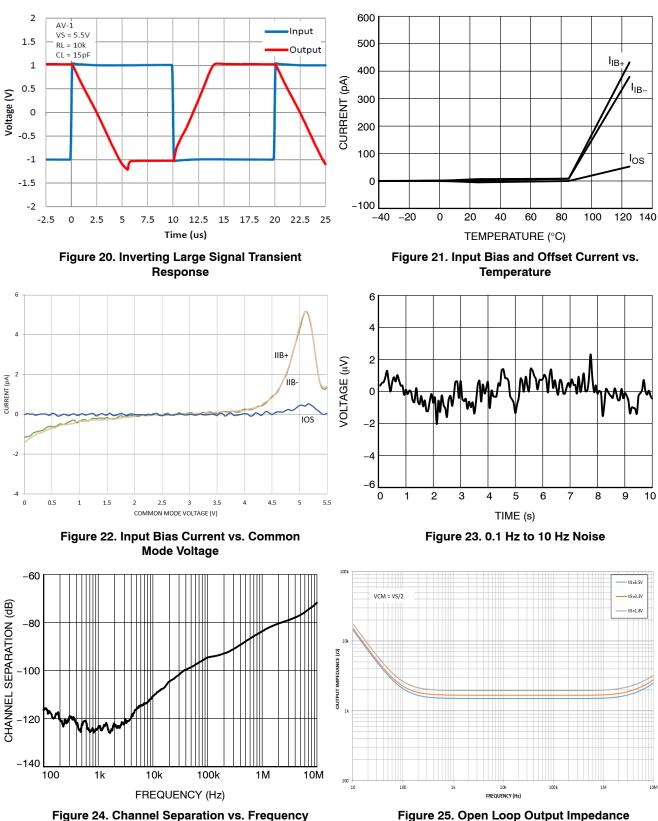

| Input Bias Current (Note 8)          | I <sub>IB</sub>            |                                           |                                |     | 1                   |      | pА       |

|                                      |                            |                                           |                                |     |                     | 1500 | pА       |

| Input Offset Current (Note 8)        | I <sub>OS</sub>            |                                           |                                |     | 1                   |      | pА       |

|                                      |                            |                                           |                                |     |                     | 1100 | pА       |

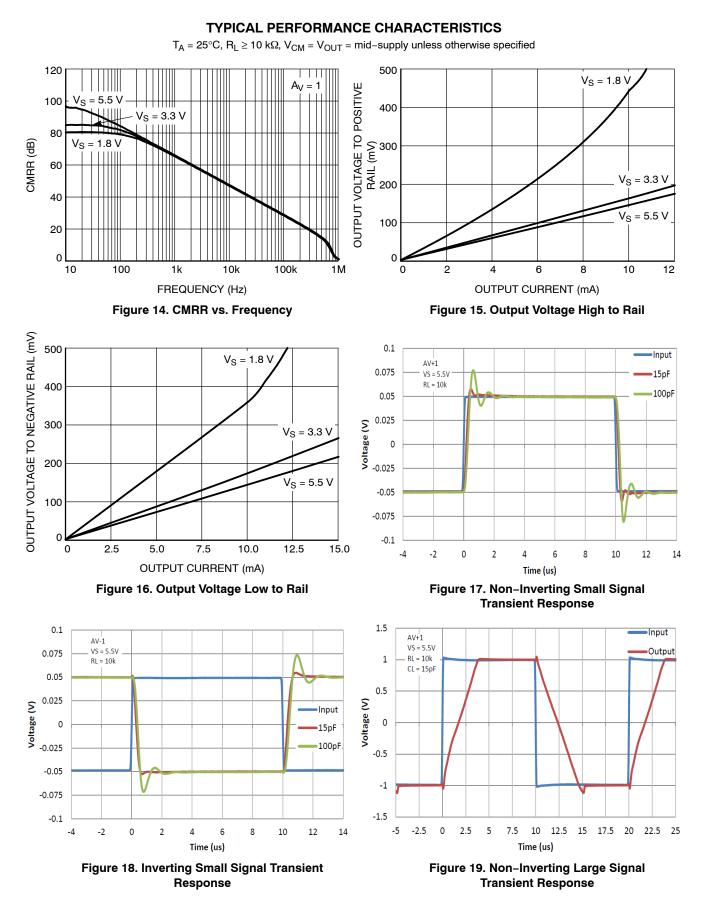

| Channel Separation                   | XTLK                       | f =                                       | 1 kHz                          |     | 125                 |      | dB       |

| Differential Input Resistance        | R <sub>ID</sub>            |                                           |                                |     | 10                  |      | GΩ       |

| Common Mode Input Resistance         | R <sub>IN</sub>            |                                           |                                |     | 10                  |      | GΩ       |

| Differential Input Capacitance       | C <sub>ID</sub>            |                                           |                                |     | 1                   |      | pF       |

| Common Mode Input Capacitance        | C <sub>CM</sub>            |                                           |                                |     | 5                   |      | pF       |

| Common Mode Rejection Ratio          | CMRR                       | $V_{CM} = V_{SS}$ –                       | - 0.2 to V <sub>DD</sub> + 0.2 | 48  | 73                  |      | dB       |

|                                      |                            | V <sub>CM</sub> = V <sub>SS</sub> +       | - 0.2 to V <sub>DD</sub> – 0.2 | 45  |                     |      | -        |

| OUTPUT CHARACTERISTICS               |                            |                                           |                                |     |                     |      |          |

| Open Loop Voltage Gain               | A <sub>VOL</sub>           |                                           |                                | 86  | 120                 |      | dB       |

|                                      |                            | t                                         |                                | 80  |                     |      | -        |

| Short Circuit Current                | I <sub>SC</sub>            | Output to positive rail, sinking current  |                                |     | 15                  |      | mA       |

|                                      |                            | Output to negative rail, sourcing current |                                |     | 11                  |      |          |

| Output Voltage High                  | V <sub>OH</sub>            | Voltage output swing from positive rail   |                                |     | 3                   | 19   | mV       |

|                                      |                            | $V_{OH} = V_{DD} - V_{OUT}$               |                                |     |                     | 20   | -        |

| Output Voltage Low                   | V <sub>OL</sub>            | Voltage output swing from negative rail   |                                |     | 3                   | 19   | mV       |

|                                      |                            | $V_{OL} = V_{OUT} - V_{SS}$               |                                |     |                     | 20   |          |

| AC CHARACTERISTICS                   | <u> </u>                   |                                           |                                |     | 1                   |      |          |

| Unity Gain Bandwidth                 | UGBW                       |                                           |                                |     | 1.2                 |      | MHz      |

| Slew Rate at Unity Gain              | SR                         | V <sub>IN</sub> = 1.2                     | Vpp, Gain = 1                  |     | 0.4                 |      | V/μs     |

| Phase Margin                         | Ψm                         |                                           |                                |     | 60                  |      | 0        |

| Gain Margin                          | A <sub>m</sub>             |                                           |                                |     | 19                  |      | dB       |

| Settling Time                        | t <sub>S</sub>             | V <sub>IN</sub> = 1.2 Vpp,                | Settling time to 0.1%          |     | 5                   |      | μs       |

|                                      |                            | Gain = 1                                  | Settling time to 0.01%         |     | 6                   |      |          |

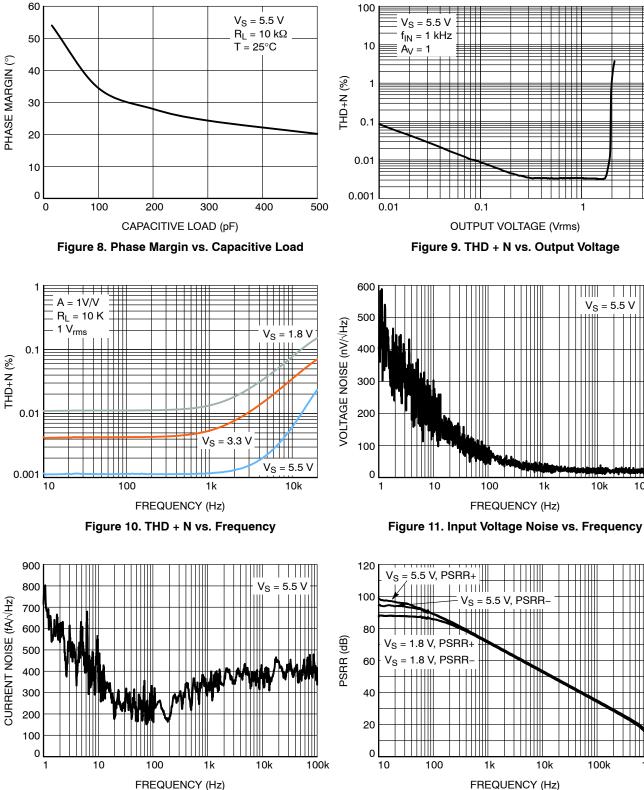

| Open Loop Output Impedance           | Z <sub>OL</sub>            |                                           |                                |     | See<br>Figure<br>25 |      | Ω        |

| NOISE CHARACTERISTICS                | <u> </u>                   |                                           |                                |     |                     |      | <u>I</u> |

| Total Harmonic Distortion plus Noise | THD+N                      | VIN = 1.2 Vpn                             | o, f = 1 kHz, Av = 1           |     | 0.005               |      | %        |

| Input Referred Voltage Noise         | e <sub>n</sub>             |                                           | = 1 kHz                        |     | 30                  |      | nV/√Hz   |

|                                      |                            |                                           | 10 kHz                         |     | 24                  |      | - ···-   |

| Input Referred Current Noise         | i <sub>n</sub>             |                                           | = 1 kHz                        |     | 300                 |      | fA/√Hz   |

| SUPPLY CHARACTERISTICS               | -11                        | . –                                       |                                |     |                     |      | L,       |

| Power Supply Rejection Ratio         | PSRR                       | N                                         | o Load                         | 67  | 90                  |      | dB       |

| , , , <u>,</u>                       |                            |                                           |                                | 64  |                     |      |          |

| Power Supply Quiescent Current       | I <sub>DD</sub>            | Per cha                                   | nnel, no load                  |     | 42                  | 60   | μA       |

|                                      | .00                        |                                           | ,                              |     | 1                   |      | P        |

8. Performance guaranteed over the indicated operating temperature range by design and/or characterization.

**ELECTRICAL CHARACTERISTICS AT**  $V_{S}$  **= 3.3 V** T<sub>A</sub> = 25°C; R<sub>L</sub> ≥ 10 kΩ; V<sub>CM</sub> = V<sub>OUT</sub> = mid-supply unless otherwise noted. **Boldface** limits apply over the specified temperature range, T<sub>A</sub> = -40°C to 125°C. (Note 9)

| Parameter                            | Symbol                     | Co                                        | nditions                       | Min | Тур                 | Мах  | Unit   |

|--------------------------------------|----------------------------|-------------------------------------------|--------------------------------|-----|---------------------|------|--------|

| INPUT CHARACTERISTICS                |                            |                                           |                                |     |                     |      |        |

| Input Offset Voltage                 | V <sub>OS</sub>            |                                           |                                |     | 0.5                 | 3.5  | mV     |

|                                      |                            |                                           |                                |     |                     | 4    | mV     |

| Offset Voltage Drift                 | $\Delta V_{OS} / \Delta T$ |                                           |                                |     | 1                   |      | μV/°C  |

| Input Bias Current (Note 9)          | I <sub>IB</sub>            |                                           |                                |     | 1                   |      | pА     |

|                                      |                            |                                           |                                |     |                     | 1500 | pА     |

| Input Offset Current (Note 9)        | I <sub>OS</sub>            |                                           |                                |     | 1                   |      | pА     |

|                                      |                            |                                           |                                |     |                     | 1100 | pА     |

| Channel Separation                   | XTLK                       | f =                                       | = 1 kHz                        |     | 125                 |      | dB     |

| Differential Input Resistance        | R <sub>ID</sub>            |                                           |                                |     | 10                  |      | GΩ     |

| Common Mode Input Resistance         | R <sub>IN</sub>            |                                           |                                |     | 10                  |      | GΩ     |

| Differential Input Capacitance       | C <sub>ID</sub>            |                                           |                                |     | 1                   |      | pF     |

| Common Mode Input Capacitance        | C <sub>CM</sub>            |                                           |                                |     | 5                   |      | pF     |

| Common Mode Rejection Ratio          | CMRR                       | V <sub>CM</sub> = V <sub>SS</sub> -       | - 0.2 to V <sub>DD</sub> + 0.2 | 53  | 76                  |      | dB     |

|                                      |                            | V <sub>CM</sub> = V <sub>SS</sub> -       | + 0.2 to V <sub>DD</sub> – 0.2 | 48  |                     |      |        |

| OUTPUT CHARACTERISTICS               |                            |                                           |                                |     |                     |      |        |

| Open Loop Voltage Gain               | A <sub>VOL</sub>           |                                           |                                | 90  | 120                 |      | dB     |

|                                      |                            | F                                         |                                | 86  |                     |      |        |

| Short Circuit Current                | I <sub>SC</sub>            | Output to positive rail, sinking current  |                                |     | 15                  |      | mA     |

|                                      |                            | Output to negative rail, sourcing current |                                |     | 11                  |      | 1      |

| Output Voltage High                  | V <sub>OH</sub>            | Voltage output swing from positive rail   |                                |     | 3                   | 24   | mV     |

|                                      |                            | $V_{OH} = V_{DD} - V_{OUT}$               |                                |     |                     | 25   | 1      |

| Output Voltage Low                   | V <sub>OL</sub>            | Voltage output swing from negative rail   |                                |     | 3                   | 24   | mV     |

|                                      |                            | $V_{OL} = V_{OUT} - V_{SS}$               |                                |     |                     | 25   | 1      |

| AC CHARACTERISTICS                   |                            |                                           |                                |     |                     |      |        |

| Unity Gain Bandwidth                 | UGBW                       |                                           |                                |     | 1.2                 |      | MHz    |

| Slew Rate at Unity Gain              | SR                         | V <sub>IN</sub> = 2.5                     | Vpp, Gain = 1                  |     | 0.4                 |      | V/μs   |

| Phase Margin                         | Ψm                         |                                           |                                |     | 60                  |      | 0      |

| Gain Margin                          | A <sub>m</sub>             |                                           |                                |     | 18                  |      | dB     |

| Settling Time                        | t <sub>S</sub>             | V <sub>IN</sub> = 2.5 Vpp,                | Settling time to 0.1%          |     | 5                   |      | μs     |

|                                      |                            | Gain = 1                                  | Settling time to 0.01%         |     | 6                   |      | 1      |

| Open Loop Output Impedance           | Z <sub>OL</sub>            |                                           |                                |     | See<br>Figure<br>25 |      | Ω      |

| NOISE CHARACTERISTICS                |                            |                                           |                                |     |                     |      |        |

| Total Harmonic Distortion plus Noise | THD+N                      | V <sub>IN</sub> = 2.5 Vpr                 | o, f = 1 kHz, Av = 1           |     | 0.005               |      | %      |

| Input Referred Voltage Noise         | e <sub>n</sub>             |                                           | = 1 kHz                        |     | 30                  |      | nV/√Hz |

| -                                    |                            | f =                                       | 10 kHz                         |     | 24                  |      | 1      |

| Input Referred Current Noise         | i <sub>n</sub>             | f =                                       | = 1 kHz                        |     | 300                 |      | fA/√Hz |

| SUPPLY CHARACTERISTICS               |                            |                                           |                                |     |                     |      | •      |

| Power Supply Rejection Ratio         | PSRR                       | N                                         | o Load                         | 67  | 90                  |      | dB     |

|                                      |                            |                                           |                                | 64  |                     |      | 1      |

| Power Supply Quiescent Current       | I <sub>DD</sub>            | Per cha                                   | nnel, no load                  |     | 42                  | 60   | μΑ     |

| 11.2                                 | 50                         |                                           |                                |     |                     |      | 1 1    |

9. Performance guaranteed over the indicated operating temperature range by design and/or characterization.

**ELECTRICAL CHARACTERISTICS AT**  $V_{S}$  **= 5.5 V** T<sub>A</sub> = 25°C; R<sub>L</sub> ≥ 10 kΩ; V<sub>CM</sub> = V<sub>OUT</sub> = mid-supply unless otherwise noted. **Boldface** limits apply over the specified temperature range, T<sub>A</sub> = -40°C to 125°C. (Note 10)

$V_{OL}$

| Parameter                      | Symbol                     | Conditions                                  | Min | Тур | Max  | Unit  |

|--------------------------------|----------------------------|---------------------------------------------|-----|-----|------|-------|

| INPUT CHARACTERISTICS          |                            |                                             |     |     |      |       |

| Input Offset Voltage           | V <sub>OS</sub>            |                                             |     | 0.5 | 3.5  | mV    |

|                                |                            |                                             |     |     | 4    | mV    |

| Offset Voltage Drift           | $\Delta V_{OS} / \Delta T$ |                                             |     | 1   |      | μV/°C |

| Input Bias Current (Note 10)   | I <sub>IB</sub>            |                                             |     | 1   |      | pА    |

|                                |                            |                                             |     |     | 1500 | pА    |

| Input Offset Current (Note 10) | I <sub>OS</sub>            |                                             |     | 1   |      | pА    |

|                                |                            |                                             |     |     | 1100 | pА    |

| Channel Separation             | XTLK                       | f = 1 kHz                                   |     | 125 |      | dB    |

| Differential Input Resistance  | R <sub>ID</sub>            |                                             |     | 10  |      | GΩ    |

| Common Mode Input Resistance   | R <sub>IN</sub>            |                                             |     | 10  |      | GΩ    |

| Differential Input Capacitance | C <sub>ID</sub>            |                                             |     | 1   |      | pF    |

| Common Mode Input Capacitance  | C <sub>CM</sub>            |                                             |     | 5   |      | pF    |

| Common Mode Rejection Ratio    | CMRR                       | $V_{CM}$ = $V_{SS}$ – 0.2 to $V_{DD}$ + 0.2 | 55  | 79  |      | dB    |

|                                |                            | $V_{CM} = V_{SS} + 0.2$ to $V_{DD} - 0.2$   | 51  |     |      | 1     |

| OUTPUT CHARACTERISTICS         |                            |                                             |     |     |      |       |

| Open Loop Voltage Gain         | A <sub>VOL</sub>           |                                             | 90  | 120 |      | dB    |

|                                |                            |                                             | 86  |     |      | 1     |

| Short Circuit Current          | I <sub>SC</sub>            | Output to positive rail, sinking current    |     | 15  |      | mA    |

|                                |                            | Output to negative rail, sourcing current   |     | 11  |      | 1     |

| Output Voltage High            | V <sub>OH</sub>            | Voltage output swing from positive rail     |     | 3   | 24   | mV    |

|                                |                            | $V_{OH} = V_{DD} - V_{OUT}$                 |     |     | 25   | 1     |

#### AC CHARACTERISTICS

**Output Voltage Low**

| Unity Gain Bandwidth       | UGBW            |                          |                        | 1.2           | M        | lHz |

|----------------------------|-----------------|--------------------------|------------------------|---------------|----------|-----|

| Slew Rate at Unity Gain    | SR              | V <sub>IN</sub> = 5      | Vpp, Gain = 1          | 0.4           | V/       | /μs |

| Phase Margin               | ψm              |                          |                        | 60            |          | 0   |

| Gain Margin                | A <sub>m</sub>  |                          |                        | 17            | d        | dB  |

| Settling Time              | t <sub>S</sub>  | V <sub>IN</sub> = 5 Vpp, | Settling time to 0.1%  | 5             | μ        | μs  |

|                            |                 | Gain = 1                 | Settling time to 0.01% | 6             |          |     |

| Open Loop Output Impedance | Z <sub>OL</sub> |                          |                        | See<br>Figure | <u>(</u> | Ω   |

Voltage output swing from negative rail  $V_{OL} = V_{OUT} - V_{SS}$

mV

3

24 25

#### NOISE CHARACTERISTICS

| Total Harmonic Distortion plus Noise | THD+N          | $V_{IN} = 5 Vpp, f = 1 kHz, Av = 1$ | 0.00 | 5 | %      |

|--------------------------------------|----------------|-------------------------------------|------|---|--------|

| Input Referred Voltage Noise         | e <sub>n</sub> | f = 1 kHz                           | 30   |   | nV/√Hz |

|                                      |                | f = 10 kHz                          | 24   |   |        |

| Input Referred Current Noise         | i <sub>n</sub> | f = 1 kHz                           | 300  | ) | fA/√Hz |

| SUPPLY CHARACTERISTICS               |                |                                     |      |   |        |

| Power Supply Rejection Ratio   | PSRR            | No Load              | 67 | 90 |    | dB |

|--------------------------------|-----------------|----------------------|----|----|----|----|

|                                |                 |                      | 64 |    |    |    |

| Power Supply Quiescent Current | I <sub>DD</sub> | Per channel, no load |    | 48 | 70 | μΑ |

10. Performance guaranteed over the indicated operating temperature range by design and/or characterization. Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

$T_A = 25^{\circ}C$ ,  $R_L \ge 10 \text{ k}\Omega$ ,  $V_{CM} = V_{OUT} = \text{mid-supply unless otherwise specified}$

$T_A$  = 25°C,  $R_L \ge$  10 kΩ,  $V_{CM}$  =  $V_{OUT}$  = mid–supply unless otherwise specified

100k

1M

Figure 12. Input Current Noise vs. Frequency

$T_A$  = 25°C,  $R_L \geq$  10 kΩ,  $V_{CM}$  =  $V_{OUT}$  = mid–supply unless otherwise specified

vs. Frequency

### **TYPICAL PERFORMANCE CHARACTERISTICS**

$T_A$  = 25°C,  $R_L \geq$  10 kΩ,  $V_{CM}$  =  $V_{OUT}$  = mid–supply unless otherwise specified

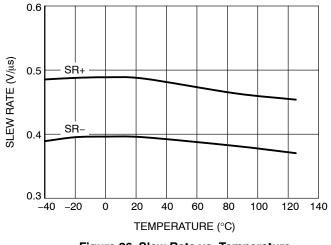

Figure 26. Slew Rate vs. Temperature

#### **Application Information**

The NCS/NCV20081/2/4 family of operational amplifiers is manufactured using ON Semiconductor's CMOS process. Products in this class are general purpose, unity–gain stable amplifiers and include single, dual and quad configurations.

#### Rail-to-Rail Input with No Phase Reversal

The NCS operational amplifiers are designed to prevent phase reversal or any similar issues when the input pins potential exceed the supply voltages by up to 100 mV. Figure 6 shows the input voltage exceeding the supply limits.

The input stage of the NCS/NCV 20081/2/4 family consists of two differential CMOS input stages connected in parallel: the first is constructed using paired PMOS devices and it operates at low common mode input voltages (VCM); the second stage is build using paired NMOS devices to operate at high VCM. The transition between the two input stages occurs at a common mode input voltage of approximately VDD–1.3V and it is visible in Figure 6 (Offset vs. VCM).

#### **Limiting Input Voltages**

In order to prevent damage and/or improper operation of these amplifiers, the application circuit must never expose the input pins to voltages or currents higher than the Absolute Maximum Ratings.

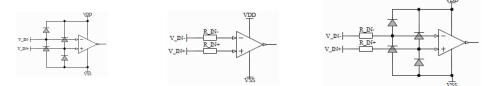

The internal ESD structure includes special diodes to protect the input stages while maintaining a low Input Bias (IIB) current. The input protection circuitry clamp the inputs when the signals applied exceed more than one diode drop below VSS or one diode drop above VDD. Very fast ESD events (within the limits specified) trigger the protection structure so the operational amplifier is not damaged.

However, in some applications, it can be necessary to prevent excessive voltages from reaching the operational amplifier inputs by adding external clamp diodes. A possible solution is presented in Figure 27, where the four low-drop fast diodes (Shottky preferred) are used in parallel with the internal structure to divert the excessive energy to the supply rails where it can be easily dissipated or absorbed by the supply capacitors. The application designer should also take into account that these external diodes add leakage currents and parasitic capacitance that must be considered when evaluating the end-to-end performance of the amplifier stage.

#### **Limiting Input Currents**

In order to prevent damage/ improper operation of these amplifiers, the application circuit must limit the currents flowing in and out of the input pins. A possible solution is presented in Figure 27 by means of the two added series resistors. The minimum value for R\_IN- and R\_IN+ should be calculated using Ohm's Law so they limit the input pin currents to less than the absolute maximum values specified. The application designer should take into account that these resistors also add parasitic inductance that must be considered when evaluating performance.

Combining the current limiting resistors with the voltage limiting diodes creates a solid input protection structure, that can be used to insure reliable operation of the amplifier even in the hardest conditions.

Figure 27. Typical Protection of the Operational Amplifier Inputs

#### Rail-to-Rail Output

The maximum output voltage swing is dependent of the particular output load. According to the specification, the output can reach within 25 mV of either supply rail when load resistance is 10 k $\Omega$ . Figure 15 and Figure 16 shows the load drive capabilities of the part under different conditions. Output current is internally limited to 15 mA typ.

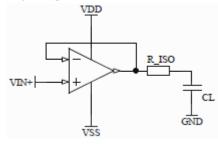

#### **Capacitive Loads**

Driving capacitive loads can create stability problems for voltage feedback opamps, as it is a known possible cause for:

- degraded phase margin

- lowered bandwidth

- gain peaking of the frequency response

- overshoot and ringing of the step response.

While the NCS(V)20081/2/4 family of opamps are capable of driving capacitive loads up to 100 pF, adding a small resistor in series to the output (R\_ISO in Figure 28) will increase the feedback loop's phase margin. This leads to higher stability by making the equivalent load more resistive at high frequencies.

Figure 28. Driving Capacitive Loads

Simulating the application with ON Semiconductor's SPICE models is a good starting point for selecting the isolation resistor's value, and then bench testing the frequency and step response can be used to fine-tune the value according to the desired characteristic.

#### **Unity Gain Bandwidth**

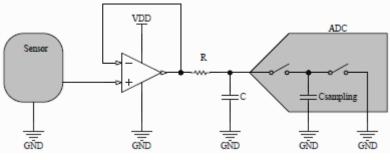

Interfacing a high impedance sensor's output to a relatively low-impedance ADC input usually requires an intermediate stage to avoid unwanted interference of the two devices, and this stage needs to have a high input impedance, a low output impedance and high output current.

The unity gain buffer is recommended here (Figure 29). The ADC's internal sampling capacitor requires a buffer front-end to recharge it faster than the sampling time, and this problem is even worse if more channels are sampled by the same ADC using an internal multiplexer. In

order to achieve a settling time shorter than the multiplexed sampling rate, an RC stage is recommended between the buffer and the ADC input. The R resistor's value should be low enough to charge the capacitor quickly, but at the same time large enough to isolate the capacitive load from the opamp's output to preserve phase margin. When transients are generated by the sensor's output, first the two opamp's inputs see a high differential voltage between them, then the output settles and brings the inverting input back to the correct voltage.

To successfully accommodate for example a 0.1 V to 4 V sensor signal, the opamp's differential input range of the NCS(V) 20081/2/4 series is close to the supply range VDD–VSS, and the output will match the input. The differential input voltage is limited only by the ESD protection structure and not by back–to–back diodes between inputs.

Figure 29. Unity Gain Buffer Stage for Sampling with ADC

#### **Power Supply Bypassing**

For AC, the power supply pins (VDD and VSS for split supply, VDD for single supply) should be bypassed locally with a quality capacitor in the range of 100 nF (ceramics are recommended for their low ESR and good high frequency response) as close as possible to the opamp's supply pins.

For DC, a bulk capacitor in the range of  $1 \mu F$  within inches distance from the opamp can provide the increased currents required to drive higher loads.

#### **Unused Operational Amplifiers**

Occasionally not all the opamps offered in the quad packages are needed for a specific application. They can be connected as "buffering ground" as shown in Figure 30, a solution that does not need any extra parts. Connecting them differently (inputs split to rails, left floating, etc.) can sometimes cause unwanted oscillation, crosstalk, increased current consumption, or add noise to the supply rails.

Figure 30. Unused Operational Amplifiers

#### PCB Surface Leakage

The Printed Circuit Board's surface leakage effects should be estimated if the lowest possible input bias current is critical. Dry environment surface current increases further when the board is exposed to humidity, dust or chemical contamination. For harsh environment conditions, protecting the entire board surface (with all the exposed metal pins and soldered areas) is advised. Conformal coating or potting the board in resin proves effective in most cases.

An alternate solution for reduced leakage is the use of guard rings around sensitive pins and pads. A proper guard ring should have low impedance and be biased to the same voltage as the sensitive pin so no current flows in between.

For an inverting amplifier, the non-inverting input is usually connected to supply's ground (or virtual ground at half the rail voltage in single supply applications) so it can represent a good ring solution. When routing the PCB traces, create a closed perimeter around the inverting input pad (which carries the signal) and connect it to the non-inverting input.

For a non-inverting amplifier, use a similarly shaped (rectangle or circle) copper trace around the non-inverting input pad (which carries the signal) and connect it to the inverting input pin, which presents a much lower impedance thanks to the feedback network.

#### **PCB Routing Recommendations**

Even when some operational amplifier is expected to amplify only the useful DC signal, it can also pick some high frequency noise altogether and amplify it accordingly, if the design allows it. In order to reach the specified operational amplifier parameters and to avoid high frequency interference issues, it is recommended that the PCB layout respects some basic guidelines:

- A dedicated layer for the ground plane should be used whenever possible and all supply decoupling capacitors should connect to it by vias.

- Copper traces should be as short as possible.

- High current paths should not be shared by small signal or low current traces.

- If present, switching power supply blocks should be kept away from the analog sensitive areas to avoid potential conducted and radiated noise issues.

- When different circuit taxonomies share the same board, it is recommended to keep separated the power areas, the digital areas and the small signal analog areas. Small-signal parts in the signal path should be placed as close as possible to the opamp's input pins.

- Metal shielding the sensitive areas and the "offender" blocks may be required in some cases.

In a sensitive application, a good PCB design can take longer but it will save troubleshooting time.

#### **Applications Example**

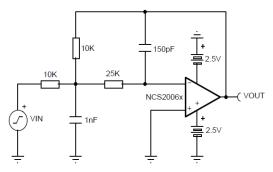

#### Second Order Active Low Pass Filter

Using an opamp with a low input bias current allows the use of higher value resistors and smaller capacitors for the same filter application. As a trade-off for the increased impedance and lower consumption obtained, the higher value resistors may also bring higher noise and sensibility to board contamination, and possibly frequency response changes (the increased R\*C time constant due to parasitic capacitances can change the gain vs. frequency plot).

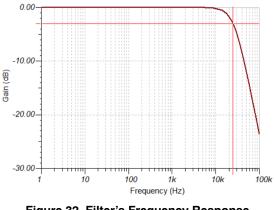

An example of an active low-pass filter using the NCS2008x operational amplifier can be found in Figure 31. The filter's 3 dB Bandwidth is approximately 25 KHz, followed by a -40 dB/dec roll-off as in Figure 32. Such filters with flat response in the sampled signal band are recommended as a front-end for ADC's to avoid aliasing.

Figure 31. Second Order Active Low Pass Filter

Figure 32. Filter's Frequency Response

Using the P–SPICE models provided by ON Semiconductor is recommended as a starting point for component selection, and then values can be further fine–tuned during bench testing the application.

# onsemí

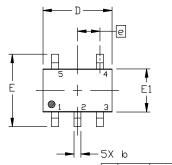

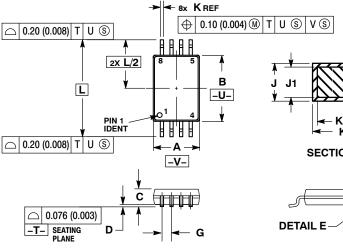

#### SC-88A (SC-70-5/SOT-353) CASE 419A-02 ISSUE M

NDTES: 1. DIM

2.

З.

4.

DATE 11 APR 2023

#### RECOMMENDED MOUNTING FOOTPRINT

For additional information on our Pb-Free strategy and soldering details, please download the DN Semiconductor Soldering and Mounting Techniques Reference Manual, SDLDERRM/D.

| лтм | MI   | LLIMETE  | RS   |  |

|-----|------|----------|------|--|

| DIM | MIN. | NDM.     | MAX. |  |

| Α   | 0.80 | 0.95     | 1.10 |  |

| A1  |      |          | 0.10 |  |

| A3  |      | 0.20 REF |      |  |

| b   | 0.10 | 0.20     | 0.30 |  |

| C   | 0.10 |          | 0.25 |  |

| D   | 1.80 | 2.00     | 2.20 |  |

| E   | 2.00 | 2.10     | 2.20 |  |

| E1  | 1.15 | 1.25     | 1.35 |  |

| e   |      | 0.65 BSI | C    |  |

| L   | 0.10 | 0.15     | 0.30 |  |

DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

DIMENSIONS D AND E1 DO NOT INCLUDE MOLD FLASH,

PROTRUSIONS, OR GATE BURRS.MOLD FLASH, PROTRUSIONS,

OR GATE BURRS SHALL NOT EXCEED 0.1016MM PER SIDE.

CONTROLLING DIMENSION: MILLIMETERS 419A-01 DBSDLETE, NEW STANDARD 419A-02

### **GENERIC MARKING**

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

(Note: Microdot may be in either location)

| DOCUMENT NUMBER: 98ASB42984B Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.   DESCRIPTION: SC-88A (SC-70-5/SOT-353) PAGE 1 OF 1 | PIN 1. EMITTER 2<br>2. BASE 2<br>3. EMITTER 1<br>4. COLLECTOR<br>5. COLLECTOR 2/BASE | PIN 1. BASE<br>2. EMITTER<br>3. BASE<br>4. COLLECTOR<br>1 5. COLLECTOR | PIN 1. CATHODE<br>2. COLLECTOR<br>3. N/C<br>4. BASE<br>5. EMITTER | PIN 1. ANODE<br>2. CATHODE<br>3. ANODE<br>4. ANODE<br>5. ANODE | style callout. If style t<br>out in the datasheet r<br>datasheet pinout or p | refer to the device |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------|---------------------|

| DESCRIPTION: SC-88A (SC-70-5/SOT-353) PAGE 1 OF 1                                                                                                                                                                                                                    | DOCUMENT NUMBER:                                                                     | 98ASB42984B                                                            |                                                                   |                                                                |                                                                              |                     |

|                                                                                                                                                                                                                                                                      | DESCRIPTION:                                                                         | SC-88A (SC-70-                                                         | 5/SOT–353)                                                        |                                                                |                                                                              | PAGE 1 OF 1         |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights of others.

XXX = Specific Device Code

M = Date Code = Pb-Free Package

# onsemi

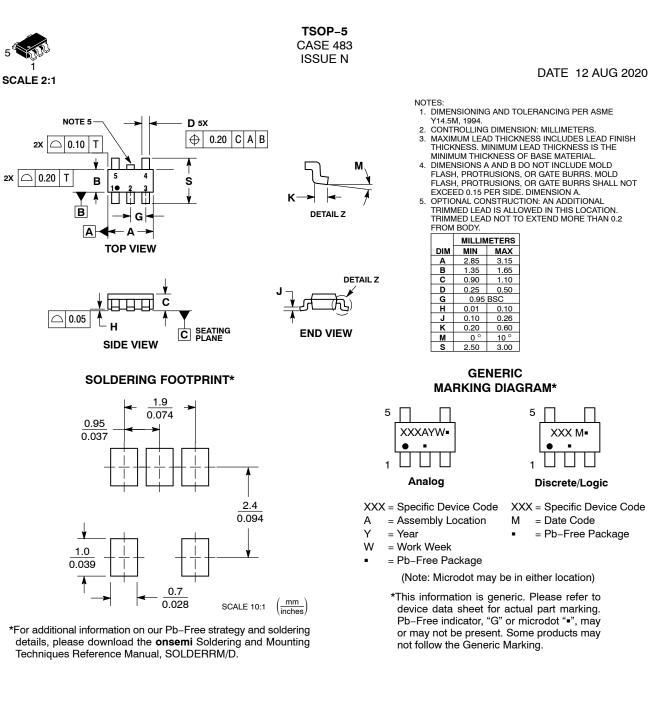

| DOCUMENT NUMBER:                                                                     | 98ARB18753C Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |  |  |  |  |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|

| DESCRIPTION:                                                                         | TSOP-5 PAGE 1 OF                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PAGE 1 OF 1 |  |  |  |  |

| the right to make changes without furth<br>purpose, nor does <b>onsemi</b> assume an | er notice to any products herein. <b>onsemi</b> making liability arising out of the application or use                                                                                          | onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights or others. |             |  |  |  |  |

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98AON25711D Electronic versions are uncontrolled except when accessed directly from the Document Repository<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6 PIN UDFN, 1.6X1.6, 0.5P                                                                                                                                                                      |  | PAGE 1 OF 1 |  |  |

| ON Semiconductor and ()) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the |                                                                                                                                                                                                |  |             |  |  |

© Semiconductor Components Industries, LLC, 2019

rights of others.

# onsemí

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### STYLES ON PAGE 2

| DOCUMENT NUMBER:                                                                     | 98ASB42564B Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |                                                                                                                                                                                                                                                                                                       |                           |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| DESCRIPTION:                                                                         | SOIC-8 NB PAGE 1 OF                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                       | PAGE 1 OF 2               |

| the right to make changes without furth<br>purpose, nor does <b>onsemi</b> assume ar | er notice to any products herein. <b>onsemi</b> make<br>ny liability arising out of the application or use                                                                                      | LLC dba <b>onsemi</b> or its subsidiaries in the United States and/or other courses no warranty, representation or guarantee regarding the suitability of its proof any product or circuit, and specifically disclaims any and all liability, incle under its patent rights nor the rights of others. | oducts for any particular |

#### SOIC-8 NB CASE 751-07 **ISSUE AK**

STYLE 1: PIN 1. EMITTER COLLECTOR 2. 3. COLLECTOR 4. EMITTER 5. EMITTER BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6 BASE. DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. DRAIN 8. STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. TXE 4. 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C REXT З. 4. GND 5. IOUT IOUT 6. IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2 EMITTER, #1 BASE, #2 З. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2 6.

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: GROUND PIN 1. BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND 6 BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3 P-SOURCE P-GATE 4. P-DRAIN 5 6. P-DRAIN N-DRAIN 7. N-DRAIN 8. STYLE 18: PIN 1. ANODE ANODE 2. SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. CATHODE 8. STYLE 22 PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3 COMMON CATHODE/VCC 4. I/O LINE 3 COMMON ANODE/GND 5. 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND STYLE 26: PIN 1. GND 2 dv/dt З. ENABLE 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 З. SOURCE 2 4 SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5.

6.

7.

8 GATE 1

SOURCE 1/DRAIN 2

STYLE 3: PIN 1. DRAIN, DIE #1 DRAIN, #1 2. DRAIN, #2 З. DRAIN, #2 4. GATE, #2 5. SOURCE, #2 6. 7 GATE #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS THIRD STAGE SOURCE GROUND З. 4. 5. DRAIN 6. GATE 3 SECOND STAGE Vd 7. FIRST STAGE Vd 8. STYLE 11: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. З. GATE 2 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 ANODE 1 3 ANODE 1 4. 5. CATHODE, COMMON CATHODE, COMMON CATHODE, COMMON 6. 7. CATHODE, COMMON 8. STYLE 19: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 MIRROR 1 8. STYLE 23: PIN 1. LINE 1 IN COMMON ANODE/GND COMMON ANODE/GND 2. 3 LINE 2 IN 4. LINE 2 OUT 5. COMMON ANODE/GND COMMON ANODE/GND 6. 7. 8. LINE 1 OUT STYLE 27: PIN 1. ILIMIT OVI O 2 UVLO З. 4. INPUT+ 5. 6. SOURCE SOURCE SOURCE 7. 8 DRAIN

#### DATE 16 FEB 2011

STYLE 4: PIN 1. 2. ANODE ANODE ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 З. BASE #2 COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE 2. 3. GATE 4. 5. DRAIN 6 DRAIN DRAIN 7. 8. DRAIN STYLE 16 EMITTER, DIE #1 PIN 1. 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE EMITTER 2. 3 COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE 6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK 8 VIN

| DOCUMENT NUMBER: | 98ASB42564B Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|

| DESCRIPTION:     | SOIC-8 NB                                                                                                                                                                                       |  | PAGE 2 OF 2 |  |

|                  |                                                                                                                                                                                                 |  |             |  |

onsem and of isor in are trademarks or semiconductor compension instructions, the do onsem or its subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced stat purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

7.

8

COLLECTOR, #1

COLLECTOR, #1

# DUSEM

0.068

0.019

0.344

0.244

DIMENSIONS: MILLIMETERS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### **STYLES ON PAGE 2**

Electronic versions are uncontrolled except when accessed directly from the Document Repository. DOCUMENT NUMBER: 98ASB42565B Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. **DESCRIPTION:** SOIC-14 NB PAGE 1 OF 2 onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

#### SOIC-14 CASE 751A-03 ISSUE L

#### DATE 03 FEB 2016

| STYLE 1:<br>PIN 1. COMMON CATHODE<br>2. ANODE/CATHODE<br>3. ANODE/CATHODE<br>4. NO CONNECTION<br>5. ANODE/CATHODE<br>6. NO CONNECTION<br>7. ANODE/CATHODE<br>8. ANODE/CATHODE<br>9. ANODE/CATHODE<br>10. NO CONNECTION<br>11. ANODE/CATHODE<br>12. ANODE/CATHODE<br>13. NO CONNECTION<br>14. COMMON ANODE | STYLE 2:<br>CANCELLED                                                                                                                                                                                   | STYLE 3:<br>PIN 1. NO CONNECTION<br>2. ANODE<br>3. ANODE<br>4. NO CONNECTION<br>5. ANODE<br>6. NO CONNECTION<br>7. ANODE<br>8. ANODE<br>9. ANODE<br>10. NO CONNECTION<br>11. ANODE<br>12. ANODE<br>13. NO CONNECTION<br>14. COMMON CATHODE                                              | STYLE 4:<br>PIN 1. NO CONNECTION<br>2. CATHODE<br>3. CATHODE<br>4. NO CONNECTION<br>5. CATHODE<br>6. NO CONNECTION<br>7. CATHODE<br>8. CATHODE<br>10. NO CONNECTION<br>11. CATHODE<br>12. CATHODE<br>13. NO CONNECTION<br>14. COMMON ANODE                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 5:<br>PIN 1. COMMON CATHODE<br>2. ANODE/CATHODE<br>3. ANODE/CATHODE<br>4. ANODE/CATHODE<br>5. ANODE/CATHODE<br>6. NO CONNECTION<br>7. COMMON ANODE<br>8. COMMON CATHODE<br>9. ANODE/CATHODE<br>10. ANODE/CATHODE<br>11. ANODE/CATHODE<br>12. ANODE/CATHODE<br>13. NO CONNECTION<br>14. COMMON ANODE | STYLE 6:<br>PIN 1. CATHODE<br>2. CATHODE<br>3. CATHODE<br>4. CATHODE<br>5. CATHODE<br>6. CATHODE<br>7. CATHODE<br>8. ANODE<br>9. ANODE<br>10. ANODE<br>11. ANODE<br>12. ANODE<br>13. ANODE<br>14. ANODE | STYLE 7:<br>PIN 1. ANODE/CATHODE<br>2. COMMON ANODE<br>3. COMMON CATHODE<br>4. ANODE/CATHODE<br>5. ANODE/CATHODE<br>6. ANODE/CATHODE<br>7. ANODE/CATHODE<br>9. ANODE/CATHODE<br>10. ANODE/CATHODE<br>11. COMMON CATHODE<br>12. COMMON CATHODE<br>13. ANODE/CATHODE<br>14. ANODE/CATHODE | STYLE 8:<br>PIN 1. COMMON CATHODE<br>2. ANODE/CATHODE<br>3. ANODE/CATHODE<br>4. NO CONNECTION<br>5. ANODE/CATHODE<br>6. ANODE/CATHODE<br>7. COMMON ANODE<br>8. COMMON ANODE<br>9. ANODE/CATHODE<br>10. ANODE/CATHODE<br>11. NO CONNECTION<br>12. ANODE/CATHODE<br>13. ANODE/CATHODE<br>14. COMMON CATHODE |

| DOCUMENT NUMBER: | 98ASB42565B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-14 NB  |                                                                                                                                                                                     | PAGE 2 OF 2 |  |

|                  |             |                                                                                                                                                                                     |             |  |

onsemi and ONSEMI: are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

| DOCUMENT NUMBER:                                                                  | 98ASB14087C                                                                                 | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.                                                                                                                          |                                                       |  |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|

| DESCRIPTION:                                                                      | MICRO8                                                                                      |                                                                                                                                                                                                                                                                                                              | PAGE 1 OF 1                                           |  |

| ON Semiconductor reserves the right<br>the suitability of its products for any pa | to make changes without further notice to an<br>articular purpose, nor does ON Semiconducto | stries, LLC dba ON Semiconductor or its subsidiaries in the United States<br>y products herein. ON Semiconductor makes no warranty, representation<br>r assume any liability arising out of the application or use of any product o<br>acidental damages. ON Semiconductor does not convey any license under | or guarantee regarding<br>r circuit, and specifically |  |

# Onsemi

SCALE 2:1

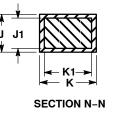

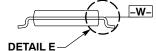

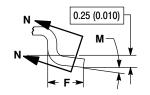

TSSOP-8 CASE 948S **ISSUE C**

DETAIL E

DATE 20 JUN 2008

NOTES:

- IOTES: 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: MILLIMETER. 3. DIMENSION A DOES NOT INCLUDE MOLD FLASH. PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15

- (0.006) PER SIDE. 4. DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010)

- PER SIDE. 5. TERMINAL NUMBERS ARE SHOWN FOR

- REFERENCE ONLY. DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE -W-. 6.

|     | MILLIMETERS |      | INC       | HES   |

|-----|-------------|------|-----------|-------|

| DIM | MIN         | MAX  | MIN       | MAX   |

| Α   | 2.90        | 3.10 | 0.114     | 0.122 |

| В   | 4.30        | 4.50 | 0.169     | 0.177 |

| С   |             | 1.10 |           | 0.043 |

| D   | 0.05        | 0.15 | 0.002     | 0.006 |

| F   | 0.50        | 0.70 | 0.020     | 0.028 |

| G   | 0.65        | BSC  | 0.026 BSC |       |

| J   | 0.09        | 0.20 | 0.004     | 0.008 |

| J1  | 0.09        | 0.16 | 0.004     | 0.006 |

| К   | 0.19        | 0.30 | 0.007     | 0.012 |

| K1  | 0.19        | 0.25 | 0.007     | 0.010 |

| L   | 6.40 BSC    |      | 0.252     | BSC   |

| М   | 0°          | 8°   | 0°        | 8°    |