# **TF23892M**

### 3-Phase Half-Bridge Gate Driver

#### **Features**

- Three floating high-side drivers in bootstrap operation to 600V

- 350mA source / 650mA sink output current capability

- Outputs tolerant to negative transients, dV/dt immune

- Logic input 3.3V capability

- Internal deadtime of 290ns to protect MOSFETs

- Wide gate driver supply voltage range: 10V to 20V

- Matched prop delay for all channels

- Outputs out of phase with inputs

- Schmitt triggered logic inputs

- Cross conduction prevention logic

- Undervoltage lockout for all channels

- Overcurrent protection shuts down drivers

- Extended temperature range: -40°C to +125°C

#### **Applications**

- 3-Phase Motor Inverter Driver

- White Goods Air Conditioner, Washing Machine, Refrigerator

- Industrial Motor Inverter Power Tools, Robotics

- General Purpose 3-Phase Inverter

#### **Description**

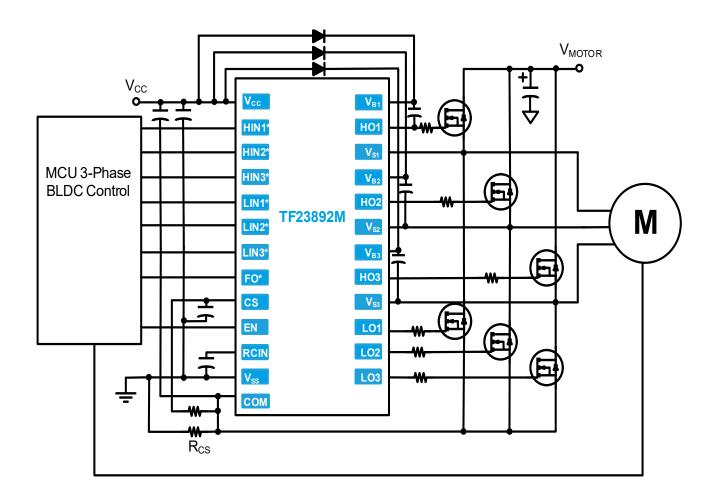

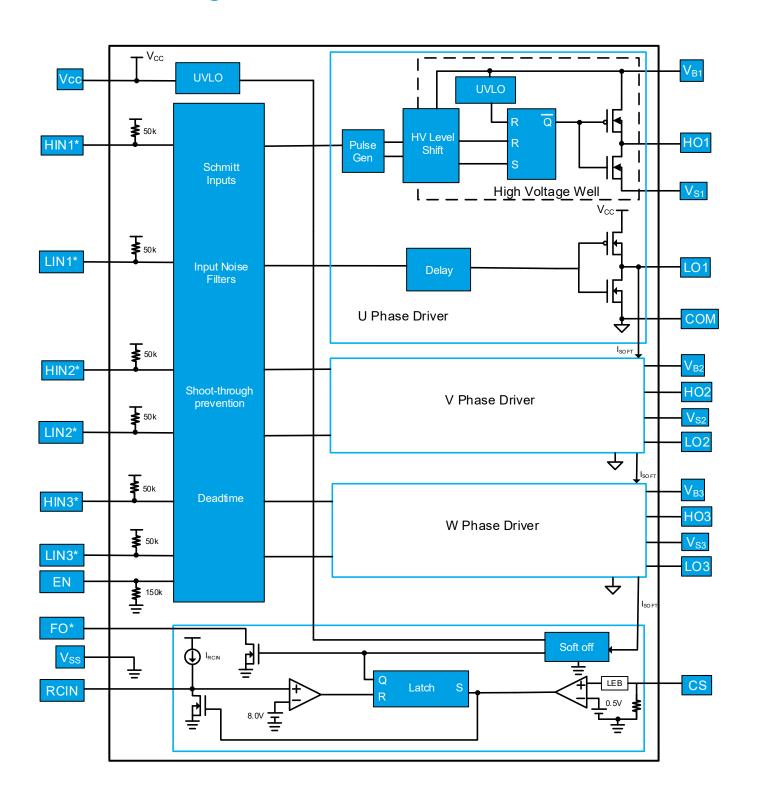

The TF23892M is a three-phase gate driver IC designed for high voltage, high speed applications, driving N-channel MOSFETs and IGBTs in a half-bridge configuration. TF Semiconductor's high voltage process enables the TF23892M high sides to switch to 600V in a bootstrap operation.

The TF23892M logic inputs are compatible with standard TTL and CMOS levels (down to 3.3V) to interface easily with controlling devices and are enabled low to better function in high noise environments. The driver outputs feature high pulse current buffers designed for minimum driver cross conduction.

The TF23892M offers numerous protection functions. A shoot-through protection logic prevents both outputs being high with both inputs high (fault state), an undervoltage lockout (UVLO) for  $V_{\rm CC}$  shuts down all drivers through an internal fault control, and a UVLO for  $V_{\rm BS}$  shuts down the respective high side output. Also an overcurrent protection will terminate the six outputs. Both the  $V_{\rm CC}$  UVLO and the overcurrent protection trip an automatic fault clear with a timing that is adjustable with an external capacitor.

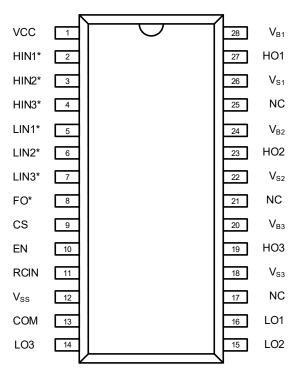

The TF23892M is offered in SOIC 28 package and operates over an extended -40 °C to +125 °C temperature range.

#### SOIC-28

#### **Ordering Information**

| PART NUMBER  | PACKAGE | PACK / Qty | MARK               |

|--------------|---------|------------|--------------------|

| TF23892M-TLS | SOIC-28 | Tube / 25  | YYWW               |

| TF23892M-TLH | SOIC-28 | T&R / 1500 | TF23892M<br>Lot ID |

www.tfsemi.com Rev. 1.0

# **Typical Application**

## **Functional Block Diagram**

**Top View:** SOIC-28

# **Pin Descriptions**

| PIN NAME                                          | PIN NUMBER | PIN DESCRIPTION                                                     |

|---------------------------------------------------|------------|---------------------------------------------------------------------|

| VCC                                               | 1          | Low-side and logic fixed supply                                     |

| HIN1*, HIN2*, HIN3*                               | 2, 3, 4    | Logic input for high-side gate driver output, out of phase with HO. |

| LIN1*, LIN2*, LIN3*                               | 5, 6, 7    | Logic input for low-side gate driver output, out of phase with LO.  |

| FO*                                               | 8          | Fault output with open drain (fault with over-current and VCC UVLO) |

| CS                                                | 9          | Analog input for over-current shutdown                              |

| EN                                                | 10         | Logic input for functionality, I/O logic functions when EN is high. |

| RCIN                                              | 11         | An external RC network input used to define FAULT CLEAR delay       |

| V <sub>ss</sub>                                   | 12         | Logic ground                                                        |

| COM                                               | 13         | Low-side driver return                                              |

| LO3, LO2, LO1                                     | 14, 15, 16 | Low-side gate driver output                                         |

| NC                                                | 17, 21, 25 | No Connect                                                          |

| V <sub>S3</sub> ,V <sub>S2</sub> ,V <sub>S1</sub> | 18, 22, 26 | High-side floating supply return                                    |

| HO3, HO2, HO1                                     | 19, 23, 27 | High-side gate driver output                                        |

| V <sub>B3</sub> ,V <sub>B2</sub> ,V <sub>B1</sub> | 20, 24, 28 | High-side floating supply                                           |

### **Absolute Maximum Ratings (NOTE1)**

### 3-Phase Half-Bridge Gate Driver

| V <sub>B</sub> - High-side floating supply voltage        | 0.3V to +624V                       |

|-----------------------------------------------------------|-------------------------------------|

| V <sub>s</sub> - High-side floating supply offset voltage | $V_B$ -24V to $V_B$ +0.3V           |

| V <sub>HO</sub> -High-sidefloating output voltage         | $V_{s}$ -0.3VtoV <sub>B</sub> +0.3V |

| V <sub>10</sub> - Low-side output voltage                 | 0.3V to $V_{cc}$ +0.3V              |

| $dV_s/dt$ - Offset supply voltage transient               | 50 V/ns                             |

| V <sub>cc</sub> - Low-side fixed supply voltage           | 0.3V to +24V                        |

| V <sub>IN</sub> -Logic input voltage(HIN*,LIN*,CS,ENanc   | dFO*)0.3Vto5.5V                     |

**NOTE1** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| $P_D$ - Package power dissipation at $T_A \le 25$ °C SOIC-28 | 2.3W    |

|--------------------------------------------------------------|---------|

| SOIC-28 Thermal Resistance (NOTE2)                           |         |

| $\theta_{\text{IC}}$                                         | 45 °C/W |

| $\theta_{IA}$                                                |         |

| 30                                                           |         |

| T <sub>1</sub> - Junction operating temperature              | +150°C  |

| T <sub>1</sub> - Lead Temperature (soldering, 10 seconds)    |         |

| T <sub>sta</sub> - Storage temerature                        |         |

**NOTE2** Thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

## **Recommended Operating Conditions**

| Symbol          | Parameter                                  | MIN                 | MAX                 | Unit |

|-----------------|--------------------------------------------|---------------------|---------------------|------|

| V <sub>B</sub>  | High side floating supply absolute voltage | V <sub>s</sub> + 10 | V <sub>s</sub> + 20 | V    |

| V <sub>s</sub>  | High side floating supply offset voltage   | NOTE3               | 600                 | V    |

| V <sub>HO</sub> | High side floating output voltage          | V <sub>s</sub>      | V <sub>B</sub>      | V    |

| V <sub>CC</sub> | Low side fixed supply voltage              | 10                  | 20                  | V    |

| V <sub>LO</sub> | Low side output voltage                    | СОМ                 | V <sub>cc</sub>     | V    |

| V <sub>IN</sub> | Logic input voltage (HIN*, LIN*, CS, EN)   | V <sub>ss</sub>     | 5                   | V    |

| V <sub>FO</sub> | Fault output Voltage                       | V <sub>ss</sub>     | V <sub>cc</sub>     | V    |

| V <sub>ss</sub> | Logic Ground                               | -5                  | 5                   | С    |

| T <sub>A</sub>  | Ambient temperature                        | -40                 | 125                 | °C   |

**NOTE3** Logic operational for VS of -5V to +600V.

#### **DC Electrical Characteristics** (NOTE4)

$\rm V_{BIAS}(\rm V_{CC}, \rm V_{BS}) = 15V, \rm T_A = 25~^{\circ}C$  , unless otherwise specified.

| Symbol                                | Parameter                                                                   | Conditions                                  | MIN | TYP | MAX | Unit |

|---------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------|-----|-----|-----|------|

| V <sub>IH</sub>                       | Logic "0" input voltage                                                     |                                             | 2.4 |     |     |      |

| V <sub>IL</sub>                       | Logic "1" input voltage                                                     | NOTE5                                       |     |     | 0.8 |      |

| V <sub>OH</sub>                       | High level output voltage, V <sub>BIAS</sub> - V <sub>O</sub>               | $I_0 = 0 \text{mA}$                         |     |     | 0.1 | V    |

| V <sub>OL</sub>                       | Low level output voltage, V <sub>o</sub>                                    | $I_{O} = 0mA$                               |     |     | 0.1 |      |

| I <sub>LK</sub>                       | Offset supply leakage current                                               | VB = VS = 600V                              |     |     | 10  |      |

| I <sub>BSQ</sub>                      | Quiescent V <sub>BS</sub> supply current                                    | V <sub>IN</sub> = 0V or 5V, EN=0V           | 10  | 85  | 130 | μΑ   |

| I <sub>ccq</sub>                      | Quiescent V <sub>CC</sub> supply current                                    | V <sub>IN</sub> = 0V or 5V, EN=0V           |     | 1.1 | 1.6 | mA   |

| I <sub>IN+</sub>                      | Logic input bias current (HO=LO=HIGH)                                       | V <sub>IN</sub> = 0V                        |     | 130 | 200 |      |

| I <sub>IN-</sub>                      | Logic input bias current (HO=LO=LOW)                                        | V <sub>IN</sub> = 5V                        |     | 3.0 | 20  | μΑ   |

| I <sub>EN+</sub>                      | Logic Enable "1" input bias current                                         | V <sub>EN</sub> = 5V                        |     | 50  | 80  | μΑ   |

| I <sub>EN-</sub>                      | Logic Enable "0" input bias current                                         | V <sub>EN</sub> = 0V                        |     |     | 2   | μА   |

| $V_{\text{BSUV+}}$ $V_{\text{CCUV+}}$ | $V_{BS}$ and $V_{CC}$ supply under-voltage positive going threshold         |                                             | 7.6 | 8.9 | 9.9 |      |

| $V_{\text{BSUV-}}$                    | $V_{\rm BS}$ and $V_{\rm CC}$ supply under-voltage negative going threshold |                                             | 7.1 | 8.3 | 9.4 | V    |

| I <sub>0+</sub>                       | Output high short circuit pulsed current                                    | $V_O = 0V$ , PW $\leq 10 \mu s$             | 250 | 350 |     |      |

| I <sub>0-</sub>                       | Output low short circuit pulsed current                                     | $V_0 = 15V, PW \le 10 \mu s$                | 500 | 650 |     | mA   |

| V <sub>ITH+</sub>                     | Overcurrent detect positive threshold                                       |                                             | 400 | 500 | 600 | mV   |

| V <sub>ITH-</sub>                     | Overcurrent detect negative threshold                                       |                                             | 340 | 420 | 500 | mV   |

| I <sub>CSIN</sub>                     | Short-circuit input current                                                 | V <sub>CSIN</sub> =1V                       | 5   | 15  | 20  |      |

| I <sub>RCIN</sub>                     | RCIN Internal current source                                                |                                             | 6   | 8   | 10  |      |

| V <sub>RCINTH+</sub>                  | RCIN Positive going threshold voltage                                       |                                             |     | 8.0 |     | V    |

| V <sub>RCINTH</sub> -                 | RCIN Negative going threshold voltage (NOTE6)                               |                                             |     | 5   |     | V    |

| V <sub>FOL</sub>                      | Fault output low level voltage                                              | V <sub>CS</sub> =1V, I <sub>FO</sub> =1.5mA |     | 0.2 | 0.5 | V    |

| R <sub>DSRCIN</sub>                   | RCIN On resistance                                                          | I <sub>RCIN</sub> =1.5mA                    | 40  | 75  | 110 | Ω    |

| R <sub>DSFO</sub>                     | Fault output on resistance                                                  | I <sub>FO</sub> =1.5mA                      | 80  | 130 | 180 | Ω    |

**NOTE4** The  $V_{NV}$   $V_{THV}$  and  $I_{NV}$  parameters are referenced to  $V_{SS}$  and are applicable to all six channels (HIN1,2,3\* and LIN1,2,3\*). The  $V_0$  and  $I_0$  parameters are applicable to the outputs (H01,2,3 and L01,2,3 and are referenced to COM.

**NOTE5** For optimal operation, it is recommended that the input pulse (to HINx\* and LINx\*) should have an amplitude of 2.4V minimum with a pulse width of 600ns minimum. **NOTE6** Guaranteed by design

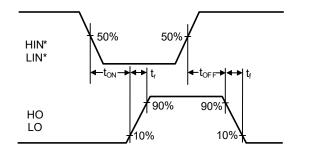

### **AC Electrical Characteristics**

$\rm V_{BIAS}(V_{CC},V_{BS})$  = 15V,  $\rm C_L$  = 1000pF, and  $\rm T_A$  = 25  $^{\circ}\rm C$  , unless otherwise specified.

| Symbol              | Parameter                                            | Conditions                                          | MIN | ТҮР | MAX | Unit |

|---------------------|------------------------------------------------------|-----------------------------------------------------|-----|-----|-----|------|

| t <sub>on</sub>     | Turn-on propogation delay                            | $V_s = 0V$                                          | 200 | 270 | 460 |      |

| t <sub>off</sub>    | Turn-off propogation delay                           | $V_s = 0V$                                          | 200 | 270 | 460 | ns   |

| t <sub>r</sub>      | Turn-on rise time                                    |                                                     |     | 40  | 150 |      |

| t <sub>f</sub>      | Turn-off fall time                                   | $V_s = 0V$                                          |     | 25  | 60  |      |

| t <sub>DM</sub>     | Delay matching                                       |                                                     |     |     | 50  | ns   |

| t <sub>EN</sub>     | Enable low to output shutdown delay                  |                                                     | 225 | 260 | 425 | ns   |

| t <sub>BLT</sub>    | CS Pin leading-edge blanking time                    |                                                     | 200 | 300 | 400 | ns   |

| t <sub>FLT</sub>    | Time from CS triggering to FO*                       | From V <sub>CS</sub> = 1V to FO* turn off           | 360 | 550 | 760 | ns   |

| t <sub>ITRIP</sub>  | Time from CS triggering to all gate outputs turn off | From V <sub>cs</sub> = 1V to starting gate turn off | 420 | 615 | 820 | ns   |

| t <sub>FLTIN</sub>  | Input filtering time (HIN*, LIN*, EN)                |                                                     |     | 250 |     | ns   |

| t <sub>FLTCLR</sub> | Fault clear time (NOTE5)                             | C <sub>RCIN</sub> = 2nF                             |     | 3.1 |     | ms   |

| t <sub>DT</sub>     | Deadtime                                             |                                                     | 200 | 290 | 420 | ns   |

| t <sub>DTM</sub>    | Deadtime matching                                    |                                                     |     |     | 50  | ns   |

| t <sub>PM</sub>     | Output pulse width matching (NOTE7)                  | PW <sub>IN</sub> >1μs                               |     | 50  | 75  | ns   |

**NOTE7**  $t_{PM}$  is defined as  $PW_{IN}$  -  $PW_{OUT}$ .

## **Timing Waveforms**

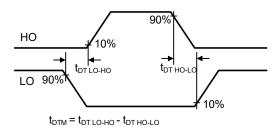

Figure 1. Switching Time Waveform Definitions

Figure 2. Deadtime Waveform Definitions

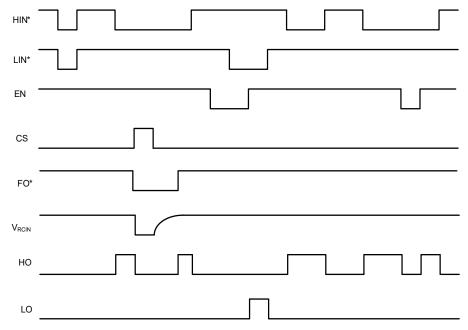

Figure 3. Input/Output Timing Diagram

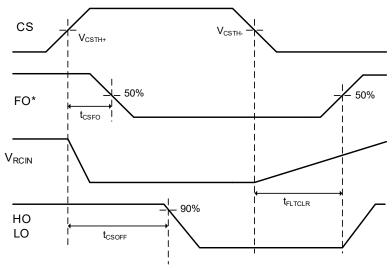

Figure 4. Overcurrent Timing Definitions

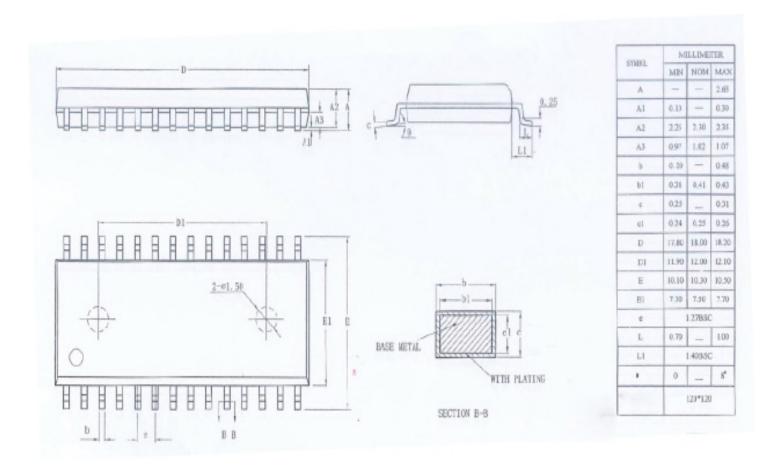

# **Package Dimensions (SOIC-28)**

3-Phase Half-Bridge Gate Driver

Please contact support@tfsemi.com for package availability.

10

#### 3-Phase Half-Bridge Gate Driver

| Rev. | Change                     | Owner        | Date       |

|------|----------------------------|--------------|------------|

| 1.0  | First Release AI datasheet | Raj Selvaraj | 06/15/2021 |

#### **Important Notice**

TF Semiconductor Solutions (TFSS) PRODUCTS ARE NEITHER DESIGNED NOR INTENDED FOR USE IN MILITARY AND/OR AEROSPACE, AUTOMOTIVE OR MEDICAL DEVICES OR SYSTEMS UNLESS THE SPECIFIC TFSS PRODUCTS ARE SPECIFICALLY DESIGNATED BY TFSS FOR SUCH USE. BUYERS ACKNOWLEDGE AND AGREE THAT ANY SUCH USE OF TFSS PRODUCTS WHICH TFSS HAS NOT DESIGNATED FOR USE IN MILITARY AND/OR AEROSPACE, AUTOMOTIVE OR MEDICAL DEVICES OR SYSTEMS IS SOLELY AT THE BUYER'S RISK.

TFSS assumes no liability for application assistance or customer product design. Customers are responsible for their products and applications using TFSS products.

Resale of TFSS products or services with statements different from or beyond the parameters stated by TFSS for that product or service voids all express and any implied warranties for the associated TFSS product or service. TFSS is not responsible or liable for any such statements.

©2021 TFSS. All Rights Reserved. Information and data in this document are owned by TFSS wholly and may not be edited, reproduced, or redistributed in any way without the express written consent from TFSS.

For additional information please contact support@tfsemi.com or visit www.tfsemi.com.