# **NMOS Motor Full-Bridge Gate Driver**

## **FEATURES**

- . Wide 5V to 40V Input Voltage Range

- Single Channel H-bridge Gate Driver

- Drives Four External N-channel MOSFETs

Supports 100% Pulse Width Modulation

- (PWM) Duty Cycle

- . OCP Threshold Voltage (V<sub>DS</sub>) Adjustable:

- 0.12V, 0.24V, 0.48V, 0.96V, Disable

- . Peak Source/Sink Current: 250mA/500mA

- . Supports 1.8V,3.3V and 5V Logical Inputs

- . Low-Power Sleep Mode

- . Protection Features

- VM Under-voltage Lockout (UVLO)

- Charge Pump Undervoltage Lockout (CPUV)

- Overcurrent Protection (OCP)

- Thermal Shutdown (TSD)

- Thermally Enhanced Surface Mount Package

- QFN3x3-16

# **APPLICATIONS**

- . DC Brush Motors

- . Automotive Actuators

- . Automotive brushed DC motors

- . Power seat modules

- . Door module

- . Body control modules

- . Power sunroof

## **GENERAL DESCRIPTION**

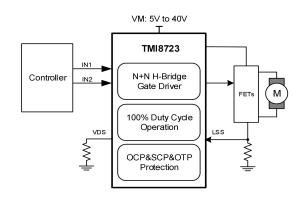

The TMI8723 is a gate driver IC designed for H- bridge driver applications. It is capable of driving H-bridge consisting of four N- channel power MOSFETs up to 40V.

The TMI8723 integrates a regulated charge pump to generate gate drive power,Peak Sink and Source current can be 500mA and 250mA. At the same time, TMI8723 can set the value of the overcurrent point through the pin VDS.

Internal protection features include programmable short-circuit protection, overcurrent protection, undervoltage lockout, and thermal shutdown.

The TMI8723 is available in a QFN-16 (3mmx3mm) package with an exposed thermal pad.

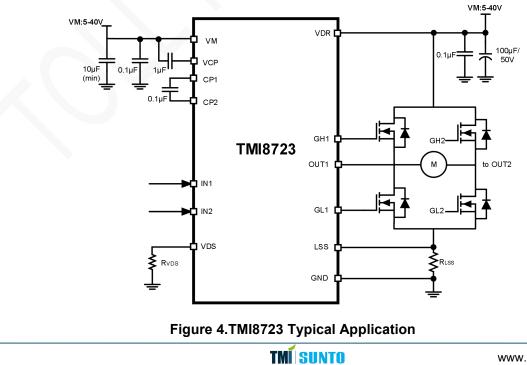

# **TYPICAL APPILCATION**

Figure 1. Basic Application Circuit

# ABSOLUTE MAXIMUM RATINGS (Note 1)

| Parameter                                               | Min  | Мах      | Unit |

|---------------------------------------------------------|------|----------|------|

| Power supply voltage (VM)                               | -0.3 | 45       | V    |

| Logic input voltage(IN1, IN2, VDS)                      | -0.3 | 6        | V    |

| Output pin voltage (OUT1, OUT2)                         | -0.3 | VM + 0.3 | V    |

| High-side gate pin voltage (GH1, GH2)                   | -0.3 | VM + 12  | V    |

| Low-side gate pin voltage (GL1, GL2)                    | -0.3 | 12       | V    |

| Current sense input pin voltage (LSS)                   | -0.3 | 12       | V    |

| Operating ambient temperature,Ta                        | -40  | 125      | °C   |

| Operating junction temperature, T <sub>J (Note 2)</sub> | -40  | 150      | °C   |

| Storage temperature                                     | -40  | 150      | °C   |

### **ESD RATING**

| Items | Description                | Value | Unit |

|-------|----------------------------|-------|------|

| VESD  | Human body model           | ±2000 | V    |

|       | Charged device model (CDM) | ±750  | V    |

### **JEDEC** specification JS-001

# PACKAGE/ORDER INFORMATION

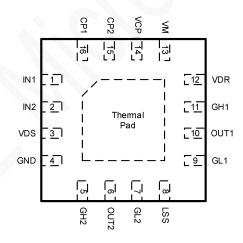

#### QFN3x3-16

TMI8723/XXXXX (TMI8723: Device Code, XXXXX: Inside Code) for TMI8723

| Part Number | Package   | Top mark | Quantity/ Reel |

|-------------|-----------|----------|----------------|

| TM10700     | QFN3x3-16 | TMI8723  | 2 000          |

| TMI8723     |           | XXXXX    | 3,000          |

The TMI8723 device is Pb-free and RoHS compliant.

**TMÍ SUNTO**

### **PIN FUNCTIONS**

| PIN# | Name                                                                                                                                    | Function                                                                                                                      |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1    | IN1                                                                                                                                     | Logic inputs. Controls the output. Internal pulldown.                                                                         |  |  |

| 2    | IN2                                                                                                                                     | Logic inputs. Controls the output. Internal pulldown.                                                                         |  |  |

| 3    | VDSVDS monitor setting pin. The resistor value or voltage forced on<br>the VDS monitor threshold. For more information see the Table 1. |                                                                                                                               |  |  |

| 4    | GND                                                                                                                                     | Ground.                                                                                                                       |  |  |

| 5    | GH2                                                                                                                                     | High-side gate, connect to the high-side FET gate.                                                                            |  |  |

| 6    | OUT2                                                                                                                                    | Connect to high-side FET source and low-side FET drain.                                                                       |  |  |

| 7    | GL2                                                                                                                                     | Low-side gate, connect to the low-side FET gate.                                                                              |  |  |

| 8    | LSS                                                                                                                                     | Low-side source .                                                                                                             |  |  |

| 9    | GL1                                                                                                                                     | Low-side gate, connect to the low-side FET gate.                                                                              |  |  |

| 10   | OUT1                                                                                                                                    | Connect to high-side FET source and low-side FET drain.                                                                       |  |  |

| 11   | GH1                                                                                                                                     | High-side gate, connect to the high-side FET gate.                                                                            |  |  |

| 12   | VDR                                                                                                                                     | High-side FET drain connection. This pin is common for the two H-bridges.                                                     |  |  |

| 13   | VM                                                                                                                                      | Power supply input. Connect a $0.1\mu$ F bypass capacitor to ground, as well as a $10\mu$ F(minimum) bulk capacitance for VM. |  |  |

| 14   | VCP                                                                                                                                     | Charge-pump output. Connect a $1\mu\text{F}$ ceramic capacitor between this pin and the VM pin.                               |  |  |

| 15   | CP2                                                                                                                                     | Charge-pump switching node. Connect a 0.1µF X7R capacitor rated for the                                                       |  |  |

| 16   | CP1                                                                                                                                     | supply voltage (VM) between the CP2 and CP1 pins.                                                                             |  |  |

| -    | GND                                                                                                                                     | Thermal pad. Connect to device power ground.                                                                                  |  |  |

# **RECOMMENDED OPERATING CONDITIONS**

| Items             | Description                 | Min  | Мах | Unit |

|-------------------|-----------------------------|------|-----|------|

| VM                | Power supply voltage range  | 5    | 40  | V    |

| V <sub>IN_X</sub> | Logic input voltage range   | -0.3 | 5   | V    |

| f <sub>IN_X</sub> | Logic input frequency       | 0    | 50  | kHz  |

| LSS               | Low-side Source Connection. | -1   | 1   | V    |

# ELECTRICAL CHARACTERISTICS T<sub>A</sub> = 25°C, (unless otherwise noted.)

| PARAMETER                                 | SYMBOL                  | TEST CONDITIONS                                                           | MIN | TYP  | MAX       | UNIT |

|-------------------------------------------|-------------------------|---------------------------------------------------------------------------|-----|------|-----------|------|

| Power section (VM)                        |                         |                                                                           |     |      |           |      |

| Power supply voltage                      | VM                      |                                                                           | 5   |      | 40        | V    |

|                                           | I <sub>VMQ</sub>        | VM=13.5V, IN1=IN2=0V, no<br>load                                          |     |      | 20        | μA   |

| Quiescent current                         | I <sub>VM</sub>         | VM=13.5V, IN1=IN2=5V or<br>IN1=5V & IN2=0V or IN1=0V &<br>IN2=5V, no load | 1   | 1.5  | 2         | mA   |

|                                           | I <sub>VMPWM</sub>      | VM=13.5V, IN1=5V,<br>IN2=50kHz, no load                                   | 1   | 1.8  | 3         | mA   |

| CONTROL LOGIC                             |                         |                                                                           |     |      |           |      |

| Input logic low threshold                 | VIL                     |                                                                           |     |      | 0.7       | V    |

| Input logic high threshold                | VIH                     |                                                                           | 1.5 |      | 5.5       | V    |

| Input logic high current                  | IIH                     | VM=13.5V, V <sub>INx</sub> = 5V                                           |     | 50   | 70        | μA   |

| Input logic low current                   | l <sub>iL</sub>         | VM=13.5V, V <sub>INx</sub> = 0V                                           |     |      | 1         | μA   |

| RDS Pulldown resistance                   | R <sub>PD</sub>         |                                                                           |     | 166  |           | kΩ   |

| RDS Pullup resistance                     | R <sub>PU</sub>         |                                                                           |     | 93   |           | kΩ   |

| Propagation delay                         | t <sub>PD</sub>         | IN1, IN2 to GHx or GLx                                                    |     | 300  |           | ns   |

| FET GATE DRIVERS (GH1, GI                 | H2, GL1, GL2, C         | OUT1, OUT2)                                                               |     |      |           |      |

|                                           |                         | VM>13.5V(VM=36V)                                                          |     | 10.5 | 11.7      | V    |

| High-side VGS gate drive (gate-to-source) | V <sub>GSH</sub>        | VM=8V                                                                     | 6.2 |      | 7.3       | V    |

|                                           |                         | VM=5.5V                                                                   | 3.9 |      | 4.9       | V    |

| Low-side VGS gate drive                   |                         | VM>13.5V(VM=36V)                                                          |     | 10.5 |           | V    |

| (gate-to-source)                          | Vgsl                    | VM<13.5V                                                                  |     | VM   |           | V    |

| Link side Osta Drive surrant              | I <sub>GHX</sub>        | Peak Sink current                                                         |     | 500  |           | mA   |

| High-side Gate Drive current              |                         | Peak Source current                                                       |     | 250  |           | mA   |

| Lauraida Oata Drive averant               |                         | Peak Sink current                                                         |     | 500  |           | mA   |

| Low-side Gate Drive current               | I <sub>GLX</sub>        | Peak Source current                                                       |     | 250  |           | mA   |

|                                           | P                       | Pulldown GHx to OUT                                                       |     | 200  |           | kΩ   |

| FET gate holdoff resistor                 | R <sub>OFF</sub>        | Pulldown GLx to GND                                                       |     | 200  |           | kΩ   |

| Output dead time                          | t <sub>DEAD</sub>       |                                                                           |     | 240  |           | ns   |

| Output rise time                          | trise                   | VM=13.5V, OUTx rising 10% to 90%                                          |     | 150  |           | ns   |

| Output fall time                          | t <sub>FALL</sub>       | VM=13.5V, OUTx falling 90% to 10%                                         |     | 150  |           | ns   |

| PROTECTION CIRCUITS                       | 1                       | 1                                                                         |     |      | 1         |      |

|                                           | V <sub>UVLO_RISE</sub>  | VM rising                                                                 | 4.5 | 4.7  | 4.8       | V    |

| VM undervoltage lockout                   | VUVLO_FALL              | VM falling                                                                | 4.2 | 4.4  | 4.5       | V    |

|                                           | VCP_UV_RISE             | VCP rising                                                                |     | 4.1  |           | V    |

| VCP undervoltage lockout                  | V <sub>CP_UV_FALL</sub> | VCP falling                                                               |     | 3.7  |           | V    |

|                                           |                         | TMÍSUNTO                                                                  |     | ·    | www.toll- |      |

# ELECTRICAL CHARACTERISTICS (Continued)

### T<sub>A</sub> = 25°C, (unless otherwise noted.)

|                                                       | V <sub>DS1</sub>          | R(VDS)=2k                              |     | 0.12 |     | V  |

|-------------------------------------------------------|---------------------------|----------------------------------------|-----|------|-----|----|

| Overcurrent protection trip                           | V <sub>DS2</sub>          | R(VDS)=30K                             |     | 0.24 |     | V  |

| level, VDS of each external                           | V <sub>DS3</sub>          | R(VDS)=100K                            |     | 0.48 |     | V  |

| FET High side FETs: VDR –<br>OUTx Low side FETs: OUTx | V <sub>DS4</sub>          | R(VDS)=FLOATING                        |     | 0.96 |     | V  |

| - LSS                                                 | V                         | VDS>4.5V                               |     | Disa |     | v  |

| - 192                                                 | V <sub>DS5</sub> VDS>4.5V |                                        | ble |      | v   |    |

| V <sub>Lss</sub> protection trip level                | V <sub>LSS</sub>          | V <sub>Lss</sub> protection trip level | 0.8 | 1    | 1.2 | V  |

| OCP deglitch time                                     | t <sub>OCP</sub>          |                                        |     | 4    |     | μs |

| Overcurrent retry time                                | t <sub>RETRY</sub>        |                                        |     | 2.5  |     | ms |

| nSLEEP wake-up time                                   | tsleep                    |                                        |     | 1    |     | ms |

| Thermal shutdown                                      | T <sub>SD(Note 3)</sub>   |                                        |     | 150  |     | °C |

| Thermal shutdown hysteresis                           | THYS (Note 3)             |                                        |     | 25   |     | °C |

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

Note 2:  $T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation  $P_D$  according to the following formula:  $T_J$

=  $T_A + P_D x \theta_{JA}$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_{D (MAX)} = (T_{J(MAX)}-T_A)/\theta_{JA}$ .

Note 3: Thermal shutdown threshold and hysteresis are guaranteed by design.

## **OPERATION**

### Overview

The TMI8723 is single H-bridge drivers, also referred to as gate controllers. The drivers control four external NMOS FETs used to drive a bi-directional brushed-DC motors, with 0.25A source and 0.5A sink current capability. It operates over a wide input voltage range of 5V to 40V, generating a boosted gate drive voltage when the input supply is below 12V. The TMI8723 features a low-power sleep mode, which disables the device and draws a very low supply current.

Both the high-side and low-side FETs are driven with a gate source voltage (VGS) of 10.5 V (nominal) when the VM voltage is more than 13.5 V. At lower VM voltages, the VGS is reduced. The high-side gate drive voltage is generated using a doubler-architecture charge pump that regulates to the VM + 10.5 V.

TMI8723 device also has protection features beyond traditional discrete implementations including: undervoltage lockout (UVLO), overcurrent protection (OCP) and thermal shutdown (TSD).

### Sleep Mode (nSLEEP Input)

The IN1 and IN2 pins put the IC into sleep mode and TMI8723 into sleep mode when IN1/IN2 continues to pull down for 1ms. When exiting sleep mode, the part will initiate the power-up sequence described above.

#### **Control Modes**

The TMI8723 output consists of four N-channel MOSFETs that are designed to drive high current. These outputs are controlled by the two logic inputs IN1 and IN2 as listed in Table 1.

| IN1 | IN2 | GH1 | GL1 | OUT1 | GH2 | GL2 | OUT2 | DESCRIPTION                               |

|-----|-----|-----|-----|------|-----|-----|------|-------------------------------------------|

| Н   | L   | 1   | 0   | Н    | 0   | 1   | L    | Forward (Current OUT1 $\rightarrow$ OUT2) |

| L   | Н   | 0   | 1   | L    | 1   | 0   | Н    | Reverse (Current OUT2 → OUT1)             |

| L   | L   | Х   | Х   | Hi-Z | Х   | Х   | Hi-Z | Sleep mode H bridge disabled Hi-Z         |

| Н   | н   | 0   | 1   | Ĺ    | 0   | 1   | L    | Brake low-side slow decay                 |

Table 1: Input Logic Truth Table

The inputs can be set to static voltages for 100% duty cycle drive, or they can be pulse-width modulated (PWM) for variable motor speed. When using PWM, switching between driving and braking typically works best. For example, to drive a motor forward with 50% of the maximum RPM, IN1 = 1 and IN2 = 0 during the driving period, and IN1 = 1 and IN2 = 1 during the other period. Alternatively, the coast mode (IN1 = 0, IN2 = 0) for fast current decay is also available. The input pins can be powered before VM is applied.

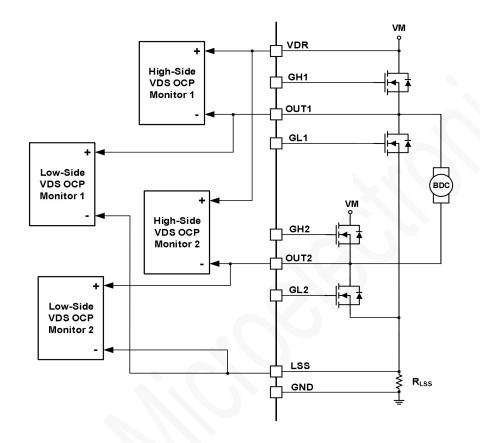

#### **Overcurrent VDS Monitor**

The gate-driver circuit monitors the VDS voltage of each external FET when it is driving current. When the voltage monitored is greater than the OCP threshold voltage (VDS(OCP)) after the OCP

deglitch time has expired, an OCP condition is detected. The TMI8723 device provides VDS(OCP) voltage levels by setting the VDS resistance.

The VDS voltage on the high-side FET is measured across the VDRAIN to OUTx pins. The low-side VDS monitor on half-bridge 1 measures the VDS voltage across the OUTx to LSS pins.

#### Figure 2. V<sub>DS(OCP)</sub> Block Diagram

The VDS pin on the TMI8723 device is used to select the VDS threshold voltage for overcurrent detection. For exemple: Tying the VDS pin  $2k\Omega$  to ground selects the lowest setting of 0.12V. For a detailed list of VDS configurations, see Table 2.

| Table  | 2. | VDS | Pin | Resistor | Settina |

|--------|----|-----|-----|----------|---------|

| 1 4010 | _  |     |     | 10010101 | ootting |

| VDS<br>RESISTANCE | VDS VOLTAGE | OVERCURRENT<br>TRIP LEVEL<br>(VDS(OCP)) | CIRCUIT |

|-------------------|-------------|-----------------------------------------|---------|

| R(VDS)=2kΩ to GND | 0.5V        | 0.12V                                   | RVDS    |

| VDS<br>RESISTANCE   | VDS VOLTAGE | OVERCURRENT<br>TRIP LEVEL<br>(VDS(OCP)) | CIRCUIT      |

|---------------------|-------------|-----------------------------------------|--------------|

| R(VDS)=30kΩ to GND  | 1.2V        | 0.24V                                   | Rvds         |

| R(VDS)=100kΩ to GND | 2.0V        | 0.48V                                   |              |

| R(VDS)=FLOATING     | 3.5V        | 0.96V                                   | FLOATING VDS |

| VDS>4.5V            | 5V          | Disable                                 | T >4.5V      |

#### Table 2. VDS Pin Resistor Setting(Continued)

### **UVLO Protection**

If at any time the voltage on the VM pin falls below the undervoltage-lockout threshold voltage, all FETs in the device will be disabled. Operation resumes when VM rises above the UVLO threshold.

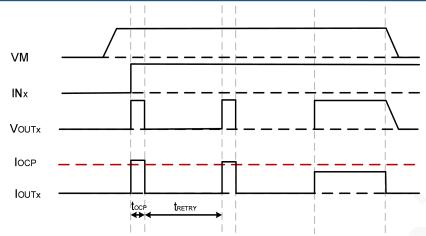

### **Overcurrent Protection (OCP)**

If the output current exceeds the OCP threshold, IOCP, for longer than  $t_{OCP}$ , all FETs in the device are disabled. After a duration of  $t_{RETRY}$ , the MOSFET is re-enabled according to the state of the INx pins. If the overcurrent fault is still present, the cycle repeats; otherwise normal device operation resumes.

TMI8723

Figure 3. Over current protection Time Periods

#### **LSS Protection**

When the LSS pin voltage exceeds 1.0V, TMI8723 triggers LSS overcurrent protection; GHSx and LHx on the high and low sides enter the automatic restart phase, and the automatic restart time tretry is 2.5ms. When the LSS pin voltage is below 1.0V, GHSx and GLHx return to normal.

### **Thermal Shutdown**

If the die temperature exceeds safe limits, all FETs in the the H-bridge are disabled. After the die temperature has fallen to a safe level, operation automatically resumes.

# **APPLICATION INFORMATION**

### **Application information**

The TMI8723 device is typically used to drive one brushed DC motor as below.

TMI8723

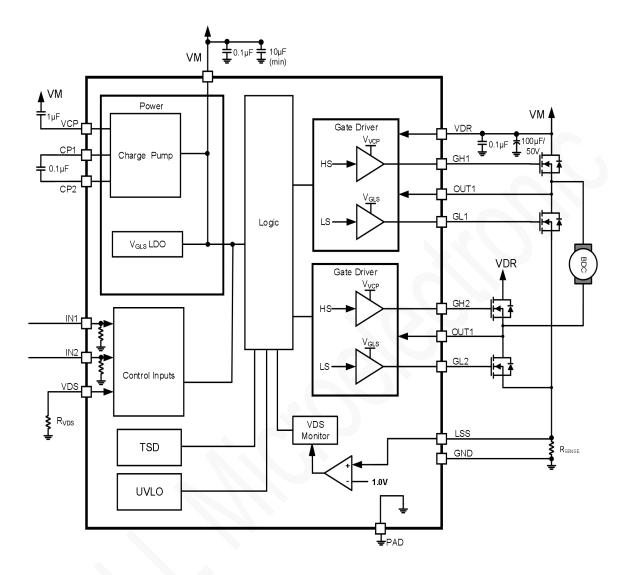

# **Block Diagram**

Figure 5. TMI8723 Block Diagram

TMÍ SUNTO

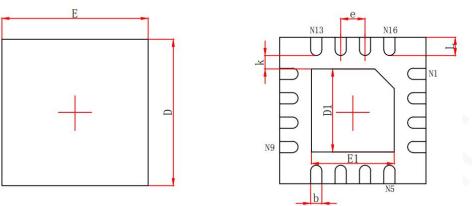

# **PACKAGE INFORMATION**

### QFN3x3-16

Top View

Side View

Unit: mm

| Symbol | Dimensions I | n Millimeters | Sum hal | <b>Dimensions In Millimeters</b> |      |  |

|--------|--------------|---------------|---------|----------------------------------|------|--|

| Symbol | Min          | Мах           | Symbol  | Min                              | Max  |  |

| А      | 0.70 0.80    |               | E1      | 1.60                             | 1.80 |  |

| A1     | -            | 0.05          | k       | 0.2MIN                           |      |  |

| A3     | 0.203        | REF           | е       | 0.50 TYP                         |      |  |

| D      | 2.90         | 3.10          | b       | 0.18                             | 0.30 |  |

| E      | 2.90 3.10    |               | L       | 0.30                             | 0.50 |  |

| D1     | 1.60         | 1.80          |         |                                  |      |  |

#### Note:

- 1) All dimensions are in millimeters.

- 2) Package length does not include mold flash, protrusion or gate burr.

- 3) Package width does not include inter lead flash or protrusion.

- 4) Lead popularity (bottom of leads after forming) shall be 0.10 millimeters max.

- 5) Pin 1 is lower left pin when reading top mark from left to right.

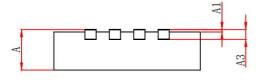

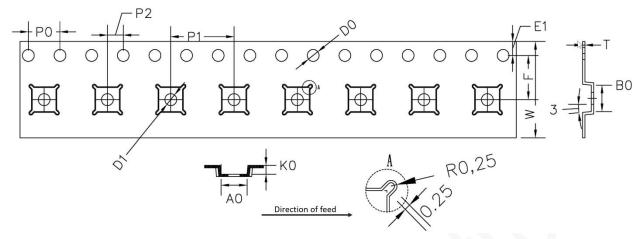

## TAPE AND REEL INFORMATION

### **TAPE DIMENSIONS: QFN3x3-16**

Unit: mm

| Symbol | Dimensions | Symbol | Dimensions | Symbol | Dimensions | Symbol | Dimensions |

|--------|------------|--------|------------|--------|------------|--------|------------|

| A0     | 3.30±0.10  | P0     | 4.00±0.10  | E1     | 1.75±0.10  | D1     | 1.55±0.05  |

| B0     | 3.30±0.10  | P1     | 8.00±0.10  | F      | 5.50±0.10  | Т      | 0.30±0.05  |

| K0     | 1.10±0.10  | P2     | 2.00±0.10  | D0     | 1.55±0.05  | W      | 12.00±0.30 |

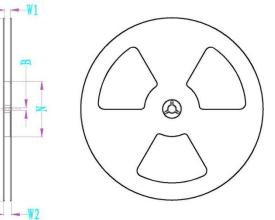

### **REEL DIMENSIONS: QFN3x3-16**

Unit: mm

|         | •       |          |         |          |          |

|---------|---------|----------|---------|----------|----------|

| ØA      | В       | ØC       | ØN      | W1       | W2       |

| 330±1.0 | 4.7±0.5 | 13.5±0.2 | 100±0.5 | 13.4±0.5 | 17.4±0.5 |

#### Note:

- 1) All Dimensions are in Millimeter

- 2) Quantity of Units per Reel is 3000

- 3) MSL level is level 3.

# **Important Notification**

This document only provides product information. Xi'an TOLL Microelectronic Inc. (TMI) reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and to discontinue any product without notice at any time.

Xi'an TOLL Microelectronic Inc. (TMI) cannot assume responsilN2lity for use of any circuitry other than circuitry entirely embodied in a TMI product. No circuit patent licenses are implied.

All rights are reserved by Xi'an TOLL Microelectronic Inc. http:// www.toll-semi.com

TMÍ SUNTO