# EVALPWD5F60

### Demonstration board for PWD5F60 smart driver with integrated high voltage full bridge

Data brief

### Features

- Power system-in-package integrating gate drivers and power MOSFETs featuring:

- R<sub>DS(ON)</sub> = 1.38 Ω

- BV<sub>DSS</sub> = 600 V

- 2 embedded comparators

- Very low area occupation, all active devices in SMT technology and no heatsink

- Fast-decay or slow-decay on-board constant OFF-time peak current control

- PWM voltage mode control with overcurrent protection possible via external logic signals

- Driver supply voltage range: 10 V to 20 V

- UVLO protection on low-side and high-side

- 3.3 V to 15 V compatible inputs with hysteresis and pull-down

- Internal bootstrap diode

- Bill of materials reduction

- Very compact and simplified layout

- Flexible, easy and fast design

- RoHS compliant

- Load current up to 1 A

### Description

The PWD5F60 is an advanced power system-inpackage integrating gate drivers and four N-channel power MOSFETs in a compact QFN package.

The integrated power MOSFETs have an R<sub>DS(ON)</sub> of 1.38  $\Omega$  and 600 V drain-source breakdown voltage. The embedded gate drivers feature two comparators that can be used for peak current control or overcurrent protection and integrate bootstrap diodes. This allows to effectively drive loads in a tiny space and to drastically reduce external components and bill of materials.

The EVALPWD5F60 demonstrates how to use the PWD5F60 to drive a single-phase load in fullbridge topology. This allows control of both the direction and the value of the current flowing into the load. Typical applications that can benefit from the high integration of the PWD5F60 are, for example, single-phase BLDC motors and fans.

The board has a very small footprint and an optimized layout thanks to the integrated features of the PWD5F60, and it can be simply run by applying the supply voltages and a direction signal.

The board allows easy selection and modification of the relevant external component values, enabling fast performance evaluation under different applicative conditions as well as fine tuning of final application components.

For further information contact your local STMicroelectronics sales office.

## 1 Board description

#### Table 1. EVALPWD5F60 electrical specifications

| Parameter                                                 | Value               |

|-----------------------------------------------------------|---------------------|

| Max supply voltage range (VS) <sup>(1)</sup>              | 400 V <sub>DC</sub> |

| Driver supply voltage (Vcc)                               | 10 to 20 V          |

| Logic control signals                                     | 0 to 15 V           |

| Junction to ambient thermal resistance RJA <sup>(2)</sup> | 30 °C/W             |

| Operating temperature range                               | -40 °C to +125 °C   |

1. Maximum VS voltage is limited by the electrolytic bulk capacitor (C26) voltage rating; PWD5F60 BVDSS is 600 V.

2. Measured with uniform dissipation on the power MOSFETs

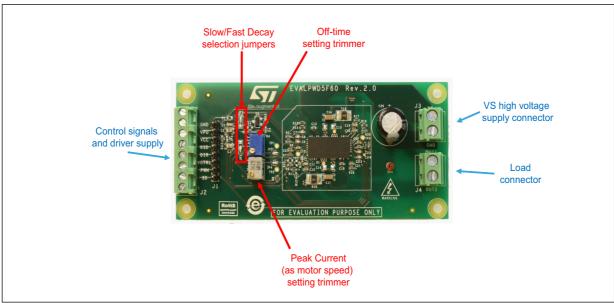

### Figure 1. Jumpers and connectors location

| Name | Туре                      | Function                                                                                       |

|------|---------------------------|------------------------------------------------------------------------------------------------|

| J1   | Control signals connector | VCC and logic control signals, pin strip header                                                |

| J2   | Control signals connector | VCC and logic control signals, terminal block connector                                        |

| J3   | Power supply              | VS high voltage power supply connector                                                         |

| J4   | Power output              | Load connector                                                                                 |

| JP1  | Configuration jumper      | To connect V <sub>PU</sub> pull-up voltage to VCC                                              |

| JP2  | Configuration jumper      | To pull-up SD or PWM signals to V <sub>PU</sub> pull-up voltage                                |

| JP3  | Configuration jumper      | To connect SD or PWM signal to CPOUT2                                                          |

| JP4  | Configuration jumper      | To use trimmer TR2 for setting the peak current instead of R10                                 |

| JP5  | Configuration jumper      | To use trimmer TR1 for setting OFF-time duration after<br>overcurrent detection instead of R23 |

Table 2. Jumpers and connectors description

| Table 3. Control sig    | nals connector | pinout (J1  | - J2)    |

|-------------------------|----------------|-------------|----------|

| Tuble 0. Control or org |                | piniout (or | <u> </u> |

| Pin | Label | Туре               | Description                                                                       |

|-----|-------|--------------------|-----------------------------------------------------------------------------------|

| 1   | SD    | Digital input      | Drivers' SD signal                                                                |

| 2   | PWM   | Digital input      | Drivers' PWM signal                                                               |

| 3   | VCTRL | Analog / PWM input | V <sub>ctrl</sub> signal, sets current limit threshold (as motor speed)           |

| 4   | DIR   | Digital input      | DIR signal, sets current's direction (as from Hall sensor)                        |

| 5   | RSD   | Reserved           | Reserved                                                                          |

| 6   | VCC   | Power supply       | Drivers' V <sub>CC</sub> power supply                                             |

| 7   | VPU   | Power supply       | $V_{\mbox{PU}}$ pull-up voltage for drivers' signals. Close JP1 to connect to VCC |

| 8   | GND   | Power supply       | GND                                                                               |

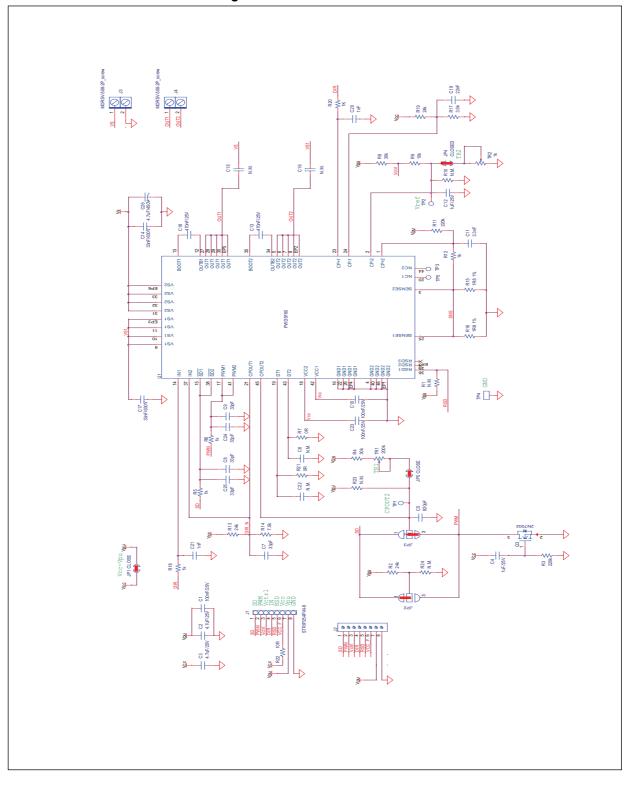

## 2 Schematic diagram

Figure 2. EVALPWD5F60 circuit schematic

DB3717 Rev 1

| Part reference        | Part value           | Part description                          |  |

|-----------------------|----------------------|-------------------------------------------|--|

| C7, C8, C9, C24, C25  | 33 pF                | Ceramic capacitor, SMT 0603               |  |

| C5                    | 820 pF               | Ceramic capacitor, SMT 0603               |  |

| C11                   | 3.3 nF               | Ceramic capacitor, SMT 0603               |  |

| C19                   | 22 nF                | Ceramic capacitor, SMT 0603               |  |

| C1, C10, C23          | 100 nF / 25 V        | Ceramic capacitor, SMT 0603               |  |

| C13, C18              | 470 nF / 25 V        | Ceramic capacitor, SMT 0603               |  |

| C4, C12               | 1 μF / 25 V          | Ceramic capacitor, SMT 0603               |  |

| C6, C22               | N.M.                 | Ceramic capacitor, SMT 0603               |  |

| C2, C3                | 4.7 μF / 25 V        | Ceramic capacitor, SMT 0805               |  |

| C14, C17              | 33 nF / 630 V        | Ceramic capacitor, SMT 1206               |  |

| C15, C16              | N.M.                 | Ceramic capacitor, SMT 1206               |  |

| C26                   | 4.7 μF / 450 V - 20% | Electrolytic capacitor, T.H. D10 H12.5 P5 |  |

| JP1, JP4, JP5         | Jumper - CLOSED      | SMT jumper - 2 poles                      |  |

| JP2                   | Jumper - 1-2 CLOSED  | SMT jumper - 3poles                       |  |

| JP3                   | Jumper - 2-3 CLOSED  | SMT jumper - 3 poles                      |  |

| J1                    | STRIP254P-M-8        | Pin strip header 2.54 mm, 8 poles         |  |

| J2                    | Screw connector      | Conn. term. block T.H. 8 POS 3.5 mm       |  |

| J3, J4                | Screw connector      | Conn. term. block T.H. 2 POS 5.08 mm      |  |

| R1, R10, R23, R24     | N.M.                 | Resistor, SMT 0603                        |  |

| R2, R13, R19          | 24 kΩ                | Resistor, SMT 0603                        |  |

| R4, R8                | 30 kΩ                | Resistor, SMT 0603                        |  |

| R5, R6, R12, R18, R20 | 1 kΩ                 | Resistor, SMT 0603                        |  |

| R7, R21               | 0 Ω                  | Resistor, SMT 0603                        |  |

| R9                    | 10 kΩ                | Resistor, SMT 0603                        |  |

| R3, R11               | 220 kΩ               | Resistor, SMT 0603                        |  |

| R14                   | 7.5 kΩ               | Resistor, SMT 0603                        |  |

| R15, R16              | 1.8 Ω - 1 %          | Resistor, SMT 1210                        |  |

| R17                   | 3.9 Ω                | Resistor, SMT 0603                        |  |

| R22                   | 10 Ω                 | Resistor, SMT 0603                        |  |

| TP1, TP2, TP3, TP5    | Test point SMD       | SMD test point 50 mils                    |  |

| TP4                   | Ring test point      | Test point PCB 1 mm T.H.                  |  |

| TR1                   | 200 kΩ               | Trimmer 1/4 W - Bourns 3266 W             |  |

#### Table 4. EVALPWD5F60 - Bill Of Materials

| Part reference Part value |         | Part description                                |

|---------------------------|---------|-------------------------------------------------|

| TR2                       | 1 kΩ    | Trimmer 1/4 W - Bourns 3266 W                   |

| U1                        | PWD5F60 | PWD5F60, VFQFPN 15x7                            |

| Q3                        | 2N7002  | 60 V small signal N-channel MOSFET,<br>SOT23-3L |

### Table 4. EVALPWD5F60 - Bill Of Materials (continued)

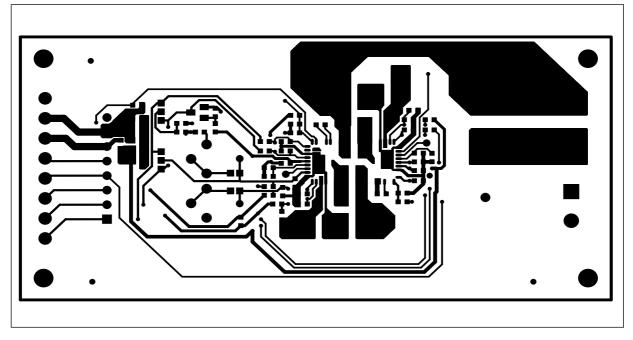

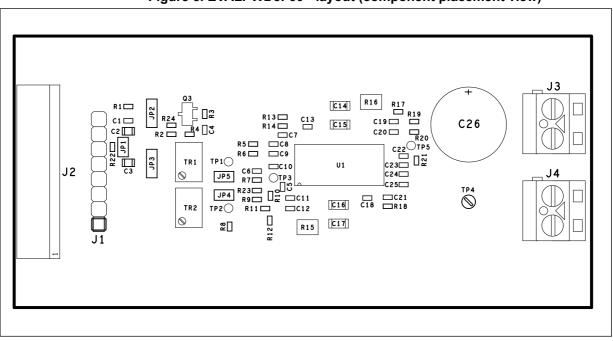

Figure 3. EVALPWD5F60 - layout (top layer)

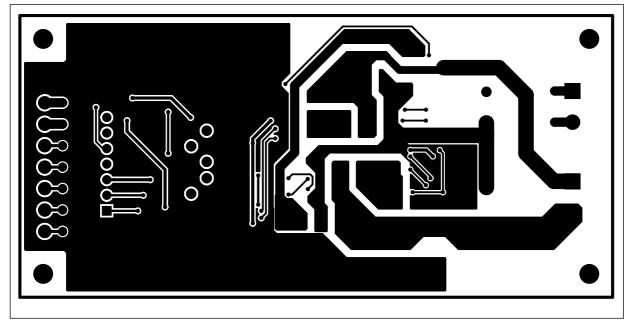

Figure 4. EVALPWD5F60 - layout (bottom layer)

### Schematic diagram

Figure 5. EVALPWD5F60 - layout (component placement view)

## 3 Revision history

| Date        | Revision | Changes         |

|-------------|----------|-----------------|

| 29-Aug-2018 | 1        | Initial release |

### Table 5. Document revision history

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics – All rights reserved

DB3717 Rev 1